国际信息工程先进技术译丛

# 纳米CMOS 电路和物理设计

**Nano-CMOS Circuit

and Physical Design**

(美) BAN P.WONG ANURAG MITTAL

YU CAO GREG STARR

辛维平 刘伟峰 戴显英 等译

著

等译

机械工业出版社

CHINA MACHINE PRESS

## 关于本书

新技术的快速发展与纳米级缩小的挑战正促使原先相互分离的电路设计、工艺技术、器件物理和物理实现组合在一起形成一门学科。深刻地理解器件、互连和组装方面包含的物理限制对设计电路系统和器件以及做出合理的技术决定都是非常重要的。

《纳米CMOS电路和物理设计》一书将纳米工艺、器件可制造性、先进电路设计和相关物理实现整合到一起，形成了一套先进的半导体技术。这本内容广泛的书探讨了器件和工艺的新发展，提供了设计考虑，重点关注了技术与设计的相互影响，如信号完整性和互连，并且描述了可制造性设计和波动性的影响。重要的主题包括：

- 纳米CMOS工艺缩小问题及其对设计的影响

- 亚波长光刻

- 运行问题的物理与理论以及解决方案

- 可制造性设计和波动性

《纳米COMS电路和物理设计》对集成电路设计者和该领域的专业人员是一本非常有用的书，给他们提供了实际的设计方案和方法。

国际信息工程先进技术译丛

# 纳米 CMOS 电路和物理设计

(美) BAN P. WONG ANURAG MITTAL

YU CAO GREG STARR 著

辛维平 刘伟峰 戴显英 李玉山 史江一 刘毅 贾新章 译校

机械工业出版社

本书将纳米工艺、器件可制造性、先进电路设计和相关物理实现等内容整合到一起，形成了一套先进的半导体技术，探讨了器件和工艺的新发展，提供了设计考虑，重点关注了技术与设计的相互影响，并且描述了可制造性设计和波动性的影响。重要的主题包括纳米 CMOS 工艺缩小问题及其对设计的影响；亚波长光刻；运行问题的物理与理论以及解决方案；可制造性设计和波动性。

本书适合集成电路设计者和该领域的专业人员阅读。

Copyright© 2005 by John Wiley & Sons, Inc., Hoboken, New Jersey.

All Right Reserved. This translation published under license.

本书中文简体字版由 Wiley 授权机械工业出版社独家出版。未经出版者书面允许，本书的任何部分不得以任何方式复制或抄袭。版权所有，翻印必究。

本书版权登记号：图字 01-2008-4175 号

### 图书在版编目 (CIP) 数据

纳米 CMOS 电路和物理设计/(美) 王班 (Wong, B. P.) 等著；辛维平等译. —北京：机械工业出版社，2011. 2

(国际信息工程先进技术译丛)

Nano-CMOS Circuit and Physical Design

ISBN 978-7-111-33083-7

I. ①纳… II. ①王…②辛… III. ①纳米材料－互补 MOS 集成电路－

集成电路－电路设计 IV. ①TN432

中国版本图书馆 CIP 数据核字 (2011) 第 008772 号

机械工业出版社 (北京市百万庄大街 22 号 邮政编码 100037)

策划编辑：吕 潢 责任编辑：吕 潢

版式设计：霍永明 责任校对：陈延翔

封面设计：马精明 责任印制：李 妍

北京振兴源印务有限公司印刷

2011 年 4 月第 1 版第 1 次印刷

169mm × 239mm · 22.5 印张 · 436 千字

0001—3000 册

标准书号：ISBN 978-7-111-33083-7

定价：98.00 元

凡购本书，如有缺页、倒页、脱页，由本社发行部调换

电话服务 网络服务

社服务中心：(010)88361066 门户网：<http://www.cmpbook.com>

销售一部：(010)68326294

教材网：<http://www.cmpedu.com>

销售二部：(010)88379649

读者购书热线：(010)88379203 封面无防伪标均为盗版

# 译者的话

随着技术的进步，以 CMOS 技术为主流的集成电路已按照摩尔定律预言的发展规律进入到了纳米时代。CMOS 电路在低成本、低功耗、高集成度等方面的优势，以及在速度方面的不断提高，使 CMOS 技术已经成为集成电路芯片，特别是 SoC 芯片设计者的最佳选择。纳米 CMOS 技术不仅对工艺技术提出了一系列需要解决的难题，也给电路设计、版图集成以及工艺工程师带来许多新的挑战，要求他们打破相互之间的隔绝状态，进一步把握电路、版图以及工艺之间的相互影响。例如，工艺技术快速发展带来的泄漏增大、工艺波动性的影响增强等问题要求电路与版图设计工程师采取新的对策；为了成功地实现电路功能的不断增加，需要工艺工程师更多地了解电路设计以及版图设计中的一些细节。

针对纳米时代 CMOS 技术的特点，本书的价值在于第一次在同一本书中将工艺与电路、版图设计综合到一起，结合大量的数据与图片资料详细论述了工艺制造与电路、版图设计之间的相互影响，同时介绍了目前最新的技术对策和发展水平。因此本书同时适合集成电路设计和工艺人员阅读。通过本书的学习，可以使设计者对纳米 CMOS 器件和工艺的现状和未来有较全面的了解，对设计者的工作起到指导作用。同时，本书也是纳米 CMOS 工艺工程师了解电路与版图设计的一个窗口。对于大学研究生来说，本书也是一本较好的参考书。

本书第 1 章、第 2 章、第 5 章、第 9 章、第 10 章和第 11 章由辛维平翻译，第 3 章由戴显英翻译，第 4 章和第 6 章由史江一翻译，第 7 章以及第 9 章和第 11 章中关于 RAM 的部分内容由刘伟峰翻译，第 8 章由李玉山翻译，刘毅协助翻译了第 11 章中关于数字电路的部分内容，徐建强对翻译初稿的改善提出了很多修改建议。全书由贾新章审校、统稿。由于本书内容新颖，涉及不少新技术，加之译校者专业和英语水平有限，译文中不当之处甚至错误在所难免，欢迎读者提出宝贵意见，展开讨论。

译、校者 于西安电子科技大学

# 原    书    序

在过去的数十年中，CMOS 前沿技术不断地发生着翻天覆地的突破性变化，创造了技术上的奇迹。由制造商耗费数十亿美元创建的工厂制造出的线宽小于 100nm、集成度达到 10 亿个晶体管的复杂集成电路，极大地改变了我们生活的世界。只有许多精通其领域技艺的专家经过不懈努力并发挥他们的聪明才智才可能实现微电子领域的革命。

IC 设计者、器件集成者和工艺工程师已经认识到了广泛理解 IC 技术各个方面带来的益处，正通过持之以恒的学习涉猎相关领域的知识。对 IC 设计者来说，为了充分获得可实现的产品价值，深刻地理解器件、互连和制造方面所包含的物理限制是非常重要的。对于技术开发者，了解技术对先进设计的影响是做出合理技术决定的必要基础。

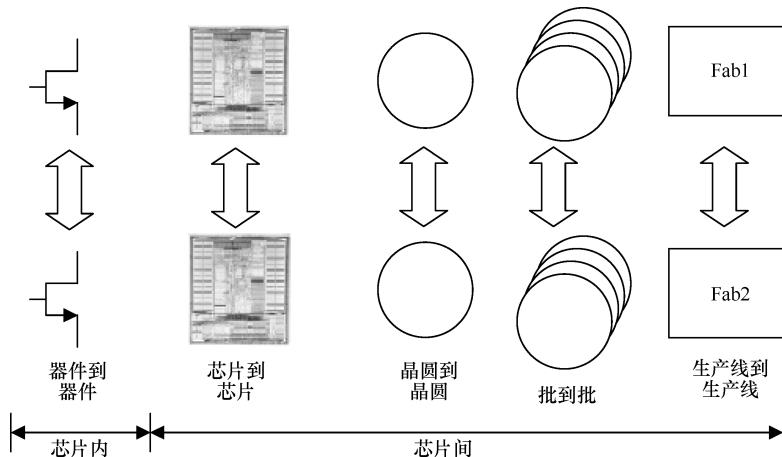

虽然获取相邻领域知识的需求总是存在的，但是近年来，基于多种原因，使得这种需求更加迫切。新技术引入的步伐与电路速度提升的速率明显快于前 20 年。这种加快的步伐可能会延续很长时间，也可能不会持续太久，不过，现在有比以前更大量的新知识需要工程师们去学习与使用。还有一个原因是，随着工艺尺寸的缩小变得越来越困难，诸如泄漏与性能之间、线宽与波动性之间的折衷必须基于对设计、器件和组装的细心考虑，采取比以前更加审慎的方式进行确定。最后一点是大量且越来越多数的工程师工作在专门从事设计或者组装的公司（也就是那些没有芯片制造设备或硅代工线的公司）。这些工程师要面对各种问题，比那些为集成 IC 公司工作的工程师面临更大的挑战。

现在有许多书专注于硅工艺技术或 IC 设计，但是很少能对当前这两个方面的状态进行全面的综览。本书是对纳米工艺、器件可制造性、先进电路设计和相关的物理实现等方面综合分析，使其更有价值。本书第一部分用 3 章的篇幅对器件和工艺的现状及其未来趋势进行了介绍，第二部分用 6 章的篇幅讲述了设计问题，着重于技术和设计的相互影响，例如信号完整性和互连，以及实际的解决方案。第三部分论述了设计对成品率或可制造性设计的影响。

本书由业界专家撰写，适用于那些需要一本方便而且反映最新发展水平参考书的 IC 设计人员和工艺人员。然而，IC 技术中依然有许多需要开拓的新领域和需要发现的新世界。本书是又一本值得我们随身携带的好书。

CHENMING HU

中国台湾半导体制造公司及加州大学伯克利分校

2004 年 1 月

# 原书前言

1965 年，戈登·摩尔提出了著名的摩尔定律，并成为半导体工业发展的催化剂。今天，如我们所见，半导体工业前进的巨大动力将我们带到了 sub-100nm 时代。这些进步给工艺控制带来许多困难，并随之对电路与物理设计方面也提出了挑战。因此，设计方法的自由度受到了极大的限制，并且对于将芯片集成在一起的途径方面要求进行革命性的变革，使得集成的芯片不仅具有规定的功能，而且要满足设计目标与高成品率要求。

然而，在缺乏制造设施情况下开发的半导体模型的爆炸性增长，导致工艺/器件工程师与电路设计工程师相互隔绝，而且由于受到工艺和器件物理基础的限制，使得电路设计工程师对于自己的设计给可制造性、成品率和性能带来的影响缺乏了解。当我们进入纳米时代时，掌握如何处理这些问题，对产品乃至公司而言都是至关重要的。这几类工程师必须协同工作以弥补彼此知识的欠缺，并且当我们沿着这条工艺尺寸缩小之路前进时，这种知识的欠缺还在不断扩大，只有协同工作才能实现目标。

当我们在工作过程中面对这些问题的时候，我们发现还没有单独的一本书讨论所有这些问题。这些信息以零碎的形式存在，并且大部分存在于专家们的大脑中，其中一部分内容我们已经在工作过程中得到了了解。本书尝试着将这些问题有机地组合成一个整体，讨论它们之间的相互作用以及它们对可制造性、成品率以及性能的影响，给设计者提供实用的指导并帮助设计者克服先进半导体工艺给设计带来的一些困难，同时在物理和电路设计与制造工序、可制造性和成品率之间架设一座迫切需要的桥梁。本书中我们提出的一些概念极其重要，特别是随着工艺不断向纳米 CMOS 特征尺寸技术发展，这些概念的重要性更加显现出来。

本书分为三个部分。第一部分详细描述了深亚微米工艺，以帮助设计者理解与之相关的问题，并且使他们深入了解尺寸缩小带来的限制。第二部分总结分析了工艺缩小对电路设计和物理实现的影响。最后一部分主要着重于可制造性和成品率方面的问题，进而提供指导，以确保设计的器件是可制造的，并且满足成品率和性能目标。

第 1 章总结分析了在深亚微米工艺中设计者所面对的问题，并介绍了本书其余部分的架构。第一部分还包括第 2、3 两章。第 2 章总结分析了 90nm 以及更小尺寸工艺中（管芯工序）（FEOL）和（组装工序）（BEOL）工序系统的当前状态并展望了未来可能的解决方案。FEOL 部分阐述了栅介质和应变工程的发展，包

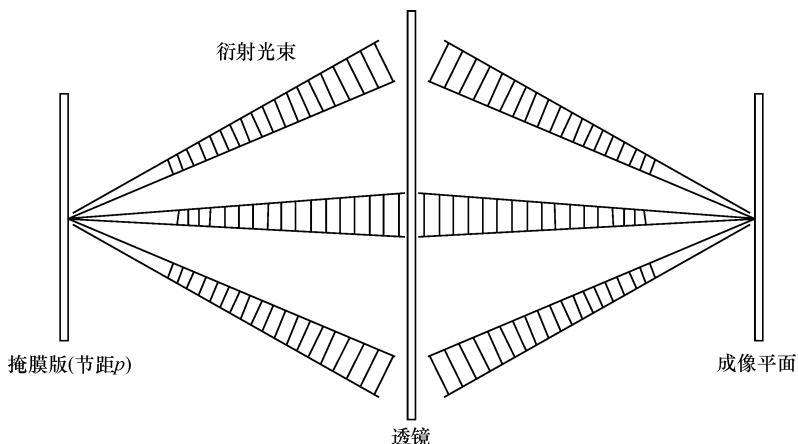

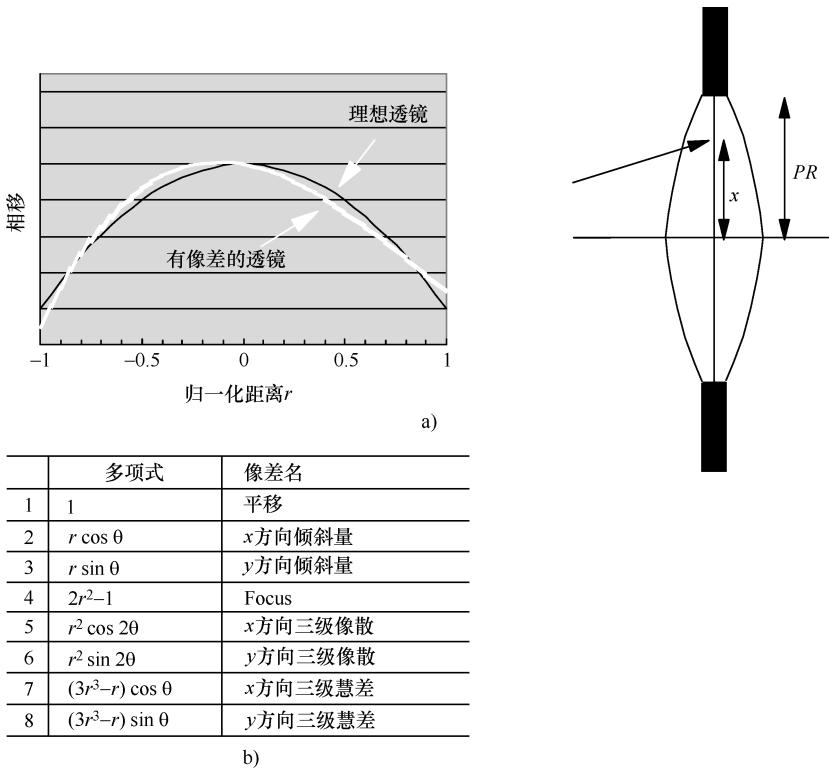

括相关的设备问题，并且深入讨论了 CMOS 尺寸缩小中遇到的问题，如栅隧穿和 NBTI 等。BEOL 部分讨论了局部和全局互连缩小、铜互连线开发、低  $k$  介质的挑战、以及集成方案（如双镶嵌工艺）。第 3 章是从物理与理论基础方面介绍光刻的内容，包括了与先进工艺和相应解决方案有关的问题。

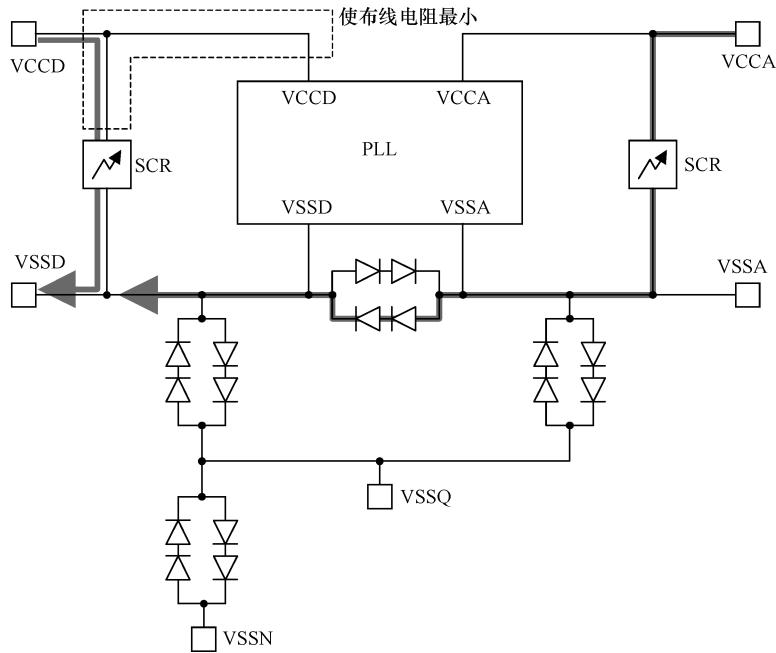

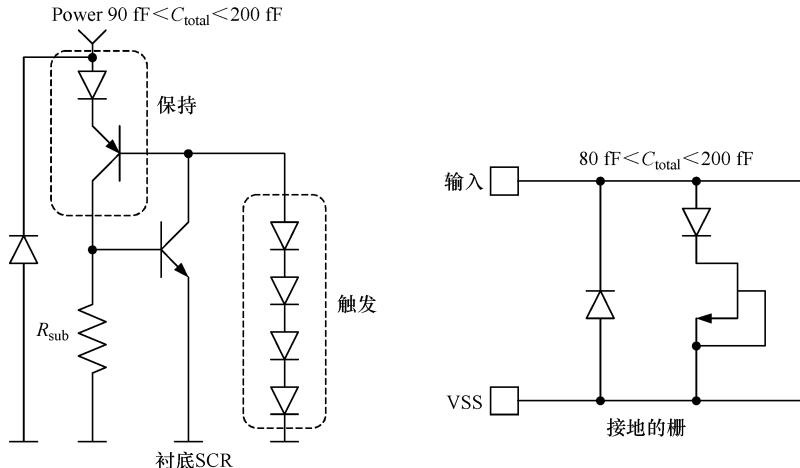

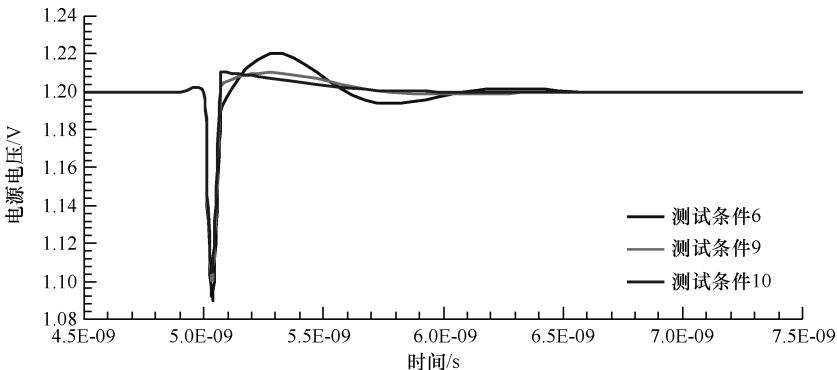

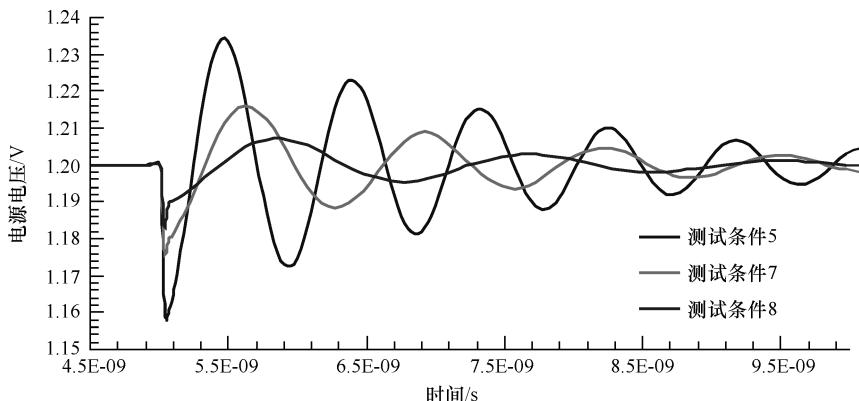

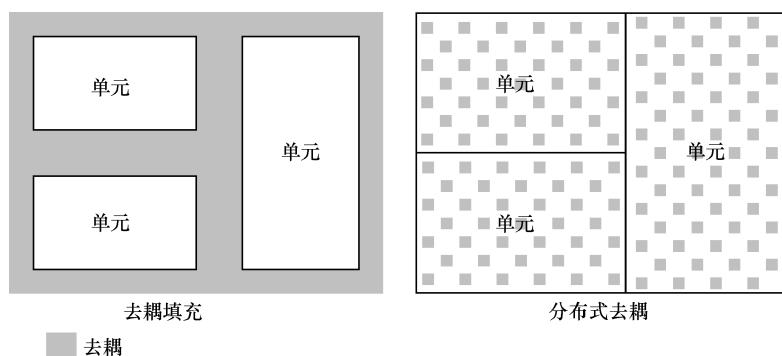

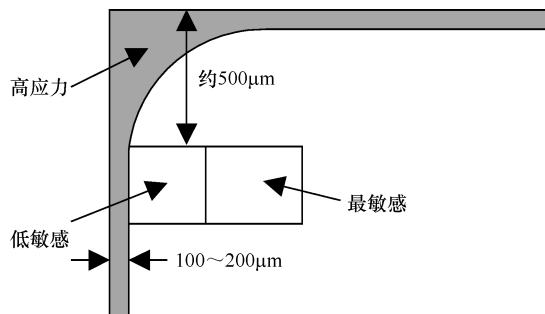

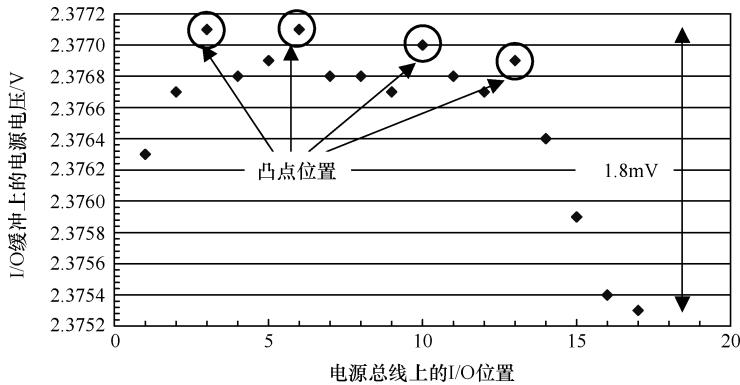

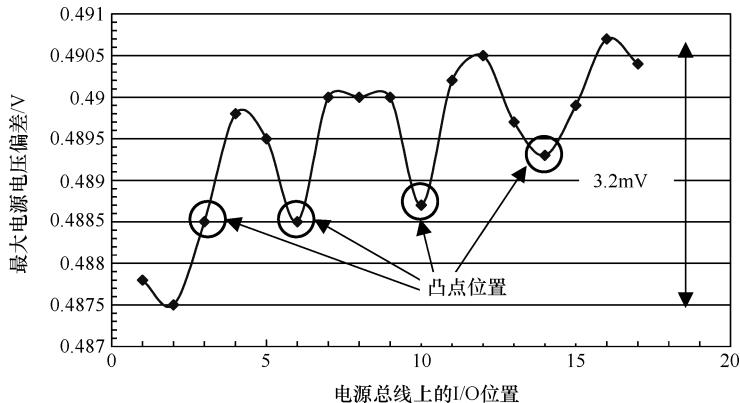

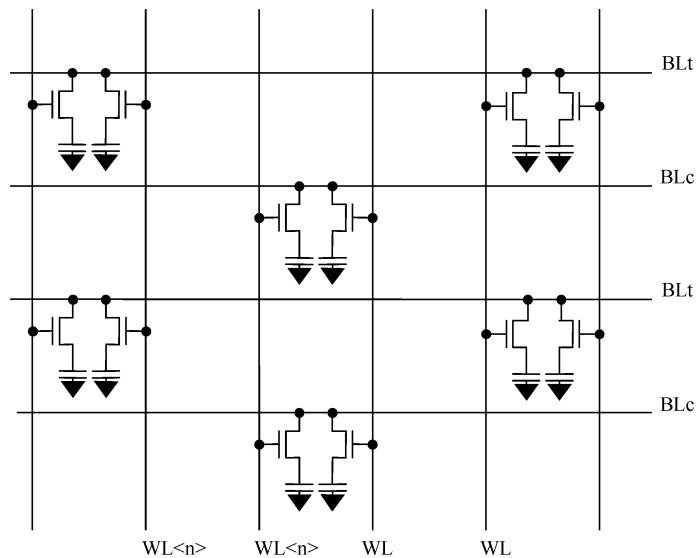

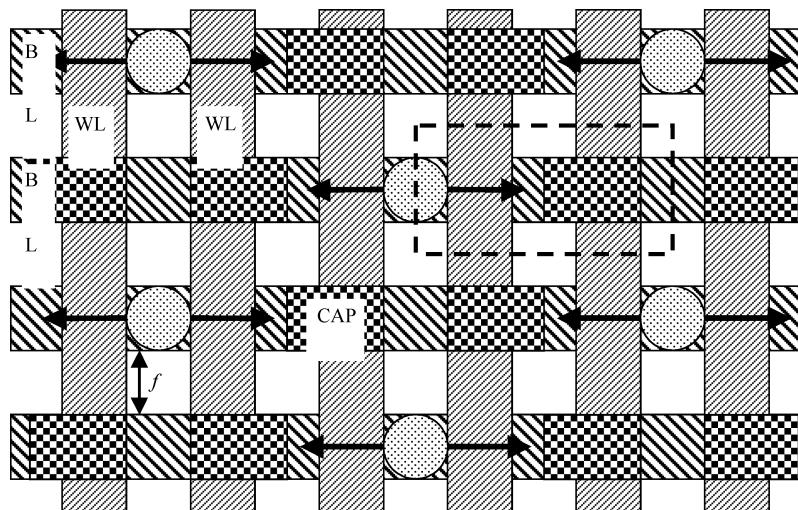

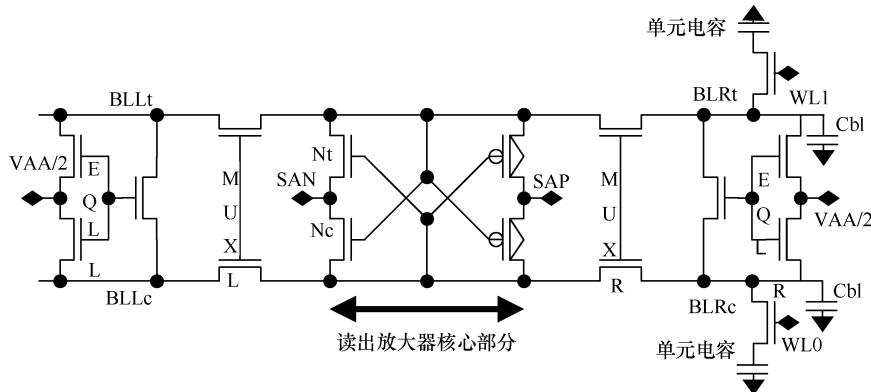

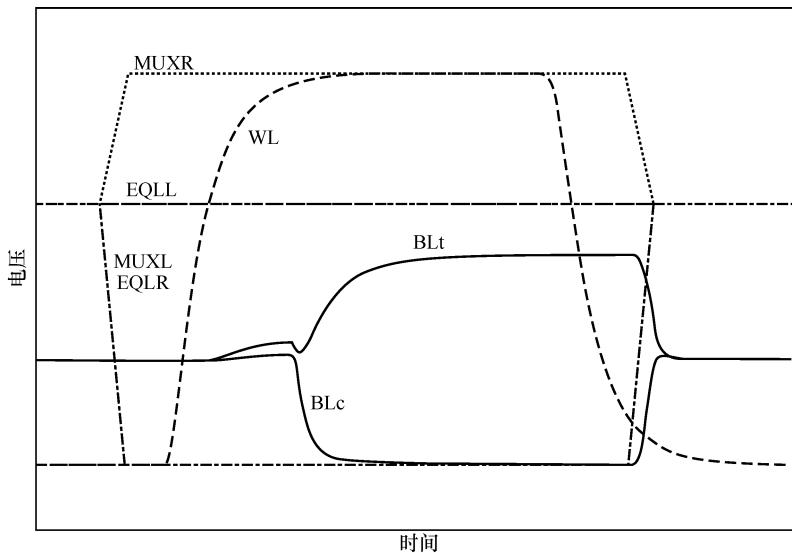

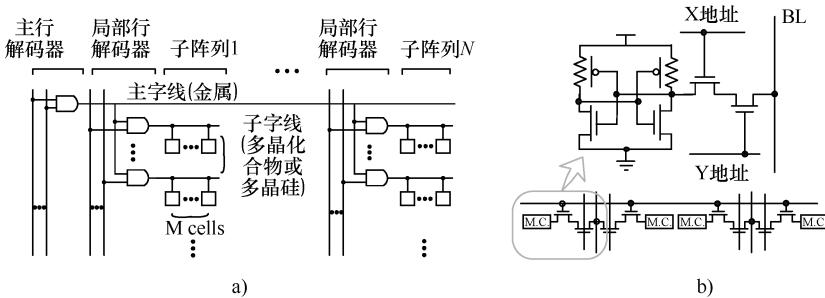

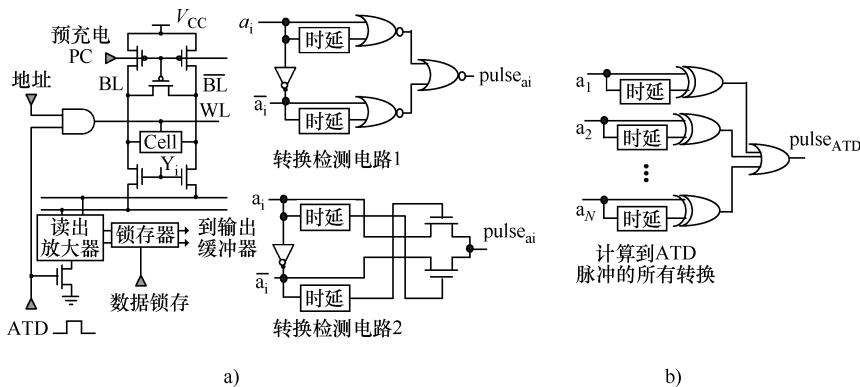

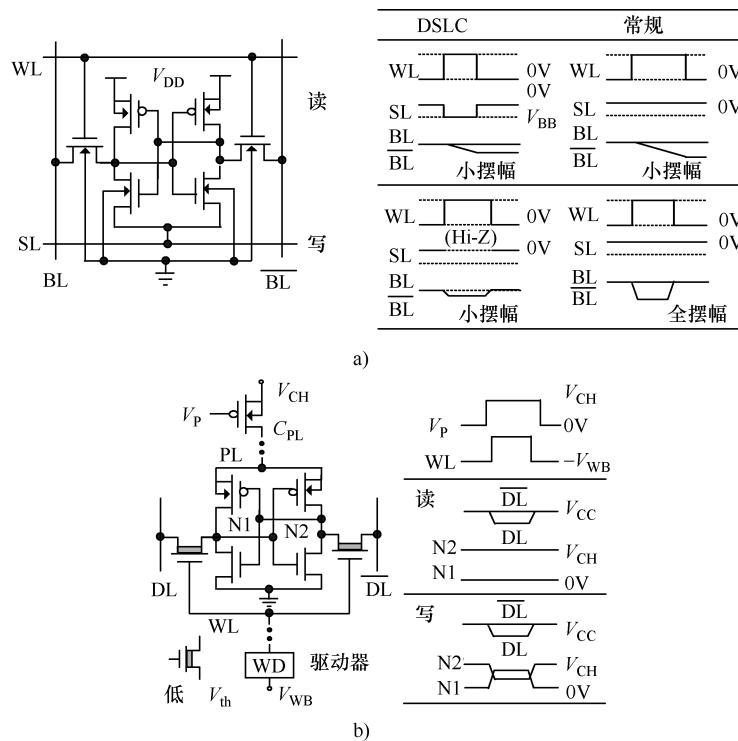

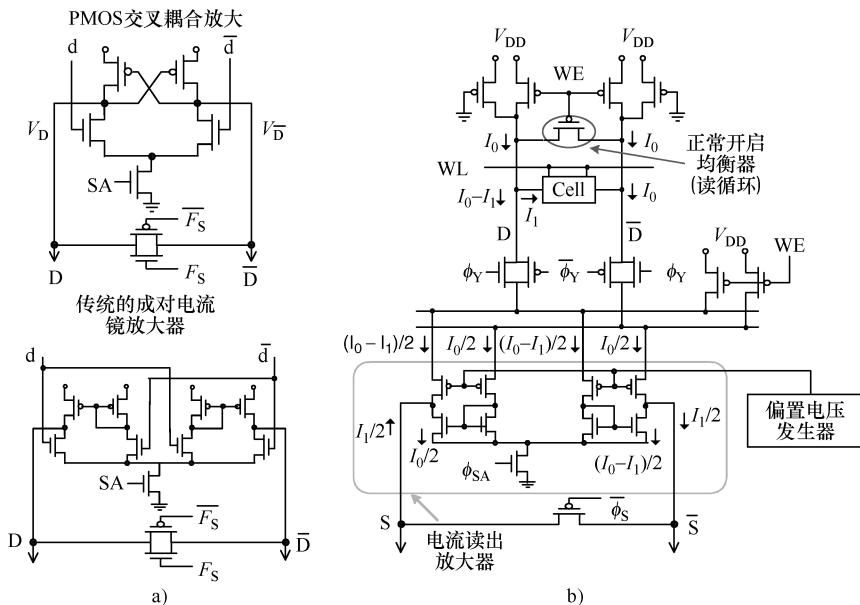

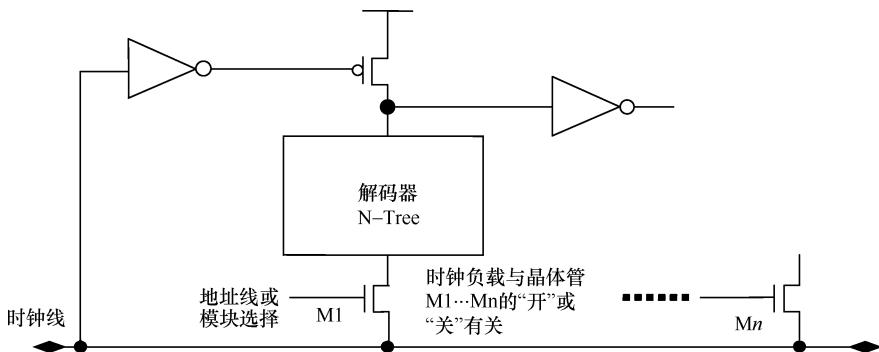

第二部分包括第 4~9 章，共 6 章。第 4 章简要总结分析了混合信号电路面临的设计问题，并对于如何克服先进工艺下电路设计所遇到的困难提供指导。第 5 章分析了设计者在一个芯片上构建一个复杂系统时面临的 ESD 问题。对于多电源保护一类问题也进行了详细的阐述，从而使设计者具备对特殊的 ESD 要求进行估计的能力。作为发展中的另一种 ESD 保护策略，对最新的 SCR 结构也进行了介绍。第 6 章介绍了 I/O 缓冲器设计的最新发展趋势，并且总结分析了各种 I/O 规范以及当前在设计实现方面的发展趋势。对电源总线问题和同步开关噪声问题进行了详细的讨论，说明了预先开发 I/O 电源总线方案的重要性。另外，还详细的讨论了对晶片上的去耦问题，因为片上去耦问题正成为满足高速接口规范的一个关键问题。第 7 章介绍了 DRAM 设计基础，然后进一步说明了在纳米 CMOS 工艺下成功地实现存储电容、存取晶体管和读出放大器等比例缩小所涉及的相关技术。第 8 章着重于信号完整性分析和片上互连的设计解决方案。首先，介绍了寄生参数的高效提取技术，并特别强调电感的问题。接着讨论了信号时序、串扰噪声和波形完整性分析的分析方法。本章最后探讨了改善高速信号的信号完整性的物理和电路设计解决方案。第 9 章对现有系统设计的各个级别在设计阶段和运行阶段采用的低功耗设计技术进行了全面的讨论，着重阐述了电路级的逻辑和存储器设计方法。第 9 章的最后对未来 90nm 工艺节点以后的超低功耗设计技术进行了展望。

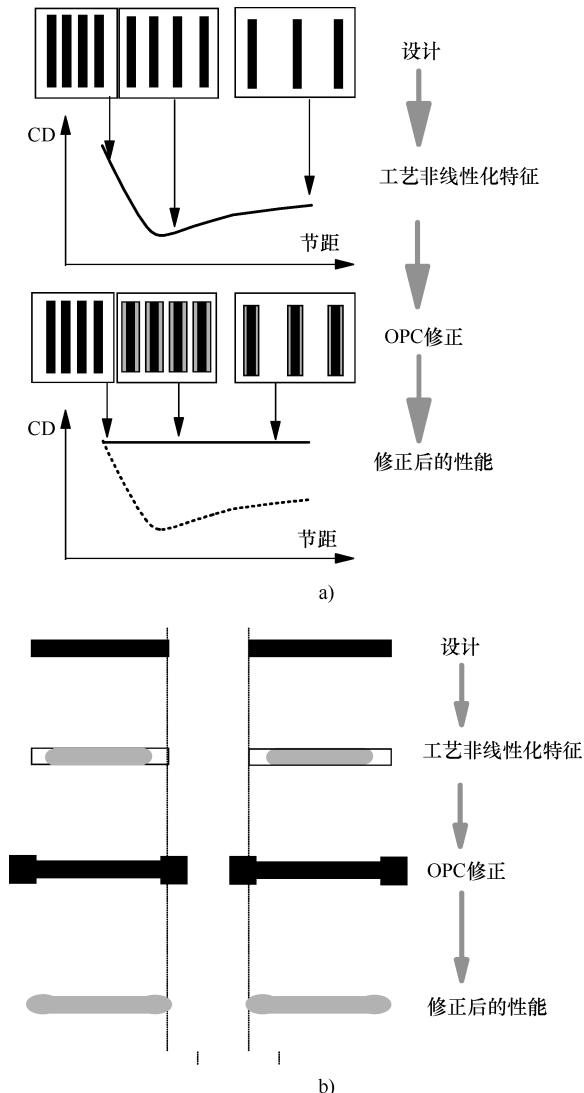

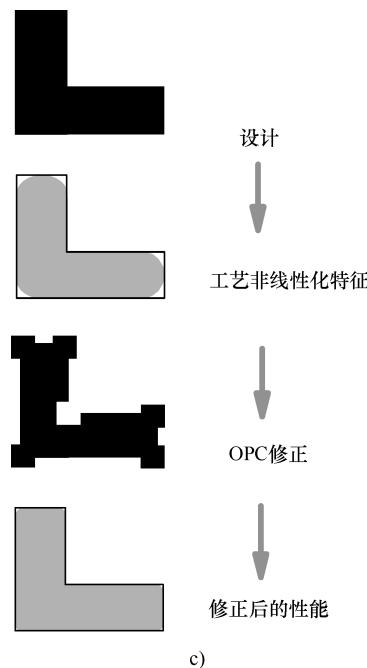

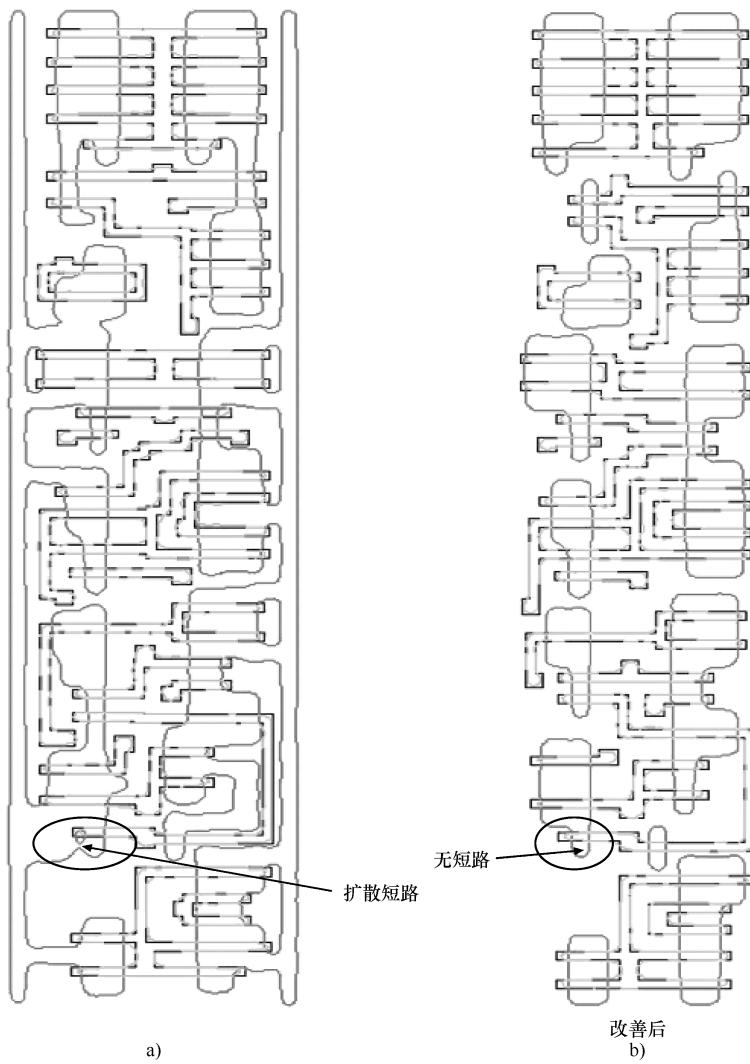

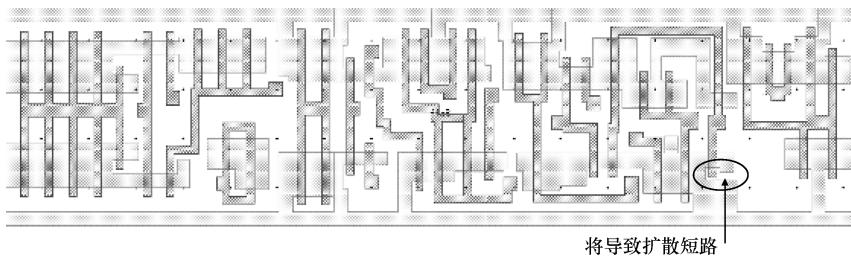

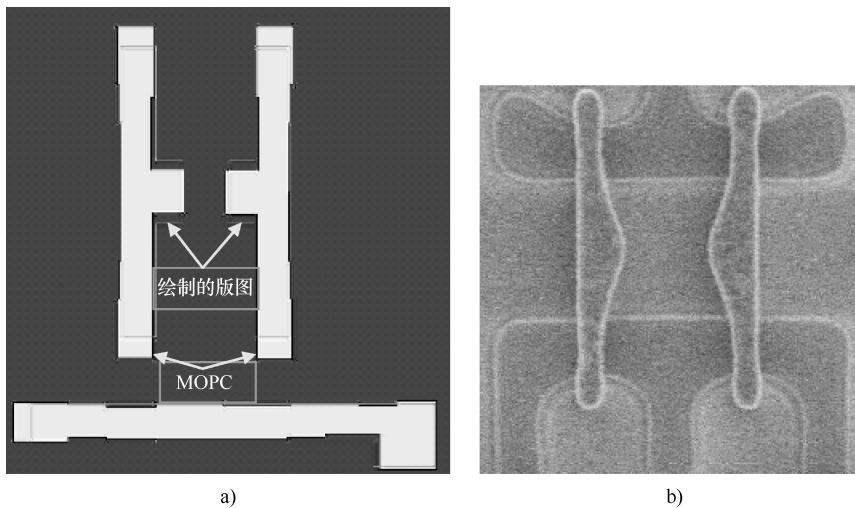

第三部分包括第 10、11 章。第 10 章对实现可制造性设计给出了指导，并给出了多个实例，包括 OPC 后仿真，说明了将电路转换为物理版图时可能出现的问题以及改善的方法。第 11 章介绍了无论工艺如何变化，实现鲁棒且高性能设计的一些原则。本章首先分析了来自工艺和其他方面的各种波动，并讨论了这些波动对电路功能和性能的影响。选用三个主要设计领域（时钟、SRAM 和选定的数字电路）作为案例来说明这些原则。本章还包括了易于进行可制造性设计的指导原则。本章最后简要分析了在纳米 CMOS 设计中对器件统计模型的需求，并简要描述了 BSIM4 模型所具有的新特点。

## 致谢

我们要对许多为本书的完成做出贡献的人们表示感谢。首先，我们要感谢那些撰写了本书部分章节的学科专家们。我们感谢应用材料公司的工艺专家们——Reza Arghavani、Faran Nouri 与 Gary Miner 先生——感谢他们对前道工序的设备

要求部分所做的贡献。我们要感谢应用材料公司的 Khaled Ahmad 先生，他提供了第 2 章前道工艺部分采用的氧化层特性方面的数据。我们要感谢加利福尼亚大学伯克利分校的工艺专家 Qiang Lu 先生，他目前就职于 AMD 公司，感谢他对 FEOL 章节的贡献。我们也要感谢 IBM 微电子的光刻专家 Franz Zach 先生，感谢他关于第 3 章中纳米 CMOS 阶段的光刻技术介绍。对第 5 章，我们要感谢被公认为这方面主题的权威——中国台湾大学的 Ming-Dou Ker 教授。我们要感谢英飞凌公司的存储器权威 Martin Brox 先生对第 7 章的贡献。我们要感谢 Rambus 的 Xuejue Huang 先生对第 8 章的卓越贡献，还要感谢 UC-Berkeley 的 Huifang Qin 先生，他撰写了第 9 章的大部分内容，并且将作者的工作整合到本章中。

我们还要感谢 Altera 公司对本书的支持，特别是 Wanli Chang、William Hwang、KangWei Lai、Richard Chang、Leon Zheng、Mian Smith 和 Howard Kahn 先生，感谢他们的仿真工作。我们感谢 Cynthia P. Tran 先生提供了作为本书中插图的物理版图以及光刻仿真的输入。我们感谢 John Madok 和 Michael Smayling 先生，他们协助推荐应用材料的专家撰写本书中的部分章节并担任顾问。

我们十分感谢 Trecenti/Hitachi 公司的 Shuji Ikeda 先生，NEC 公司的 Ryuichi Hashishita、Yashushi Yamagata 和 Toshiaki Hoshi 先生；AMD 公司的 Richard Klein 和 Qiang Lu 先生，感谢他们提供了本书中使用的技术数据和多幅 SE 和 TE 显微照片。我们感谢 ASML Masktools 公司的 Fung Chen、Armin Liebchen 和 Sabita Roy 先生，感谢他们在光刻仿真以及提供仿真工具用来产生作为插图的仿真光刻胶剖面的俯视图。

我们感谢英国哥伦比亚大学的 Mark Greenstreet 教授，他审阅了本书的编写提纲并给出了许多有价值的建议。最后，我们表示对 Chenming Hu 教授的感谢，感谢他提出的卓有远见的建议以及为本书撰写的序。

## 作 者

# 目 录

译者的话

原书序

原书前言

|                              |    |

|------------------------------|----|

| <b>第1章 纳米 CMOS 的缩小问题及内涵</b>  | 1  |

| 1.1 纳米 CMOS 时代的设计方法          | 1  |

| 1.2 使得性能改善得到延续所必需的创新         | 3  |

| 1.3 sub-100nm 缩小的挑战和亚波长光刻综述  | 5  |

| 1.3.1 后道工艺的挑战（金属化）           | 5  |

| 1.3.2 前道工艺的挑战（晶体管）           | 10 |

| 1.4 工艺控制和可靠性                 | 13 |

| 1.5 光刻问题和掩膜数据爆炸              | 14 |

| 1.6 新型的电路和物理设计工程师            | 15 |

| 1.7 建模的挑战                    | 16 |

| 1.8 变革设计方法的需要                | 17 |

| 1.9 总结                       | 19 |

| 参考文献                         | 19 |

| <b>第2章 CMOS 器件与工艺技术</b>      | 22 |

| 2.1 前道工序的设备要求                | 22 |

| 2.1.1 技术背景                   | 22 |

| 2.1.2 栅介质的缩小                 | 24 |

| 2.1.3 应变工程                   | 28 |

| 2.1.4 快速热处理技术                | 30 |

| 2.2 在 CMOS 尺寸缩小中与前道工序相关的器件问题 | 36 |

| 2.2.1 CMOS 缩小的挑战             | 36 |

| 2.2.2 量子效应模型                 | 38 |

| 2.2.3 多晶硅栅耗尽效应               | 40 |

| 2.2.4 金属栅电极                  | 42 |

| 2.2.5 栅直接隧穿泄漏电流              | 43 |

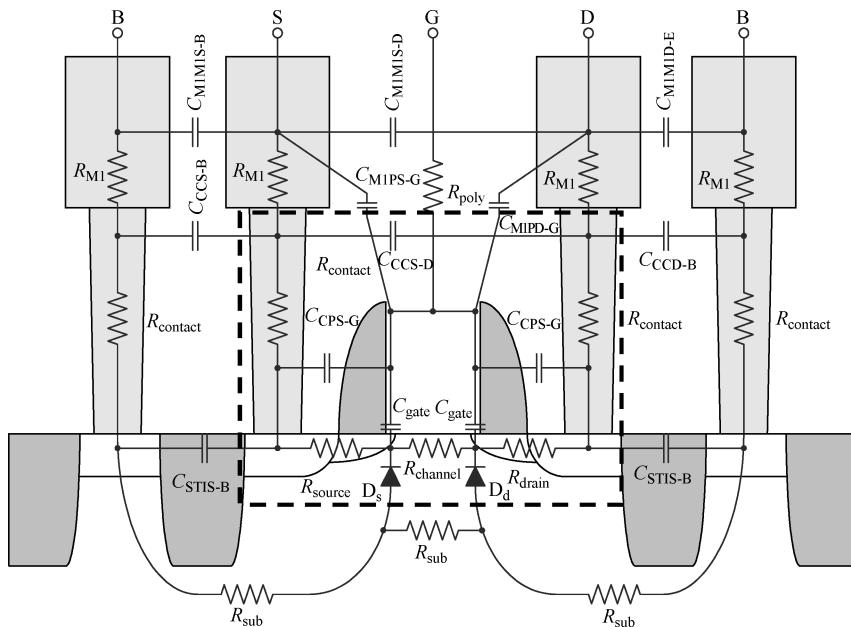

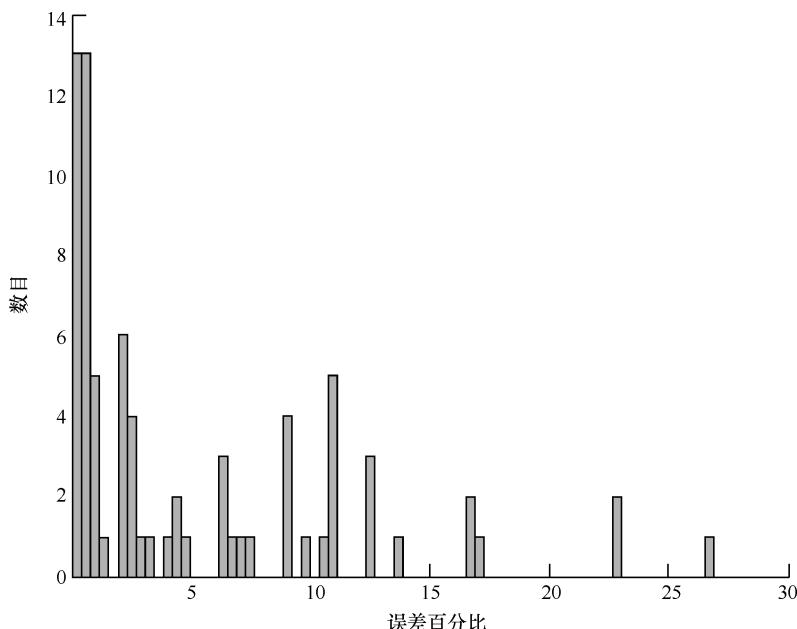

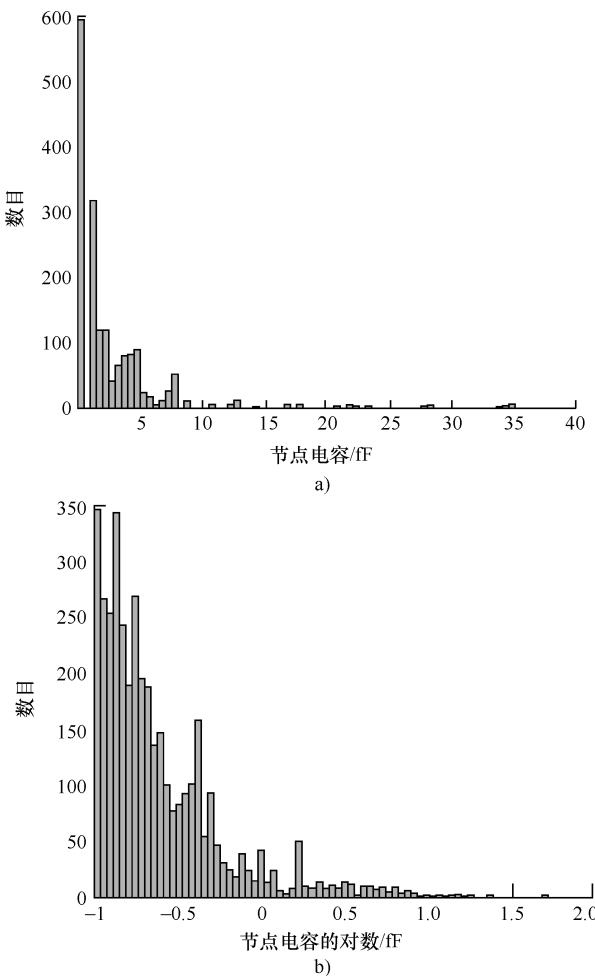

| 2.2.6 寄生电容                   | 45 |

| 2.2.7 需要关注的可靠性问题             | 48 |

| 2.3 后道工序互连线技术                | 50 |

---

|                                    |            |

|------------------------------------|------------|

| 2.3.1 互连缩放 .....                   | 51         |

| 2.3.2 铜互连技术 .....                  | 52         |

| 2.3.3 低 $k$ 介质的挑战 .....            | 54         |

| 2.3.4 未来的全局互连技术 .....              | 55         |

| 参考文献 .....                         | 56         |

| <b>第3章 亚波长光刻的理论与实践 .....</b>       | <b>63</b>  |

| 3.1 引言与成像理论概述 .....                | 63         |

| 3.2 对 100nm 节点的挑战 .....            | 65         |

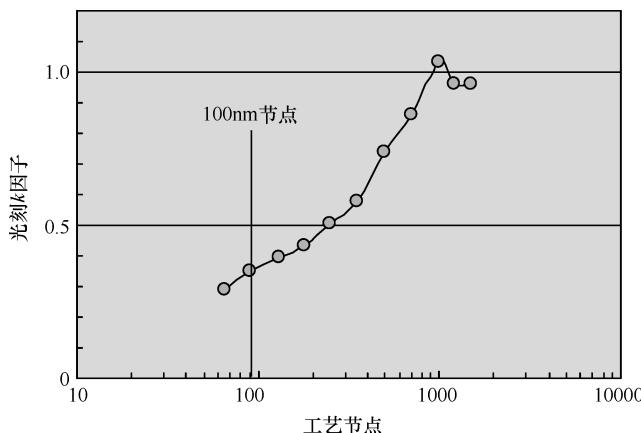

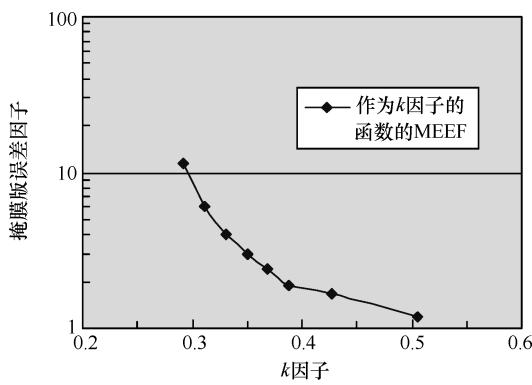

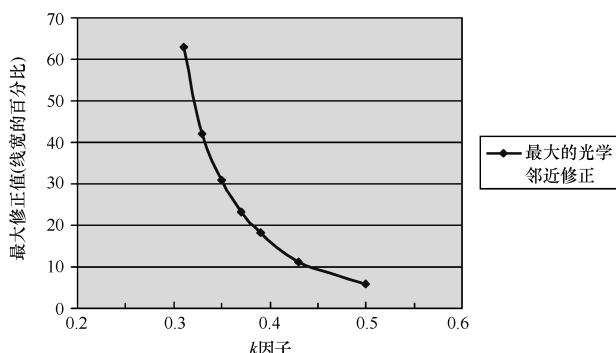

| 3.2.1 100nm 节点的 $k$ 因子 .....       | 65         |

| 3.2.2 重要的工艺波动 .....                | 67         |

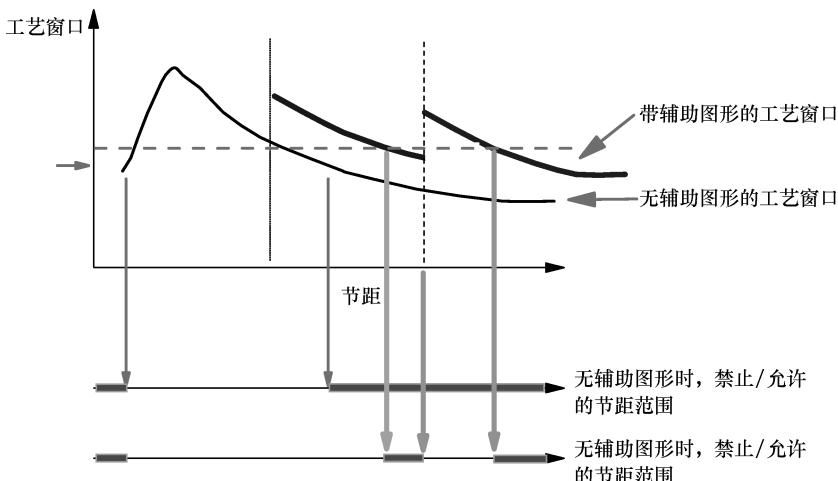

| 3.2.3 低 $k$ 成像对工艺敏感性的影响 .....      | 70         |

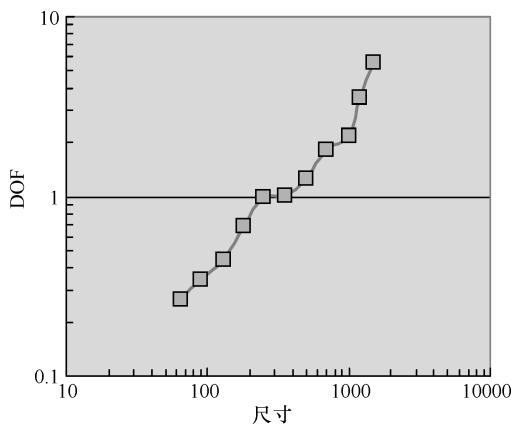

| 3.2.4 低 $k$ 成像和聚焦深度的影响 .....       | 71         |

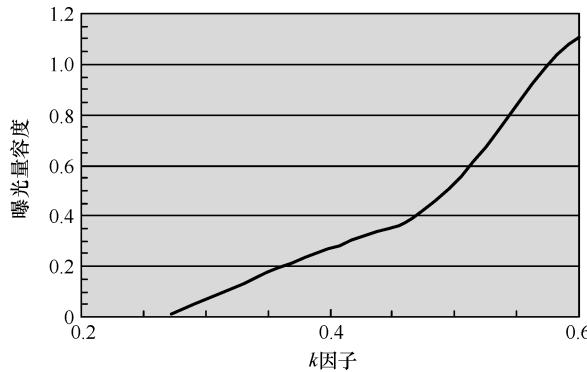

| 3.2.5 低 $k$ 成像和曝光容限 .....          | 71         |

| 3.2.6 低 $k$ 成像及其对掩膜误差增强因子的影响 ..... | 72         |

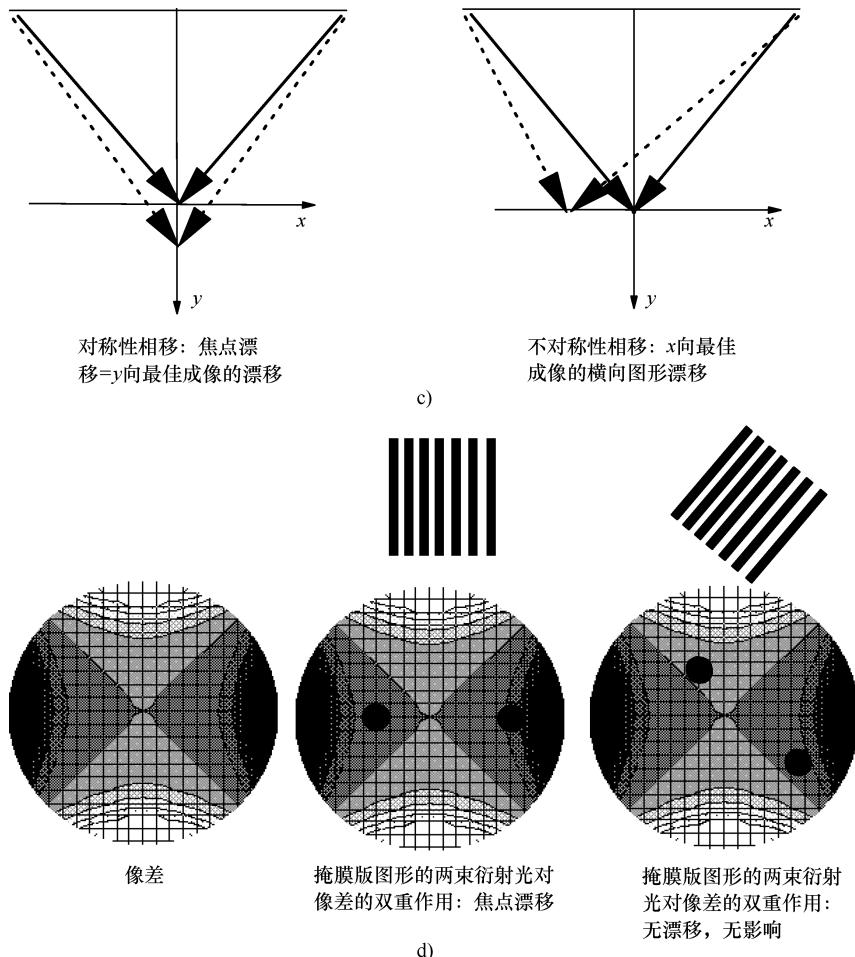

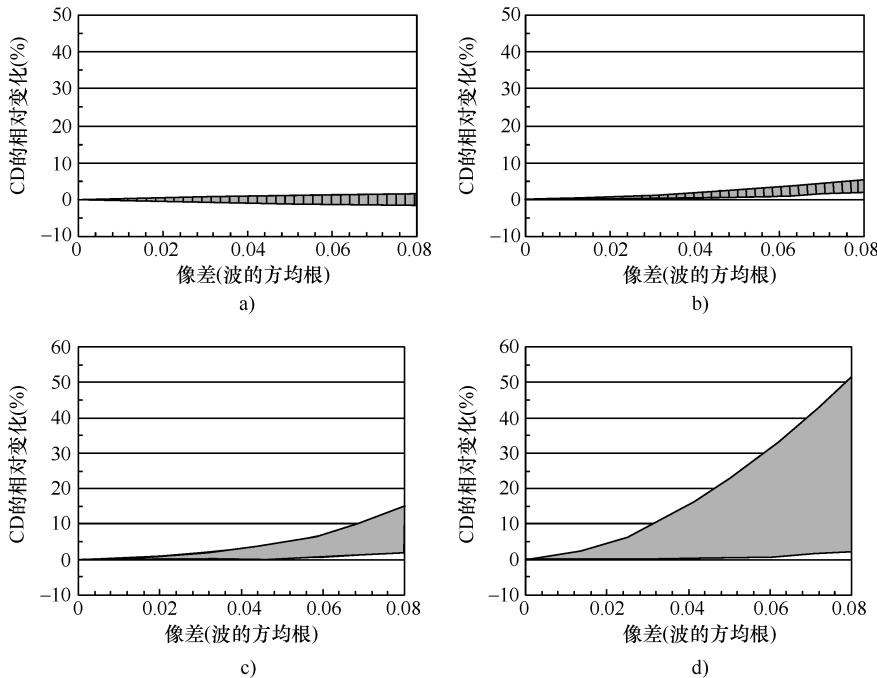

| 3.2.7 低 $k$ 成像及其对像差的敏感性 .....      | 73         |

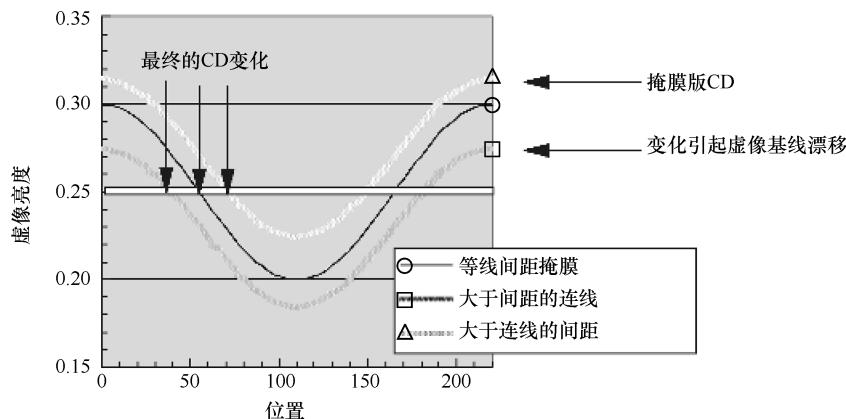

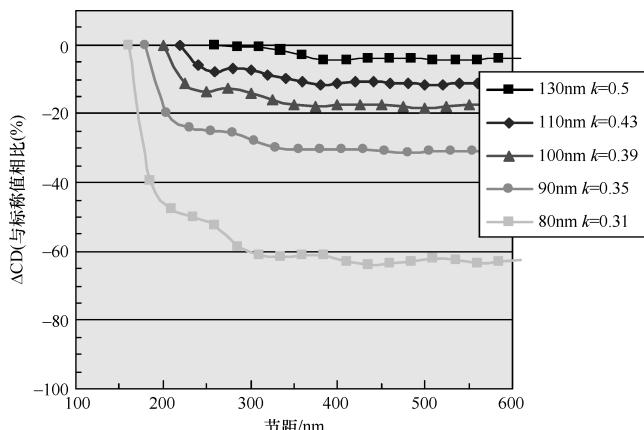

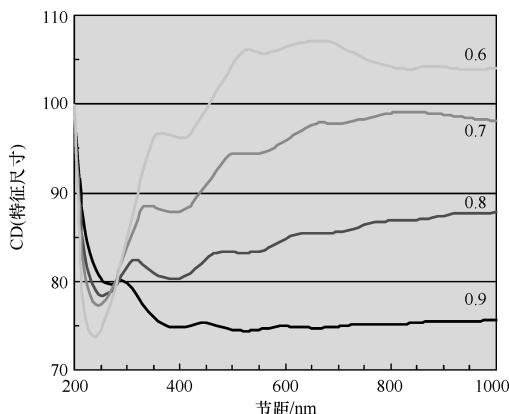

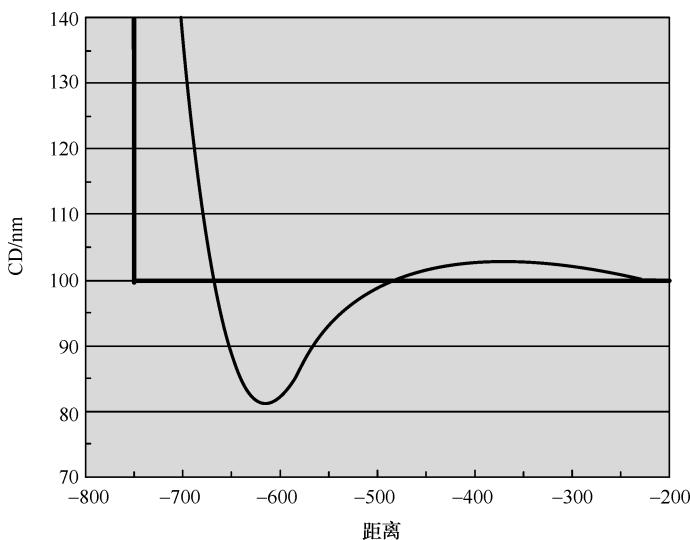

| 3.2.8 低 $k$ 成像以及 CD 变化与条宽的关系 ..... | 74         |

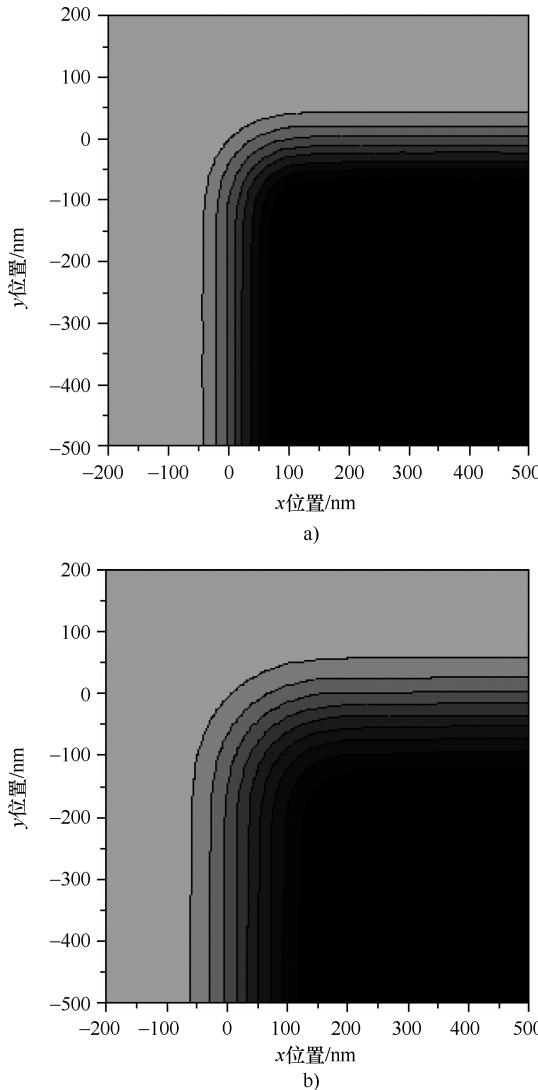

| 3.2.9 低 $k$ 成像和拐角处的圆角半径 .....      | 76         |

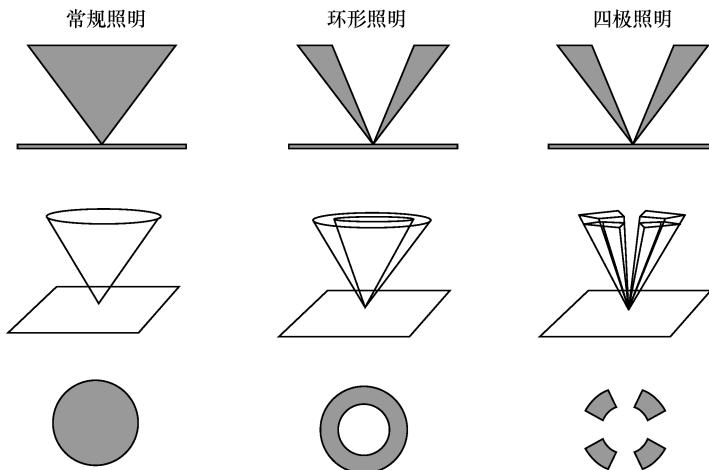

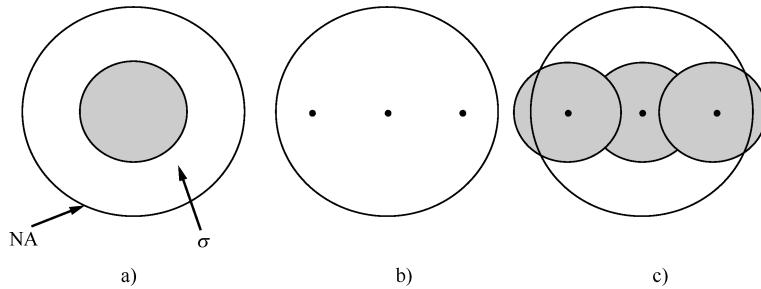

| 3.3 分辨率增强技术：物理 .....               | 78         |

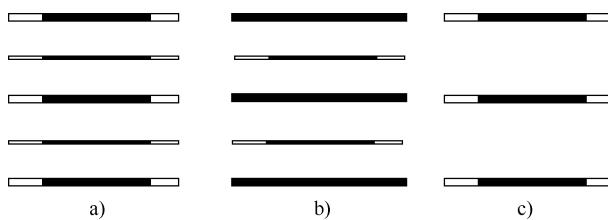

| 3.3.1 专门的照明模式 .....                | 79         |

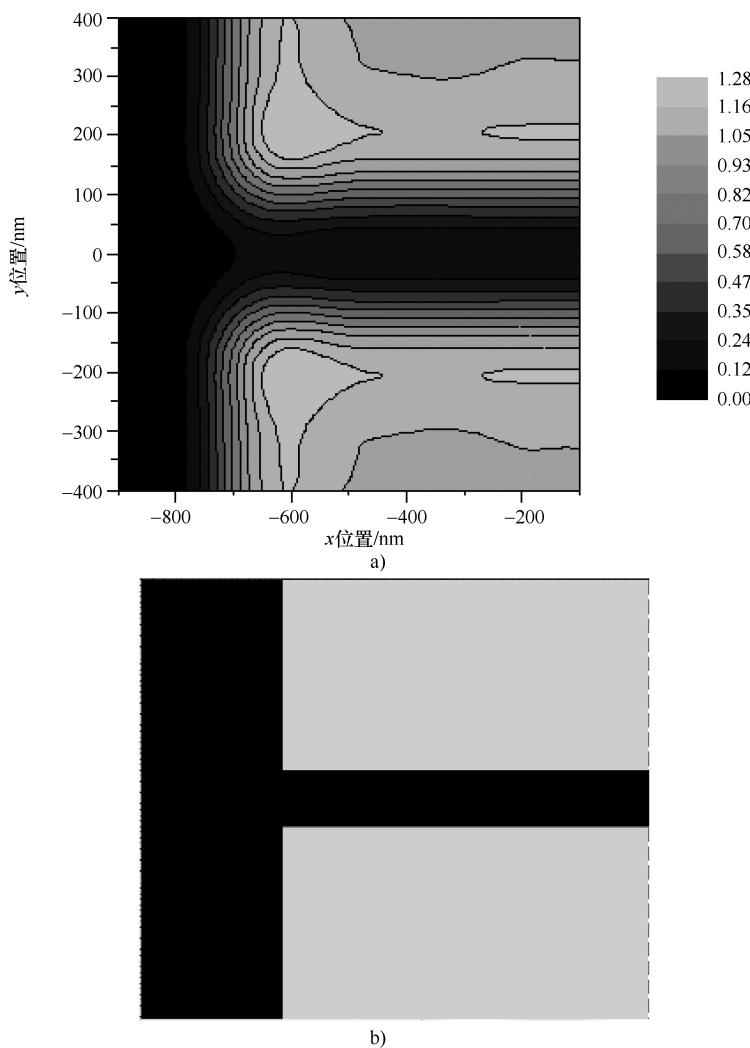

| 3.3.2 光学邻近修正（OPC） .....            | 80         |

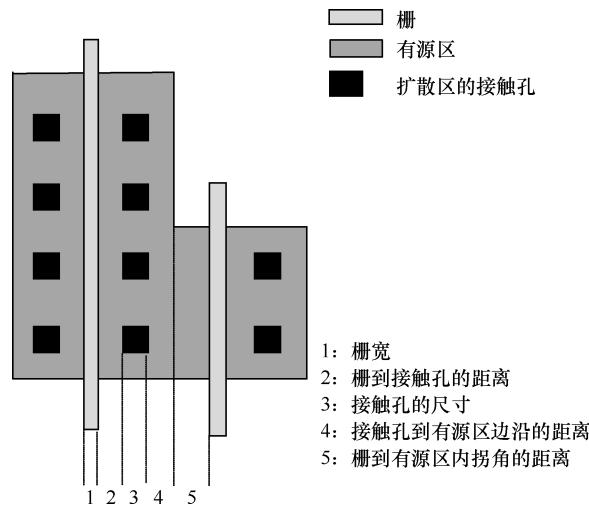

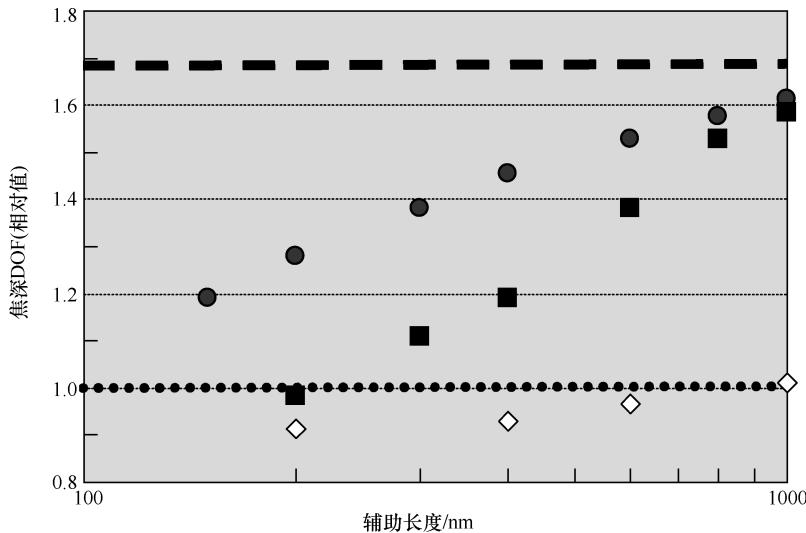

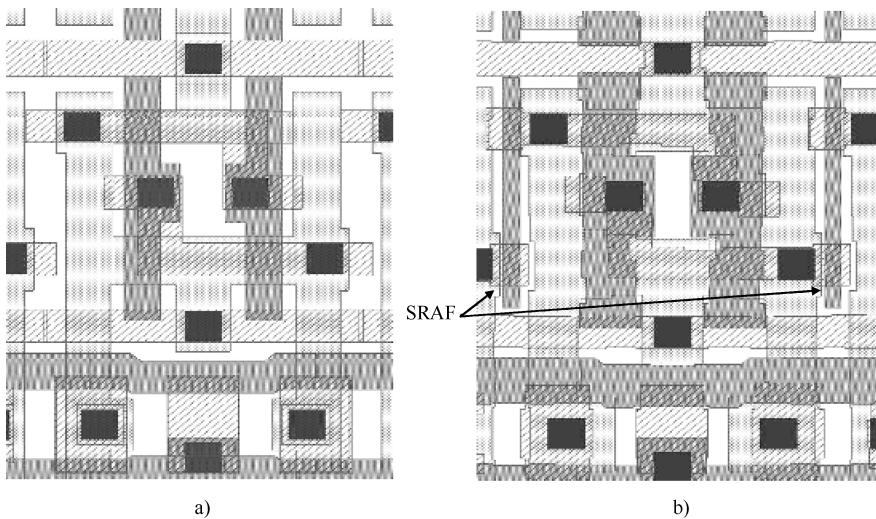

| 3.3.3 亚分辨率辅助图形 .....               | 86         |

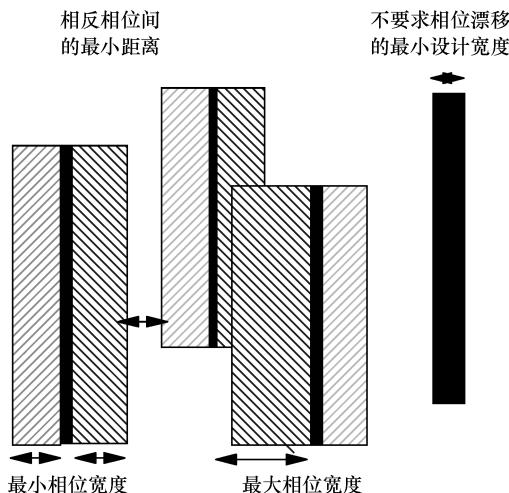

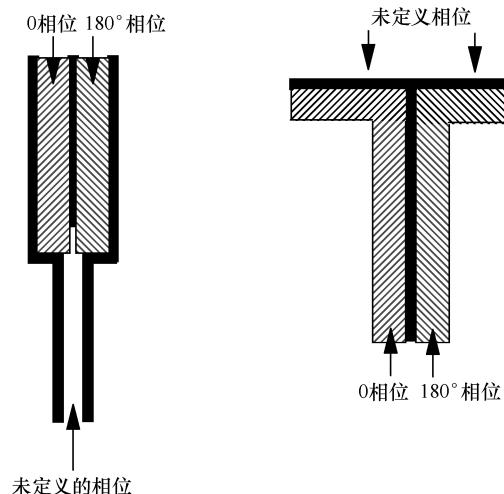

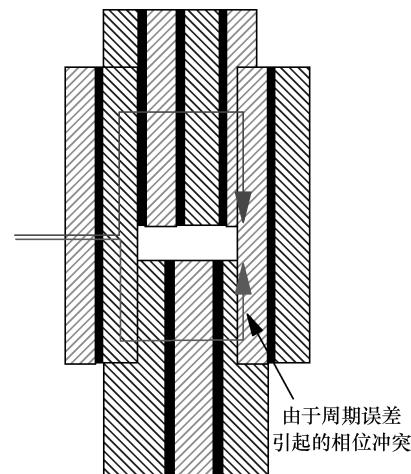

| 3.3.4 交替式相移掩膜 .....                | 88         |

| 3.4 物理设计风格对 RET 和 OPC 复杂性的影响 ..... | 91         |

| 3.4.1 特定照明条件 .....                 | 92         |

| 3.4.2 二维版图 .....                   | 94         |

| 3.4.3 交替式相移掩膜 .....                | 98         |

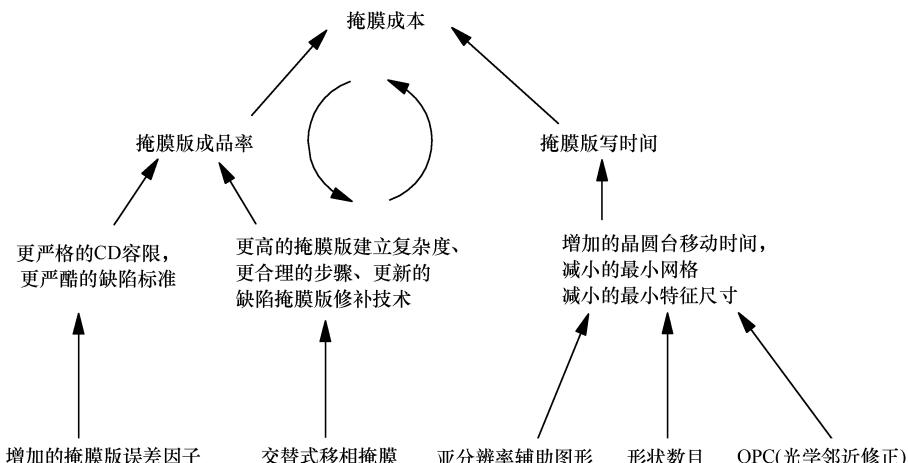

| 3.4.4 掩膜版成本 .....                  | 101        |

| 3.5 发展前景：未来的光刻技术 .....             | 103        |

| 3.5.1 发展之路：157nm 光刻 .....          | 103        |

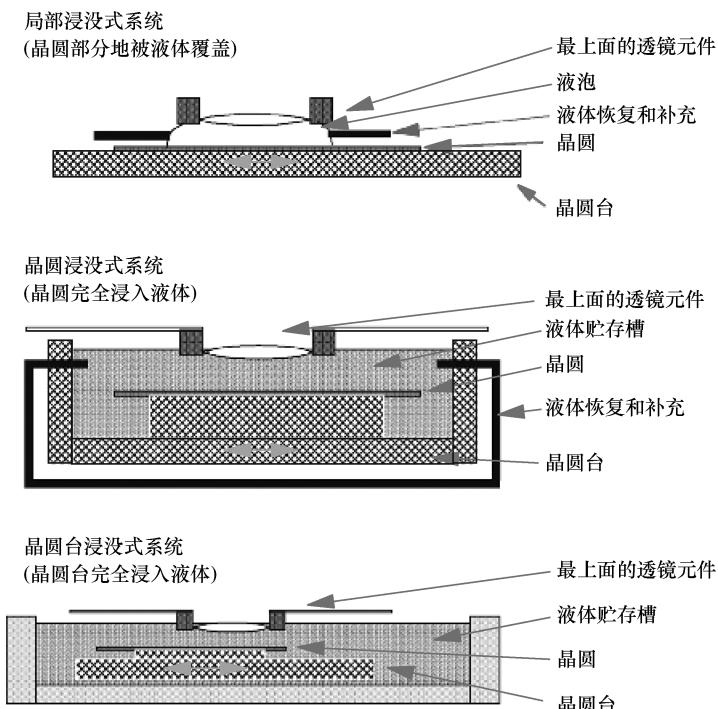

| 3.5.2 进一步演化：浸没式光刻 .....            | 104        |

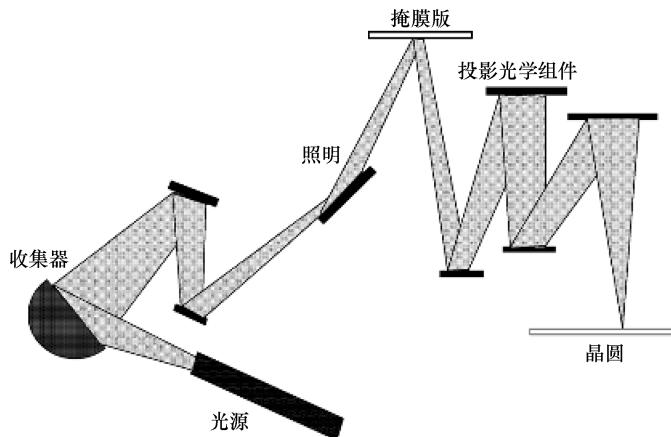

| 3.5.3 巨大突破：EUV 光刻 .....            | 106        |

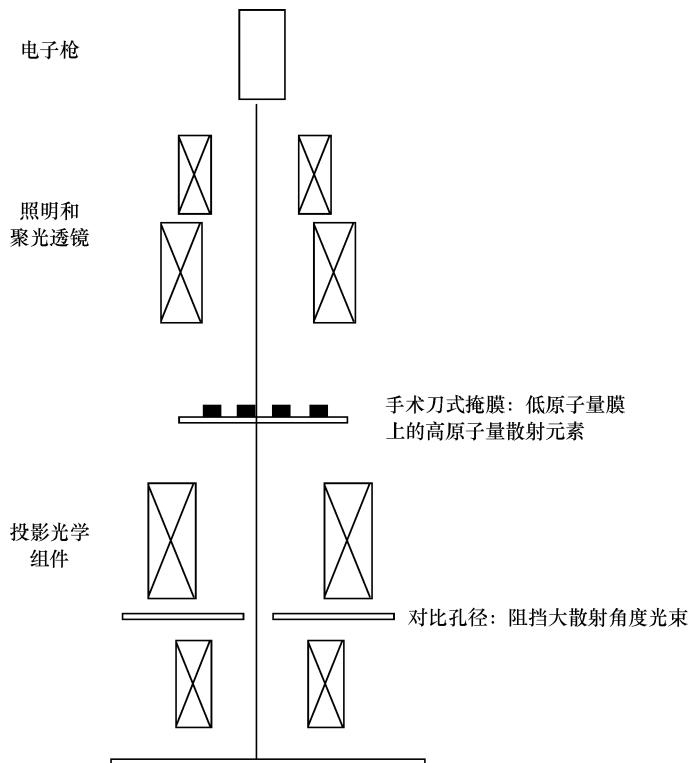

| 3.5.4 粒子束光刻 .....                  | 107        |

| 3.5.5 直写式电子束设备 .....               | 108        |

| 参考文献 .....                         | 111        |

| <b>第4章 混合信号电路设计 .....</b>          | <b>115</b> |

| 4.1 引言 .....                       | 115        |

|                                  |            |

|----------------------------------|------------|

| 4.2 设计考虑 .....                   | 115        |

| 4.3 器件建模 .....                   | 116        |

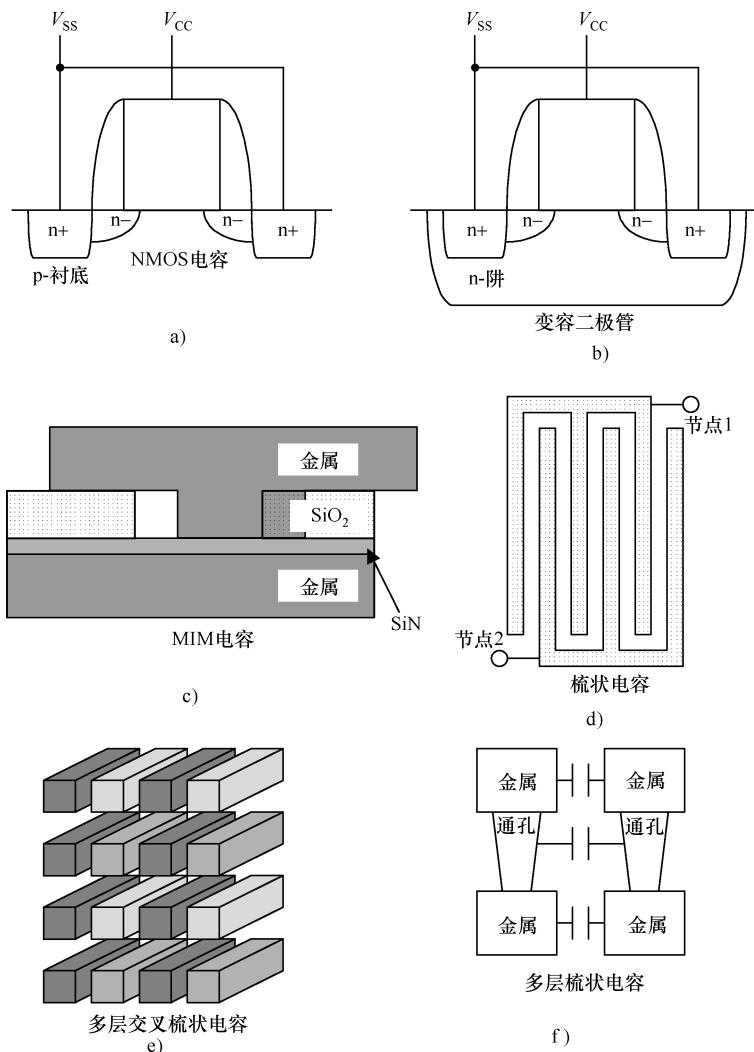

| 4.4 无源器件 .....                   | 122        |

| 4.5 设计方法学 .....                  | 125        |

| 4.5.1 工艺测试基准电路 .....             | 126        |

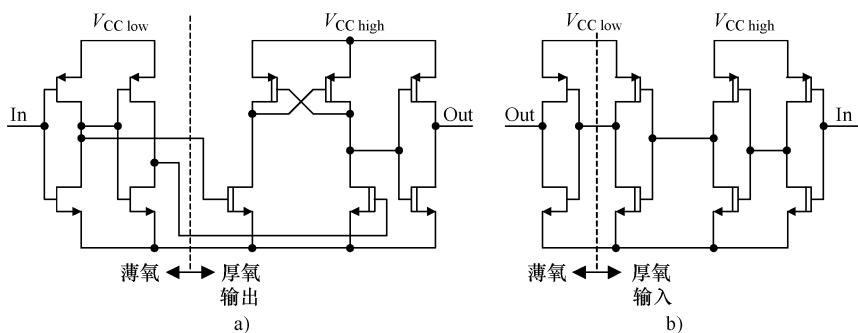

| 4.5.2 薄氧器件设计 .....               | 126        |

| 4.5.3 厚氧器件设计 .....               | 127        |

| 4.6 低压技术 .....                   | 129        |

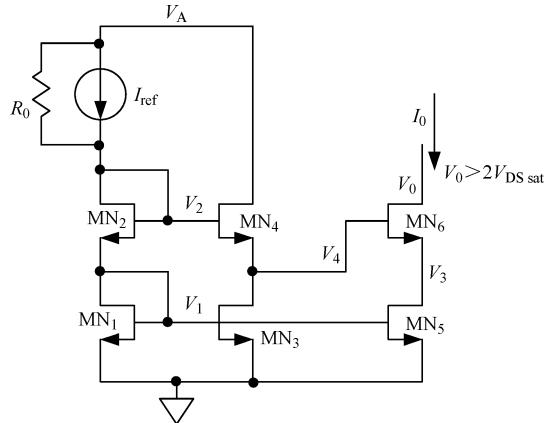

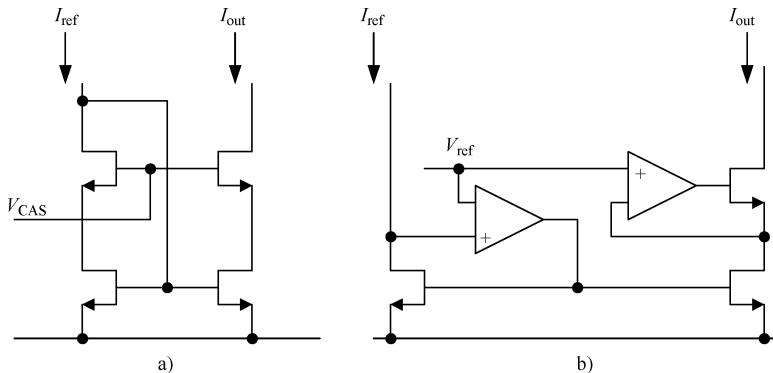

| 4.6.1 电流镜 .....                  | 129        |

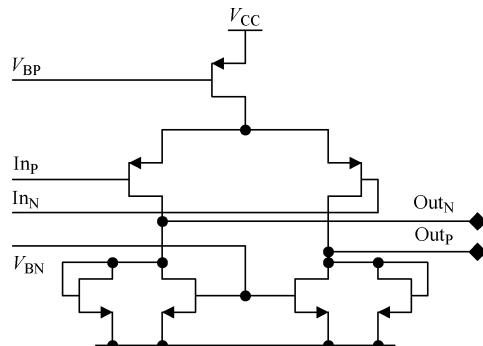

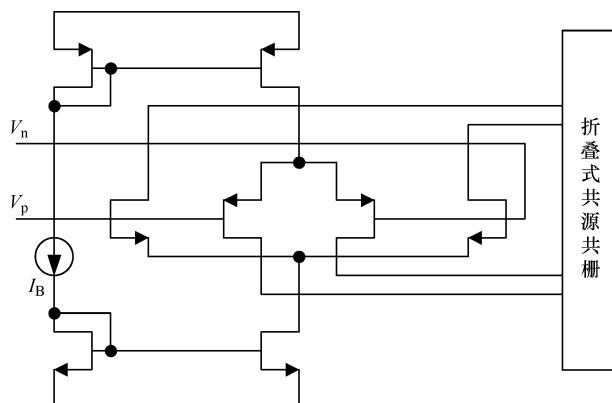

| 4.6.2 输入级 .....                  | 131        |

| 4.6.3 输出级 .....                  | 132        |

| 4.6.4 带隙基准 .....                 | 132        |

| 4.7 设计过程 .....                   | 133        |

| 4.8 静电放电保护 .....                 | 135        |

| 4.8.1 针对多电源情况的考虑 .....           | 136        |

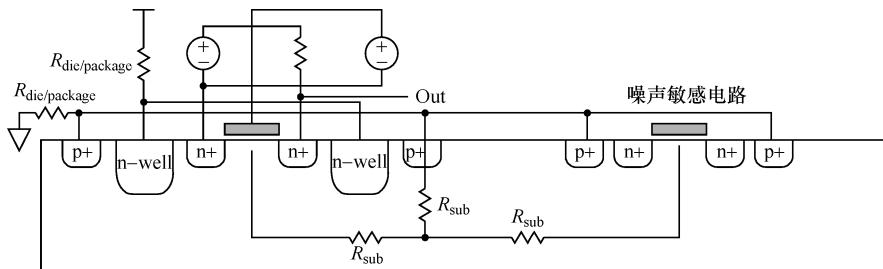

| 4.9 噪声隔离 .....                   | 137        |

| 4.9.1 保护环结构 .....                | 137        |

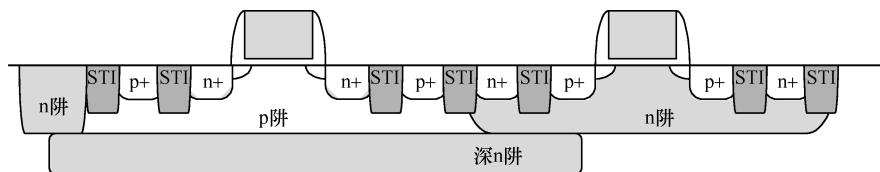

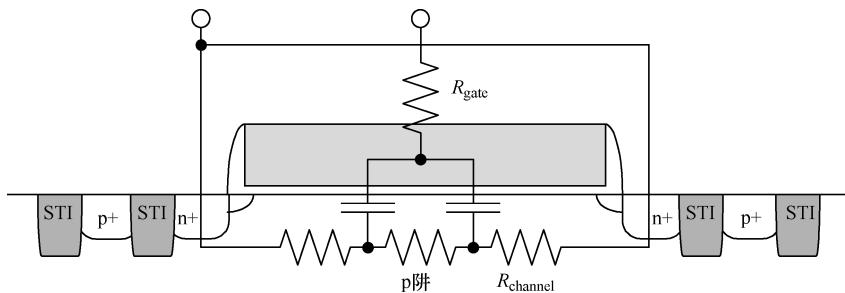

| 4.9.2 隔离的 NMOS 器件 .....          | 139        |

| 4.9.3 外延材料与体硅 .....              | 139        |

| 4.10 去耦 .....                    | 140        |

| 4.11 主电源线 .....                  | 144        |

| 4.12 集成问题 .....                  | 144        |

| 4.12.1 芯片四角区域的影响 .....           | 144        |

| 4.12.2 邻近电路的影响 .....             | 145        |

| 4.13 总结 .....                    | 145        |

| 参考文献 .....                       | 146        |

| <b>第 5 章 静电放电保护设计 .....</b>      | <b>149</b> |

| 5.1 引言 .....                     | 149        |

| 5.2 ESD 标准与模型 .....              | 149        |

| 5.3 ESD 保护设计 .....               | 150        |

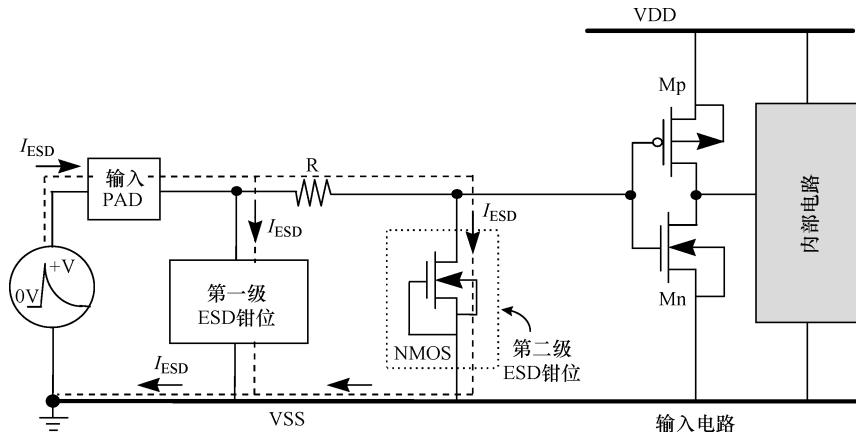

| 5.3.1 ESD 保护方案 .....             | 150        |

| 5.3.2 ESD 保护器件开启的一致性 .....       | 152        |

| 5.3.3 ESD 注入与金属硅化物阻挡 .....       | 153        |

| 5.3.4 ESD 保护指导意见 .....           | 154        |

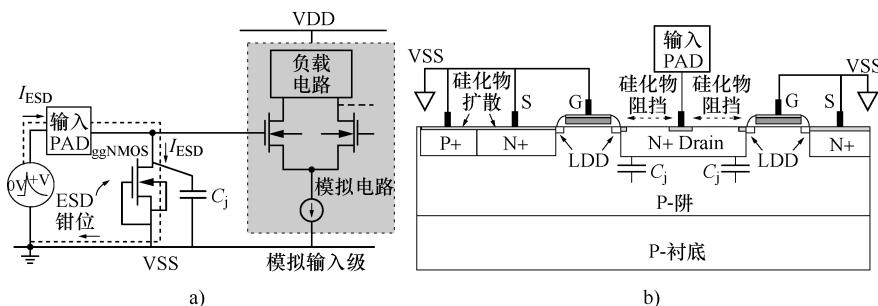

| 5.4 针对高速 I/O 的低电容 ESD 保护设计 ..... | 154        |

| 5.4.1 高速 I/O 或模拟引脚的 ESD 保护 ..... | 154        |

---

|                                       |            |

|---------------------------------------|------------|

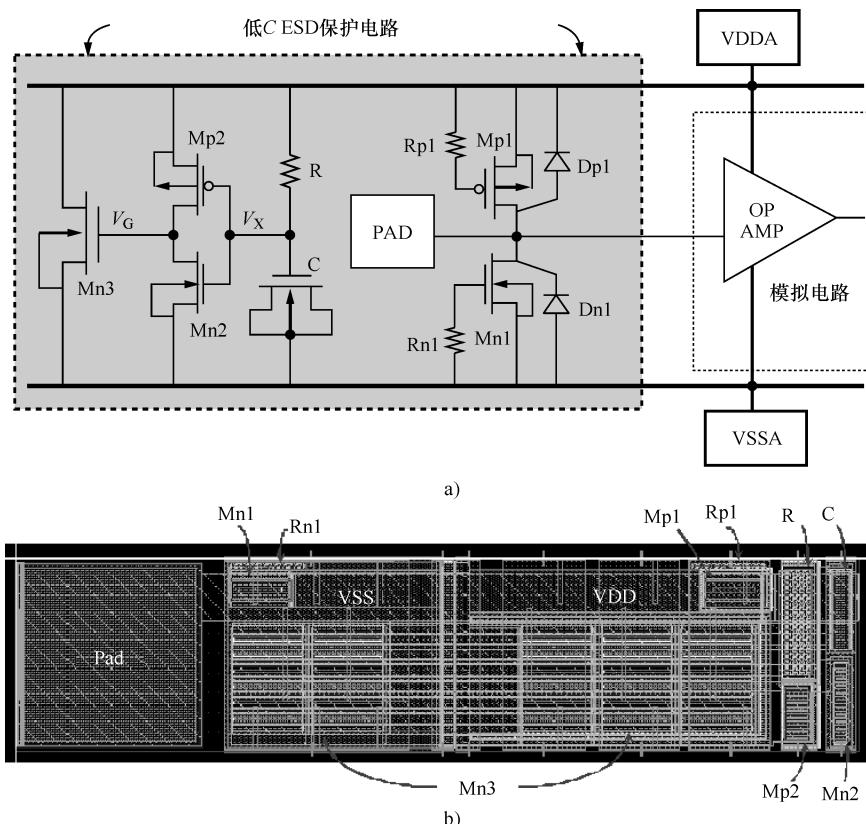

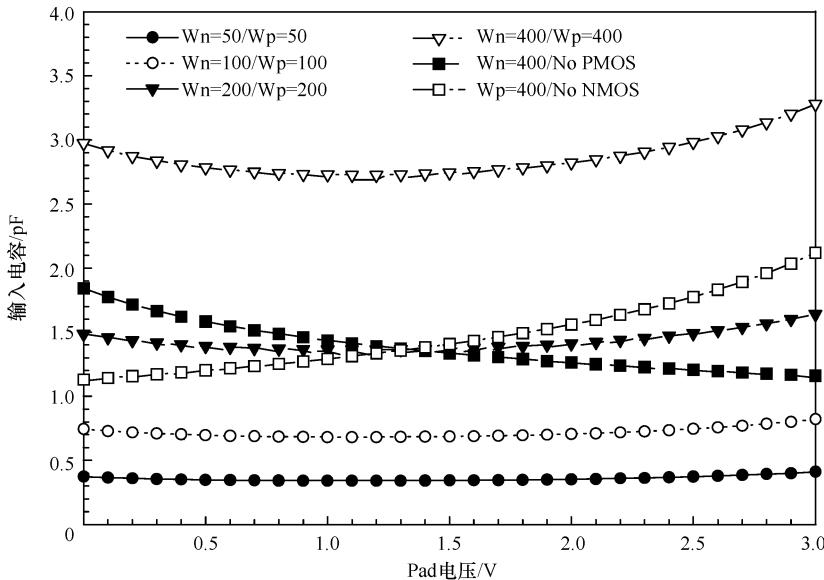

| 5.4.2 小电容 ESD 保护设计 .....              | 156        |

| 5.4.3 输入电容的计算 .....                   | 159        |

| 5.4.4 ESD 鲁棒性 .....                   | 160        |

| 5.4.5 开启验证 .....                      | 161        |

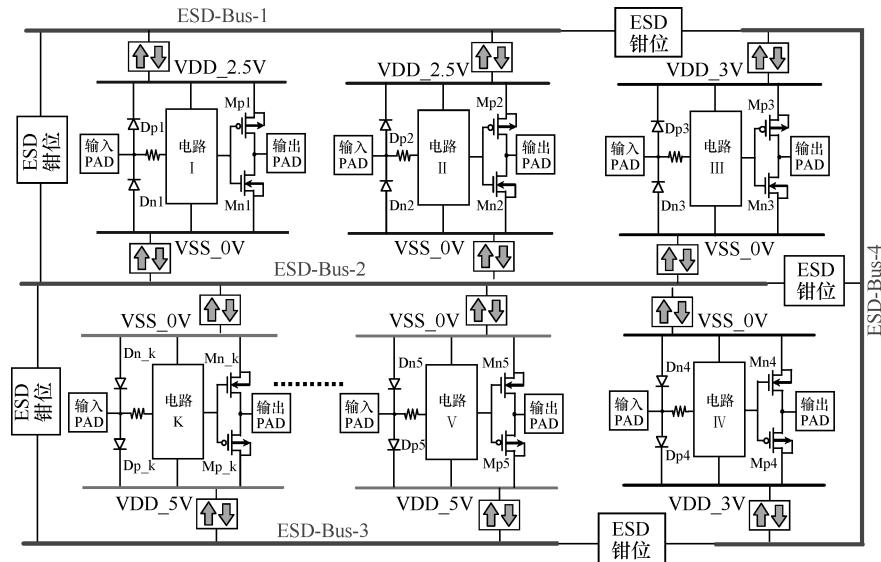

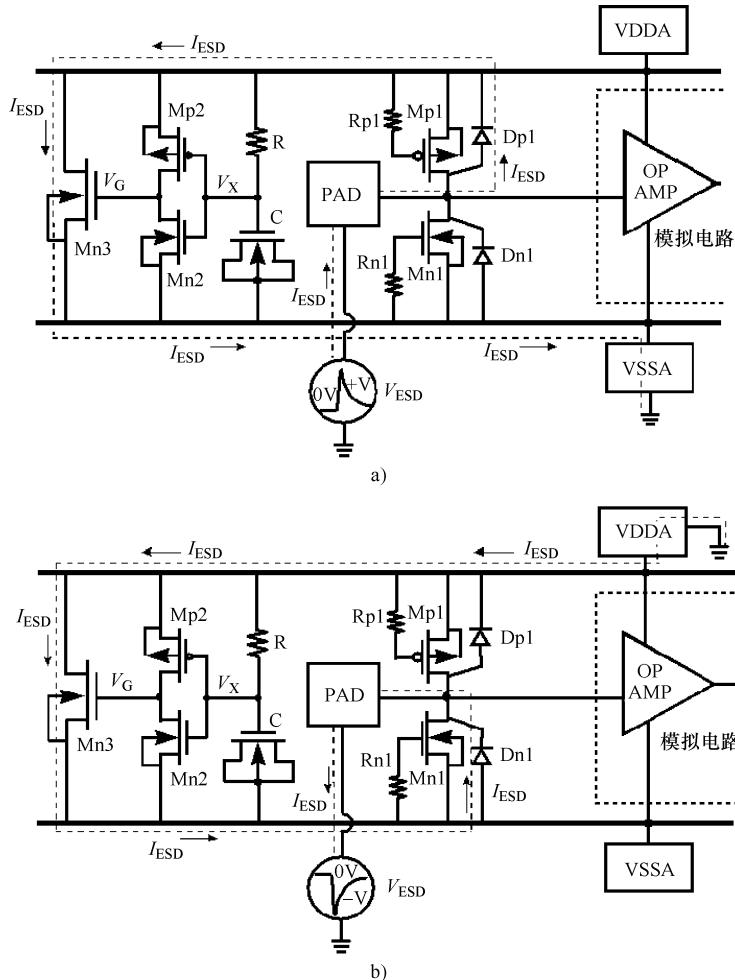

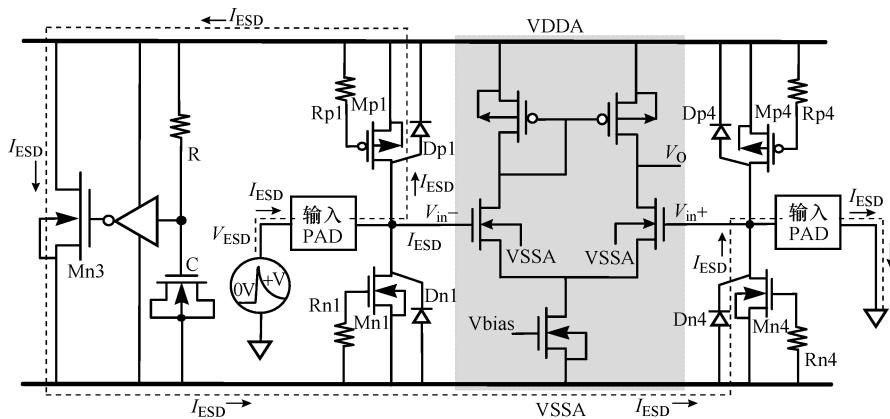

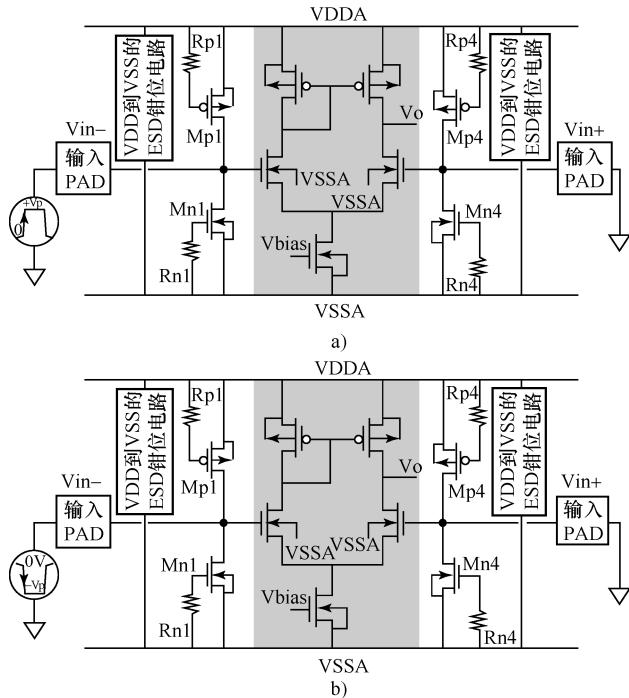

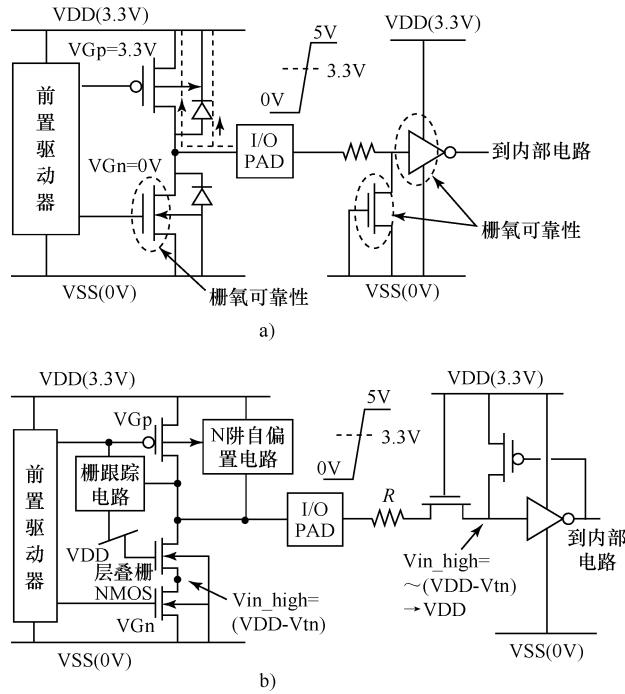

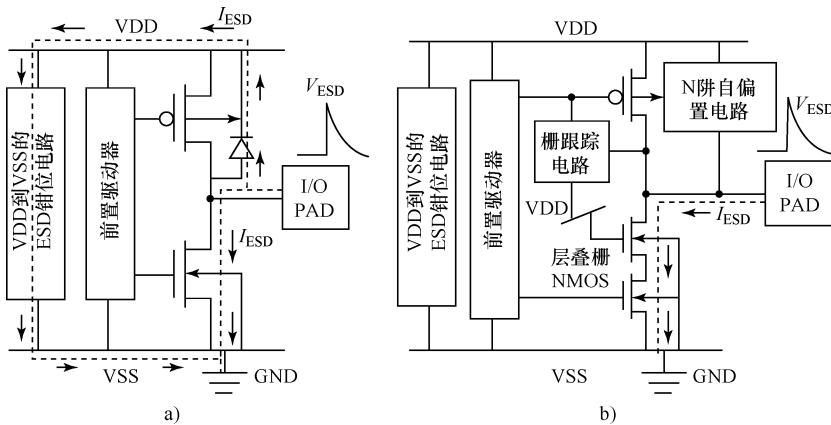

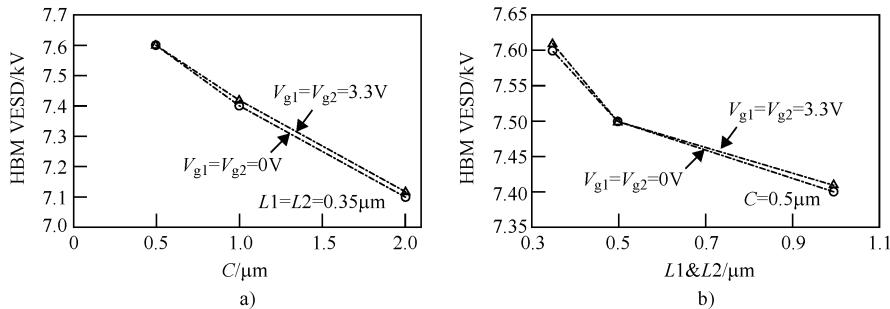

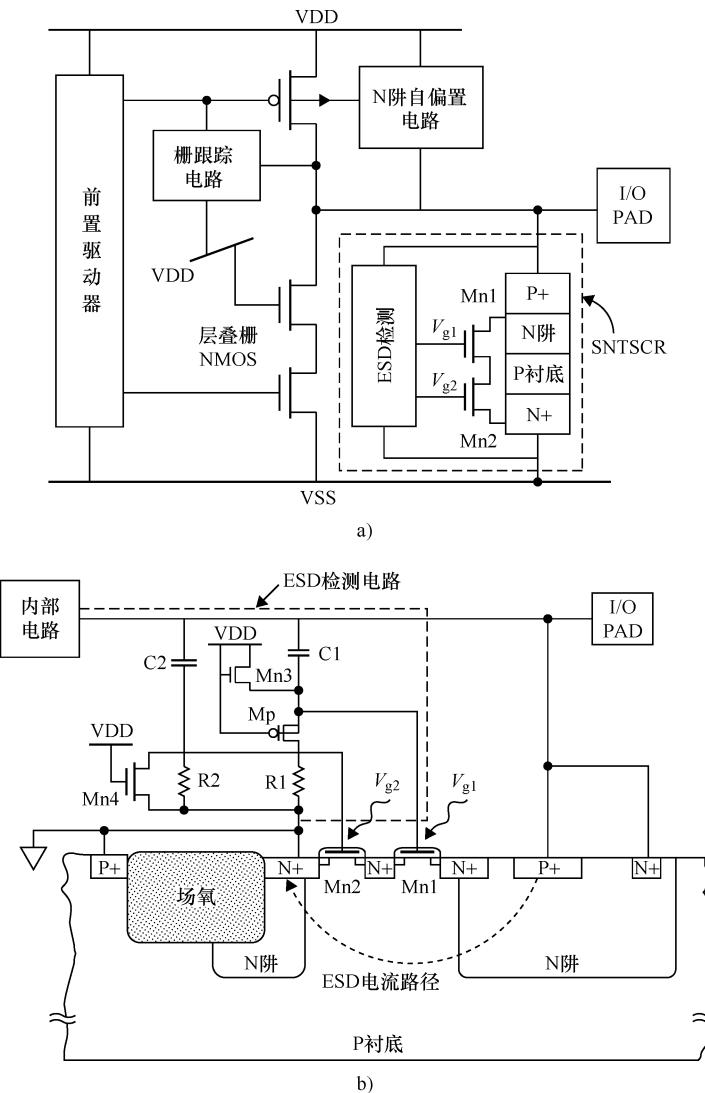

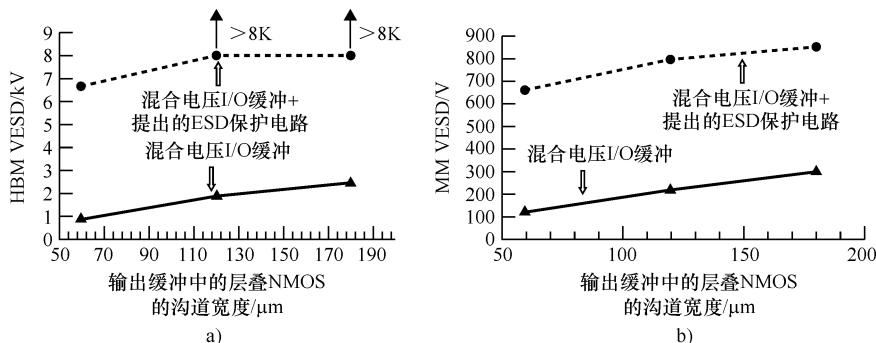

| 5.5 混合电压 I/O 的 ESD 保护设计 .....         | 165        |

| 5.5.1 混合电压 I/O 接口 .....               | 165        |

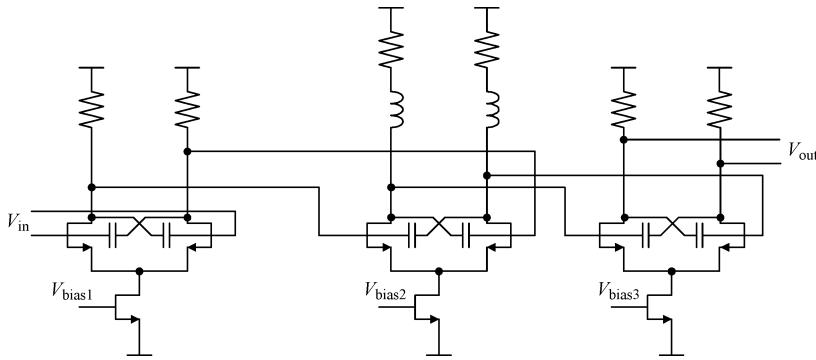

| 5.5.2 混合电压 I/O 接口的 ESD 问题 .....       | 165        |

| 5.5.3 混合电压 I/O 接口的 ESD 保护器件 .....     | 167        |

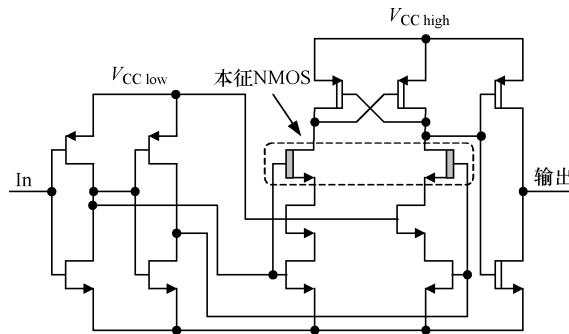

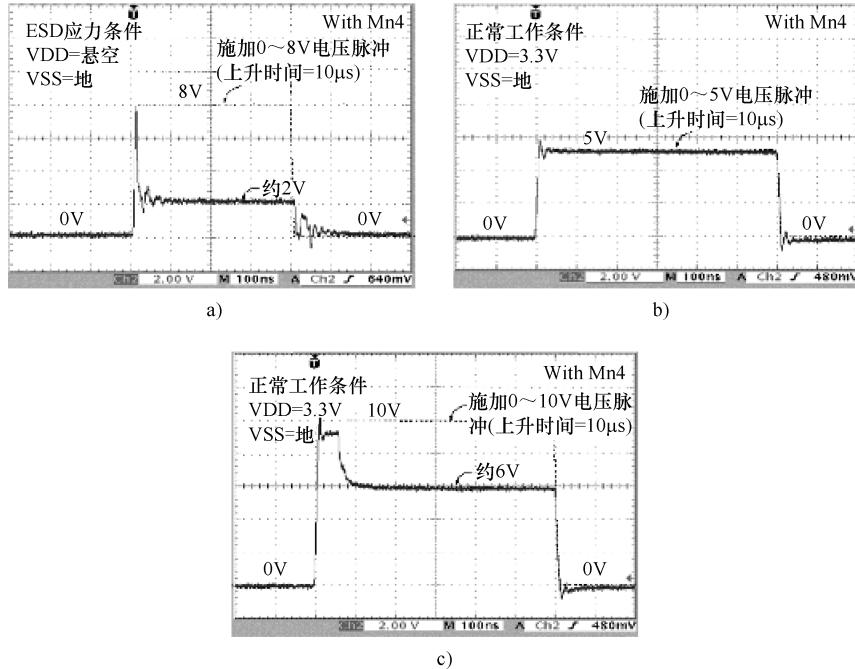

| 5.5.4 混合电压 I/O 接口的 ESD 保护电路设计 .....   | 170        |

| 5.5.5 ESD 鲁棒性 .....                   | 172        |

| 5.5.6 开启验证 .....                      | 173        |

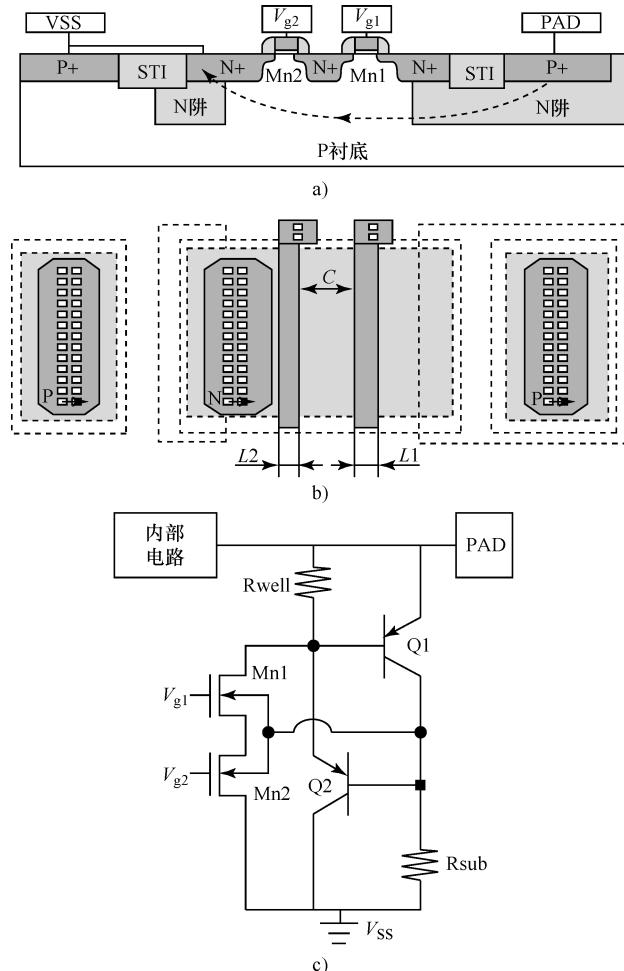

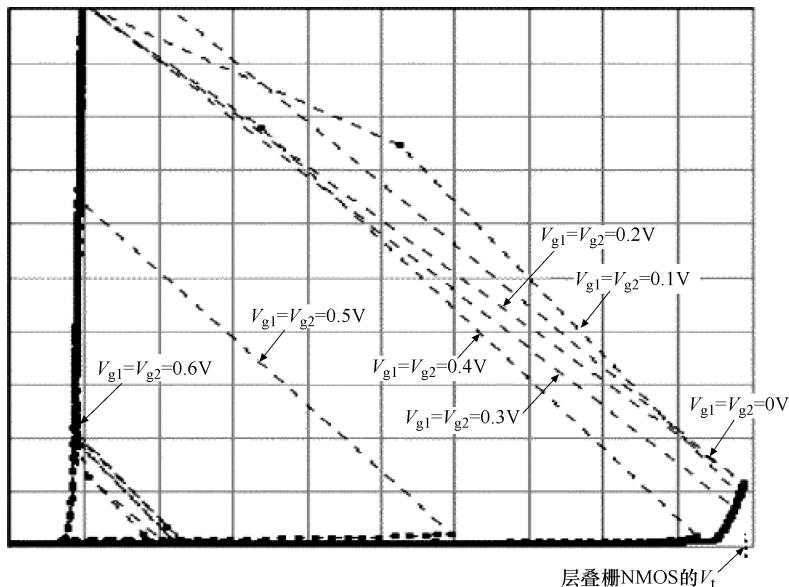

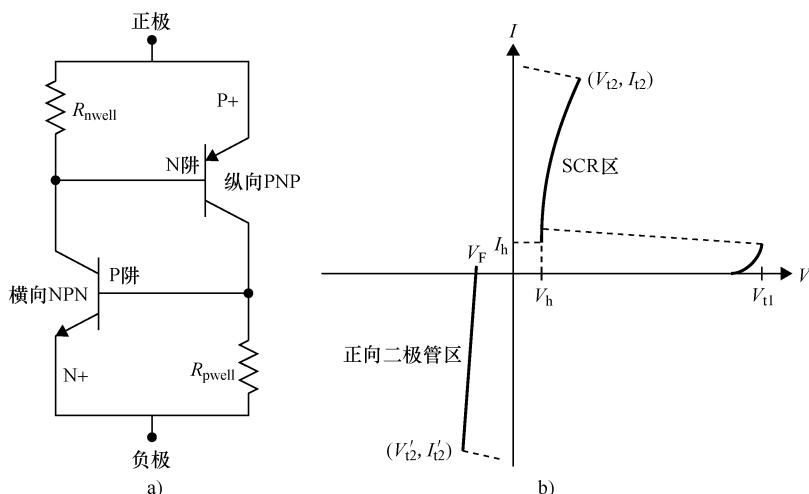

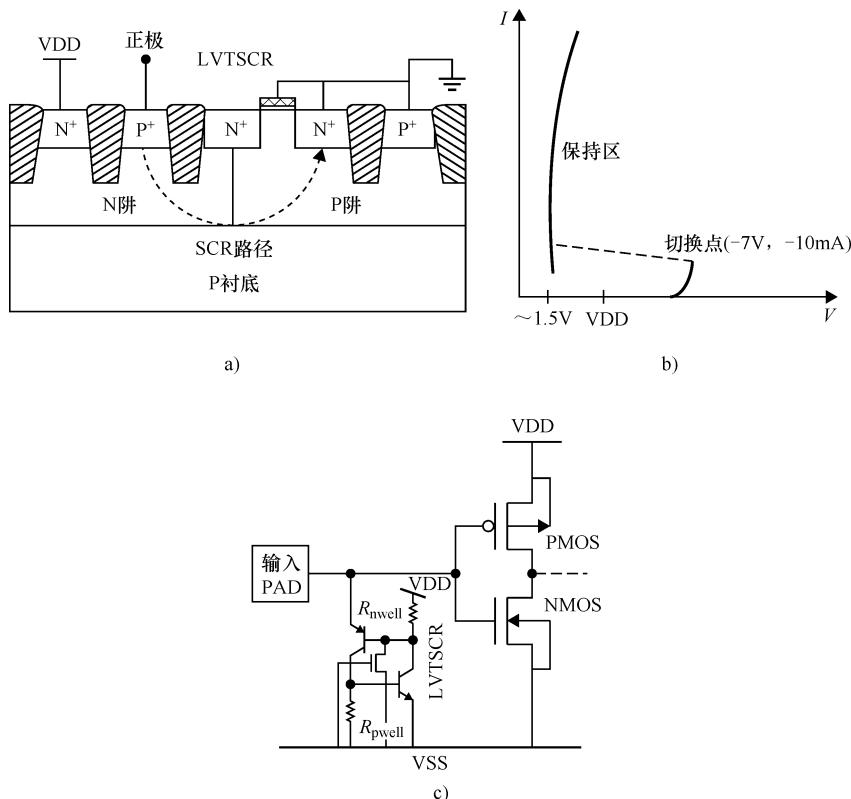

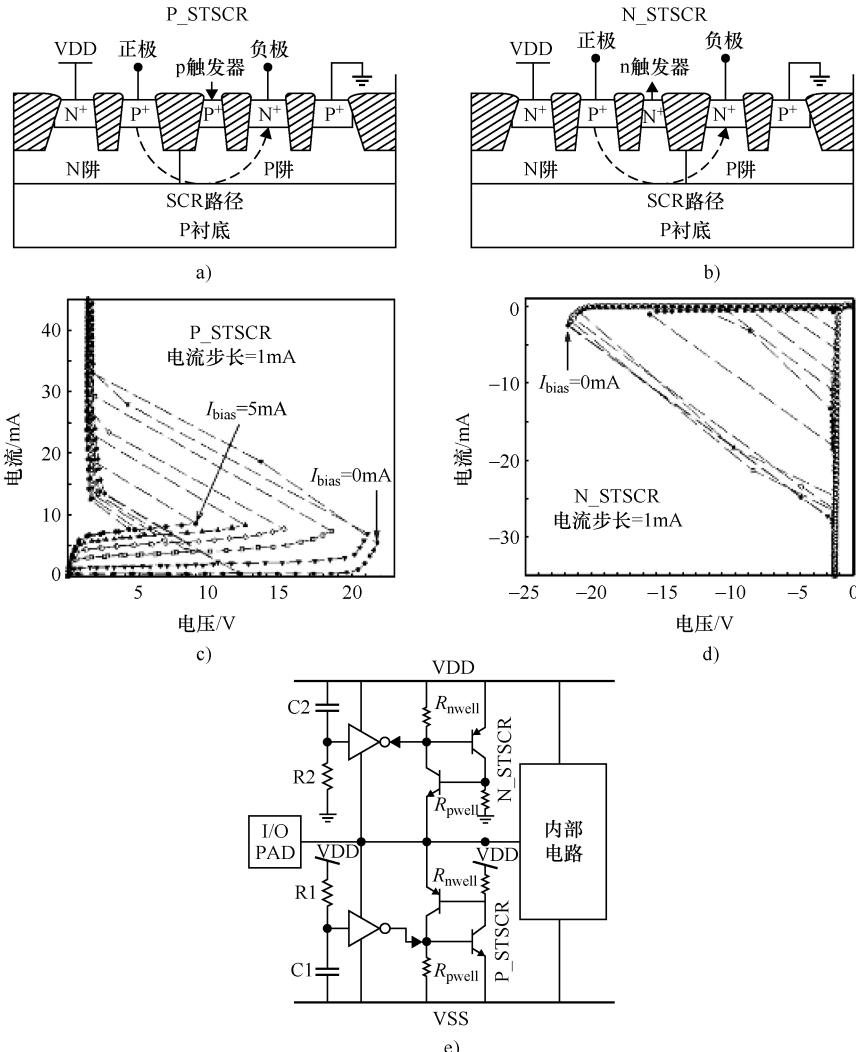

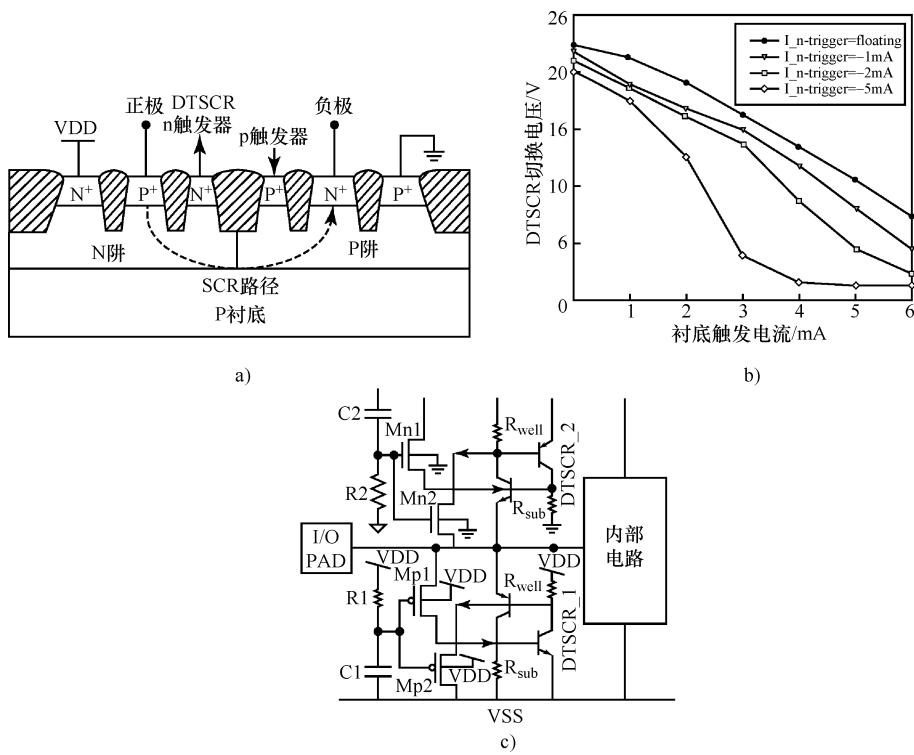

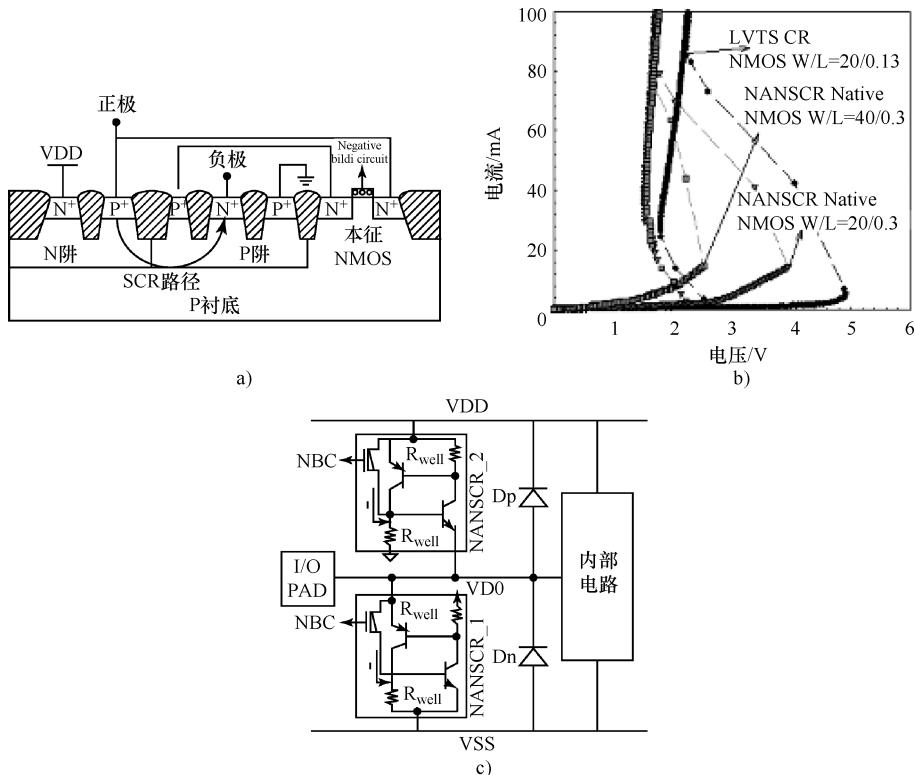

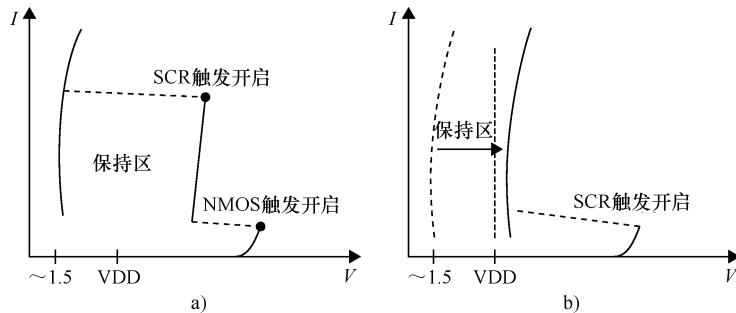

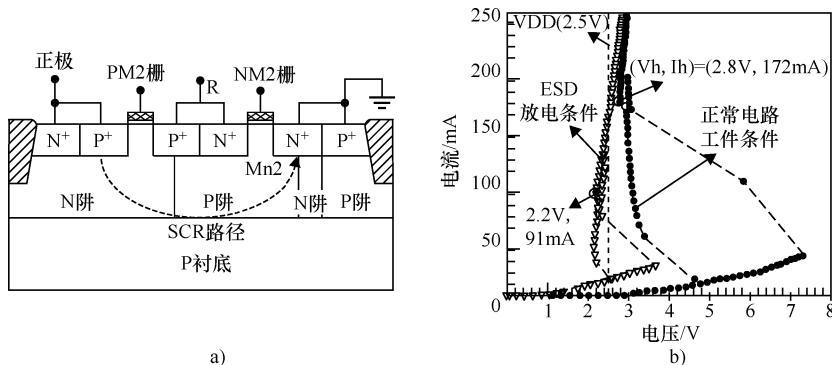

| 5.6 用于 ESD 保护的 SCR 器件 .....           | 174        |

| 5.6.1 SCR 器件的开启机制 .....               | 175        |

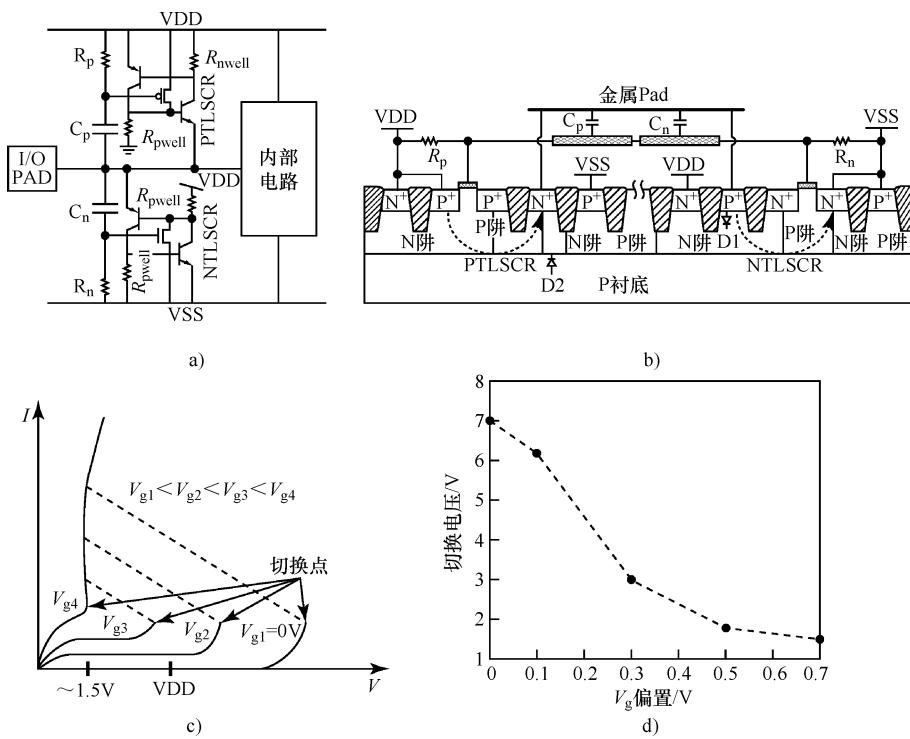

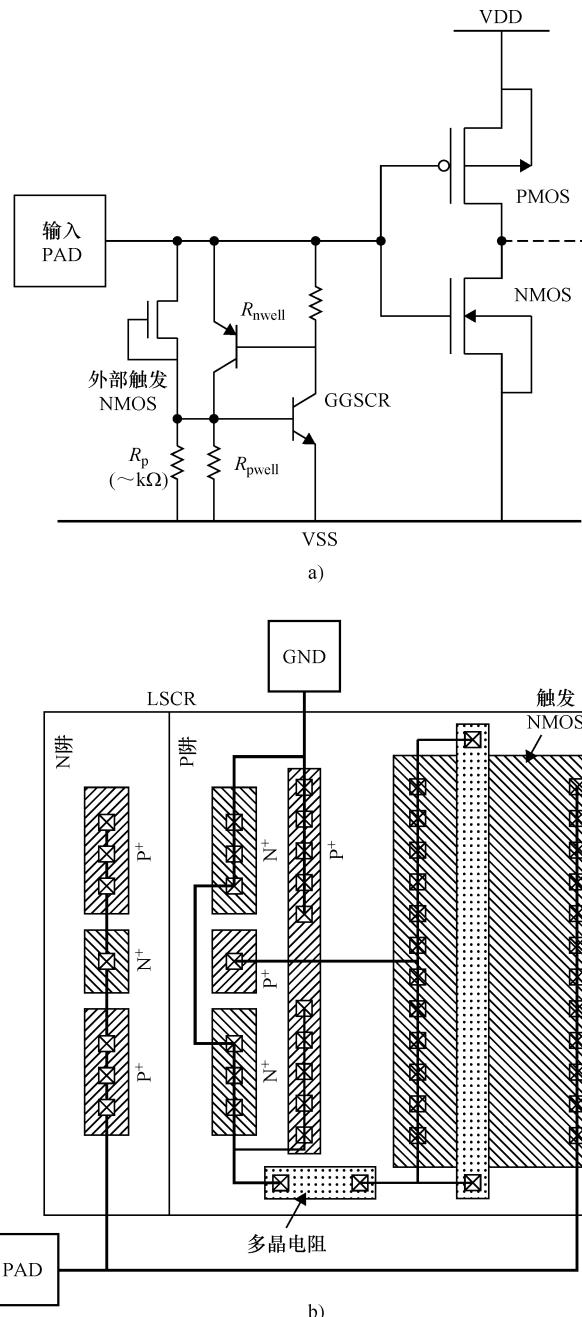

| 5.6.2 基于 SCR 的 CMOS 片上 ESD 保护器件 ..... | 176        |

| 5.6.3 SCR 闩锁工程 .....                  | 183        |

| 5.7 总结 .....                          | 185        |

| 参考文献 .....                            | 186        |

| <b>第6章 输入/输出设计 .....</b>              | <b>193</b> |

| 6.1 引言 .....                          | 193        |

| 6.2 I/O 标准 .....                      | 194        |

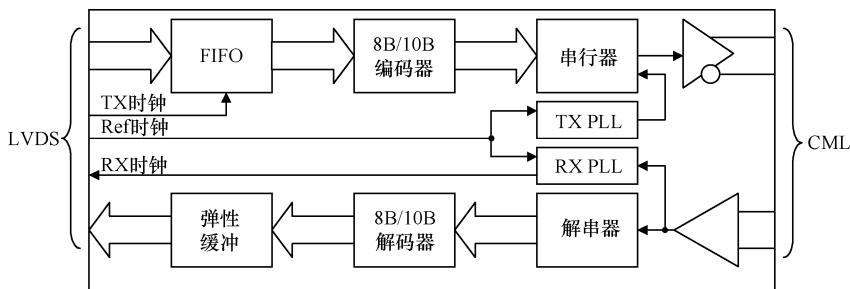

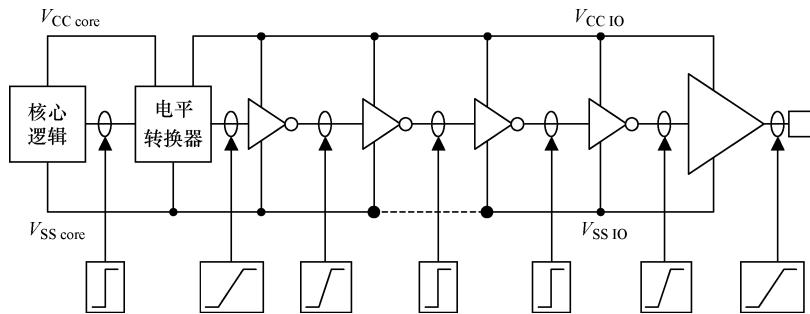

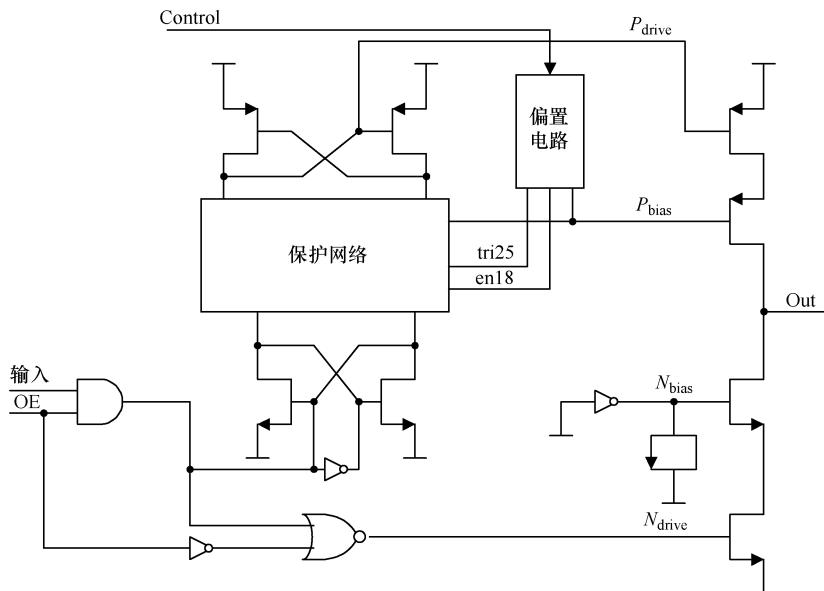

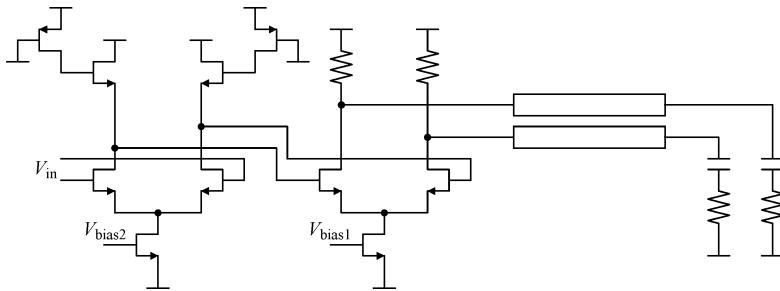

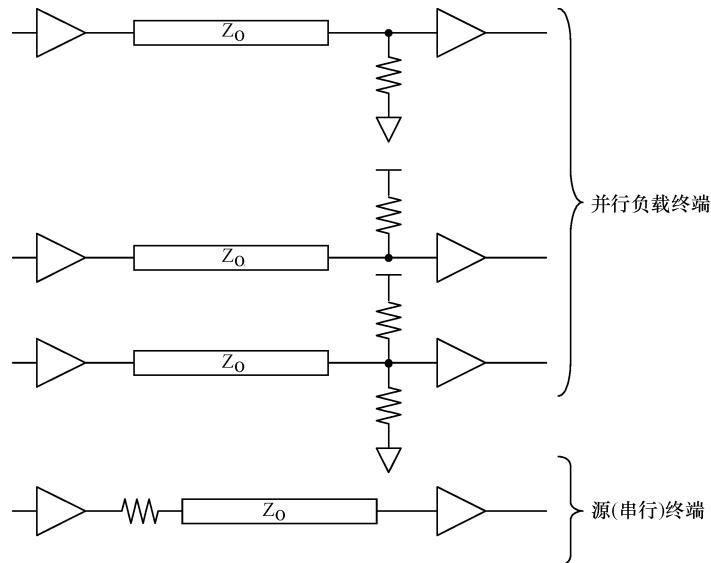

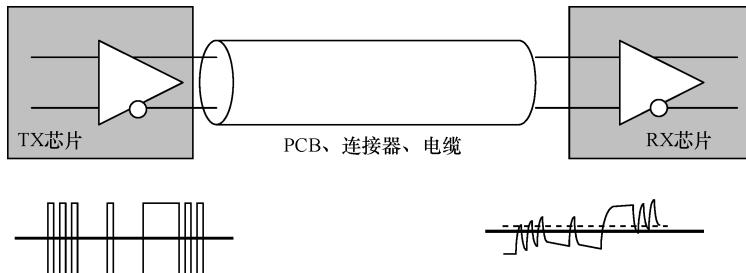

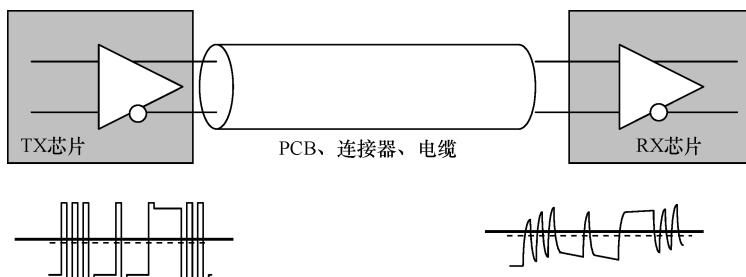

| 6.3 信号传输 .....                        | 195        |

| 6.3.1 单端缓冲器 .....                     | 195        |

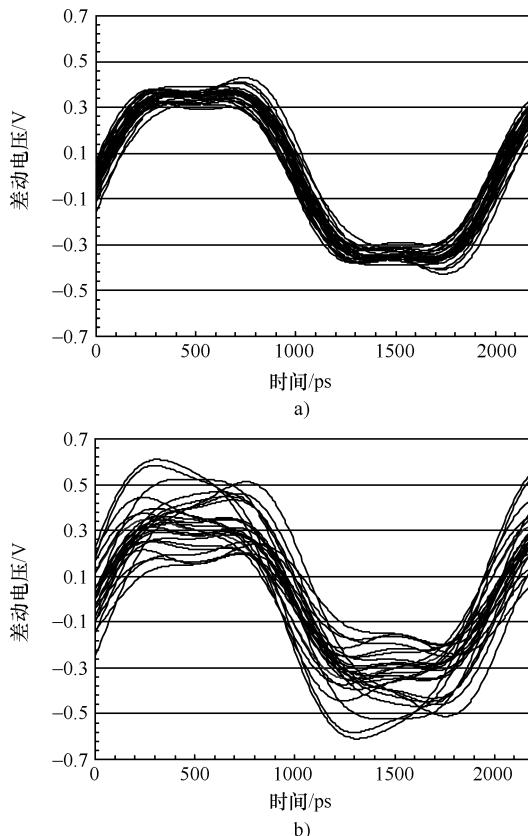

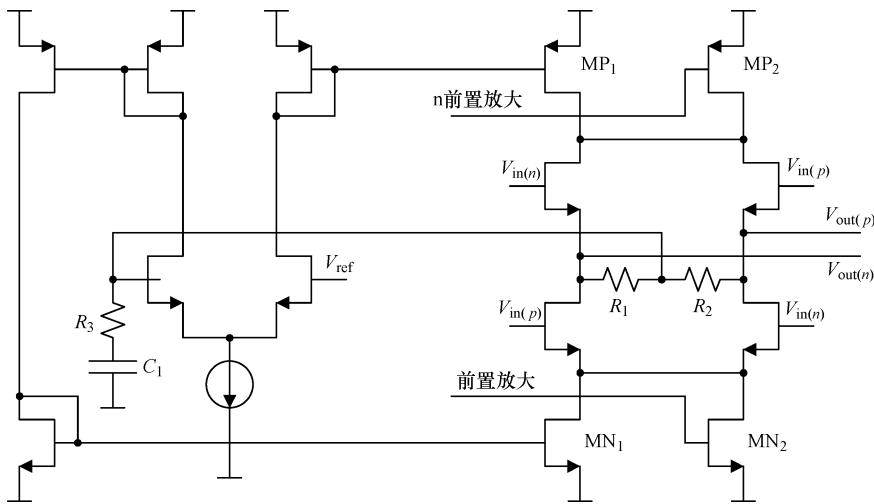

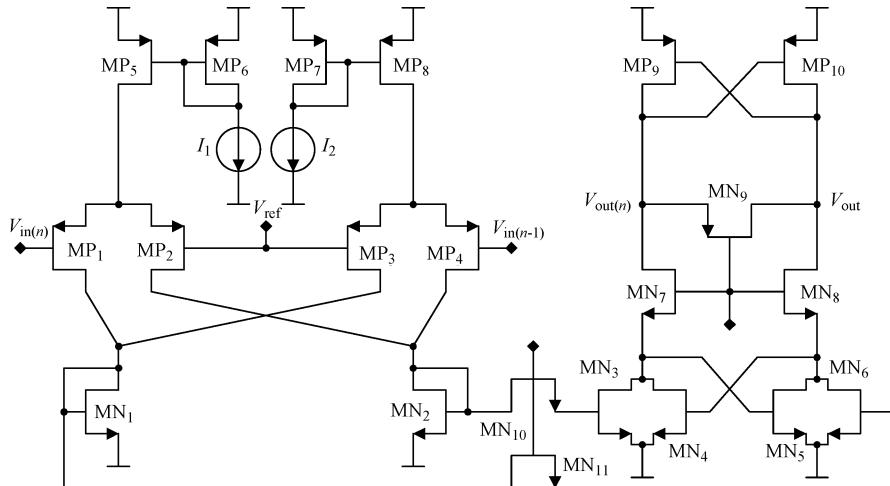

| 6.3.2 差分缓冲器 .....                     | 196        |

| 6.4 ESD 保护 .....                      | 199        |

| 6.5 I/O 开关噪声 .....                    | 200        |

| 6.6 匹配 .....                          | 203        |

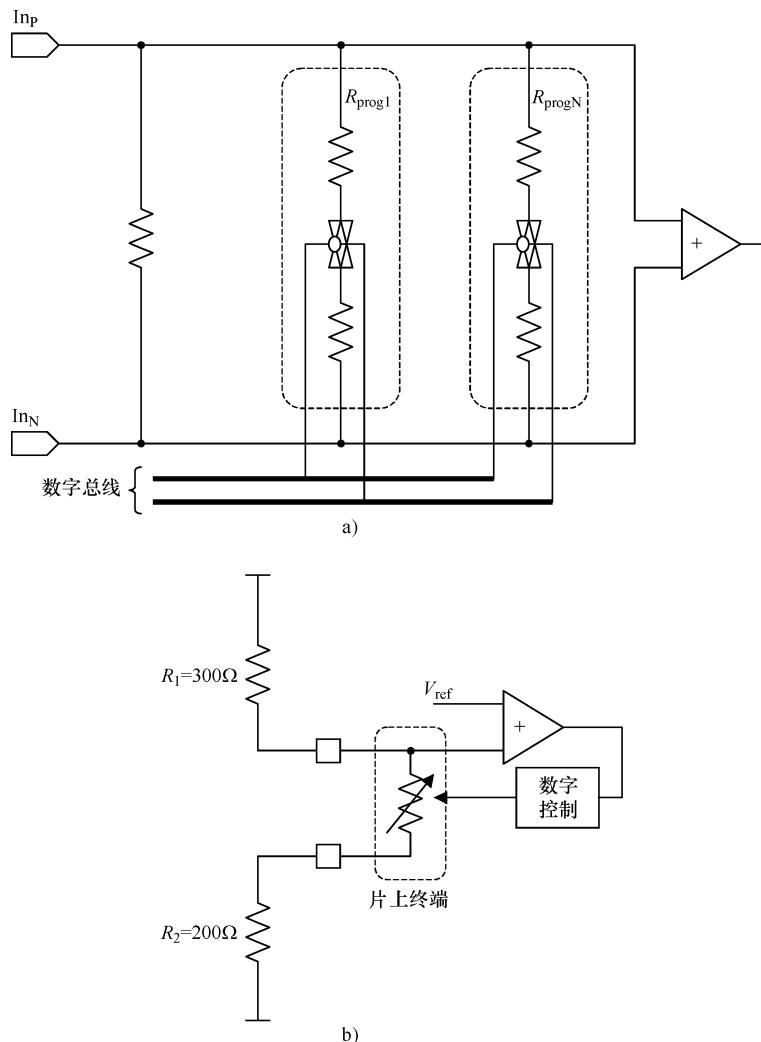

| 6.7 阻抗匹配 .....                        | 206        |

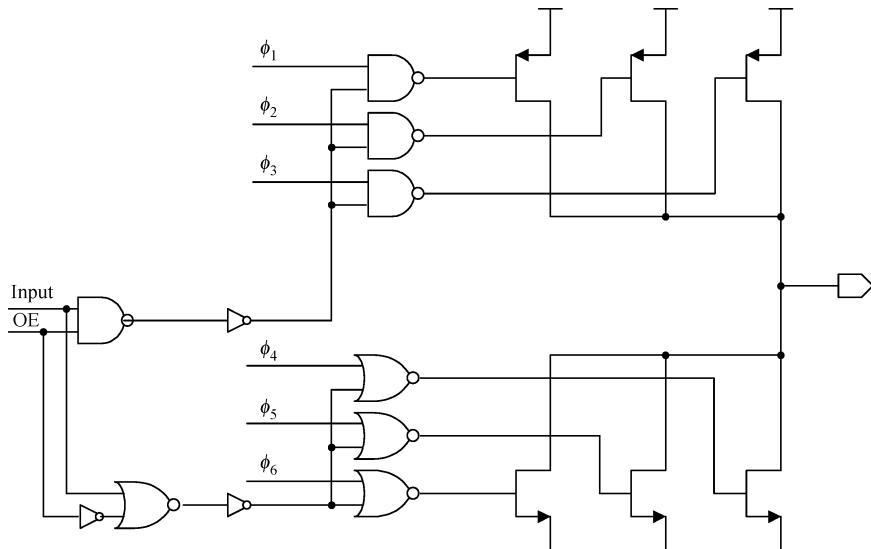

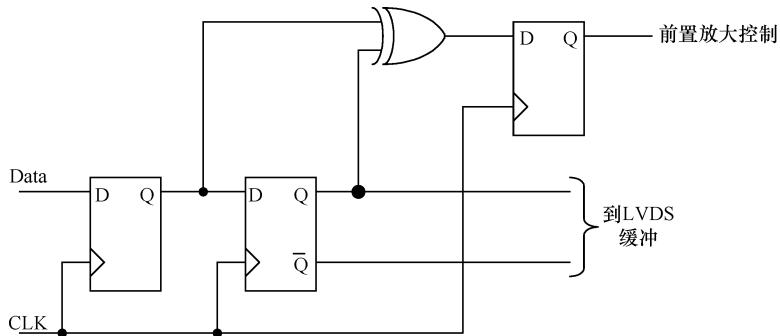

| 6.8 前置放大 .....                        | 206        |

| 6.9 均衡化 .....                         | 208        |

| 6.10 总结 .....                         | 209        |

| 参考文献 .....                            | 210        |

| <b>第7章 DRAM .....</b>                 | <b>212</b> |

| 7.1 引言 .....                          | 212        |

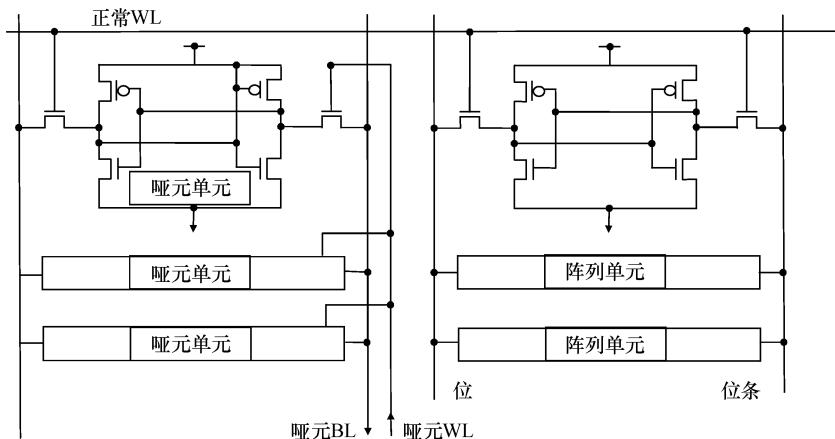

| 7.2 DRAM 基础 .....                     | 212        |

| 7.3 电容的缩放 .....                       | 215        |

| 7.4 阵列晶体管的缩放 .....                    | 217        |

|                               |            |

|-------------------------------|------------|

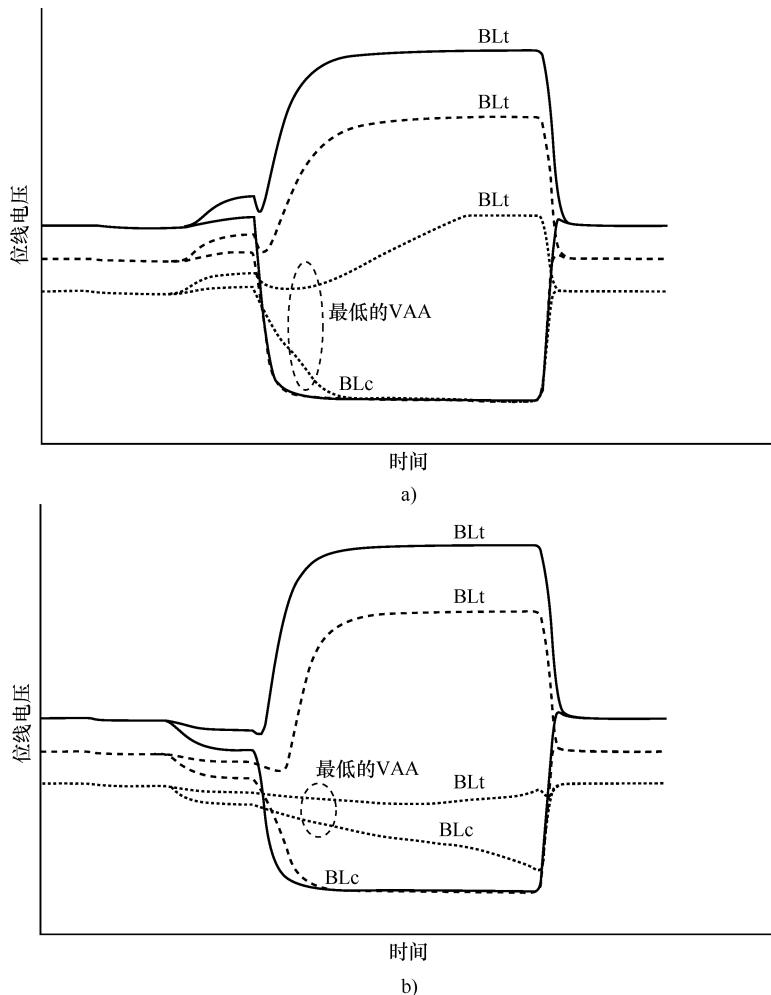

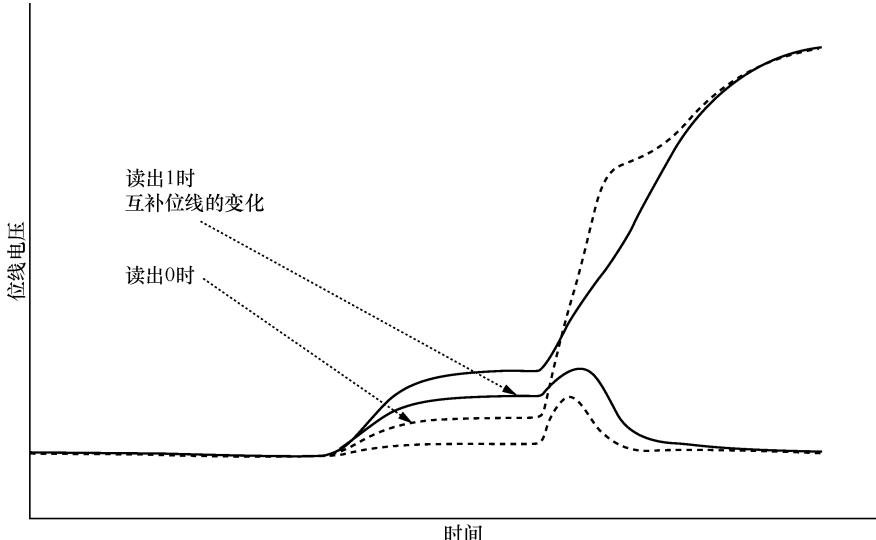

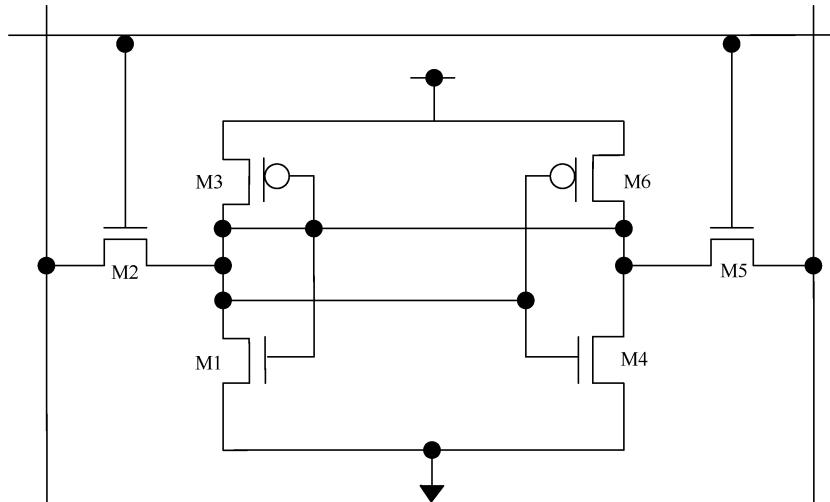

| 7.5 读出放大器的缩放 .....            | 220        |

| 7.6 总结 .....                  | 223        |

| 参考文献 .....                    | 223        |

| <b>第8章 片上互连的信号完整性问题.....</b>  | <b>225</b> |

| 8.1 引言 .....                  | 225        |

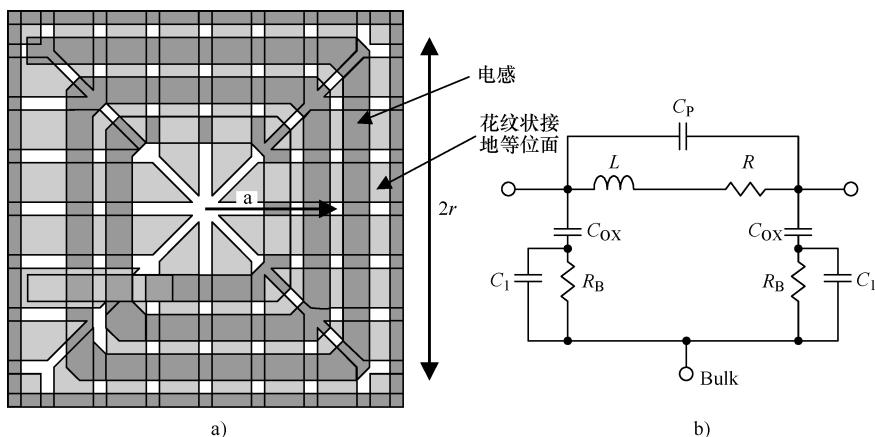

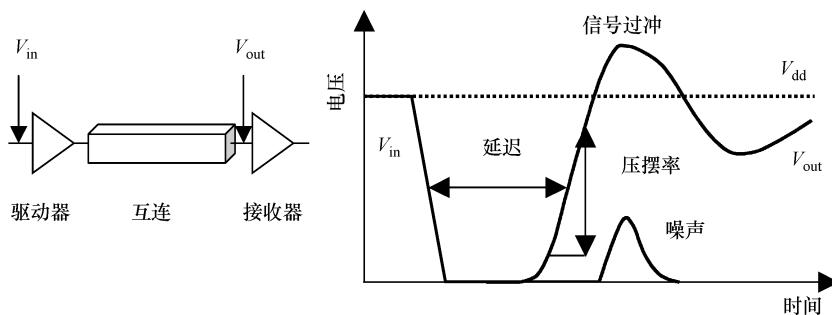

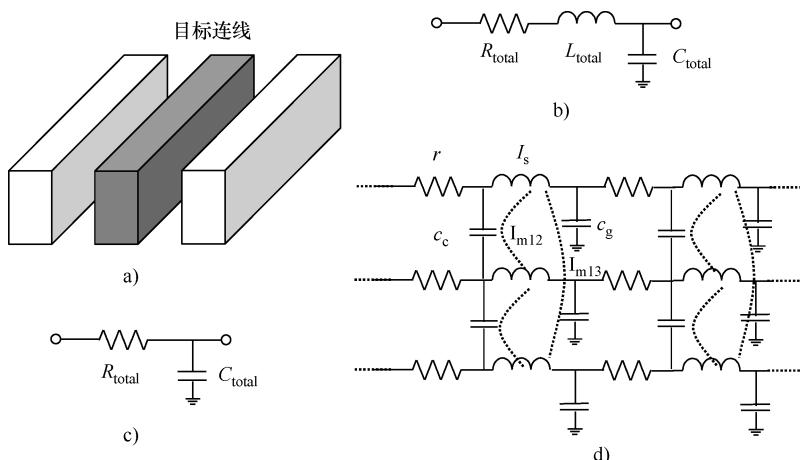

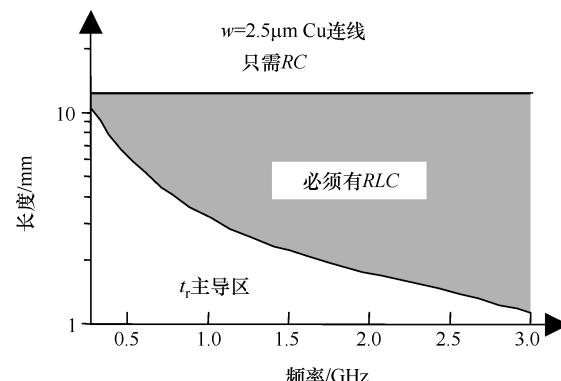

| 8.1.1 互连的品质因数 .....           | 227        |

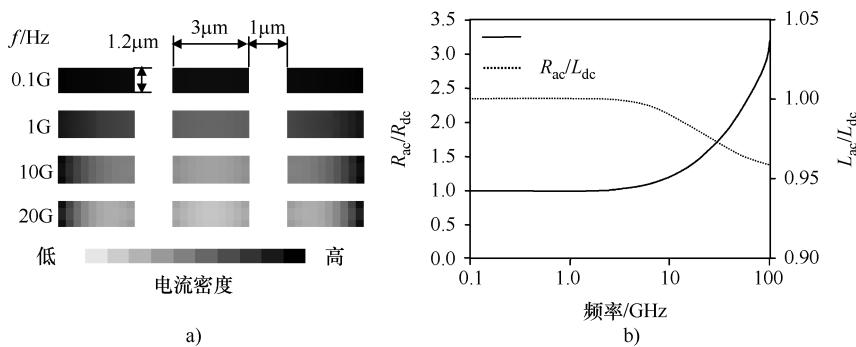

| 8.2 互连参数提取 .....              | 228        |

| 8.2.1 互连的等效电路表示 .....         | 229        |

| 8.2.2 $RC$ 的提取 .....          | 232        |

| 8.2.3 电感提取 .....              | 235        |

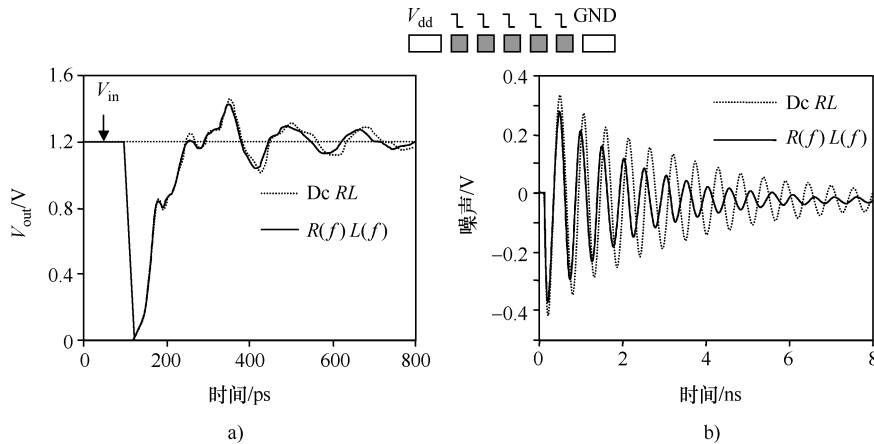

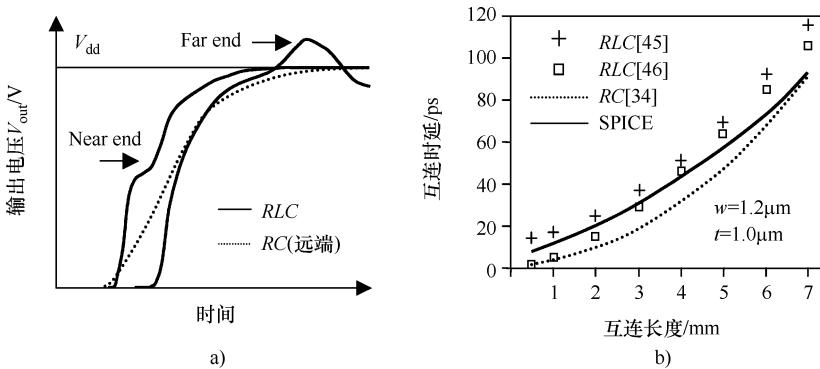

| 8.3 信号完整性分析 .....             | 239        |

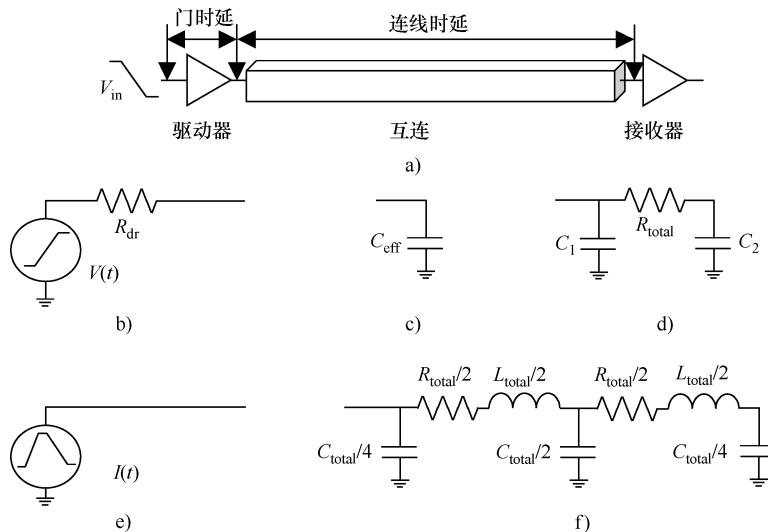

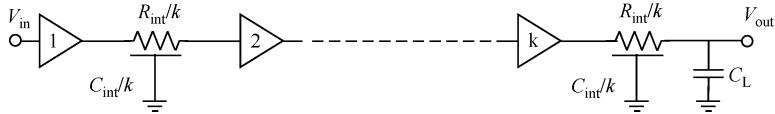

| 8.3.1 互连驱动器模型 .....           | 239        |

| 8.3.2 $RC$ 互连分析 .....         | 241        |

| 8.3.3 $RLC$ 互连分析 .....        | 244        |

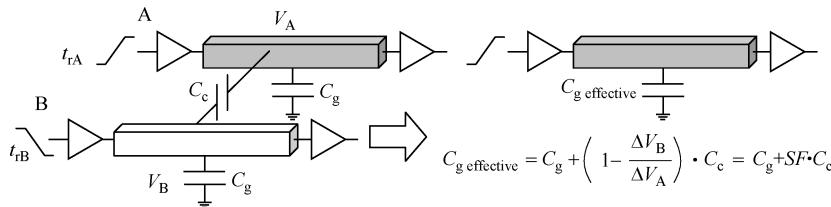

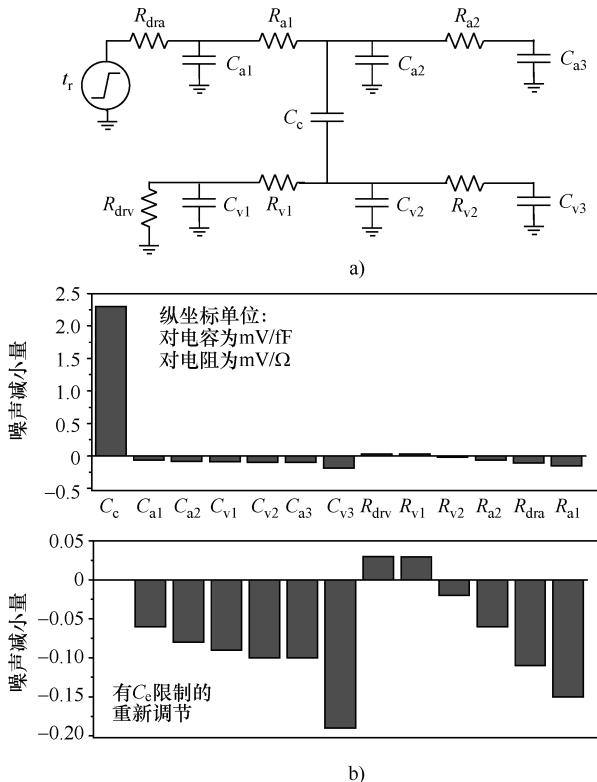

| 8.3.4 考虑噪声耦合效应的时序分析 .....     | 247        |

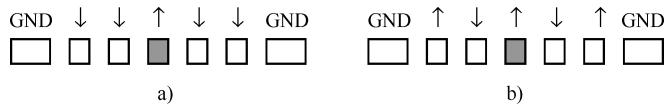

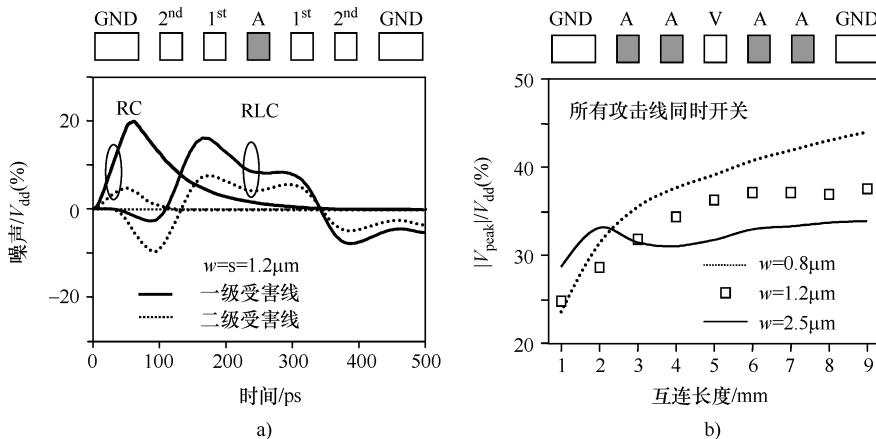

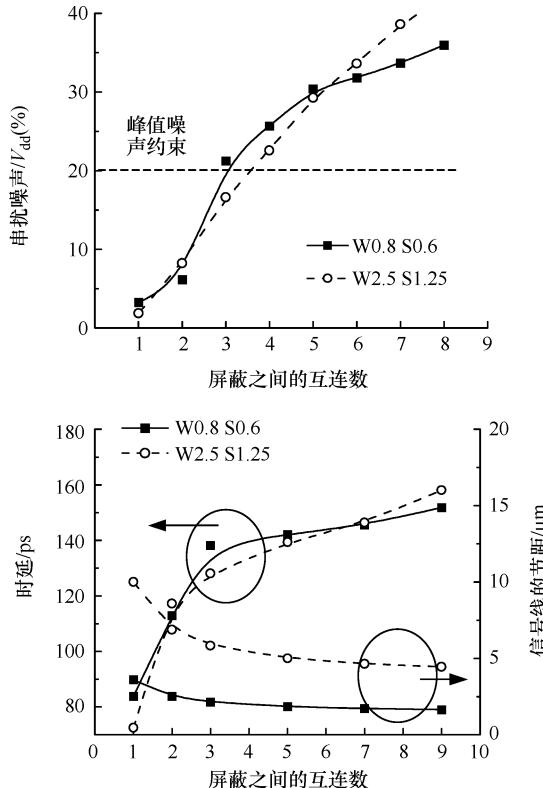

| 8.4 信号完整性设计技术 .....           | 249        |

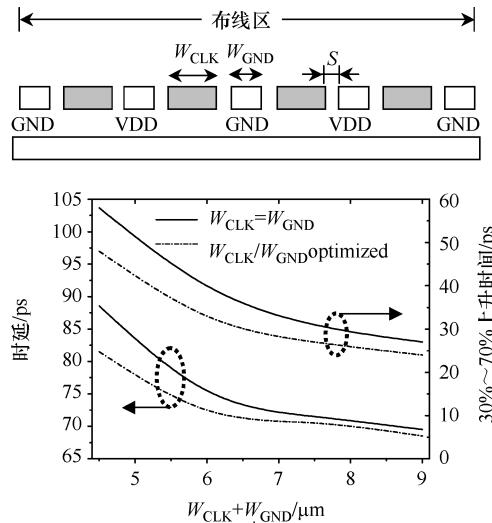

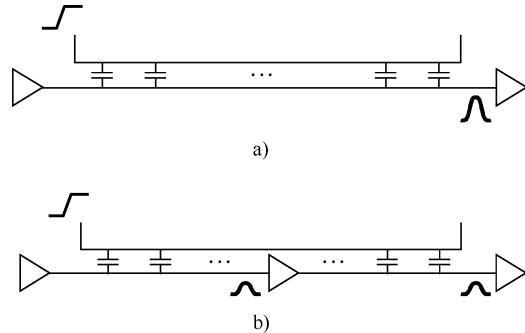

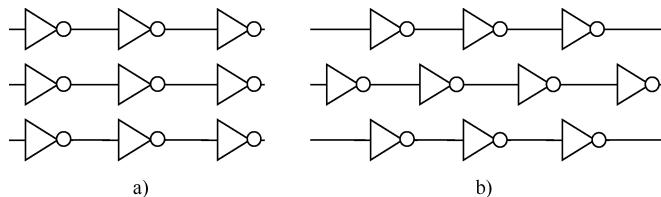

| 8.4.1 物理设计技术 .....            | 250        |

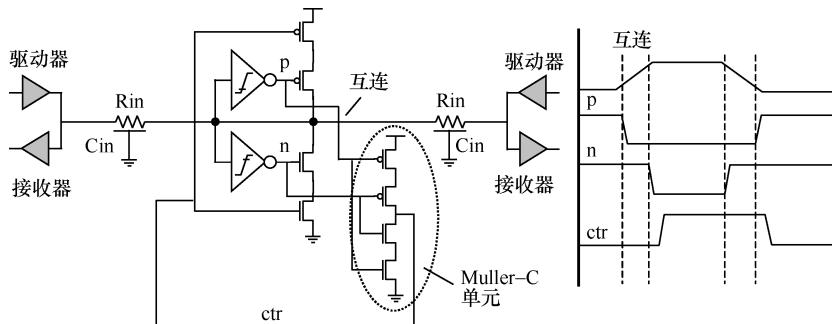

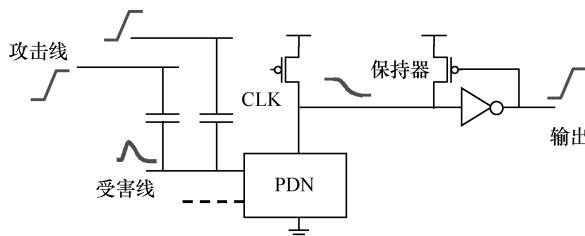

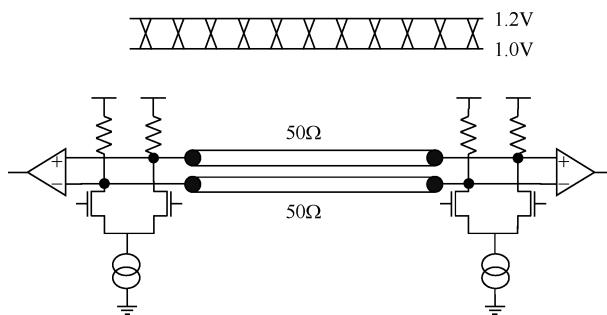

| 8.4.2 电路技术 .....              | 254        |

| 8.5 总结 .....                  | 258        |

| 参考文献 .....                    | 259        |

| <b>第9章 超低功耗电路设计.....</b>      | <b>263</b> |

| 9.1 引言 .....                  | 263        |

| 9.2 设计阶段的低功耗技术 .....          | 264        |

| 9.2.1 系统级和结构级设计阶段的低功耗技术 ..... | 264        |

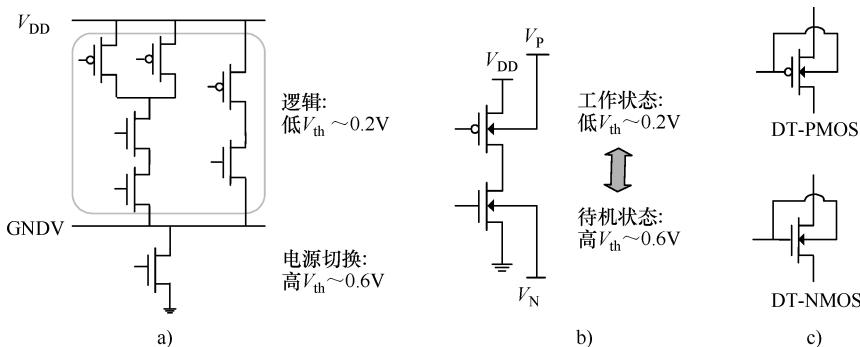

| 9.2.2 电路级设计阶段的低功耗技术 .....     | 265        |

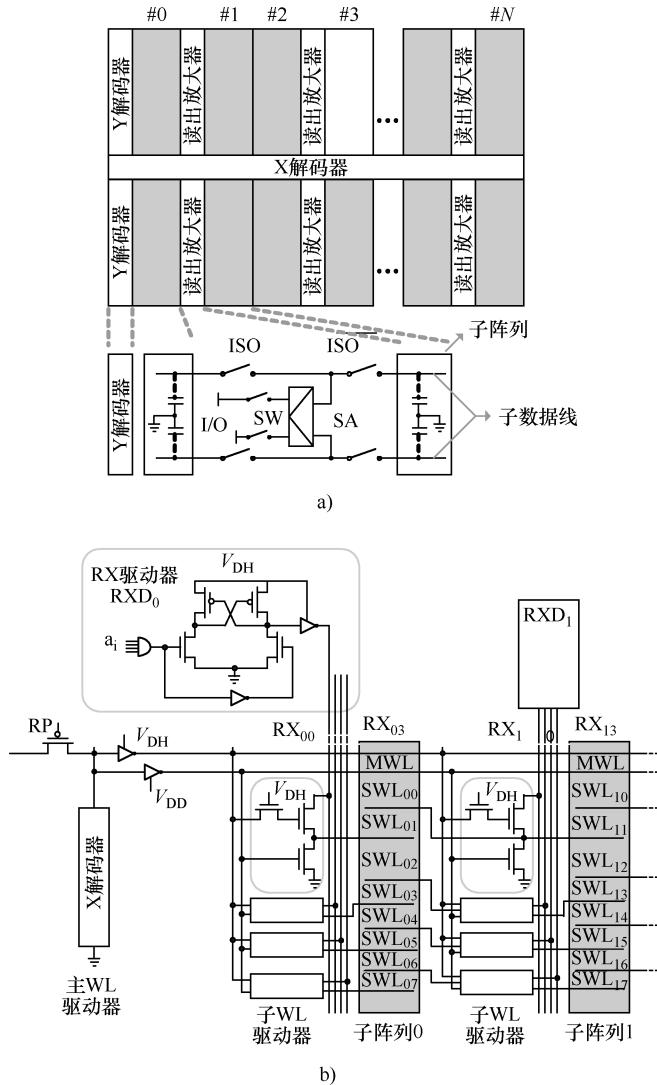

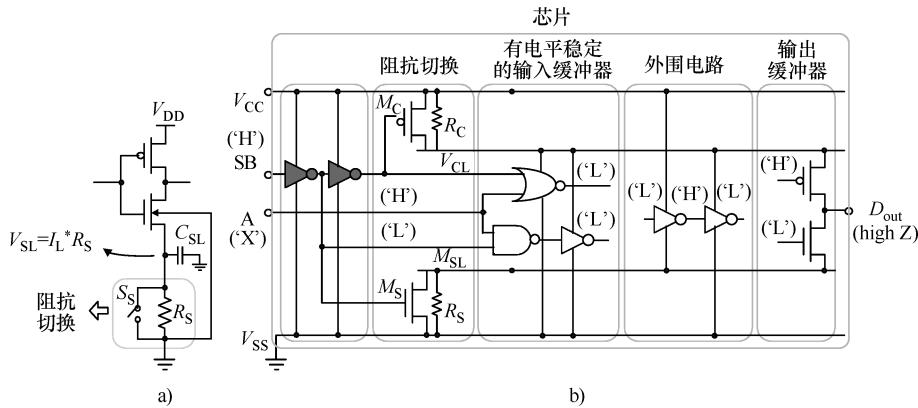

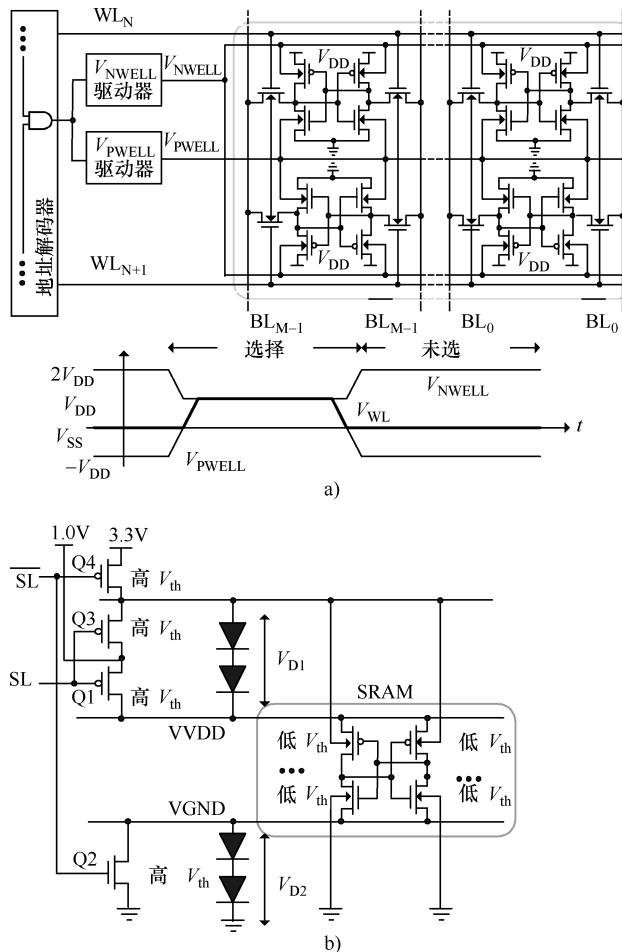

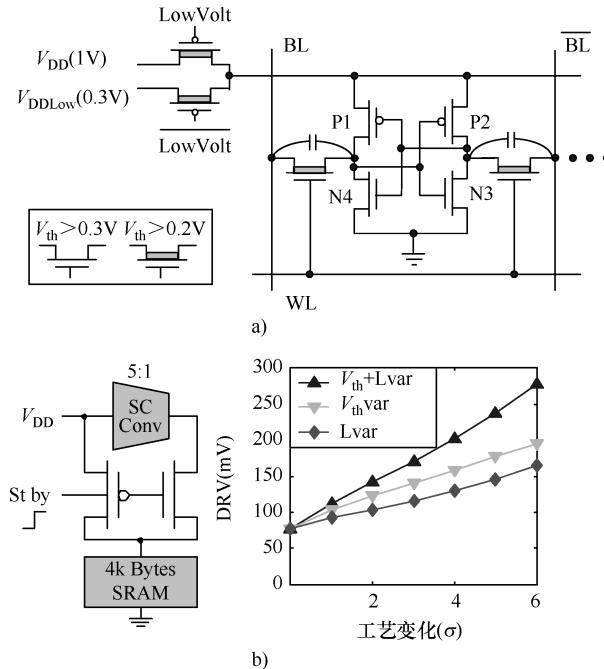

| 9.2.3 设计阶段的存储器技术 .....        | 269        |

| 9.3 运行阶段的低功耗技术 .....          | 274        |

| 9.3.1 运行阶段的系统级和结构级低功耗技术 ..... | 274        |

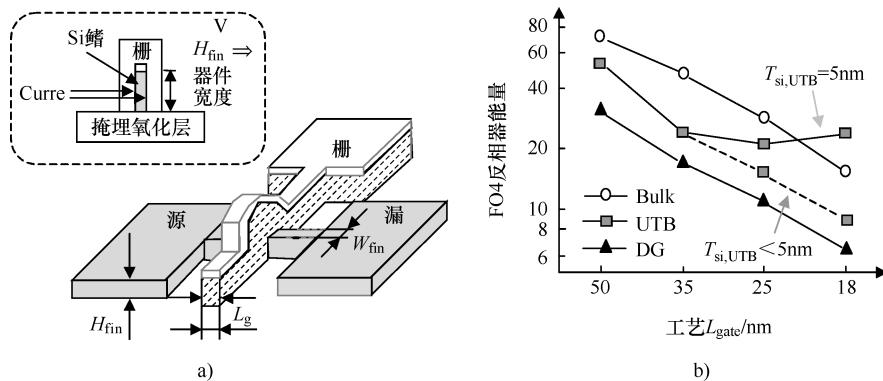

| 9.3.2 针对运行阶段的电路级低功耗技术 .....   | 277        |

| 9.3.3 针对运行阶段的存储器低功耗技术 .....   | 279        |

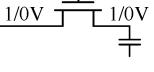

| 9.4 低功耗设计的技术革新 .....          | 283        |

| 9.4.1 新颖的器件技术 .....           | 283        |

| 9.4.2 组装技术革新 .....            | 284        |

| 9.5 未来超低功耗设计的展望 .....         | 285        |

| 9.5.1 亚阈区电路工作 .....           | 285        |

| 9.5.2 容错设计 .....              | 286        |

---

|                              |            |

|------------------------------|------------|

| 9.5.3 异步设计与同步设计 .....        | 286        |

| 9.5.4 栅感应泄漏抑制方法 .....        | 286        |

| 参考文献 .....                   | 287        |

| <b>第 10 章 可制造性设计 .....</b>   | <b>294</b> |

| 10.1 引言 .....                | 294        |

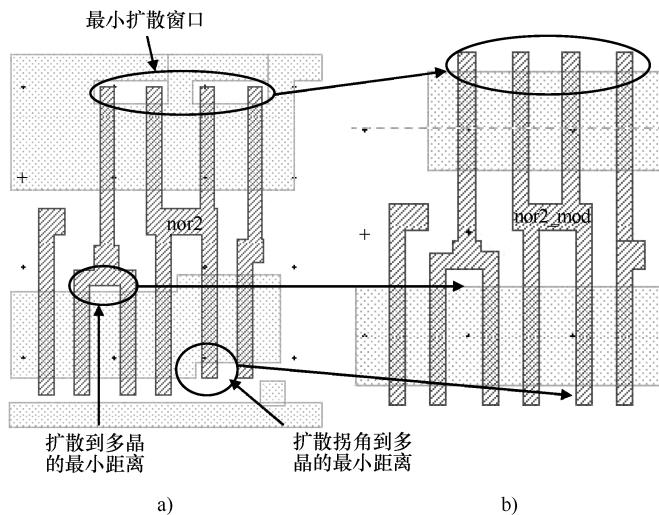

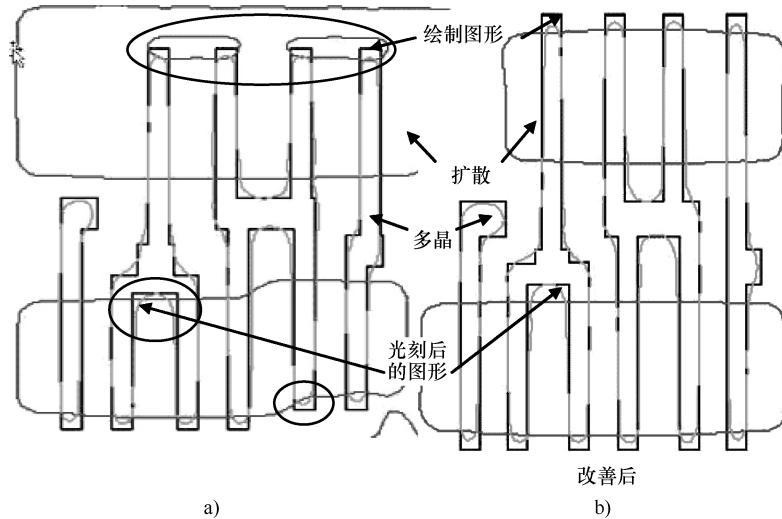

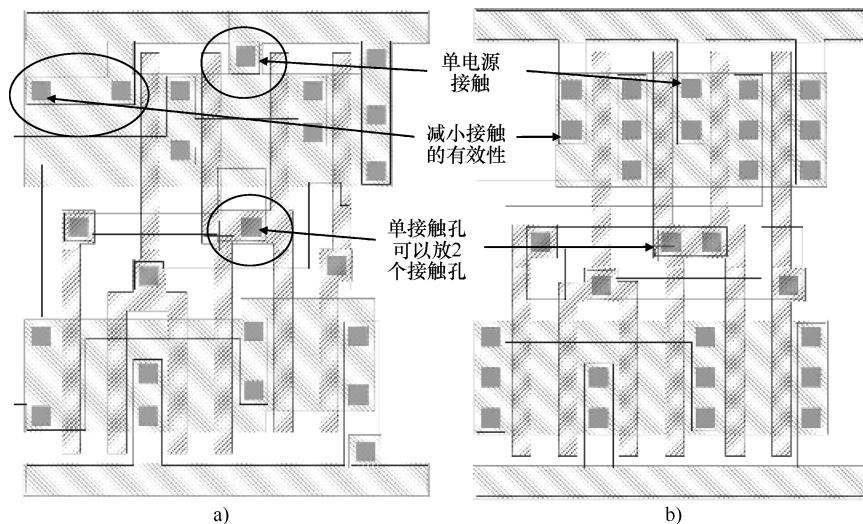

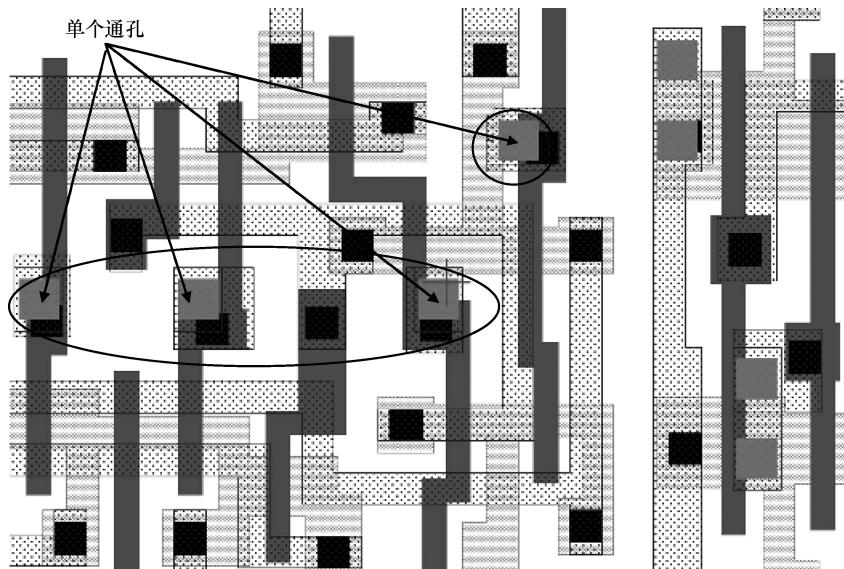

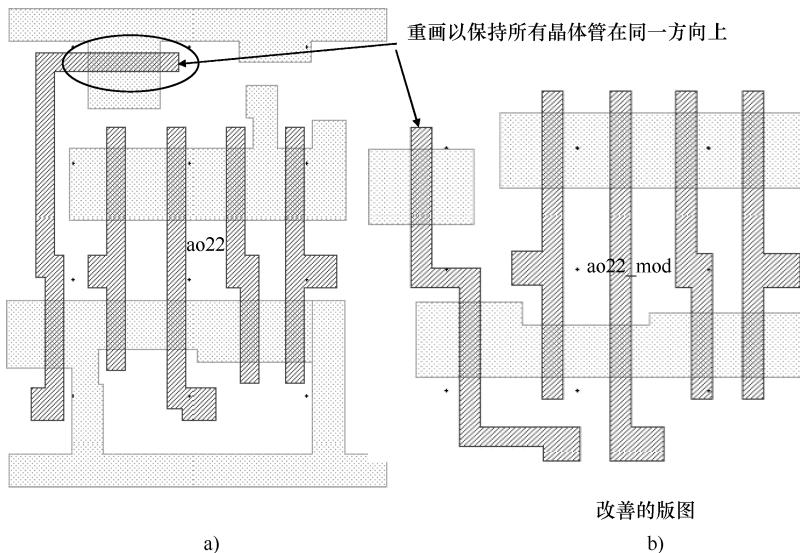

| 10.2 最优和亚最优版图对比 .....        | 295        |

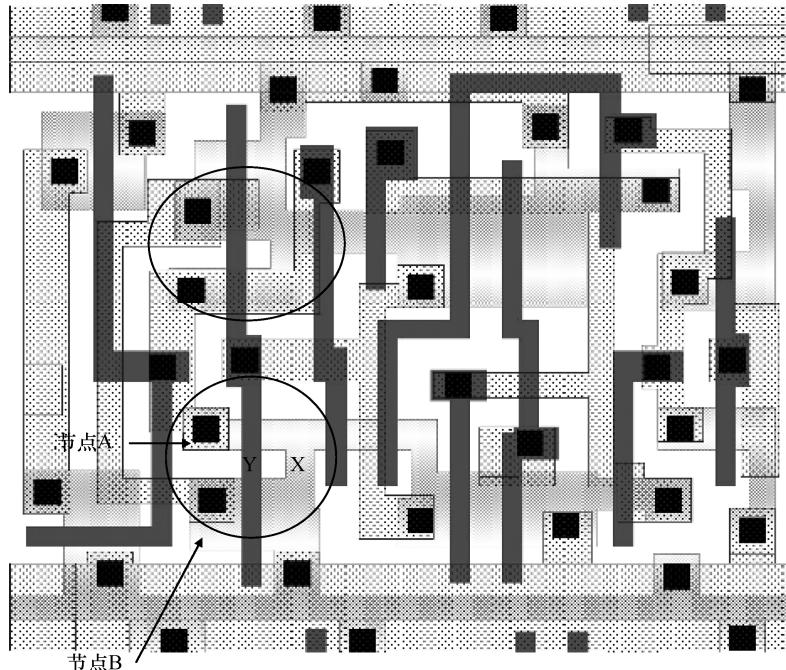

| 10.3 全局布线 DFM .....          | 300        |

| 10.4 模拟电路的 DFM .....         | 301        |

| 10.5 一些基本规则 .....            | 303        |

| 10.6 总结 .....                | 304        |

| 参考文献 .....                   | 304        |

| <b>第 11 章 针对波动性的设计 .....</b> | <b>305</b> |

| 11.1 波动性对未来设计的影响 .....       | 305        |

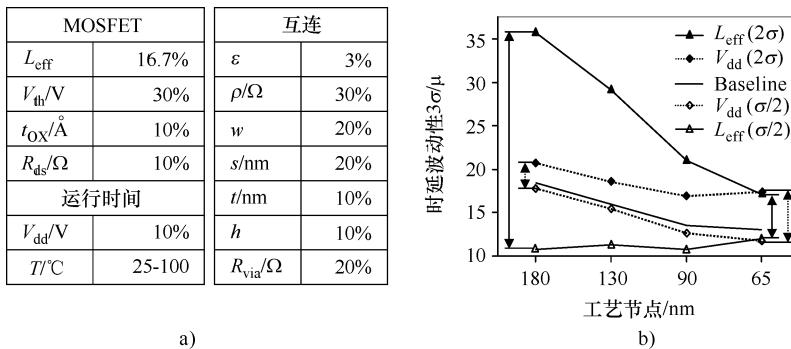

| 11.1.1 电路设计中的参数波动 .....      | 305        |

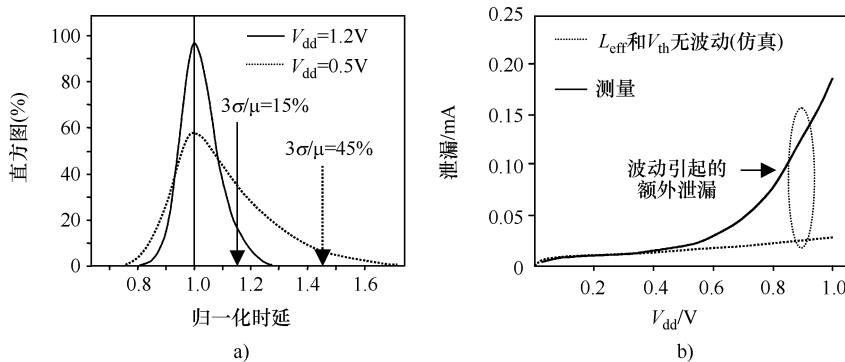

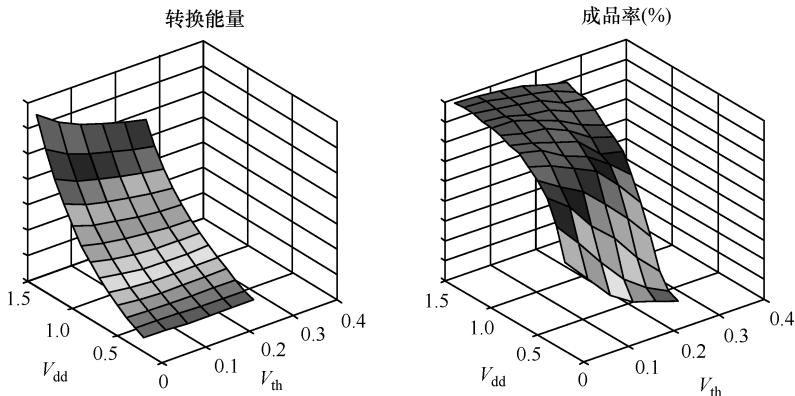

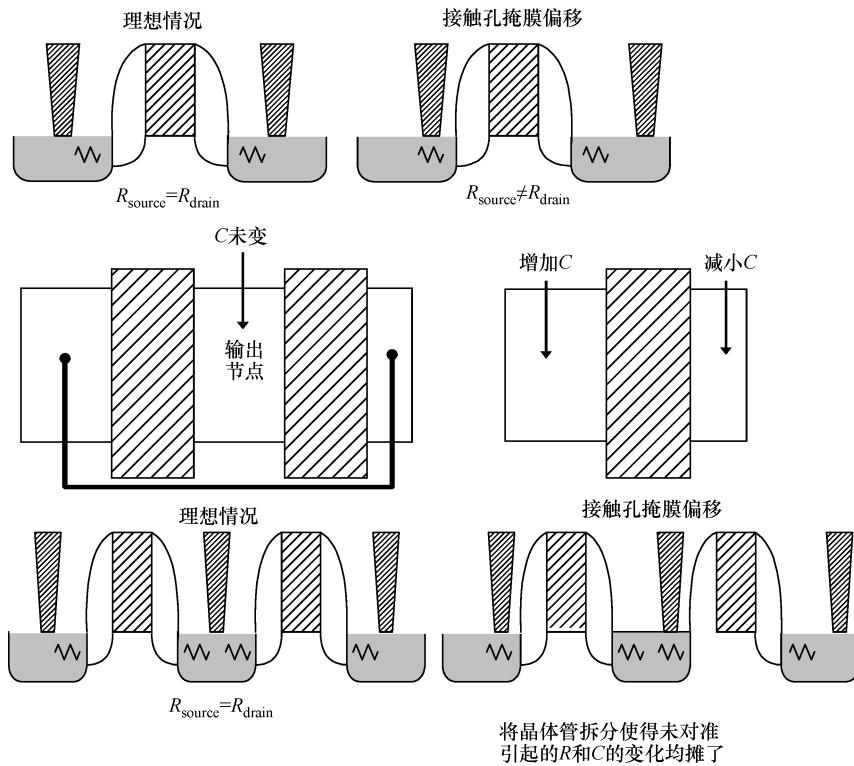

| 11.1.2 对电路性能的影响 .....        | 307        |

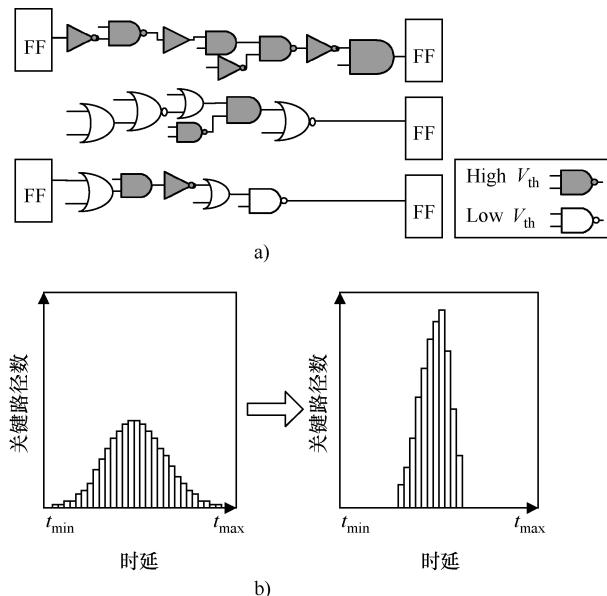

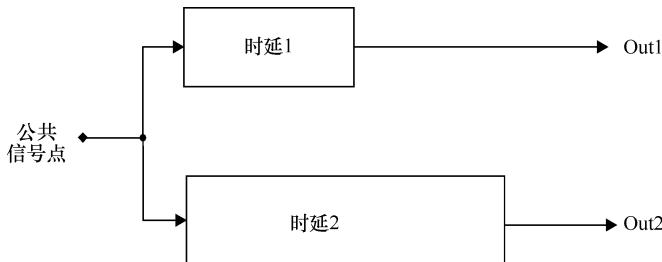

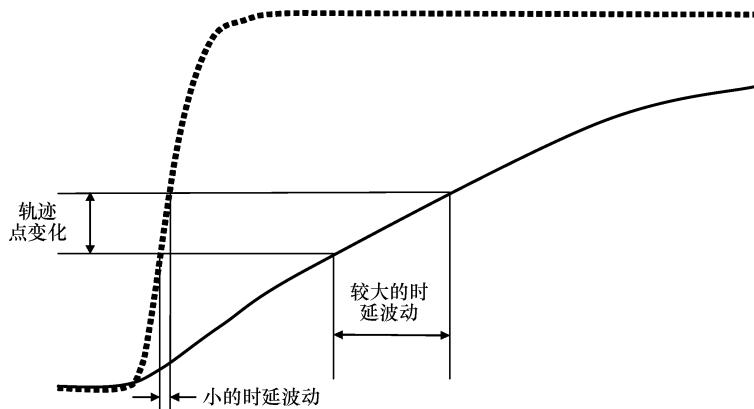

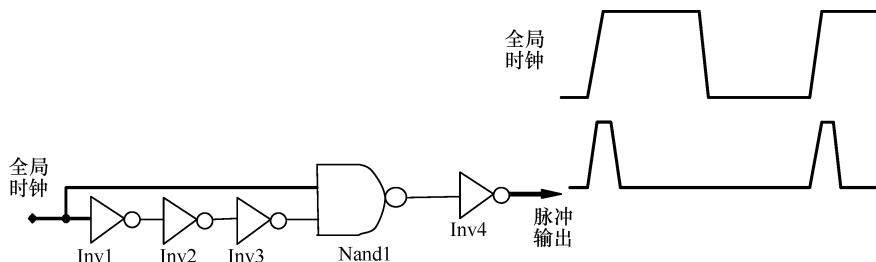

| 11.2 减轻波动影响的策略 .....         | 309        |

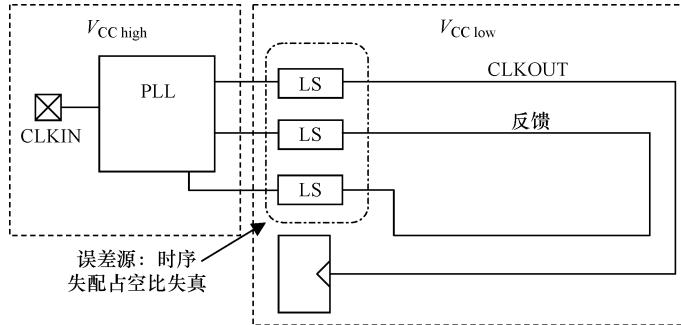

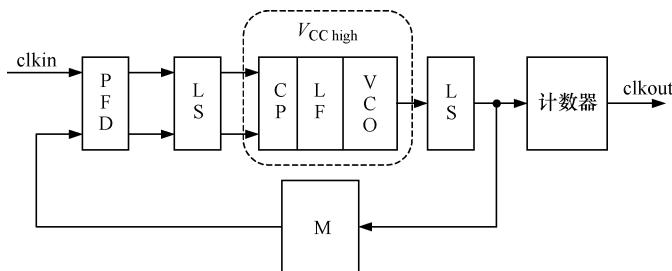

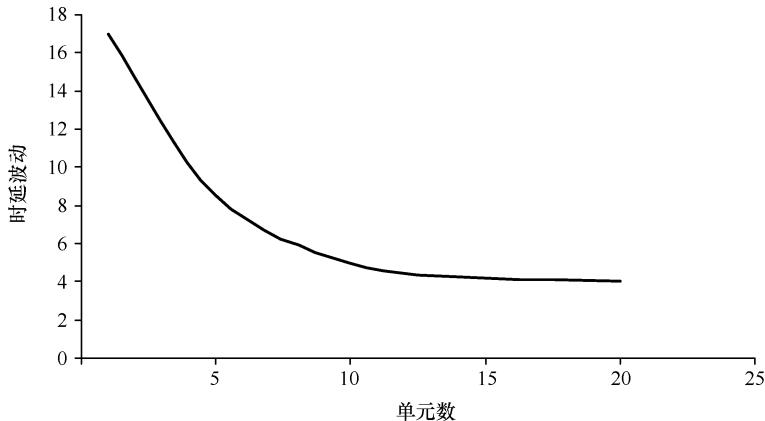

| 11.2.1 使偏斜最小化的时钟分布策略 .....   | 309        |

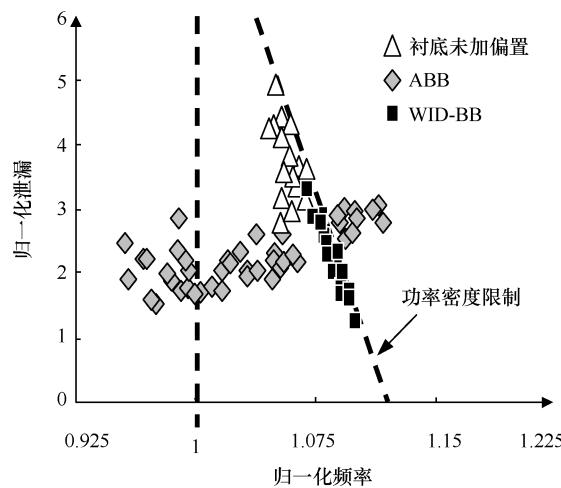

| 11.2.2 针对波动性的 SRAM 技术 .....  | 312        |

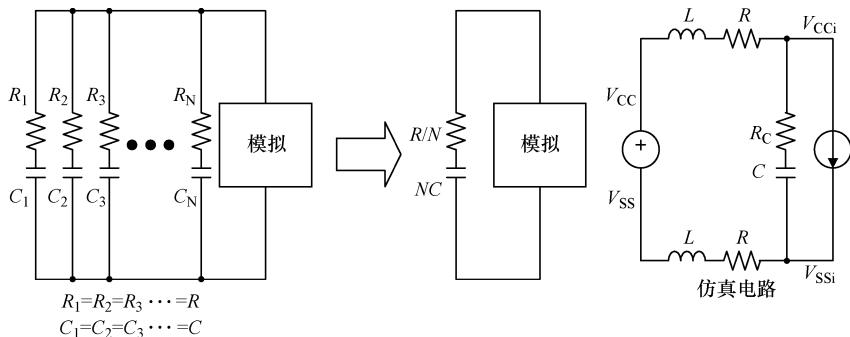

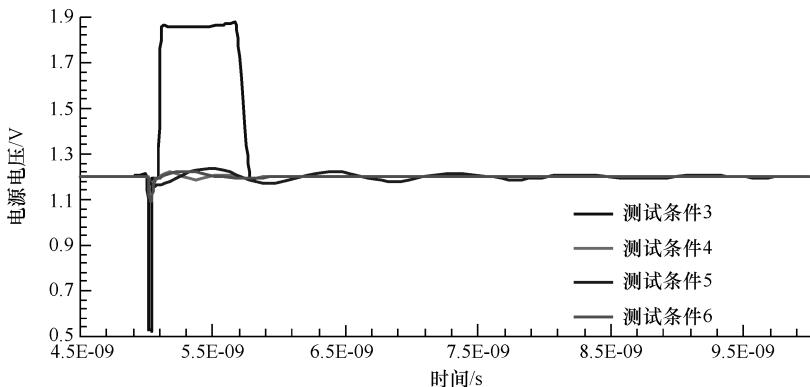

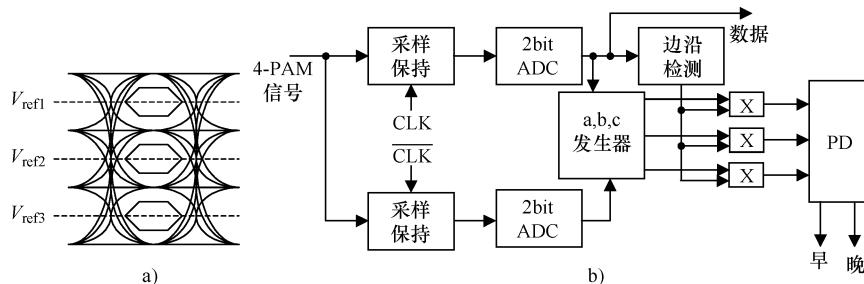

| 11.2.3 应对波动性的模拟电路策略 .....    | 321        |

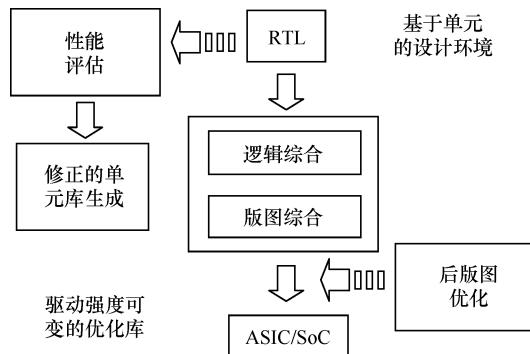

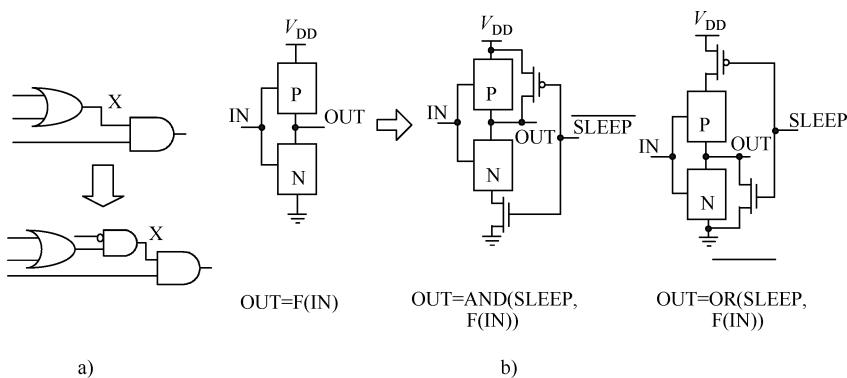

| 11.2.4 应对波动的数字电路策略 .....     | 329        |

| 11.3 纳米 CMOS 工艺角建模方法 .....   | 335        |

| 11.3.1 统计模型的需求 .....         | 335        |

| 11.3.2 统计模型的使用 .....         | 336        |

| 11.4 BSIM4 模型的新特点 .....      | 340        |

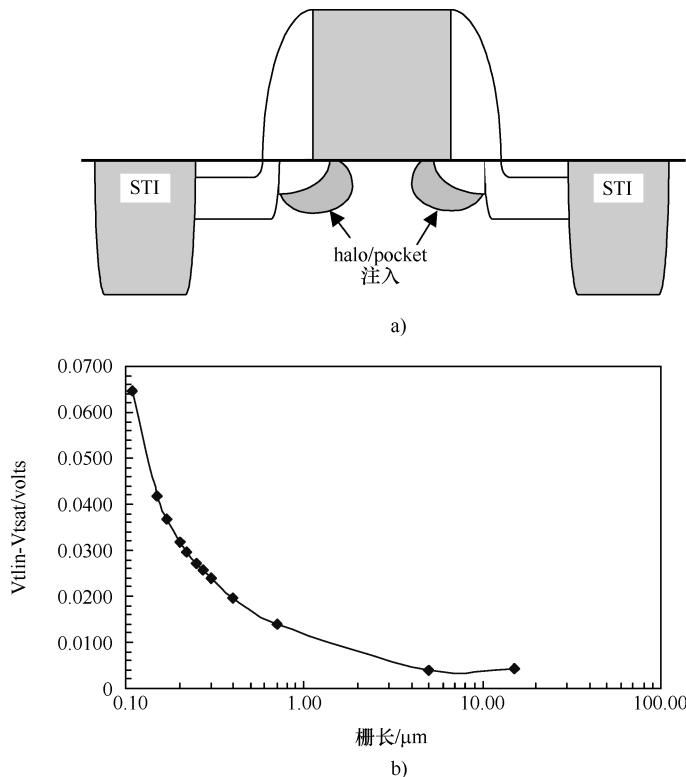

| 11.4.1 halo/packet 注入 .....  | 340        |

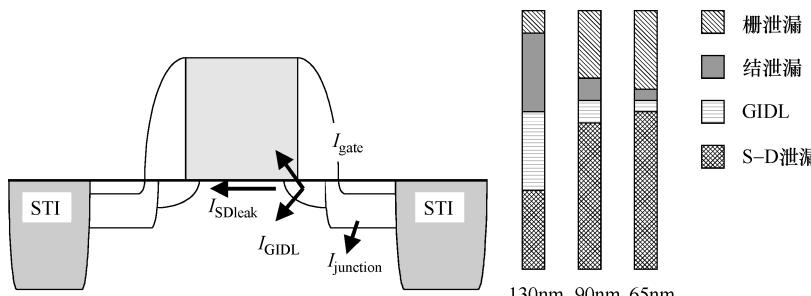

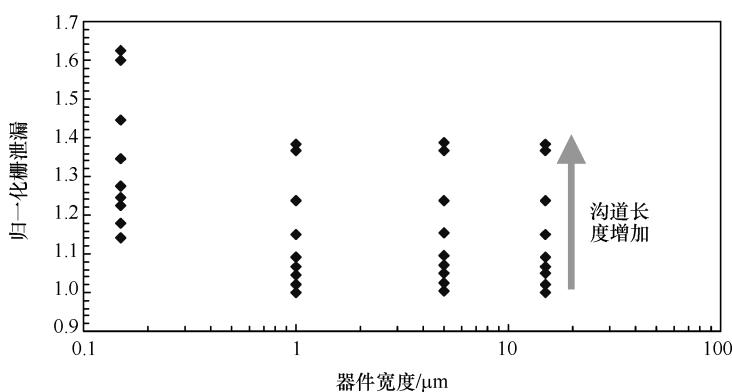

| 11.4.2 栅感应漏极泄漏和栅直接隧穿 .....   | 341        |

| 11.4.3 建模的挑战 .....           | 342        |

| 11.4.4 与建模相关的问题 .....        | 343        |

| 11.4.5 模型总结 .....            | 343        |

| 11.5 总结 .....                | 343        |

| 参考文献 .....                   | 343        |

# 第1章 纳米 CMOS 的缩小问题及内涵

## 1.1 纳米 CMOS 时代的设计方法

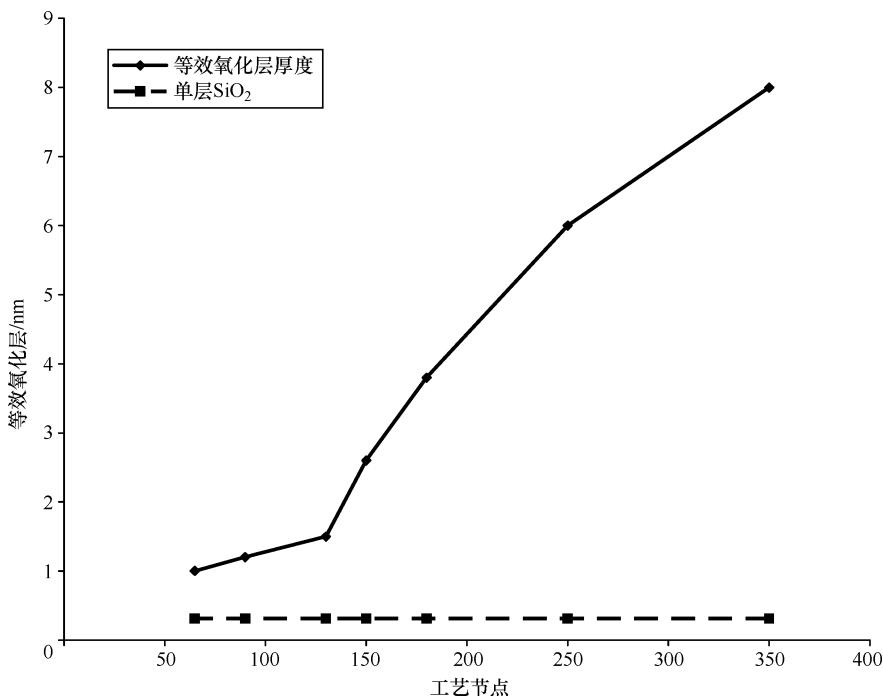

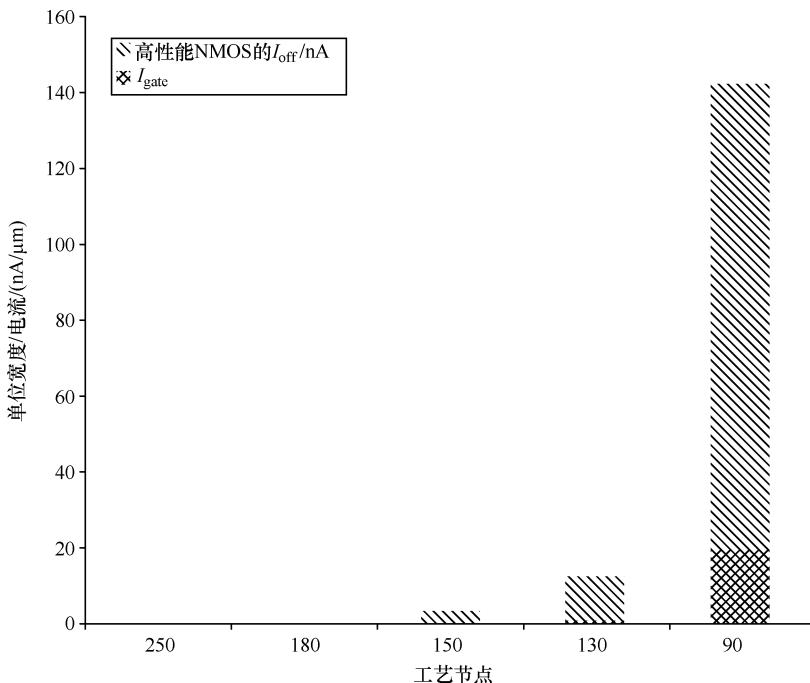

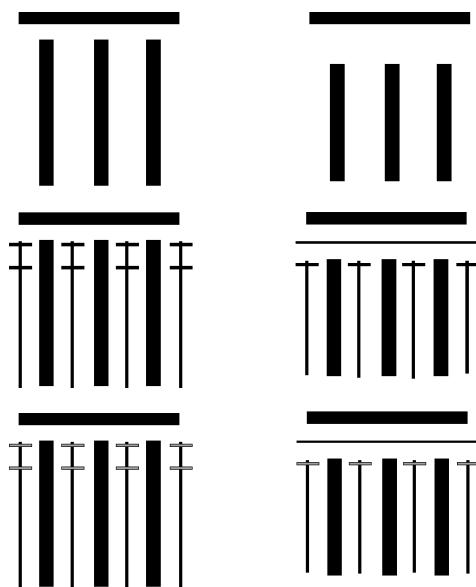

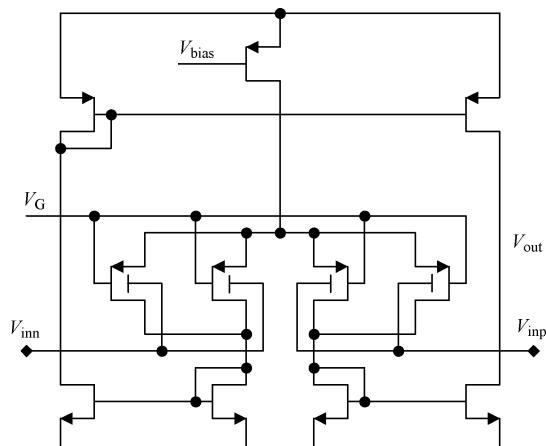

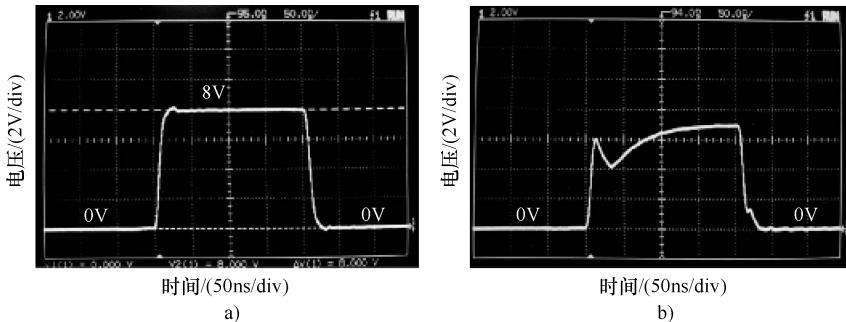

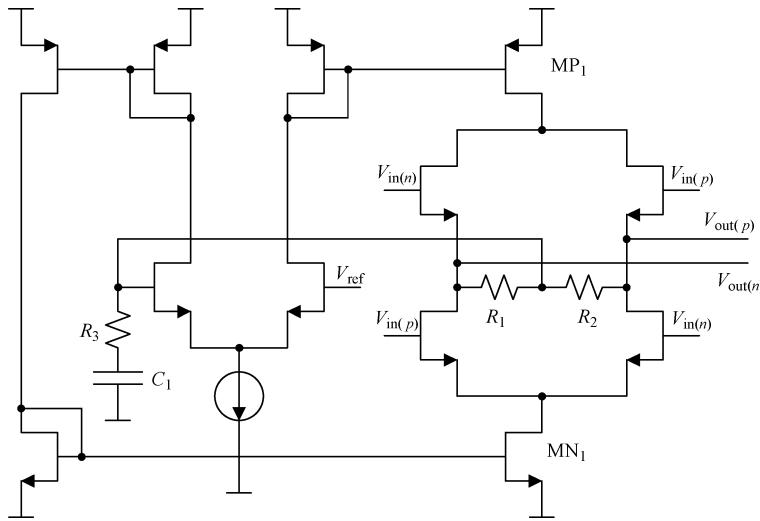

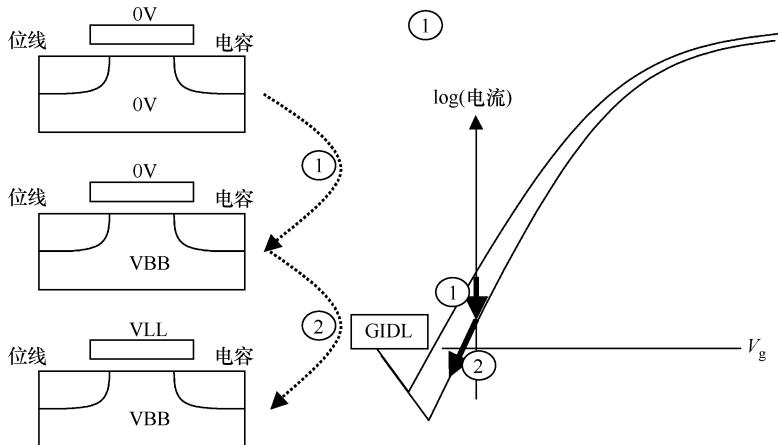

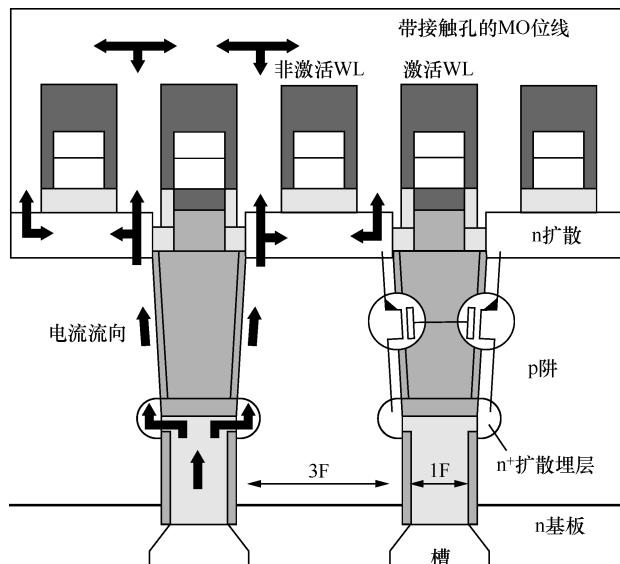

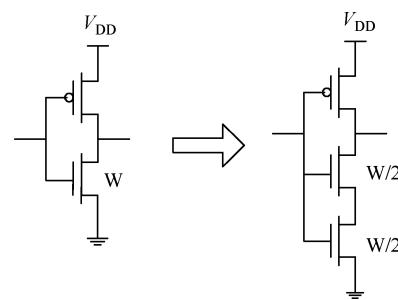

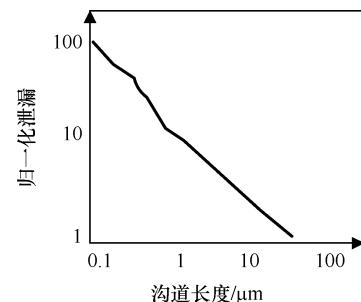

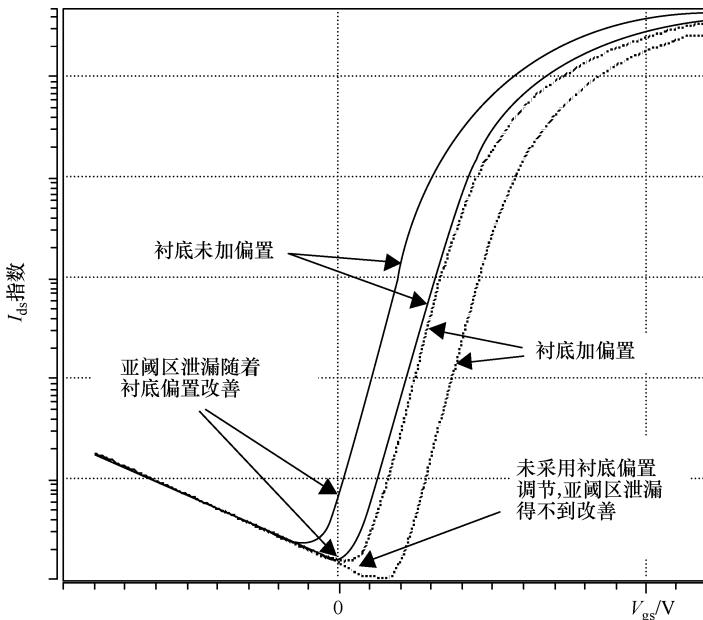

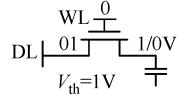

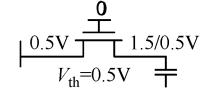

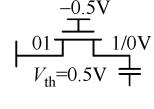

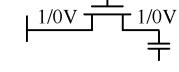

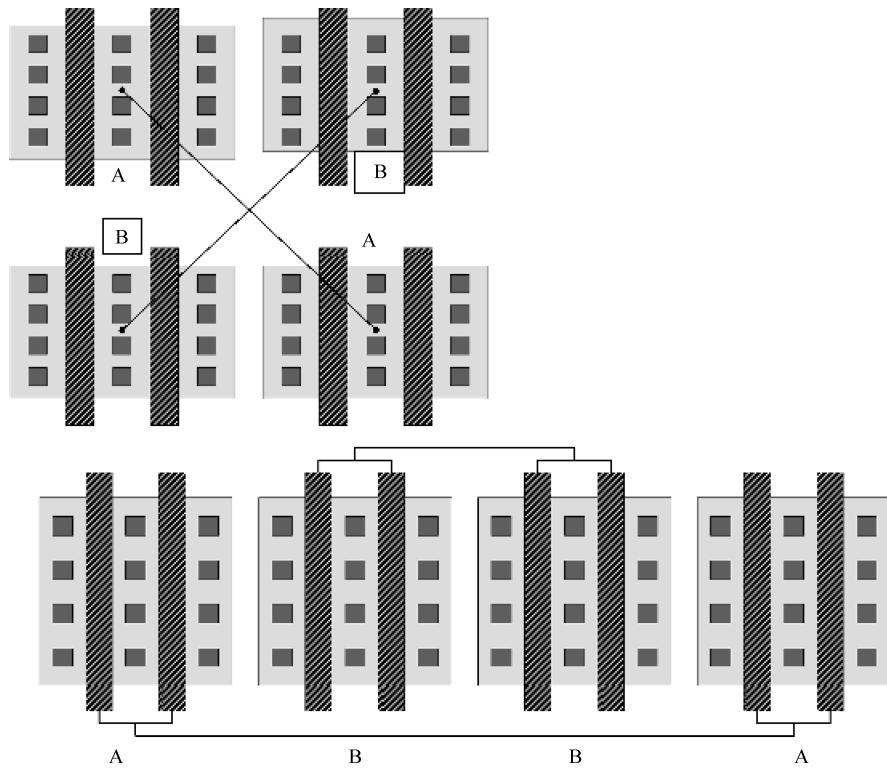

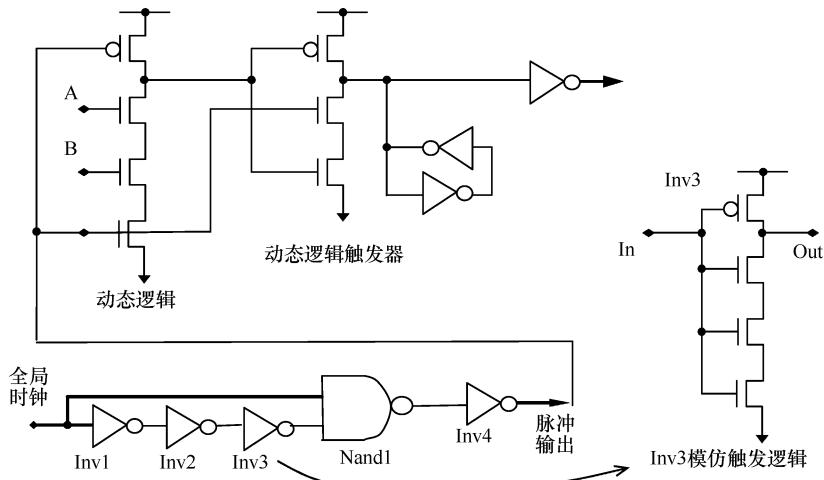

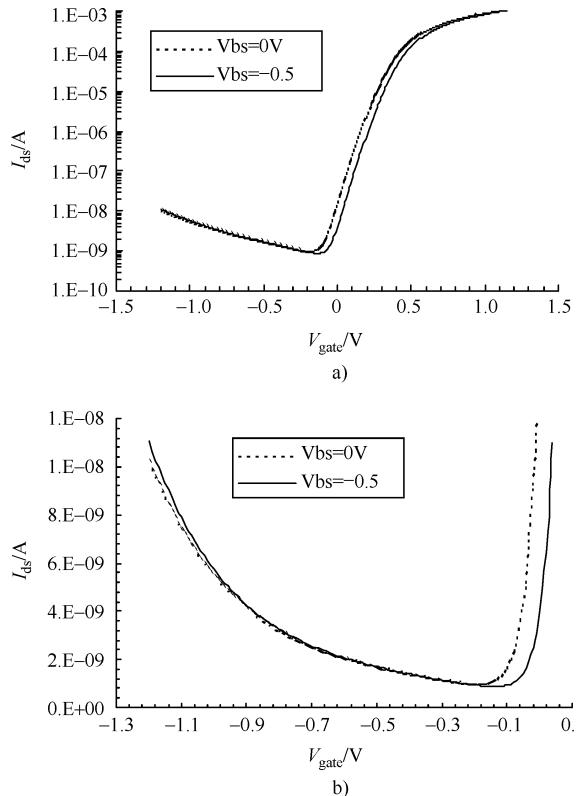

随着工艺特征尺寸缩小到 100nm 节点以下，对于硅集成电路，为了满足功能和高成品率的要求，需要针对工艺波动的增加、互连工艺的困难和其他一些新出现的更严重的物理效应，改变传统的设计方法。纳米 CMOS 中栅氧的减薄（见图1-1）致使栅直接隧穿电流急剧增加。亚阈区泄漏和栅直接隧穿电流（见图 1-2）不再是二级效应了<sup>[1,15]</sup>。设计中将要考虑栅感应漏极泄漏（Gate-Induced Drain Leakage, GIDL）的影响。例如对于 DRAM（第 7 章）和低功耗 SRAM（第 9 章），它们的栅压相对于源极来说是负电位<sup>[15]</sup>，如果不考虑这些效应，得到的 SRAM、DRAM 或者任何其他使用这个技术来减小亚阈区泄漏的电路会丧失功能。某些情况下甚至多路器和触发器也会受到影响。

图 1-1 栅氧化层厚度随工艺节点的变化趋势

图 1-2  $I_{gate}$  和亚阈区泄漏随工艺节点的变化趋势

在功能级需要面对的问题不仅仅是亚阈区泄漏和栅电流，还需要应对高性能电路，如微处理器、数字信号处理器和图形处理单元等芯片中的电源管理问题。电源管理也是移动应用中需要面对的一个挑战。

另外，即使采用增强分辨率扩展技术（Resolution Extension Technology, RET），光刻也会趋于极限。这些新的光刻技术还会使掩膜版费用增加，并且使生产周期更长。经过几次修改才能得到一个值得进行生产的设计，这将明显增加研制费用。过去，处理器设计者一般在验证置信度达到 98% 时就可以提交设计数据，在随后的工艺过程中还可以继续排错，这样一般能够使产品的研制速度快几个数量级，从而使产品投放到市场的时间更快。现在，由于掩膜费用的增加和制造周期变得更长，在获得最低的研制成本和以最短的时间将产品投放市场之间进行折衷，将会相当困难<sup>[28]</sup>。

因为设计规则不能以相同的速率缩小，原先成功的设计在下一代工艺中必须完全重新设计，除非设计者可以预见设计规则的变化，并且在针对原先尺寸较大的工艺技术进行设计时就有意识地牺牲密度以便在下一代工艺技术中可以缩小设计而无需重新设计物理版图。但是仍然必须对关键电路进行再次仿真。如果设计者使用易于缩小的电路技术，也能实现版图的最小化。为此需要预先的计划以及对设计规则进行折衷从而获得一个可以缩小的设计，所以，可以通过工艺缩小以

及很少的重新设计（如果需要的话），采用中等的投入提升性能，获得一个速度更快、面积更小的芯片。预测设计规则变化趋势的关键是要对工艺难点和工具设备的制约具有充分的理解，这将会在以后几章中详细讨论。

## 1.2 使得性能改善得到延续所必需的创新

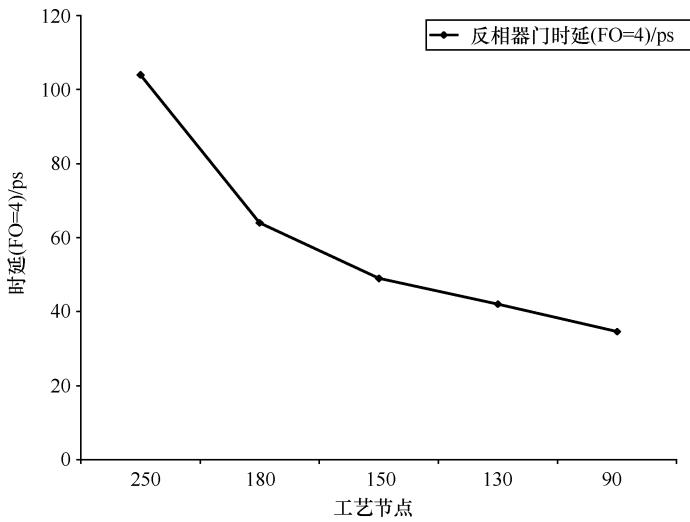

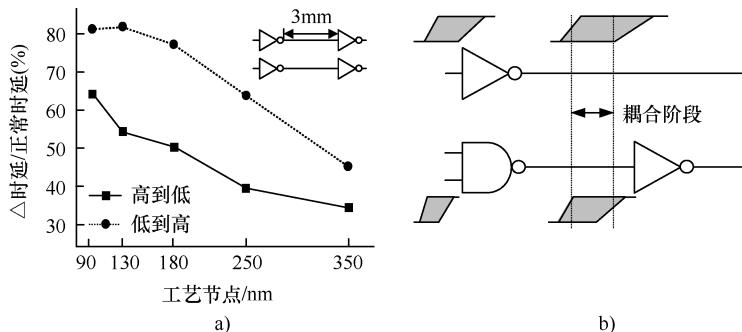

晶体管的品质因数现在已经偏离了与栅长倒数之间的关系。如图 1-3 所示，4 扇出延迟随着现代工艺技术进步而变小的趋势在减小。另外，芯片总体互连线并不能缩短，而  $0.1\mu\text{m}$  以下的互连线电阻正在以指数关系增长。这主要是由于表面散射和窄槽中晶粒尺寸的限制，导致载流子散射和迁移率退化<sup>[2]</sup>。目前栅介质的厚度已经接近原子尺寸，在 90nm 节点中栅氧化层约为 1.2nm，为五层原子<sup>[22]</sup>。如图 1-1 所示，栅氧在趋于其一层原子厚度的极限过程中，减薄的趋势正在减缓<sup>[26]</sup>。源漏扩展电阻（RSD）在晶体管“导通”电阻中占据的比例正不断增大。在 130nm 节点中，源漏扩展掺杂已经增加得非常显著，减小扩展电阻的能力必须与其他短沟效应，如热载流子注入（Hot-Carrier Injection，HCI）以及由能带到能带隧穿引起的泄漏电流，进行折衷。源漏扩散层已变得很薄以致于注入处于饱和水平，电阻不再能减小，除非改用其他掺杂剂<sup>[21]</sup>。

图 1-3 棚延迟与工艺节点的关系

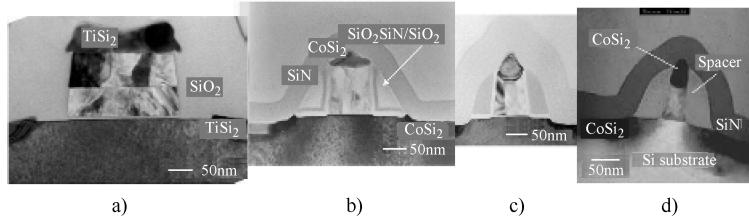

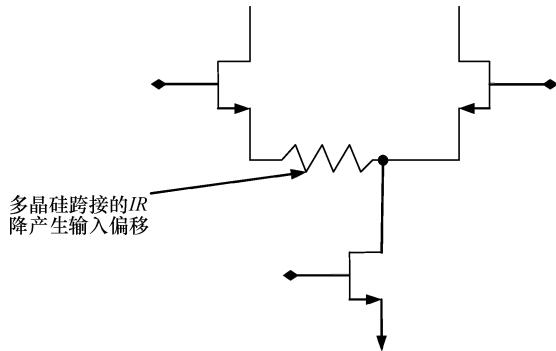

现在的多晶硅连线变得相当窄，130nm 工艺约为 70~90nm，而 90nm 工艺为 50nm（见图 1-4）。这要求在多晶硅方阻与源漏泄漏之间进行折衷。为了降低较窄多晶硅连线的电阻，要求多晶硅形成更多的硅化物。因为多晶和源漏扩散都会发生硅化过程，增加多晶硅的硅化物会导致源漏扩散发生更多的硅化消耗。由于

源漏采用超浅结，源漏扩散硅化消耗会导致穿透。在 65nm 工艺中，正在研究在生产过程中采用抬高的源漏技术以缓解这种效应，并且可能用于 90nm 工艺。一些厂商可能将这种在线技术应用到目前建立的 90nm 工艺过程中。

图 1-4 晶体管 TEM [a)、b)、d) 源于 NEC 和 Trecenti/Hitachi; c) 源于 Advanced Micro Devices, Inc., 引用已得到许可]

a) 250nm b) 130nm c) 90nm d) 65nm

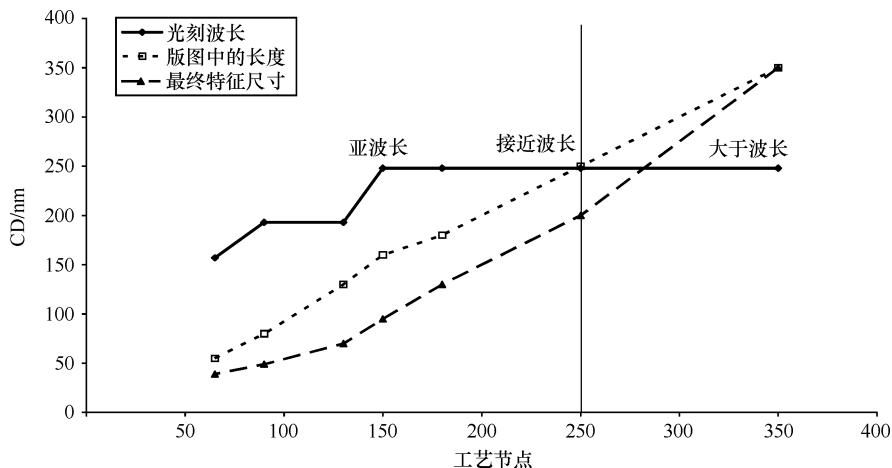

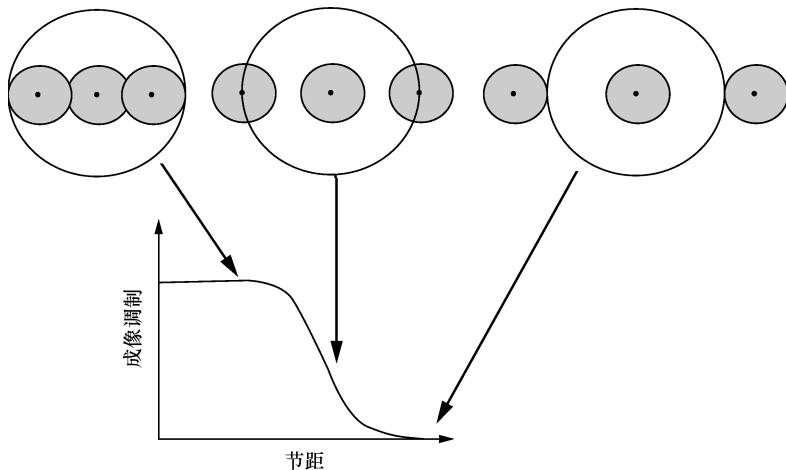

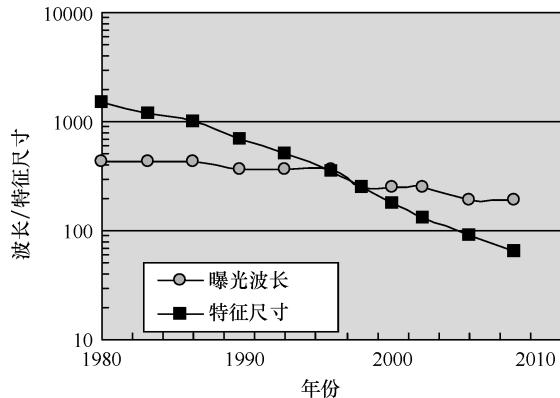

从 180nm 工艺开始，特征尺寸（多晶）已经达到亚波长阶段，即特征尺寸小于光刻中使用的紫外线波长（UV）。随着下一代工艺的发展，这种差距正在扩大（见图 1-5）。在 65nm，即使有先进的 RET，193nm 光刻也已经走到了尽头。为了增加 193nm 扫描器的分辨率。正通过研究增加了光刻系统的数值孔径（Numerical Aperture, NA），包括采用浸入式光刻。关于光刻方面所面临的挑战将在第 3 章详细描述。157nm 的挑战和远紫外线（EUV）光刻是新的里程碑，并且会增加设备和掩膜费用以及生产周期。如果 157nm 光刻不能用于 65nm，亚波长差距将进一步扩大。电路和物理设计者将不可能再简单地采用工艺设计规则进行设计，也不可能指望生成一种可缩放的功能设计，只采用一组掩膜版就能满足设计目标可变的要求，例如高性能和低功耗的移动应用。设计者必须明白什么时候采用宽松的规则，

图 1-5 各代工艺节点中的多晶 CD 与光刻 UV 波长

而不是简单地对整个设计放宽规则，否则会给物理缩小带来负面结果。

用来制造新结构的材料和工艺的组合所产生的集成复杂度需要同时从设计和版图多方面考虑解决方案<sup>[20]</sup>。工艺工程师和技术开发人员不能解决所有这些在 sub-100nm 缩小中出现的问题，这些问题包括集成的复杂度以及制造和工艺控制方面的困难。我们将给电路和物理设计者在应对 sub-100nm 工艺中遇到的困难方面提出可以采用的技术建议，并且帮助他们加深对设计中采用的工艺技术的理解。同样，对工艺工程师来说，理解物理设计基础也非常重要，从而可以改进技术，满足一个可以持续实现物理和性能缩小，并且可缩放的鲁棒设计的需要。

技术设计者需要进行一些革新，在工艺线上采用一些新工艺。开发新材料也是必需的。一个无可争议的事实是，仅由物理缩小获得性能提升的方法已经到达了一个拐点，并且即便可能的话，也不能提供更多的改进。为了继续进行性能提升，在研究工作中已经有一些创新的改进，但更多的是处于开发中。绝缘层上硅(SOI) 技术已经证明可以将晶体管的性能提高约 20% ~ 30%，数值的差别在于数据来源不同。作为技术选择，一些微处理器已经采用 SOI。实验证明，采用宽松的锗化硅衬底的应变硅可以将载流子迁移率提高达 30%。然而，这些衬底材料成本高，并且易于产生位错缺陷，因此还没有被广泛应用。

在载流子迁移率提高方面，还有一种已经证实可以采用的硅上应变方式的革新是使用氮化硅“帽”层。漏源扩散上的压应力在这一层产生应变，由于漏源扩散相互隔开，就在晶体管的沟道中产生应变。但是，它仅适用于 90nm 及其以下工艺，因为沟道必须非常接近漏源应力。长沟器件几乎不会获得好处。即使在 90nm 工艺的晶体管中，如果版图上沟道长度大于最小值，也会使这种获益减小。不幸的是，在 130nm，这种能提高性能的选项受到了限制。这个技术将会是产生应变的首选方式。因为它不要求特殊的衬底，并且迄今为止也未发现有层错。其最大的优点是，不需要增加工艺步骤，只需要调整工艺顺序。

采用铜互连替代铝互连使得因尺寸缩小带来的性能提升不断接近极限所承受的压力获得了短暂的缓解。这是一个革新需要引入新材料的实例。许多其他得到普遍认可的新技术尚处于从研究到试用阶段，包括提高源漏 (SD) 扩散、双栅 FET、FinFET、高  $k$  栅介质和金属栅<sup>[4]</sup>。它们能否最终得到成功应用取决于风险收益比，以及成本、集成与制造复杂度和制造周期。

## 1.3 sub-100nm 缩小的挑战和亚波长光刻综述

### 1.3.1 后道工艺的挑战（金属化）

金属电阻 互连线宽度小于  $0.1\mu\text{m}$  时，电阻率会随着线宽的减小以指数形

式增加。对较窄的互连线来说，高电阻率阻挡层材料占据了导体横截面面积的较大部分。由于表面散射导致的电子迁移率减小成为电阻率增加的因素之一<sup>[2]</sup>。窄互连中形成的晶粒更小，在填充凹槽时不能再结晶为更大的晶粒，使得电阻率进一步增大。

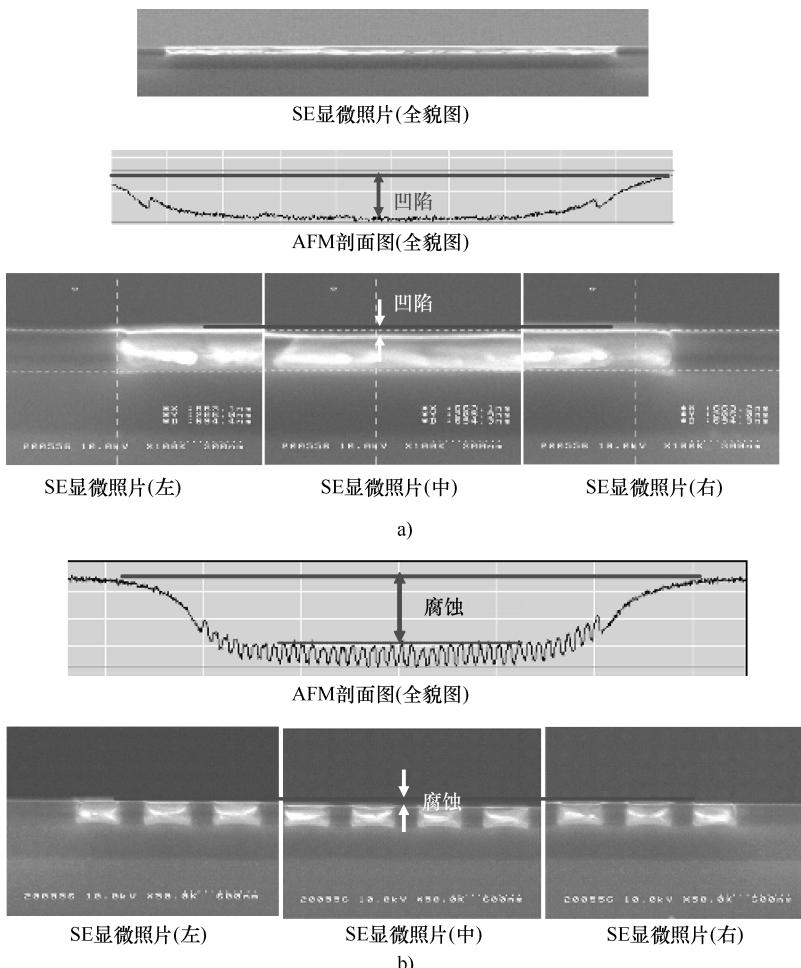

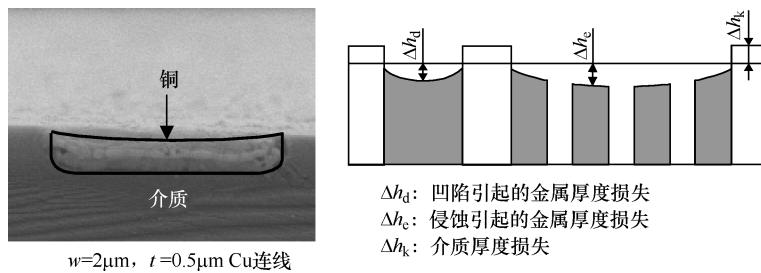

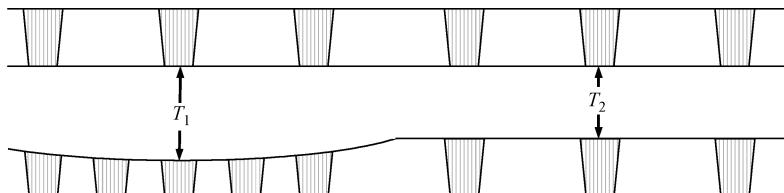

另外，阻挡层和凹槽（互连线宽度）特征尺寸（Critical Dimension, CD）的变化导致电阻的变化更大。这些因素与化学机械抛光（Chemical-Mechanical Polish, CMP）形成的凹陷和腐蚀，以及光刻和刻蚀变形一起会引起互连线电阻的进一步变化<sup>[19]</sup>（见图 1-6）。

图1-6 a) 互连凹陷：较宽互连线的面积 b) 互连腐蚀：互连线和间距面积

(图片来源于 Trecenti/Hitachi)

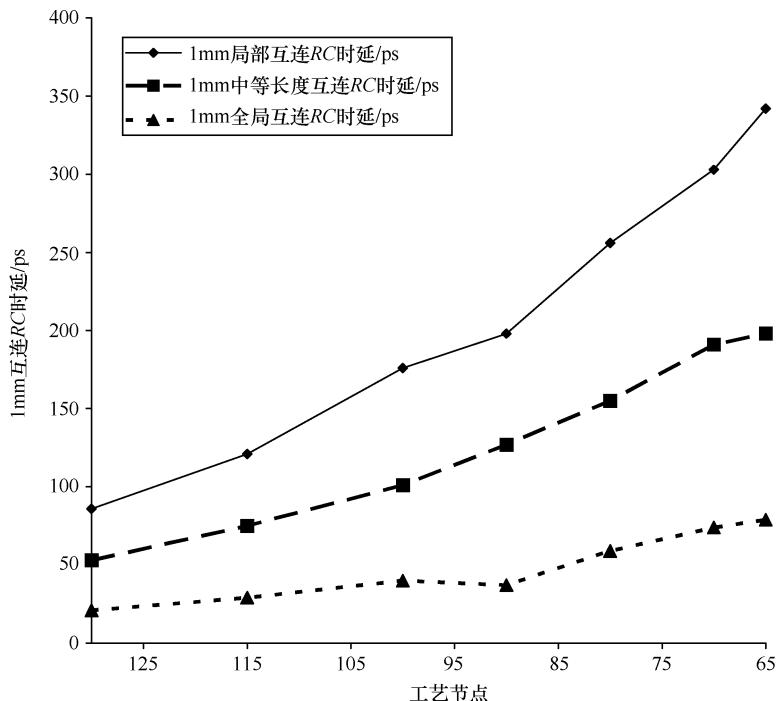

130nm 工艺的互连  $RC$  值不断增加，并且对小于 130nm 的情况，局部和全局互连都变得更差。像上面解释的那样，随着线条尺寸的减小，电阻率不断增加（见第 2 章图 2-25），而电容并未减小。其结果是，即使局部互连线的长度变得越来越短，而局部互连线的时延却在增加（见图 1-7~图 1-9）。虽然线条尺寸在减小，但是因为新的设计中增加了更多的功能，因此芯片面积并没有减小，全局互连线的长度也就没有减小。例如，180nm 工艺生产的 Pentium 4 Willamette core 有 4200 万个晶体管；而 130nm 工艺的 Northwood core 的晶体管数达到了 5500 万个。这是因为在 Northwood core 中 L2 缓存从 256KB 增加到了 512KB。随着工艺的发展，在一个时钟周期里信号可到达的区域与芯片面积之比正在减小。对一个采用先进工艺的设计来说，时钟频率在增加，而晶片的尺寸并没有减小，使这一问题更加严重。

图 1-7 互连时延与工艺节点的关系

**互连介电常数** 低  $k$  介质使纳米 CMOS 中互连线缩小成为可能，但是随着互连线宽度和间距不断减小，使得低  $k$  介质的使用更加困难。这是由于间距较窄互连线之间的经时介质击穿 (Time-Dependent Dielectric Breakdown, TDDB)，使得低  $k$  介质存在着潜在的泄漏和可靠性风险。封装工艺带来的问题要求芯片上形成一层“硬外层”，使得管芯具有足够的机械强度，能够承受封装工艺施加给芯片

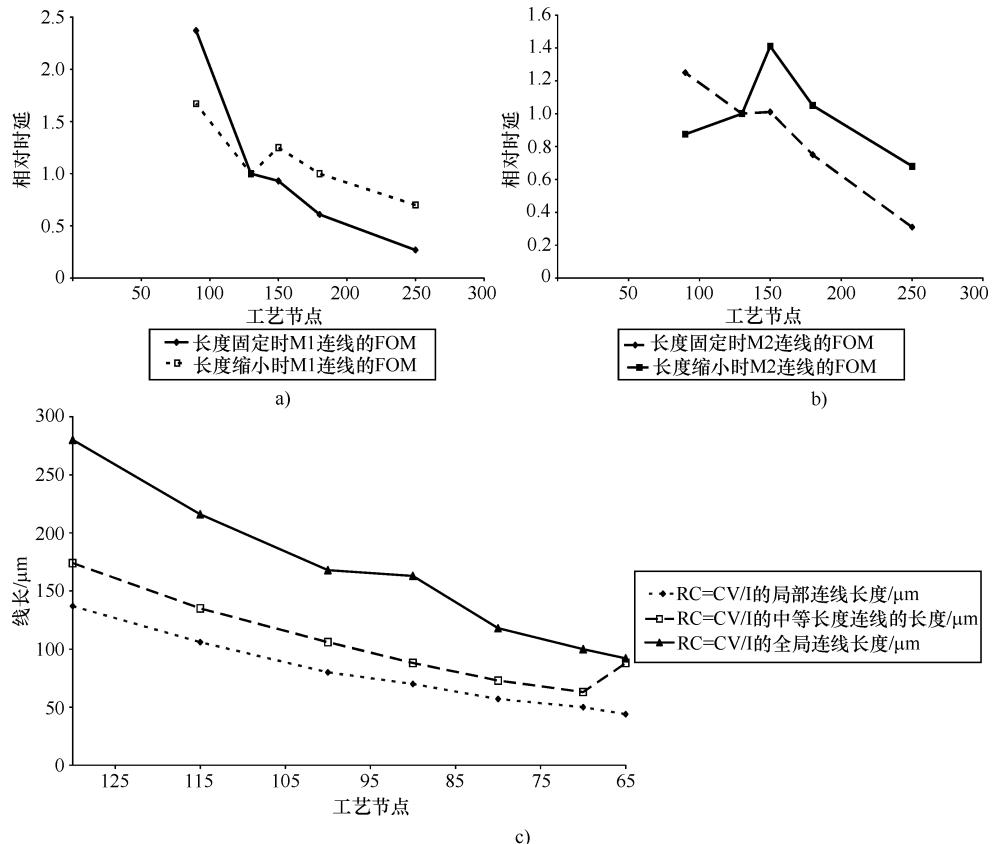

图 1-8 a) M1 (局部互连) 的品质因数 (无 Miller, 无重复)

b) 中等长度互连的品质因数 (无 Miller, 无重复)

c) 等效于 NMOS CV/I 的互连线长度与工艺节点的关系

的应力。这种硬外层的要求意味着位于层叠金属上面的几层需要采用较高介电常数的介质材料，这会稍稍减小低  $k$  金属技术的有效性。在 8 ~ 9 层金属的工艺中，低  $k$  介质将被限制到只能用于 4 ~ 5 层。具体情况取决于上层金属的使用方法。一般地，上层金属被用来作功率分布。在大多数设计中，它们也被用作时钟分布层，因此就增加了时钟网络的功耗并且也要求更多级去缓冲来自 PLL 的信号，这会导致更高的时钟偏差。

**低  $k$  互连的应用严重缓慢** 低  $k$  技术的引入比较缓慢的原因在于铜互连阻挡材料带来的问题、应对封装过程中应力的机械完整性问题以及制造过程中的一系列问题。这使得几个厂商转而采用氟硅玻璃 (FSG) 介质。

低  $k$  介质形似果冻并且多孔，因此很容易受潮、吸附杂质并且气体也容易渗透。因为材料很软，很容易受 CMP 损伤，引起成品率降低和侵蚀，进而影响互

图 1-9 棚时延和互连时延与工艺节点的关系

连线电阻率。低  $k$  介质的导热性不良，这样会使互连的抗电迁移（EM）特性退化，在一定程度上抵消了一些铜互连 EM 特性好的优点。

**互连的品质因数 (Figure of Merit, FOM)** 对每代工艺节点，按照其设计规则确定的互连线的 FOM 一直在下降（见图 1-7 ~ 图 1-9）。过去，晶体管性能滞后。现在，我们已经到达了这样一个转折点，即互连性能已成为芯片性能的制约因素。局部互连性能未得到改善，而全局互连实际上正变得更慢，特别是如果增加了附加的功能使得互连长度没有减少<sup>[12-14]</sup>。不管工艺技术如何缩小，由于在新的设计中功能不断增加，芯片尺寸却没有减小，总是维持在与以前设计相同的尺寸上。其他情况下，例如微处理器，不管工艺技术如何缩小，芯片尺寸实际上都在增加。尽管工艺技术在缩小，如果芯片变得更大，在不同模块之间就需要全局互连传递信号。

已经预见到的是，当工艺技术缩小时，时钟频率将增加，而一个周期中可达到的区域与总芯片面积的比率会下降<sup>[13]</sup>。为了使互连主宰的路径可以实现更好的缩小并且不限制频率，就迫使设计者在全局互连上插入更多的中继器，并且有时在全局信号中必须采用流水线方式。然而，这将增加芯片面积、功耗和时钟负载<sup>[14]</sup>，也增加整个芯片时序的复杂性。更高的时钟负载将导致更高的时钟偏差。由于采用流水线，就增加了信号的等待时间，这对其他的微结构也会产生影响。

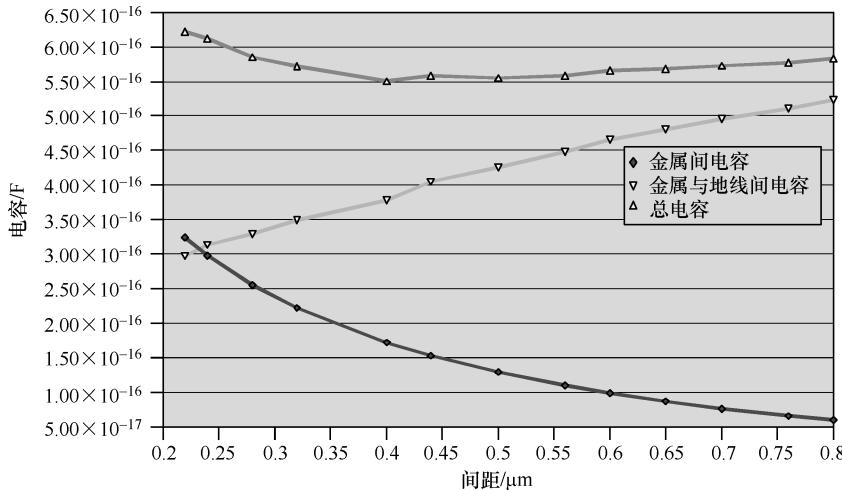

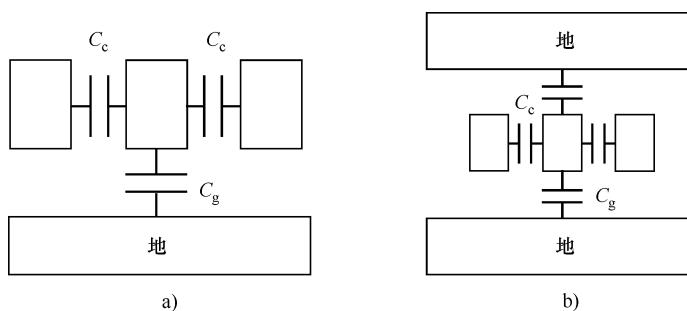

这些问题迫使设计者只好放宽节距，以改善全局互连线的性能和信号完整性。增加互连的节距可以减小线间耦合，但是电容将逼近渐进值，即随着互连线之间间距的进一步增大，电容将不再会随之减小（见图 1-10）。使得电容为最小时的间距还与层间介质的厚度有关。工艺技术进一步缩小到小于 130nm 节点时，由于性能问题和信号完整性问题，互连密度几乎不会得到改善，这将要求对一些互连需要采取屏蔽措施，而对另外一些互连需要增大互连之间的间距。这样，对复杂芯片进行布线，会要求采用更多的金属层。

图 1-10 金属-金属电容与间距的关系

**接触孔和通孔不能进一步缩小** 对大多数 130nm 技术来说，接触孔尺寸已经是  $0.16\mu\text{m}$ ，而通孔尺寸是  $0.2\mu\text{m}$ 。在未来的工艺中，很难使它们缩减得更多，它们将不能与其他特征尺寸一样以相同的速率缩小。另一个限制因素是接触孔和通孔电阻，随着接触孔和通孔尺寸的缩小，电阻将上升。

130nm 节点中，接触孔和通孔这两层已经要求采用光学邻近修正（Optical Proximity Correction, OPC）和相移光刻。这些层掩膜版的数据以及掩膜版制作费用已经是其他不需要 OPC 和/或相移层次的两倍<sup>[5]</sup>。

### 1.3.2 前道工艺的挑战（晶体管）

**晶体管性能** 晶体管的品质因数现在正偏离与栅长倒数成正比的关系。导致这一结果的主要因素是：

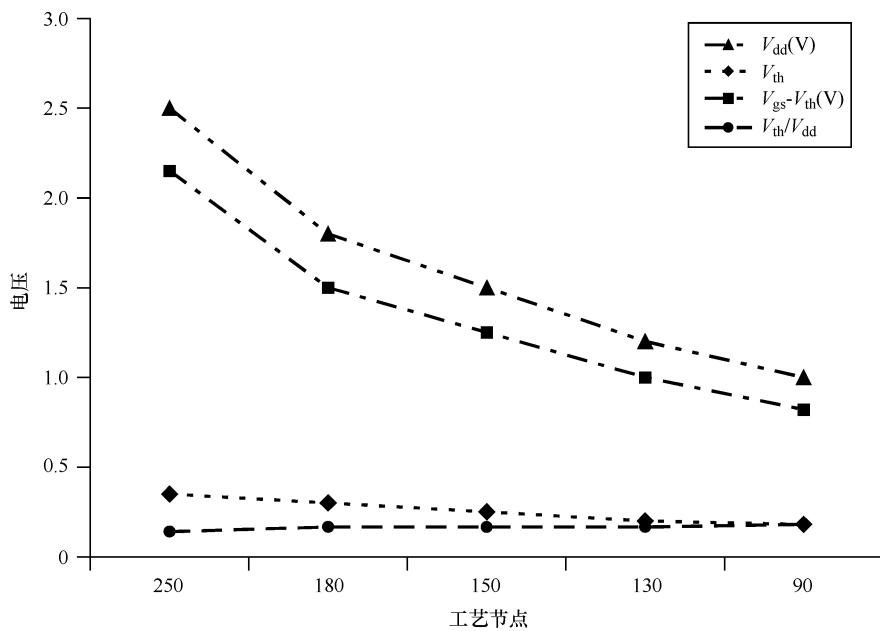

- $V_{\text{gs}} - V_{\text{th}}$  不断缩小，而  $V_{\text{th}}/V_{\text{dd}}$  越来越大（见图 1-11）。

- 作为晶体管总导通电阻一部分的 RSD 的作用正变得更大，导通电阻部分由多晶栅与接触孔之间的间距以及 RSD 决定。

- 浅结正使得掺杂水平达到饱和。使得RSD没有进一步减小的可能；同时，结电容却不断增加。

- 由于电流的聚集，更薄的源和漏扩散使得RSD进一步增大。

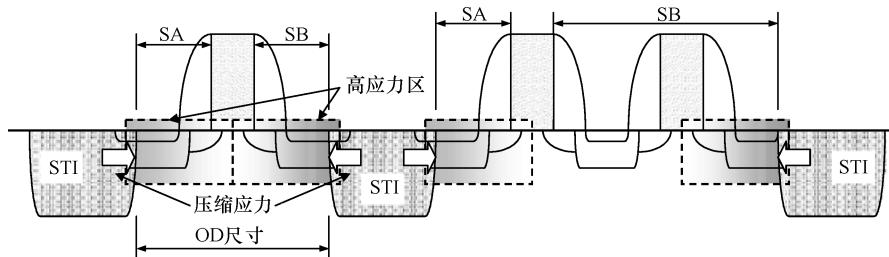

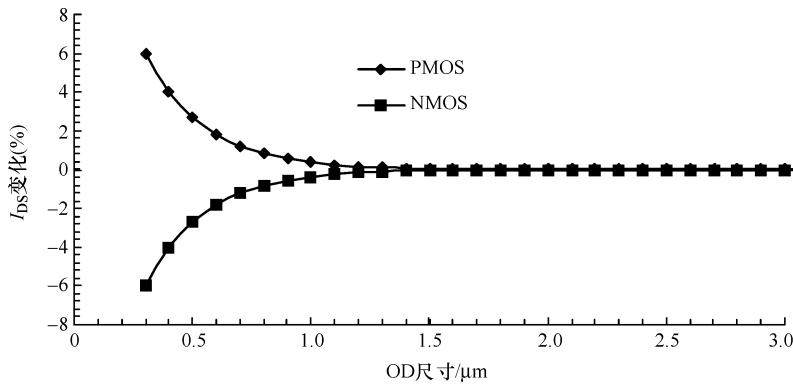

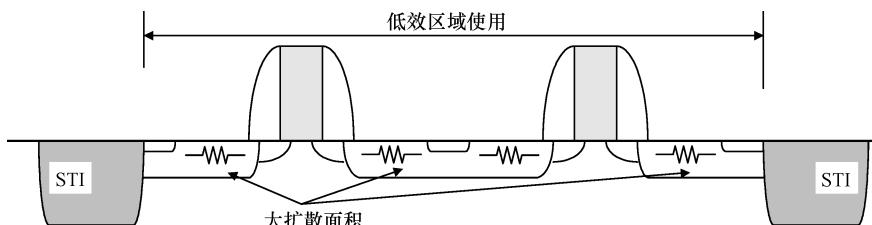

- 浅沟槽隔离（Shallow Trench Isolation, STI）应力感应的迁移率退化更加显著，虽然PMOS晶体管在STI应力下稍有改善，而NMOS晶体管则受到消极影响<sup>[10,11]</sup>。

- 即使更小尺寸晶体管采用STI， $\Delta W$ 也变得重要。

- 现在漏电容的减小慢于面积的减小。

- 对小几何尺寸器件，掺杂损失和掺杂的统计波动增加了器件的波动性：输入/输出、模拟和存储器设计对此特别敏感。

- 为了控制漏感应势垒降低（Drain-induced Barrier Lowering, DIBL）效应而增加的沟道掺杂浓度则减小了载流子迁移率，而增加了体效应。

- 薄栅氧导致杂质穿透，将影响PMOS的驱动电流<sup>[6]</sup>。

- 随着栅氧厚度接近单层二氧化硅厚度，栅氧的缩小也变得越来越慢了（见图1-1）。

图1-11 栅驱动与工艺节点的关系

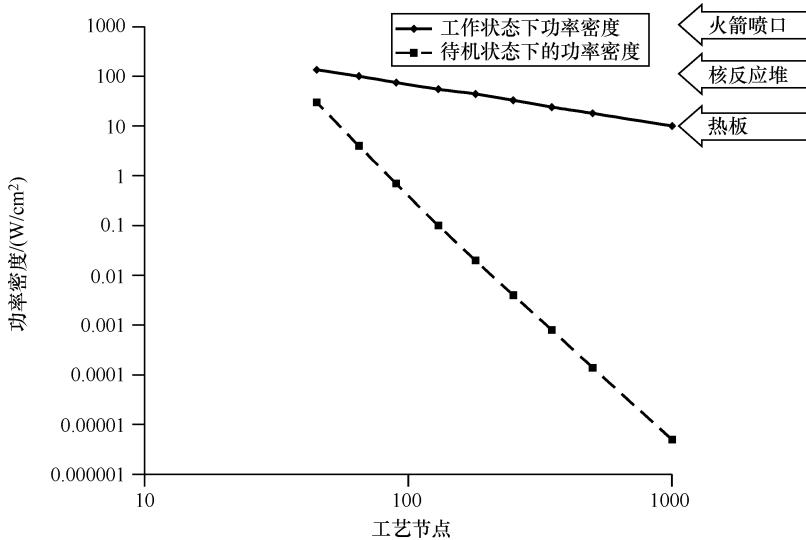

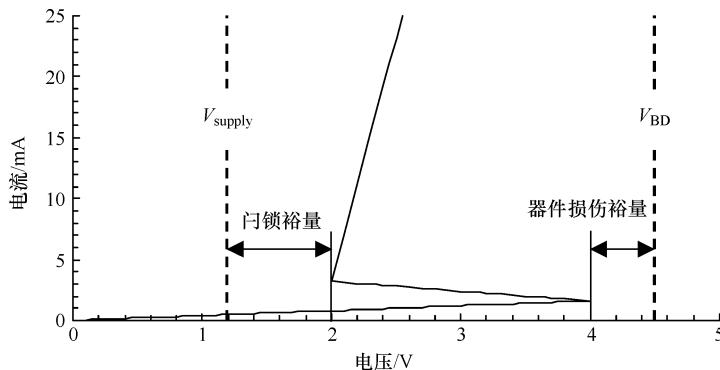

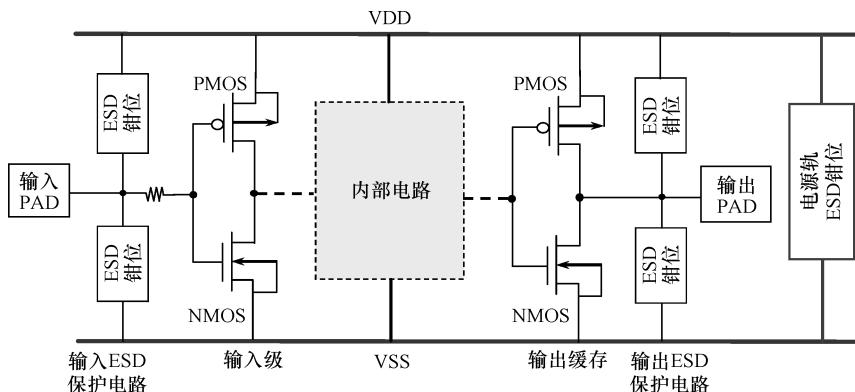

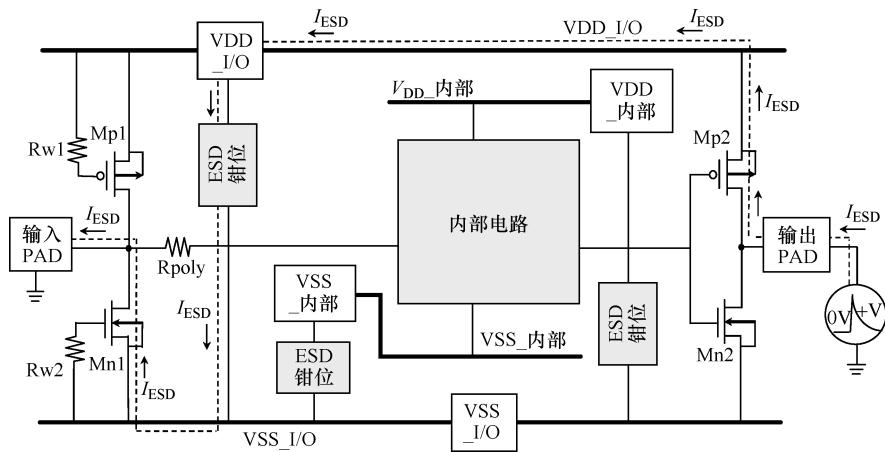

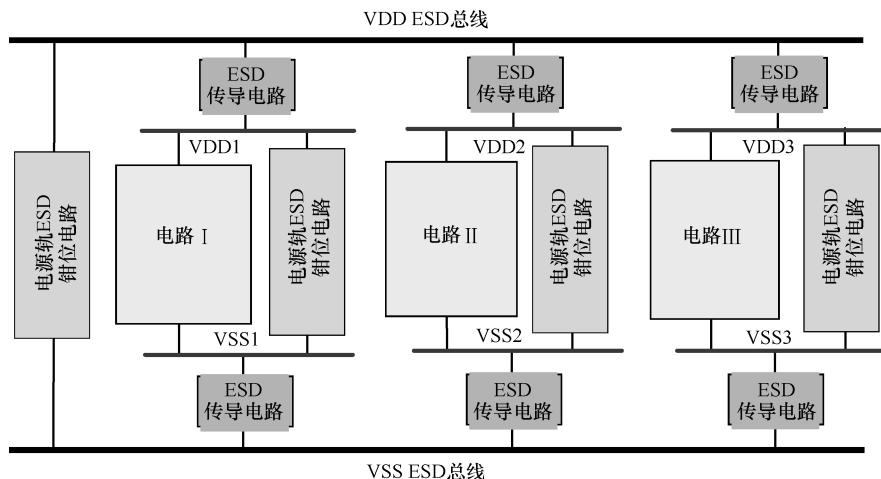

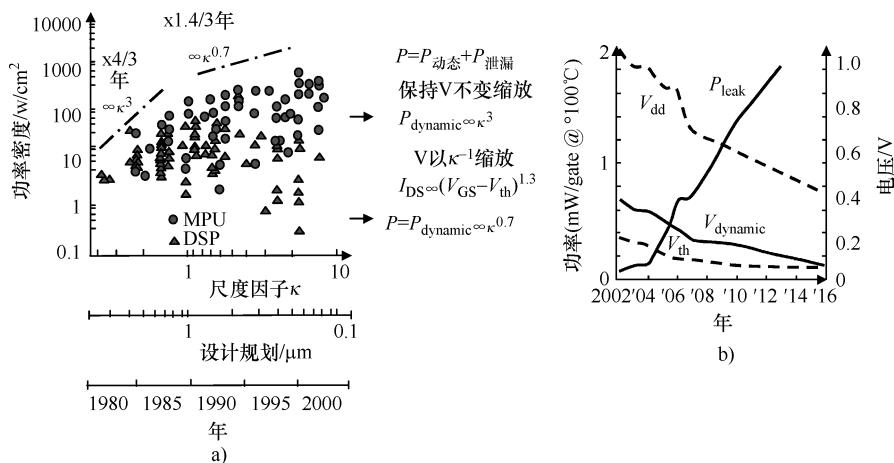

**泄漏问题** 如果不能通过设计方法学的改进减缓其增加的趋势，亚阈区泄漏的增加速率最终会与芯片动态功耗（见图1-12）的速率相同，特别是对几代工艺中的高性能微处理器而言。氧化层厚度每减小1Å，栅电流（见图1-13）会增

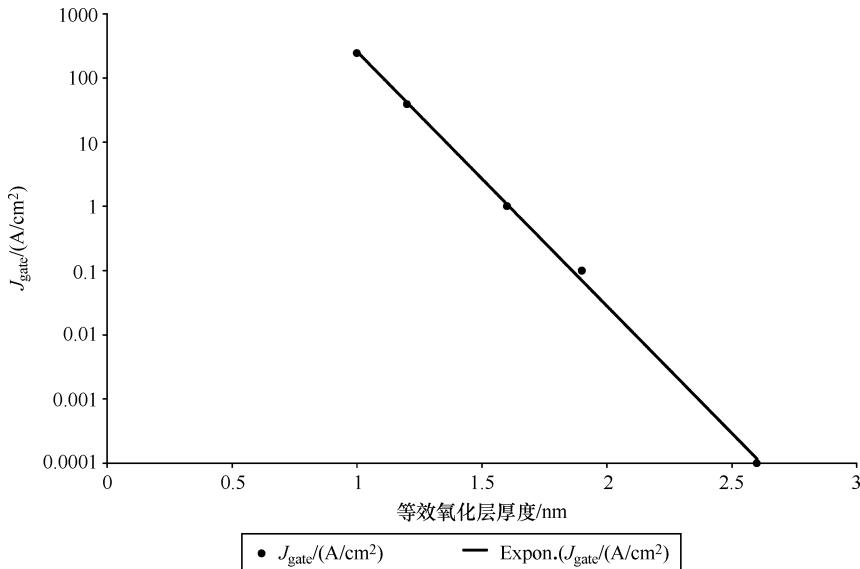

加 2.5 倍，从 130nm 开始，每代技术间的栅电流变化约为两个数量级。

图 1-12 CMOS 功率密度的变化趋势

图 1-13 NMOS 的  $J_{\text{gate}}$  ( $\text{A}/\text{cm}^2$ ) 与等效氧化层厚度的关系 (数据源于 NEC)

随着特征尺寸的减小，栅电阻不断增加，并且 SD 电阻也随着结的不断减薄而增加。对结泄漏来说，需要仔细地调整 SD 电阻，直到需要的源漏结深是采用实际工艺可以实现的。图 1-4 表明，从 250nm 减小到 65nm，多晶栅厚度的变化

很小，发生显著变化的只是多晶栅的长度和宽度。因此，沟道电阻随着工艺缩小而增加并且需要在晶体管模型中予以考虑。

为了继续改善晶体管  $I_{d\text{sat}}$ ，人们对应变硅沟道晶体管投入了大量的认真研究和开发努力，据报道，采用 SiGe 应变硅已经实现了 10% ~ 20% 的改善<sup>[22]</sup>。一种初步的应变技术是采用氮化硅“帽”薄膜来提供应变沟道，只能实现适度的  $I_{d\text{sat}}$  改善。提升源漏技术也在不断发展，但是该技术要求采用选择性外延工艺，这是一种困难的制造工艺。引入的许多新材料使高  $k$  栅氧化层成为现实，现在正采用 NiSi 取代 CoSi<sup>[22]</sup>。尽管高  $k$  栅氧化层可以与金属栅一起使用，但是与硅不兼容，因此在集成方面提出了重大的挑战<sup>[4]</sup>。与多晶栅相比，金属栅具有的明显优点是因为它们不会发生耗尽，所以对相同的电容有效氧化层厚度 (CET)，工艺工程师不需要使用更薄的栅氧化层<sup>[4]</sup>。因此，对给定的氧化层 CET，从理论上说金属栅技术的累积态栅泄漏更低。但是金属栅是非自对准的，因此为了采用金属栅，生产中必须进行革新。在准备本书时，预先掺杂的多晶硅正被用来减小多晶的耗尽问题，其代价是增加了刻蚀的复杂性。由于使用预先掺杂的多晶硅，一些厂商已经有了解决这些问题的方法。在集成电路生产的开始阶段，采用的材料只有 5 种，但是现在已经上升到 20 种了<sup>[23]</sup>。

由工艺技术缩小获得的性能改善已接近极限，但是尺寸的缩小有望会继续依据摩尔定律进行。现在，通过诸如新的晶体管设计和新材料及工艺改进可以改善性能，就最近开发的而言，包括高  $k$  介质、FinFET、SOI、应变硅以及纯硅衬底等。

## 1.4 工艺控制和可靠性

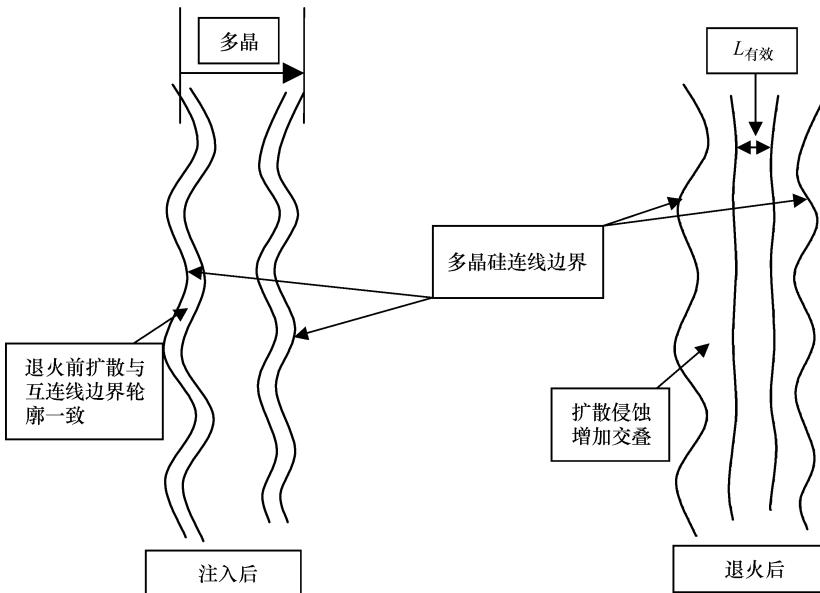

随着工艺缩小，栅长特征尺寸 (CD) 的绝对物理变化没有减小，因此对未来工艺节点来说，栅长 CD 变化的相对百分比会增大<sup>[7]</sup>。除此之外，栅长减小到 100nm 以下时，互连边缘的粗糙度 (LER) 影响着几个晶体管参数，因此受到了越来越多的关注。sub-100nm 工艺中 LER 控制是关键，因为随着工艺的缩小，对于更短的栅长，LER 对器件的影响来说非常重要。LER 控制需要采用先进的光刻和刻蚀工艺，这只能通过更好的工艺控制来改善。较大 LER 带来的负面影响是更大的交叠电容  $C_{gd}$ ，特别是对 PMOS。受到影响的其他器件参数包括 DIBL 的和阈值电压，因为退火后，有效沟道长度会随着 LER 减小，特别是 PMOS (见图 1-14)。当晶体管的  $L_{\text{effective}}$  值由于 LER 效应而减小时，PMOS 的  $V_{th}$  和穿通电压将会受到相反的影响。

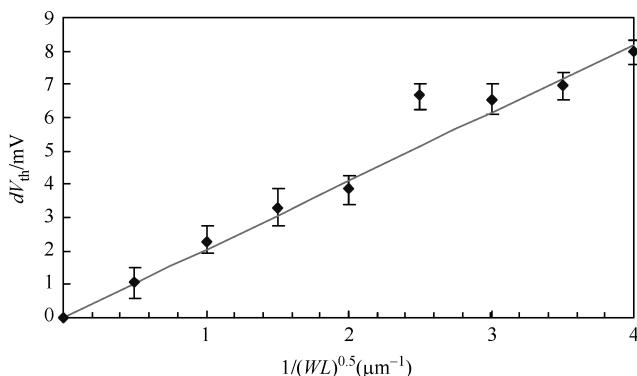

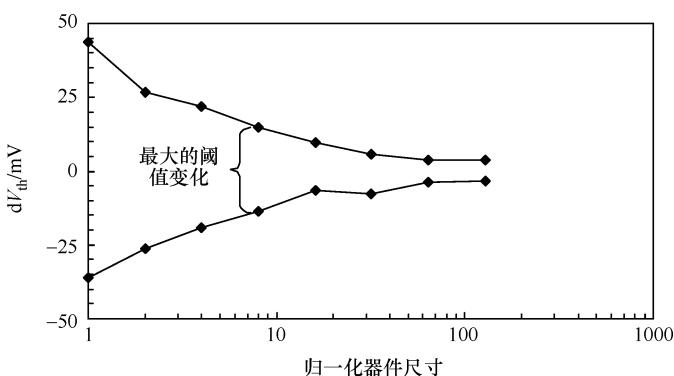

$V_{th}$  的变化受到掺杂的随机波动和栅 CD 变化的影响。薄栅氧与掺杂沟道的形成一起引起沟道杂质的波动，波动情况还与栅多晶的形态有关 (参见图 11-7)。

图 1-14 LER 使交叠电容增加而使沟道长度减小

这些效应使  $V_{th}$  更加难以控制，特别是晶体管  $V_{th}$  匹配更加困难，尤其是对小尺寸器件。从图 11-37 可以看到，最小器件  $V_{th}$  的变化最大，但其会逼近一个渐进值。避免使用最小宽度的晶体管是一个明智的选择，除非  $V_{th}$  变化不会引起电路失效。

负偏压温度不稳定性（Negative Bias Temperature Instability, NBTI）是栅氧厚度缩小后面临的一个效应。130nm 工艺节点的栅氧厚度已经对 NBTI 非常敏感了<sup>[18]</sup>。任何引起断键的工艺步骤都会增强 NBTI。特别是等离子或反应离子刻蚀是能引起键断裂的工艺，因此会使 NBTI 增强。65nm 工艺节点中，栅氧厚度将等于或低于  $10\text{ \AA}^{\ominus}$ 。对这个量级的厚度，界面控制非常关键。多晶耗尽将会是制约性能进一步缩小的限制因素，为此需要采用无耗尽的栅材料。90nm 及以下工艺节点的栅氧厚度控制对保持一个可预期的、较小的栅电流来说是很重要的。栅氧厚度每减小  $1\text{ \AA}$ ，栅电流大约增加 2.5 倍（见图 1-13）。

## 1.5 光刻问题和掩膜数据爆炸

从 180nm 节点起，开始进入亚波长范围，即最细线条已小于光刻中曝光采用的光源的波长。采用光学方法进行光刻越来越不能满足亚波长光刻的需求

$\ominus 1\text{ \AA} = 0.1\text{ nm}$ , 后同。

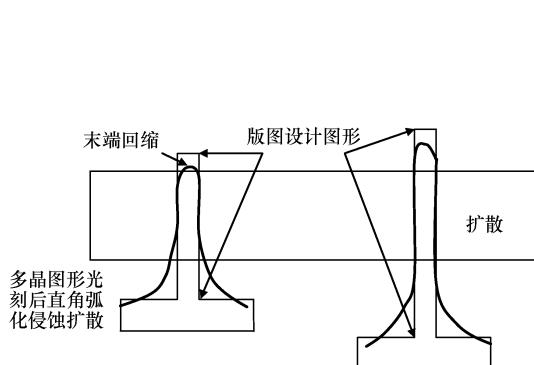

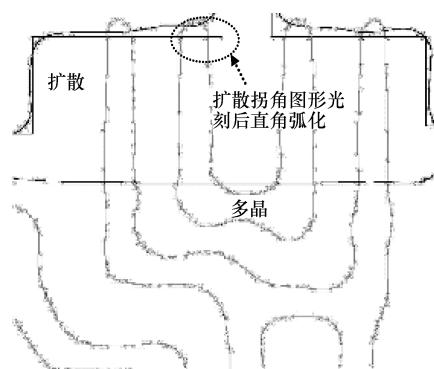

(见图 1-5)，因为必须克服众多的困难才能使新一代光刻技术用于生产中。因此在 sub-100nm 节点，必须变革物理设计，从而不需要下一代光刻技术就可以进行可靠的图形光刻。在 90nm 节点以下，将需要采用先进的 OPC 技术，同时必须采用能够与光刻技术相适应的物理设计。分辨率扩展技术导致了图形分割之后的掩膜数据剧增，这也就增加了掩膜版费用<sup>[8]</sup>。不断变大的亚波长差距使得未来几代工艺节点中掩膜版和光刻费用成指数增加；因此，只有资金雄厚的生产厂商才能使用得起处于领先地位的光刻设备。对于其他厂商来说，在增加光刻设备数值孔径值和采用积极的 OPC 技术以扩展 193nm 光刻技术分辨率的同时，物理设计的自由度将不得不受到限制<sup>[9]</sup>。关于这个问题的详细介绍见第 3 章。

## 1.6 新型的电路和物理设计工程师

目前 CMOS 工艺的缩小已到达这样一个阶段，即从工艺开发的角度考虑，认为电路和物理设计之间相互没有关联的这种传统假设已不再成立。因此，这要求以我们在电路的实现方式方面发生模式的转换<sup>[20]</sup>。即使是可以保证性能的专用集成电路（Application-Specific Intergrated Circuit, ASIC）设计，如果要求能实现功能并且可以缩小到图形特征尺寸在 100nm 以下，设计方法也必须采用这种转换。

特别是高性能设计会要求完全不同的方法。这就要求新型的电路和物理设计工程师。他们清楚这些困难，通过建立与光刻技术相适应的物理设计，从而获得一个鲁棒的、可缩小的并且是高成品率的设计，使其成为解决方案的一部分。这种设计在未来的工艺节点中必须可以容忍较大的泄漏，包括亚阈区泄漏（包括 GIDL）和栅泄漏。波动容限是未来工艺节点中的另一个设计要求。

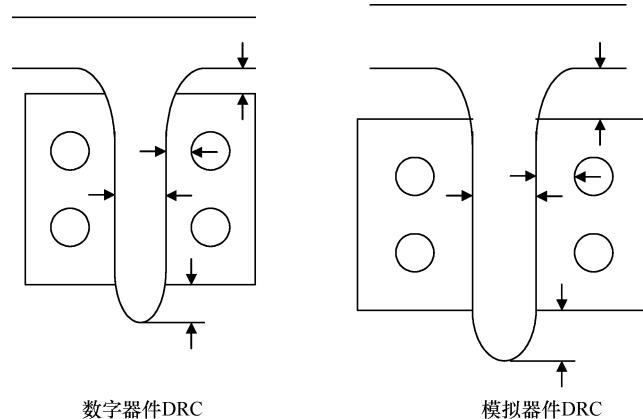

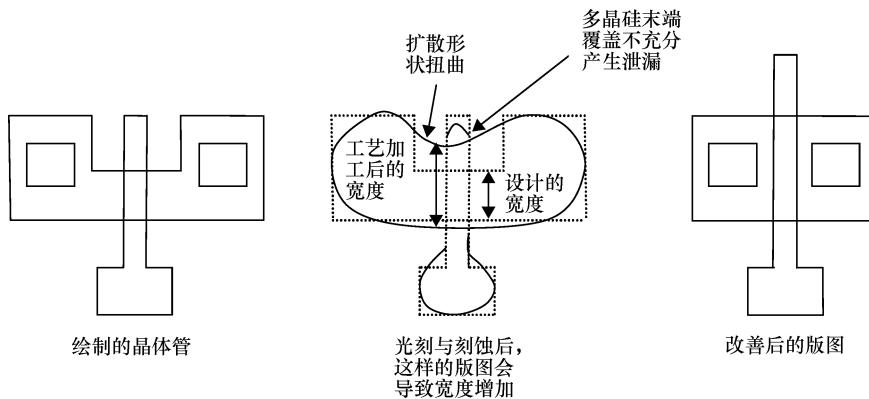

许多工艺步骤受版图设计风格的影响。最显著的是，多边形图形密度对层间介质层厚度有重要的影响。扩散层图形密度对最终产品制造成品率的影响很大。在器件匹配性对电路性能非常重要的电路中，其他版图类型可以缓解掺杂波动和多晶 CD 的变化。

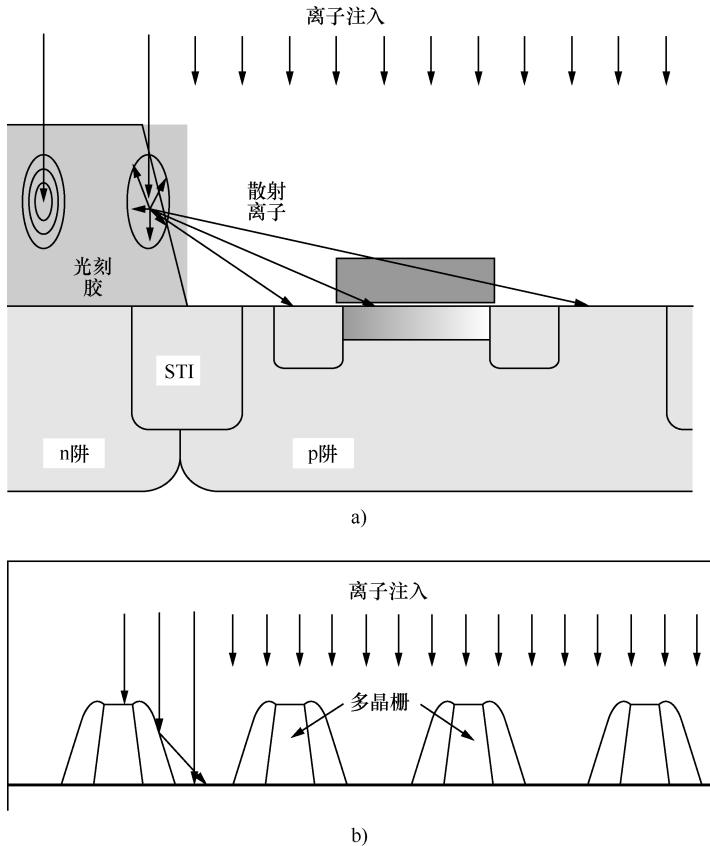

新型的电路和物理设计工程师必须清楚邻近效应对电路以及随之对电路设计的相应影响，从而使硅集成电路能够如仿真时预测的一样。如果将一个晶体管紧靠着阱或位于多晶密集或稀疏的区域时，都会产生邻近效应。如果将晶体管紧靠另一种结构，注入时将使注入的杂质偏转到紧靠光刻胶掩膜的晶体管上，引起掺杂波动。只要每个晶体管的相邻环境都相似，邻近效应就是一致的。否则邻近效应会引起器件  $V_{th}$  的变化。其他的邻近效应包括光刻引起的多晶 CD 变化、刻蚀微负载导致的欠优化版图风格引起的刻蚀邻近效应，以及光学邻近效应。许多系统的邻近效应可以通过采用好的版图风格和依靠光刻技术以及偏置加以避免。但

是设计者必须理解邻近效应带来的制约因素，并且能够采用设计技术来减轻这些效应的影响。本书将在后面章节中详细地讨论这些技术，以便给电路和物理设计工程师提供一个知识背景，使他们可以通过物理设计更好地应对这些效应的影响。

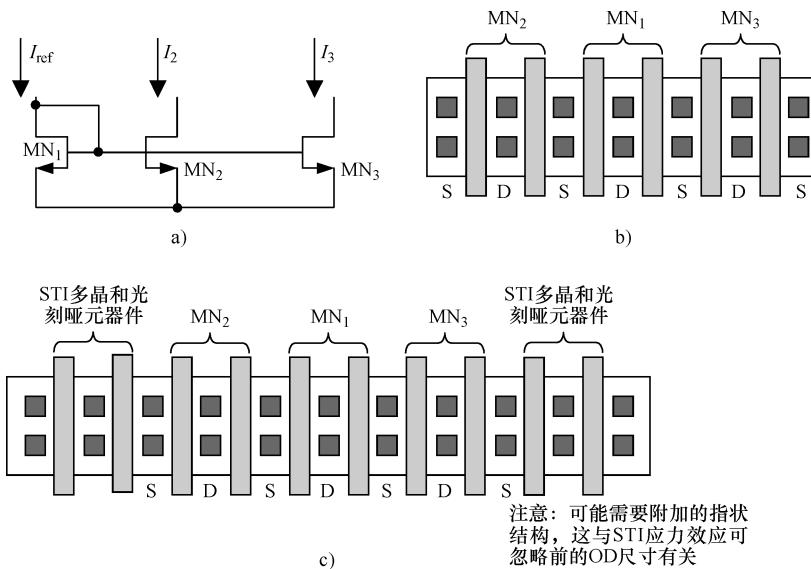

## 1.7 建模的挑战

持续的物理尺寸缩小增加了器件电参数的容差，并且成为对建模的挑战。在 BSIM4 之前，模拟软件中没有包含栅电流模型，设计人员不得不自己考虑栅电流的计算。沟道中杂质的统计波动将影响位单元中使用的小几何尺寸晶体管，但是对其建模难度较大，使得建立的模型精度较差<sup>[3]</sup>。由于邻近效应和 STI 应力导致的迁移率退化与版图本身的关系非常密切，因此建模难度也很大<sup>[10,11]</sup>。目前已经推出了一些新的工具，通过版图提取在这个领域提供一些帮助。最好的工作方式是理解这些效应，然后在物理设计中使这些效应对电路的影响最小。第 2 章将详细讨论这些效应。

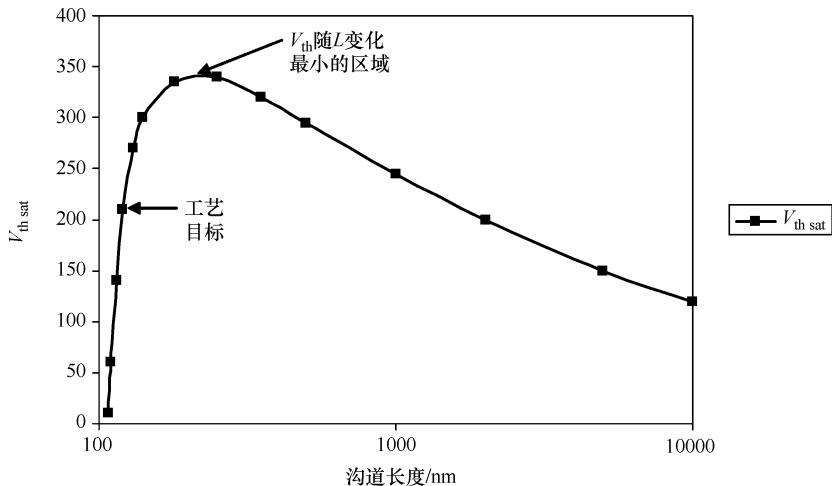

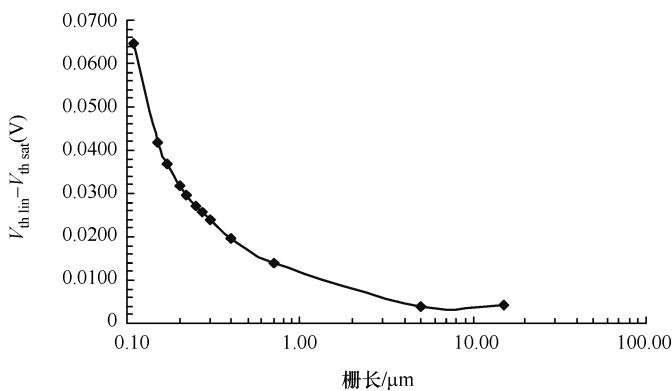

由于 halo 注入（大斜角注入）效应与沟道长度之间关系的无规律性，导致对 halo 注入的逻辑过程进行的模拟建模精度很差。这样混合信号设计工程师就需要使用“模拟晶体管”<sup>[17]</sup>，这将增加费用，并且有时还没有模拟晶体管可供使用。除非你能够与 Foundry 生产线共同工作，有能力将 halo 对 DIBL、 $V_{th}$  以及厄尔利电压的影响及其和晶体管沟道长度的关系进行建模，否则明智的做法还是采用模拟晶体管。正如 IEDM 2002 出版的参考文献 [16] 中所述，这样一种模型并不是不可能的，但是并不是每条 Foundry 生产线都能提供这种模型。无论什么原因，如果你必须在模拟设计中使用 halo 工艺的晶体管，而 SPICE 模型又没有考虑 halo 效应（反型短沟道和漏感应阈值电压漂移）和输出电阻以及厄尔利电压的变化，选择合适的晶体管尺寸就变得非常重要。要求模型能够适用于选用的晶体管尺寸，以避免由于晶体管特性随着沟道长度的非线性变化而影响模拟精度。

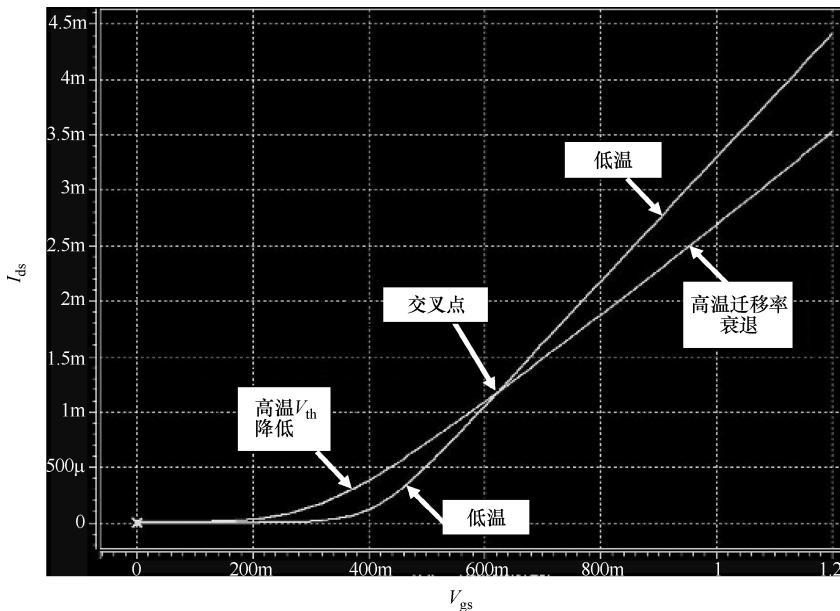

需要建立模型的新物理效应包括对  $V_{th}$  与晶体管多晶长度之间关系产生影响的 halo 注入效应（反型短沟道（RSC）效应）<sup>[16]</sup>、栅感应漏极泄漏（GIDL）、漏感应阈值电压漂移（DITS）<sup>[24]</sup>、输出电阻和厄尔利电压变化，以及栅电流<sup>[15]</sup>。在以往的模型中，仅从 BSIM4 开始才对其中一部分新效应建模<sup>[24]</sup>。对小于 130nm 的工艺节点，强烈推荐在所有的仿真中，包括在数字电路仿真中，采用 BSIM4 模型。

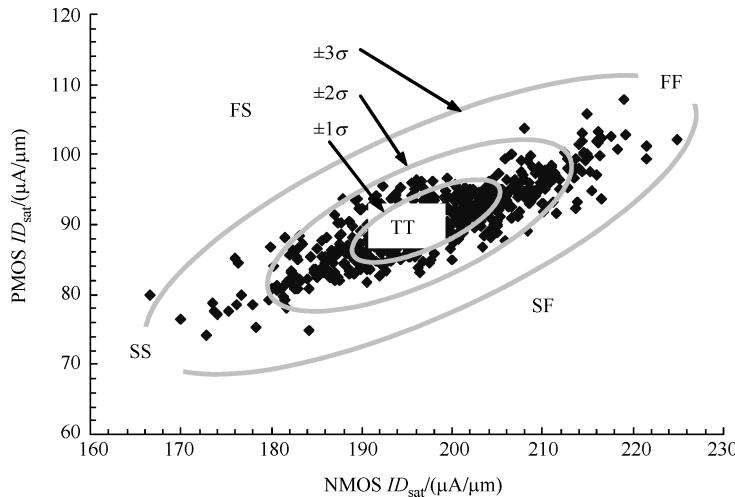

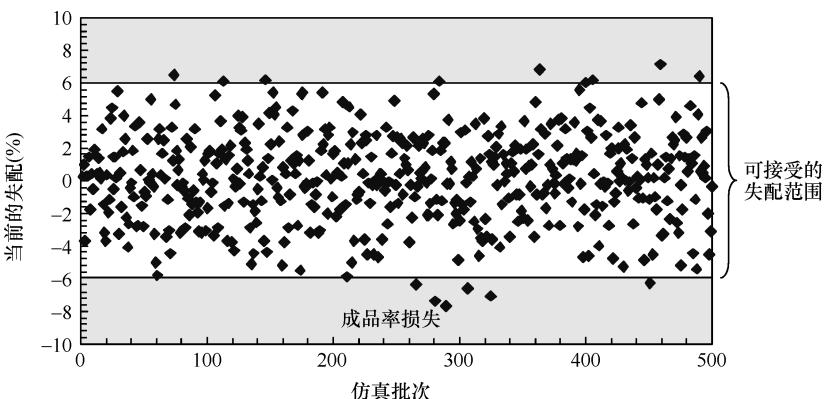

针对上面描述的注入工艺和特征尺寸的波动，统计模型对解决其中一些问题也是必需的。除非能明智地选择适合特定电路的模型组合，否则只是采用工艺角模型会以速度、功耗和面积为代价，产生不切实际的工艺组合，导致对电路过于保守的设计。另外，通过传统的五点工艺角方法并不能建立关键工艺角模型，因此对特定的电路来说，可能并没有分析最坏情况。表 1-1 是对建模挑战的总结。

表 1-1 sub-100nm 工艺中器件建模挑战的总结

| 参 数                            | 效应产生原因              | 效 应 说 明                                                                 |

|--------------------------------|---------------------|-------------------------------------------------------------------------|

| RSC                            | halo 注入 (工艺、物理器件效应) | 由于横向不均匀掺杂引起的反型短沟道效应；当沟道长度变化时， $V_{th}$ 随之变化                             |

| DITS                           | halo 注入 (工艺、物理器件效应) | 对沟道较长的器件，当 halo 注入对沟道的影响减小时，由于 DIBL 的变化导致的漏感应随阈值电压漂移                    |

| 厄尔利电压<br>和输出电阻 <sup>[17]</sup> | halo 注入 (工艺、物理器件效应) | 对长沟器件，DIBL 变化导致的效应，与上面相似                                                |

| 多晶耗尽 <sup>[25]</sup>           | 超薄栅氧 (工艺、物理器件效应)    | 对超薄栅氧，多晶耗尽正变得很重要，对大多数器件来说多晶耗尽大约导致 8nm 等效氧化层厚度的增加 (EOT)，对预掺杂的多晶则很小       |

| 栅隧穿电流                          | 超薄栅氧 (工艺、物理器件效应)    | 由于超薄栅氧，从栅到沟道发生直接隧穿                                                      |

| 迁移率随掺<br>杂的变化                  | halo 注入 (工艺、物理器件效应) | 迁移率随着掺杂的降低而改善                                                           |

| 线性邻近<br>效应                     | 密集、隔离               | 部分由光刻效应引起，部分与刻蚀微负载效应有关，还与多晶对杂质的散射有关，导致掺杂与设计中多晶互连间距有关的系统变化               |

| 非线性邻近<br>效应                    | 光学邻近修正 (OPC)        | 亚波长光刻技术要求分辨率增强技术                                                        |

| GIDL                           | 能带到能带之间的隧穿          | 对于高的结掺杂和 sub-100nm 器件中的突变结，由漏到栅之间的强电场引起能带到能带的隧穿                         |

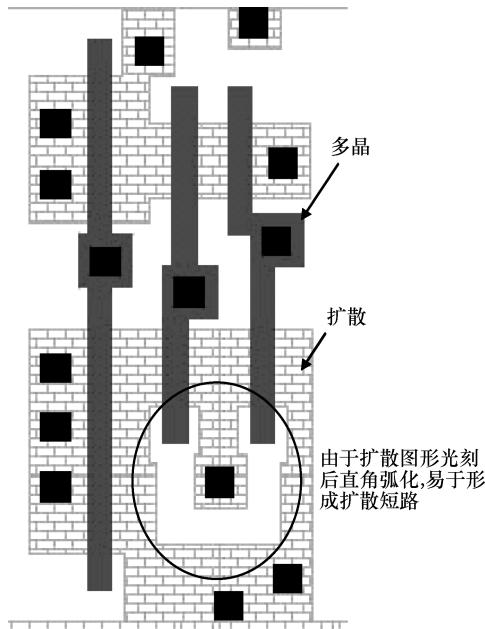

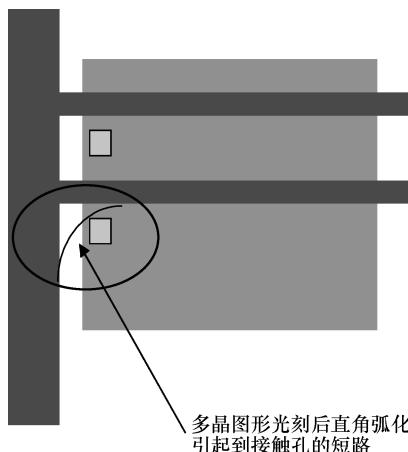

| 扩散和多晶<br>光刻后直角<br>弧化           | 工艺和版图效应             | 亚波长光刻引起扩散和多晶光刻后直角弧化，进而导致小尺寸器件的器件图形变化以及多晶接触压焊点到扩散边界的邻近效应                 |

| 阱邻近                            | 在阱边界上的器件            | 光刻胶外的阱注入原子的横向散射会导致靠近阱边缘的器件阈值电压的增加。对 NMOS 和 PMOS 器件，典型增加量分别为 50mV 和 20mV |

| STI 应力                         | STI 对器件沟道的邻近效应      | STI 应力减小电子迁移率但是增加空穴迁移率，因此影响 $I_{d\text{ sat}}$                          |

## 1.8 变革设计方法的需要

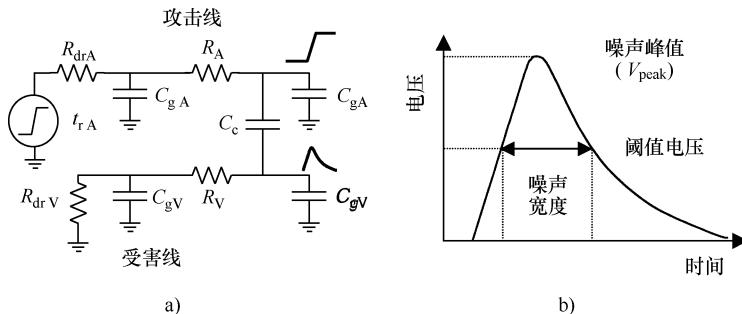

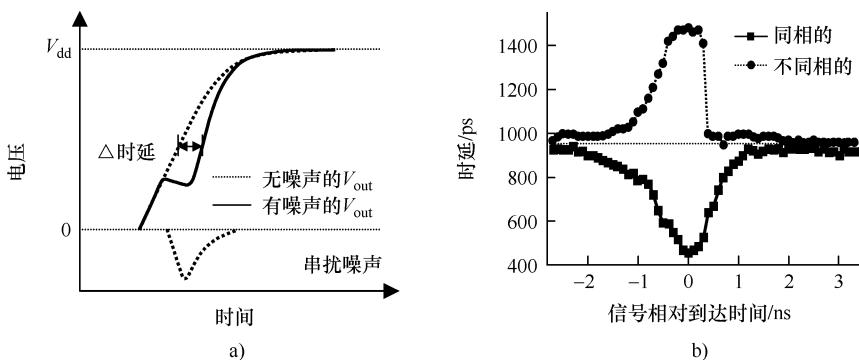

过去，进行容性噪声分析就足够了，但是现今，信号完整性已经扩展到了感

性噪声。时序通常过去主要关心的问题，现在也要考虑功能问题了。为此就需要开发抗噪声电路以减小长时分析以及对片上和片外信号完整性的建模。同时还需要开发通过构建进行校正的技术以保证信号完整性的信号传输方法。这可能会是采取放置中继放大器的方式，在间距允许的地方展开互连。在某些地方，可能需要屏蔽。对感性屏蔽，鲁棒的功率分配系统将翻倍，还要求采用宽大总线返回路径。

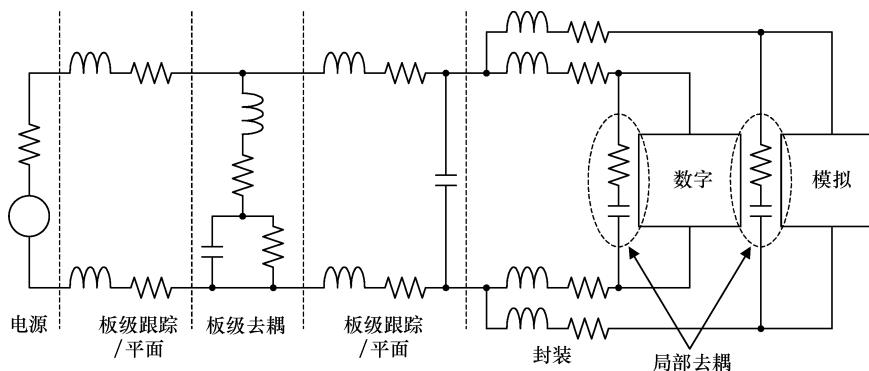

最近，伴随着外加电压缩小、器件尺寸缩小以及更高的时钟频率，也需要考虑功率完整性问题。尽管器件尺寸不断缩小，但是为了满足不断增加的芯片性能的需求而使功能不断增加，导致功率耗散始终保持向上增加的趋势。当电源电压下降时，功耗却在增加，因此电源电流不断增加并且因此  $di/dt$  和阻性压降也不断增加，使得  $L(di/dt)$  正逐渐成为主要的性能制约因素。为了应对这个问题，现在设计方法必须能够将芯片的功率分配设计扩展到封装和系统板以实现整个系统的解决方案。否则，将不可能实现期望的电源阻抗，从而缓解较高的阻性和  $L(di/dt)$  压降。

工艺的波动，不管是器件还是互连的波动都将将是纳米 CMOS 设计的主要问题。对于能适应较大波动的设计，设计方法必须具有应对波动的能力。传统的五点工艺角方法正变得越来越没有意义。在某些情况下会以芯片面积和功耗为代价导致一个开销巨大的过于保守的设计，而在其他情况下又可能完全错失了重要的最坏情况条件。

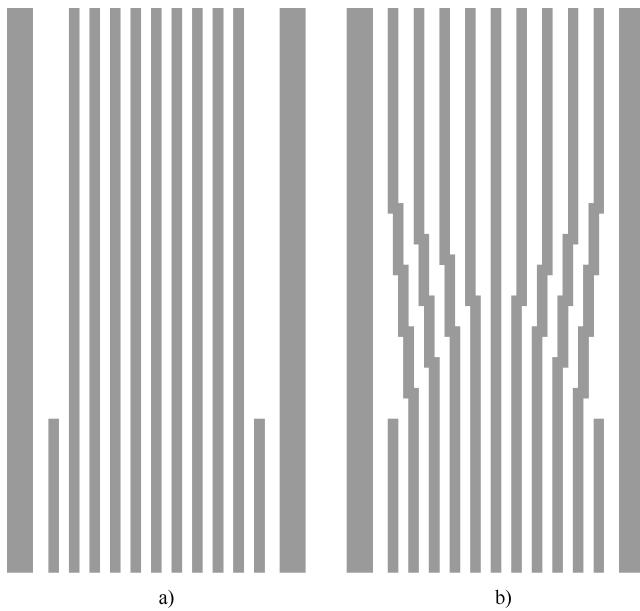

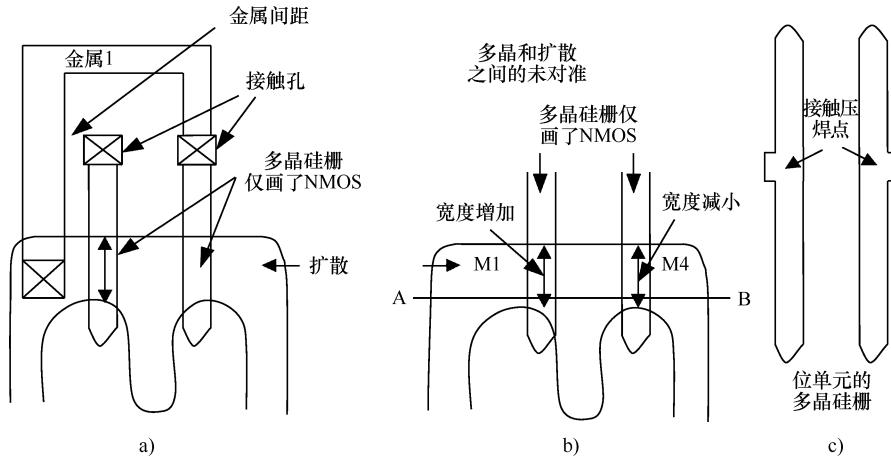

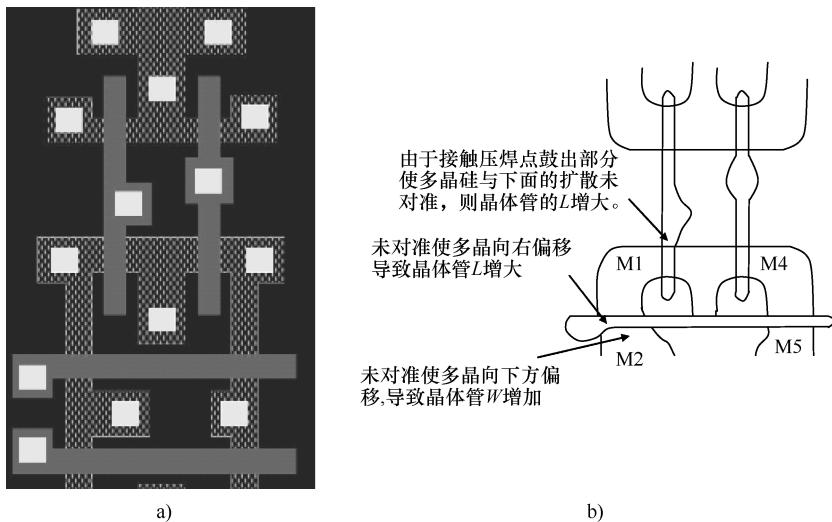

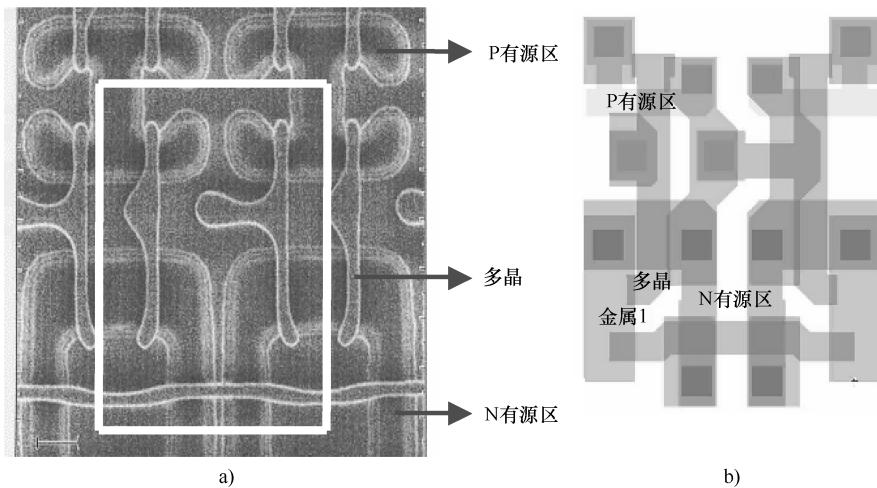

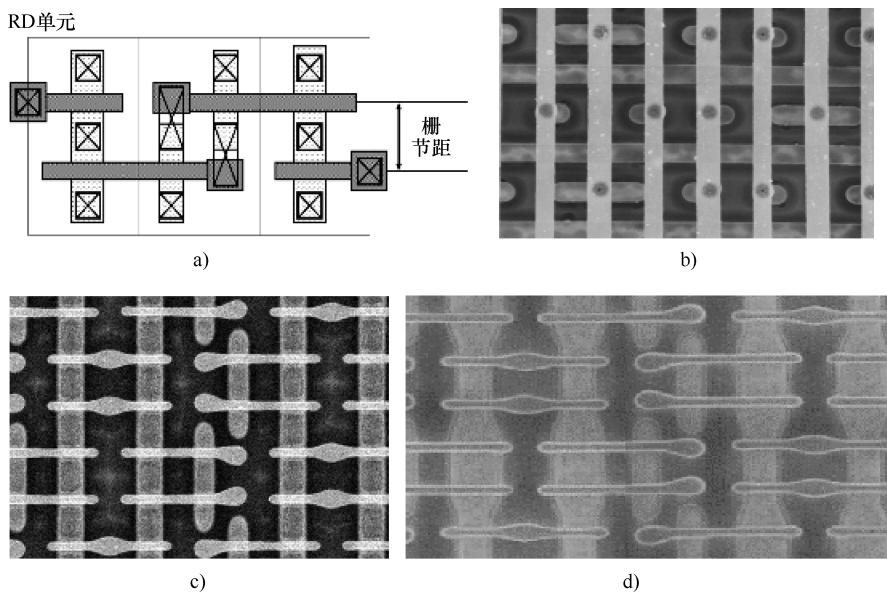

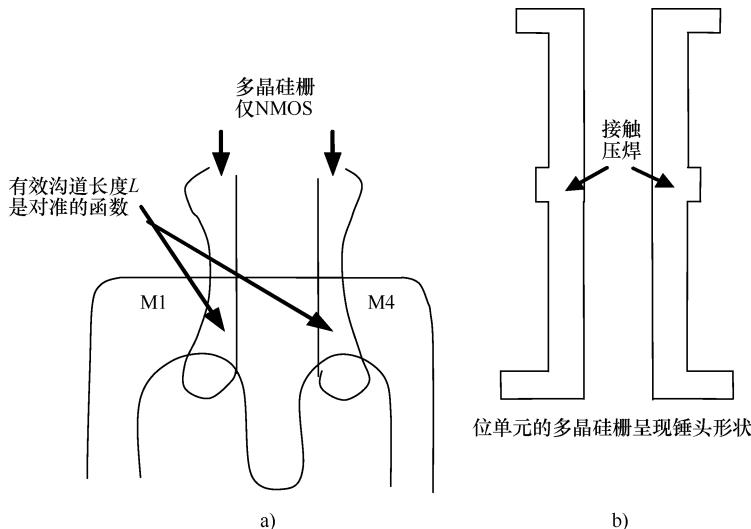

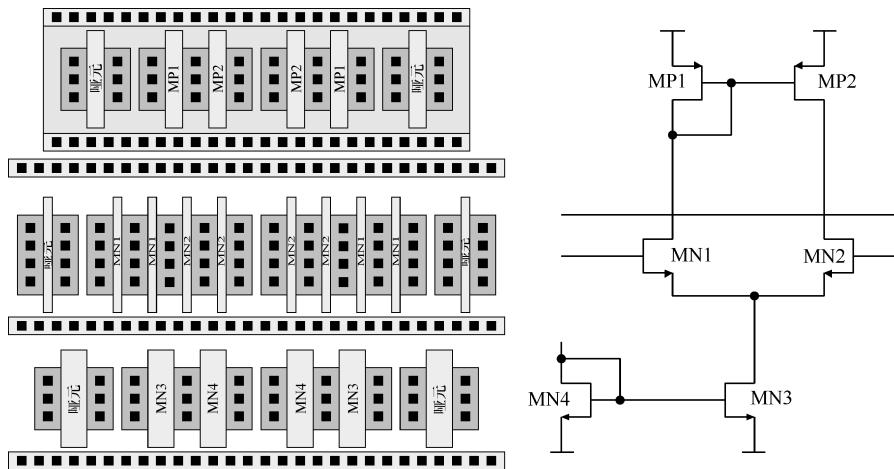

设计方法的自由度正在减小。未来的设计将会提出对准关键多晶的要求。这也要求在位单元设计中进行变革。现有的设计中传输晶体管的多晶与下拉和上拉晶体管直交。新的位单元设计需要考虑这个问题，并且使所有的多晶互连对齐。使所有的多晶互连以同一方向排列的原因是由于采用了有一定注入角度的 halo 注入。如果将栅布置成彼此之间直交，会导致掺杂的变化，这是由于每个多晶栅边缘接受 halo 注入的时间不同而引起的。例如，水平方向栅在不同时间只接受到一半的注入剂量，因此引起  $V_{th}$  的波动。由于光刻效应和掩膜版的影响，彼此直交的多晶互连的 CD 变化也更高，详细情况在第 11 章介绍。

泄漏（亚阈区、GIDL 和栅）是我们在新的设计方法中必须面对的下一个难题。存储器必须设计成比以前能容忍更大的泄漏，但是又不能明显降低阵列的效率。在像 L2 和 L3 缓存那样巨大的阵列中，较大的泄漏不仅是性能和功能问题，也是面积和功耗问题。将 L2 和 L3 缓存设计成采用多个周期中存取可能是必需的，因为它们可以容忍更长的等待时间。这是弥补更慢的存取时间所必须的，因为采用更长的沟道长度和更高的  $V_{th}$  注入来减小泄漏功耗是以增加存取时间为代价的。由于较长的沟长可以使位单元晶体管实现更好的匹配，并且允许采用更富挑战的下拉/传输晶体管，这也可使速度得到一定的恢复。

宽的多米诺门不再是纳米 CMOS 时代切实可行的设计类型，这是由于在功

能、噪声容限和速度之间进行折衷的难度更大了。具有功能的宽多米诺电路将不再比一个采用两级电路的单元快了。比例逻辑也将被摒弃。器件和泄漏波动将导致设计良好的比例逻辑偏离其最佳工作点，某些情况下甚至会完全失去功能。

功率耗散、性能和工艺复杂度之间协调变得更加困难，为此要求设计者更加慎重地确定对不同晶体管可以采用的阈值电压注入的最佳次数，并且与费用之间进行权衡。如果设计中能够采用较低  $V_{th}$  的晶体管，设计人员就可以在改善芯片性能的同时不会大幅增加待机功耗。

在 130nm 工艺中，互连线转换到采用铜互连已经表明能显著提升抗电迁移(EM)能力和互连性能。然而，当芯片面积增大时，设计者要求更高的互连性能。而在 130nm 后的各代工艺中还没有出现互连线的进一步更新。随着工艺尺寸的缩小，工艺工程师正试着采用低  $k$  介质提升互连性能。因为低  $k$  介质的热传导性更差，在纳米 CMOS 工艺中，EM 问题已经重新成为一个问题。加之更高信号速度导致流过互连的电流脉冲更高，进一步恶化了 EM 问题。

## 1.9 总结

本章讨论了特征尺寸缩小到 100nm 以下时所带来的大部分问题，并指出，如果我们继续使用先前工艺中开发的设计方法，这些问题将提出哪些挑战。很清楚的一点是我们需要进行模式转换，才能在未来的设计中继续利用工艺技术缩小的优势，从而继续沿着摩尔定律确定的趋势发展<sup>[27]</sup>。

虽然我们看到作为器件尺寸缩小的结果，性能改善的趋势已经变缓。但是如果器件和工艺工程师发明了新的工艺和材料，能够解决由于物理限制影响性能改善的问题，性能的进一步改善是可以持续的<sup>[23]</sup>。

虽然如此，现在已经到达这样一个阶段，即要求电路和物理设计工程师也必须理解尺寸进一步缩小带来的这些效应，以便利用这种技术并且确保具备功能的鲁棒设计。随着掩膜费用的增加，更迫切的问题是工程师们能理解这些效应，以避免陷阱，并在第一次投片中就能实现设计功能。

## 参 考 文 献

- [1] IBM J. Res. Dev., Vol. 46, No. 2/3, 2002.

- [2] P. Kapur, Performance challenges of the future on chip metal interconnects and possible alternatives, Stanford University, May 23, 2002.

- [3] Near limit scaling, workshop, Solid State Circuits Technology Committee, 2003.

- [4] The future of semiconductor manufacturing, short course, IEEE International Electron Devices Meeting, 2002.

- [5] S. Schulze, Mentor Graphics Corp., Wilsonville, OR, Effecting mask costs by solving the data explosion bottleneck in mask data preparation, *Semiconduct. Int.*, July 1, 2003.

- [6] H. S. Momose, S. Nakamura, T. Ohguro, T. Yoshitomi, E. Morifudi, T. Morimoto, Y. Katsumata, and H. Iwai, Study of the manufacturing feasibility of 1.5 nm direct-tunnelling gate oxide MOSFETs: uniformity, reliability, and dopant penetration of the gate-oxide, *IEEE Trans. Electron Devices*, Vol. 45, No. 3, Mar. 1998.

- [7] A. Allan, D. Edenfeld, W. Joyner, A. Kahng, M. Rodgers, and Y. Zorian, International Technology Roadmap for Semiconductors, *IEEE Comput.*, Jan. 2002.

- [8] S. Schulze, Effecting mask cost by solving the data explosion bottleneck in mask data preparation, *Semiconductor Int.*, July 1, 2003.

- [9] Y. Pati, Sub-wavelength lithography, Tutorial, *Design Automation Conference*, 1999.

- [10] C. Diaz, M. Chang, T. Ong, and J. Sun, Process and circuit design interlock for application-dependent scaling tradeoffs and optimization in the SoC era, *IEEE J. Solid State Circuits*, Vol. 38, No. 3, Mar. 2003.

- [11] G. Scott, J. Lutze, M. Rubin, F. Nouri, and M. Manley, NMOS drive current reduction caused by transistor layout and trench isolation induced stress, *IEEE International Electron Devices Meeting*, 1999.

- [12] M. Horowitz, R. Ho, and K. Mai, The future of wires, *Semiconductor Research Corporation Workshop on Interconnects for Systems on a Chip*, May 1999.

- [13] V. Agarwal, M. Hrishikesh, S. Keckler, and D. Burger, Clock rate vs. IPC: the end of the road for conventional microarchitectures, *27th Annual International Symposium on Computer Architecture*, June 2000.

- [14] T. Sakurai, Issues of current LSI technology and an expectation for new system-level integration, *International Conference on Solid State Devices and Materials*, pp. 36–37, Sept. 2001.

- [15] K. Osada, Y. Saitoh, E. Ibe, and K. Ishibashi, 16.7fA cell tunnel-leakage-suppressed 16 Mb SRAM for handling cosmic-ray-induced multi-errors, Session 17.2, *International Solid-State Conference*, 2003.

- [16] R. Rios, W. K. Shih, A. Shah, S. Mudanai, P. Packan, T. Sandford, and K. Mistry, A three-transistor threshold voltage model for halo processes, *IEEE International Electron Devices Meeting*, Dec. 2002.

- [17] K. Cao, W. Liu, X. Jin, K. Vasantha, K. Green, J. Krick, T. Vrotsos, and C. Hu, Modeling of pocket implanted MOSFETs for anomalous analog behavior, *IEEE International Electron Devices Meeting*, 1999.

- [18] C. Liu, M. Lee, C. Lin, J. Chen, Y. Loh, F. Liou, K. Schruefer, A. Katsetos, Z. Yang, N. Rovedo, T. Hook, C. Wann, and T. Chen, Mechanism of threshold voltage shift ( $\Delta V_{th}$ ) caused by negative bias temperature (NBTI) instability in deep sub-micron pMOSFETs, *Jpn. J. Appl. Phys.*, Vol. 41, Pt. 1, No. 4B, pp. 2424–2425, Apr. 2002.

- [19] A. Stamper, Interconnection scaling to 1 GHz and beyond, *MicroNews*, Vol. 4, No. 2, first quarter 1998.

- [20] International Technology Roadmap for Semiconductors, <http://public.itrs.net>.

- [21] P. Ranade, H. Takeuchi, W. Lee, V. Subramanian, and T. King, Application of silicon–germanium in the fabrication of ultra-shallow extension junctions for sub-100 nm PMOSFTs, *IEEE Trans. Electron Devices*, Vol. 49, No. 8, Aug. 2002.

- [22] S. Thompson et al., A 90 nm logic technology featuring 50 nm strained silicon channel transistors, 7 layers of Cu interconnects, low  $\kappa$  ILD, and  $1 \mu\text{m}^2$  SRAM cell, *IEEE International Electron Devices Meeting*, 2002.

- [23] A. Grove, Changing vectors of Moore's law, *IEEE International Electron Devices Meeting*, 2002.

- [24] J. Assenmacher, *BSIM4 Modeling and Parameter Extraction*, CL TD SIM, Infineon Technologies, Workshop Analog Integrated Circuits, Berlin, Germany, Mar. 19, 2003.

- [25] C. Choi, Modeling of nanoscale MOSFETs, Ph.D. dissertation, Stanford University, 2002.

- [26] G. Brown, The tyranny of roadmap: new CMOS gate dielectrics with reliability promises and challenges, ISMT Reliability Engineering Working Group, Dec. 12, 2001.

- [27] G. Moore, Cramming more components onto integrated circuits, *Electronics*, Vol. 38, No. 8, Apr. 19, 1965.

- [28] G. Moore, No exponential is forever..., keynote, *IEEE International Solid-State Circuits Conference*, 2003.

# 第2章 CMOS 器件与工艺技术

## 2.1 前道工序的设备要求

过去 10 年，集成电路技术领域取得了重大的突破。在集成电路生产的后道工序，由于采用特有的集成方式（如双镶嵌工艺），在互连技术引入了铜互连及低  $k$  介质，使  $RC$  得到了改善。前道工序中，高性能器件的栅介质通常采用由单层原子层淀积生长形成的可靠的氮氧化合物。伴随着超浅结技术的重要进展，应变工程使得采用 sub-130nm 技术生产高功率和低功率器件成为可能。本章我们将回顾 sub-130nm 技术前道工序生产过程目前的状态及未来可能的发展趋势。

### 2.1.1 技术背景

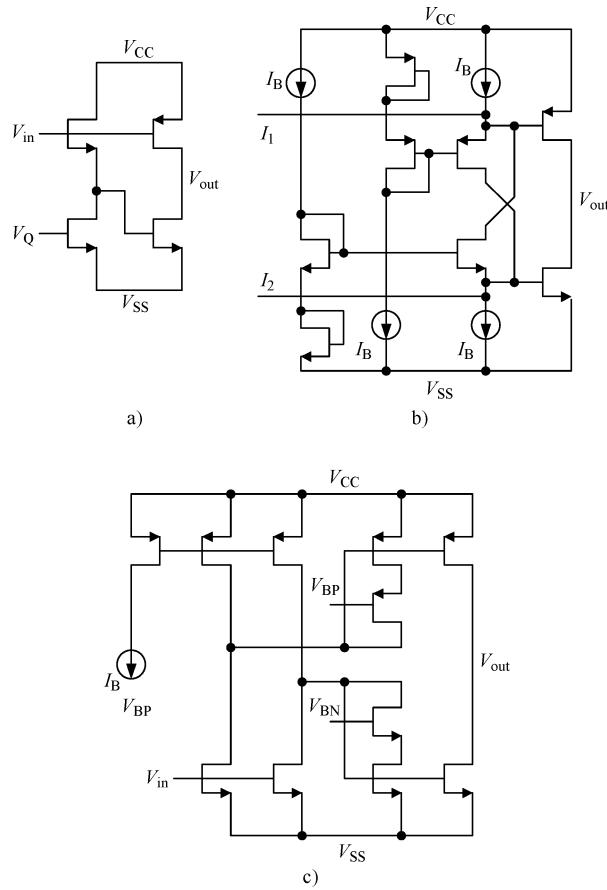

在过去的 40 年，以快速步伐不断前进的半导体工业提供了速度更高、功能更强大、更小型化、价格更低的电子产品。由于 MOSFET（金属氧化物半导体场效应晶体管）是集成电路中使用最普遍的单元，因此半导体工业生产中缩小 MOSFET 尺寸的能力更是极大地推动了电子产品市场的快速发展。尽管存在很多挑战，但是摩尔定律依然在 IC 的晶体管尺寸缩小方面起着指导性作用。长期以来，栅长和栅氧厚度的缩小一直是影响晶体管尺寸缩小的两个关键因素。栅长小于 130nm 的生产技术以及栅长小于 30nm 的技术研究都分别取得了很大的进展。然而，超薄栅氧中基本量子力学的隧穿效应以及对短沟道效应和关态电流的控制程度，限制了由尺寸缩小带来的预期性能改善。因此，在传统的 MOS 架构中采用了新的维数。例如通过多种技术（如采用 SiGe）提高沟道迁移率的应变工程。另外一种方式就是摒弃体平面晶体管结构，采用绝缘上硅（SOI）和三维 finFET（鳍形栅 FET）器件。

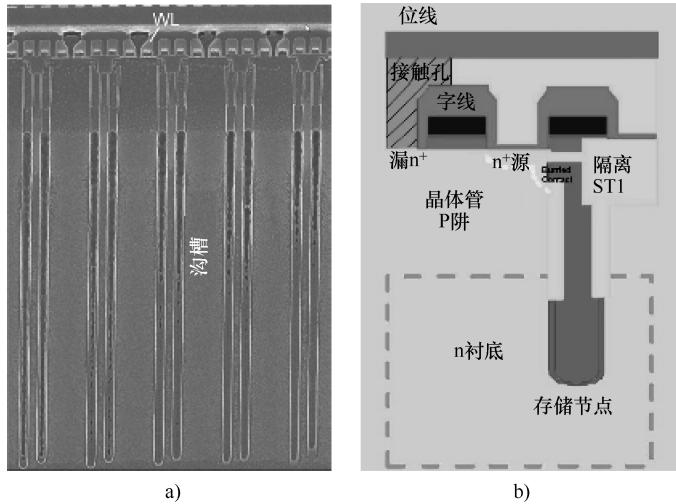

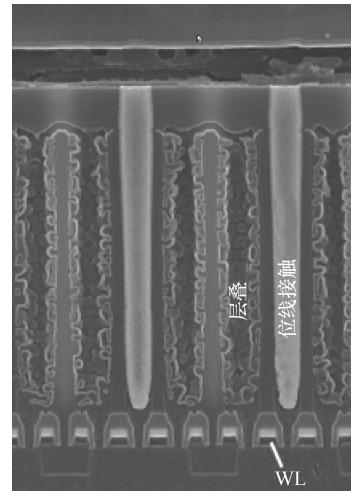

基于硅的集成电路典型工序首先是生成隔离结构。易失性（如 SRAM）和非易失性 [ 如 flash，见图 2-1a ] 器件工艺中采用浅槽和深槽。槽的刻蚀是一个很大的挑战（例如如何保证获得正确的侧墙剖面）。槽的填充也极其关键。介质材料的合理选择是减少硅器件沟道中空洞、寄生结和不希望产生的应力的关键。槽填充后，一般用机械抛光的方法去除多余的介质材料。然后经过各种湿法及干法清洗工序清洗硅表面，为后面的离子注入及栅介质淀积做准备。在多晶硅刻蚀后，变化的低能量倾斜角度的离子注入、侧墙偏移和短时快速退火等工序生成超

浅结。然后形成低热消耗隔离层以及随之的源漏注入和激活，再接着是形成低热消耗的金属硅化物。采用氮化层作接触孔刻蚀阻挡，允许位于槽氧化层上的接触与源漏接触有一定量的偏移。最后，一层淀积薄膜如硼磷硅玻璃（BPSG）或高密度等离子（HDP）薄膜形成第一层层间介质层，到此完成了生产的前道工序。闪存生产过程的工序与此相似。采用约10nm的隧道氧化层，使得沟道热电子注入到多晶硅I，即浮棚中，随后利用Fowler-Nordheim隧穿效应擦除单元。闪存单元中有时使用不对称源漏结构，还采用氧化层-氮化物-氧化层的层叠结构形成浮棚多晶硅I和控制栅多晶硅II之间的第二层栅介质<sup>[2,3]</sup>。本章将回顾前道工序和在sub-130nm工艺中可使用的关键设备，重点是栅层叠结构、应变工程和快速热处理工艺。

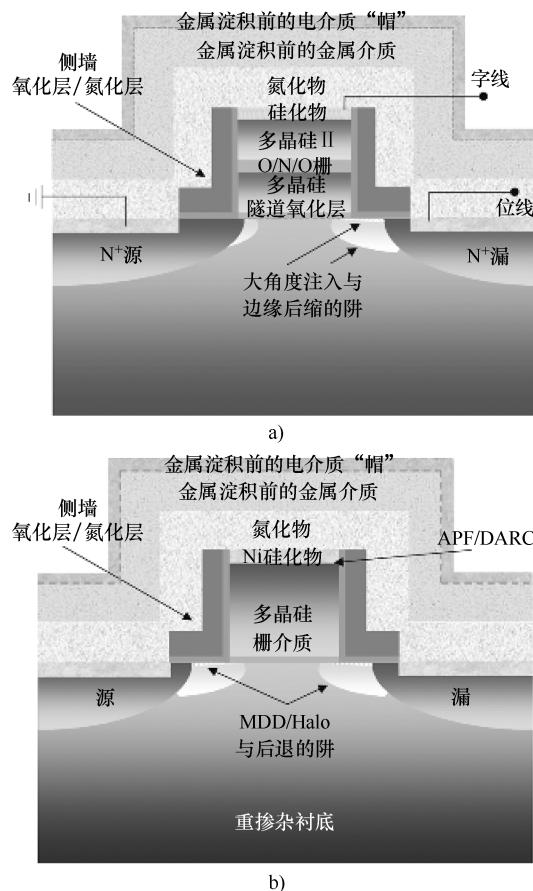

图 2-1 a) 典型的 NMOS 闪存单元和 b) 典型的 MOSFET 单元

[虽然这两种单元间大多数的工艺步骤都是相同的，但是每种单元的设计和工艺还是要面对一些独特的挑战。例如，MOSFET 的栅缩小到了 sub-2nm，而闪存单元的栅（由于其对栅泄漏电流的要求）却在 sub-10nm 范围]

## 2.1.2 栅介质的缩小

随着 MOSFET 尺寸的缩小（见图 2-1b），要求提高单位面积栅介质电容，因此就要减小栅介质厚度。本节将回顾半导体工业可能选用的新栅介质代替  $\text{SiO}_2$  时所面临的挑战与栅介质缩小的趋势<sup>[1]</sup>。栅层叠结构由栅介质（ $\text{SiO}_2$  或者  $\text{SiON}$ ）和其上高掺杂的  $\text{N}^+$ （NMOS）和  $\text{P}^+$ （PMOS）多晶硅栅电极组成。为了改善性能、增加密度和更好地控制短沟道效应，器件尺寸的缩小要求栅介质也随之减薄。当栅氧厚度缩减到 4.0nm 时，工业生产面临着新的挑战。这些挑战包括：PMOS 高掺杂多晶硅电极中硼的穿通、增加的泄漏和日益严重的可靠性问题。生产中，采用由热氮化过程（ $\text{N}_2\text{O}$ 、 $\text{NH}_3$  或者  $\text{NO}$ ）生长的氮氧化硅（ $\text{SiON}$ ）来阻止硼穿通氧化层并提高其抗热载流子的能力。当栅介质厚度减小到 2.0nm 时，采用等离子氮化硅作为栅介质，以提高介质中的氮分，并较好地控制氮的分布<sup>[4]</sup>。尽管人们曾经担心超薄氧化层的击穿将成为主要的可靠性问题，但是由于电源电压的不断减小，使超薄氧化层可以继续满足可靠性要求。然而，由于穿过超薄氧化层的栅泄漏电流将产生过大的待机功耗并使介质的完整性和可靠性退化，这可能成为介质进一步缩小的制约因素。

**栅介质中的载流子输运**  $\text{SiO}_2$  高达 9eV 的禁带宽度和巨大的势垒高度使硅氧化层在中度偏置条件及厚度大于 4.0nm 时接近于理想的绝缘体。这与其他一些薄膜（例如  $\text{Si}_3\text{N}_4$  或者高  $k$  介质）形成对比。在  $\text{Si}_3\text{N}_4$  或者高  $k$  介质薄膜中，传导特性由体制约机制（如 Frenkel-Poole 发射）表征<sup>[5,6]</sup>。将电子由费米能级激发到真空需要的能量称为功函数  $\phi_m$ 。在外加偏置  $V_{\text{ox}} = E_{\text{ox}} t_{\text{ox}}$  作用下，电子有一定的概率隧穿  $\text{Si}-\text{SiO}_2$  势垒，由 Si 的导带到达  $\text{SiO}_2$  的导带。穿过三角势垒的传导可由 Fowler-Nordheim 隧穿来描述，电流密度可表示为<sup>[7-9]</sup>

$$J_{\text{FN}} = AE_{\text{ox}}^{-2} \exp\left(\frac{-B}{E_{\text{ox}}}\right) \quad (2.1.1)$$

式中， $A$  是与  $\text{Si}-\text{SiO}_2$  势垒高度  $\phi_b$  相关的常数； $B$  是与电子有效质量  $m^*$  和  $\phi_b$  有关的常数。当氧化层厚度减小并且  $V_{\text{ox}}$  下降时，电子不再进入导带而直接隧穿梯形势垒。 $V_{\text{ox}}$  小于势垒高度  $\phi_b$  时，直接隧穿电流密度可由式（2.1.2）来描述<sup>[10,11]</sup>。

当介质厚度小于 3.0nm 时，直接隧穿电流将是主要的电流传导机制。由于隧穿电流与氧化层的厚度成指数关系，介质厚度缩小到 1.0nm 时，将引起不希望的高泄漏电流，导致高待机功耗、可靠性问题及介质完整性问题。NMOS 泄漏电流将是栅介质缩小的制约因素。由于空穴隧穿要通过较高的势垒，因此 NMOS 隧穿电流约是 PMOS 隧穿电流的 10 倍<sup>[11]</sup>。

$$J_n = AC(V_g, V_{\text{ox}}, t_{\text{ox}}, \phi_b) \exp\left\{\frac{-B[1 - (1 - V_{\text{ox}}/\phi_b)^{3/2}]}{E_{\text{ox}}}\right\} \quad (2.1.2)$$

式中,  $C(V_g, V_{ox}, t_{ox}, \phi_b)$  是修正函数, 与  $V_g$ 、 $V_{ox}$ 、 $t_{ox}$ 、 $\phi_b$  有关, 由经验拟合获得<sup>[11]</sup>。

**C-V 和等效氧化层厚度** 低频和高频的电容电压 ( $C-V$ ) 特性测量通常可以用于提取金属-绝缘层-半导体 (MIS) 特性, 包括介质厚度、平带电压、固定电荷和界面态密度等。然而对薄栅氧, 特别是当栅氧厚度小于 2.0 nm 以下时,  $C-V$  数据的测量和解读变得非常复杂。随着介质厚度的减小, 穿过薄介质的隧穿电流成指数增长关系 (氧化层物理厚度每减小 0.2 nm, 隧穿电流约增大 10 倍), 在栅电极和衬底中存在的串联电阻上将产生压降 (见图 2-2)。栅介质可以等效为一个与电压有关的电阻与电容的并联, 栅电极和衬底起分布串联电阻的作用<sup>[12]</sup>。在强反型中, 沟道阻抗引起的电容衰减将变得很重要, 这就制约了测量 MOSFET 时可以采用的器件沟道长度<sup>[13]</sup>。

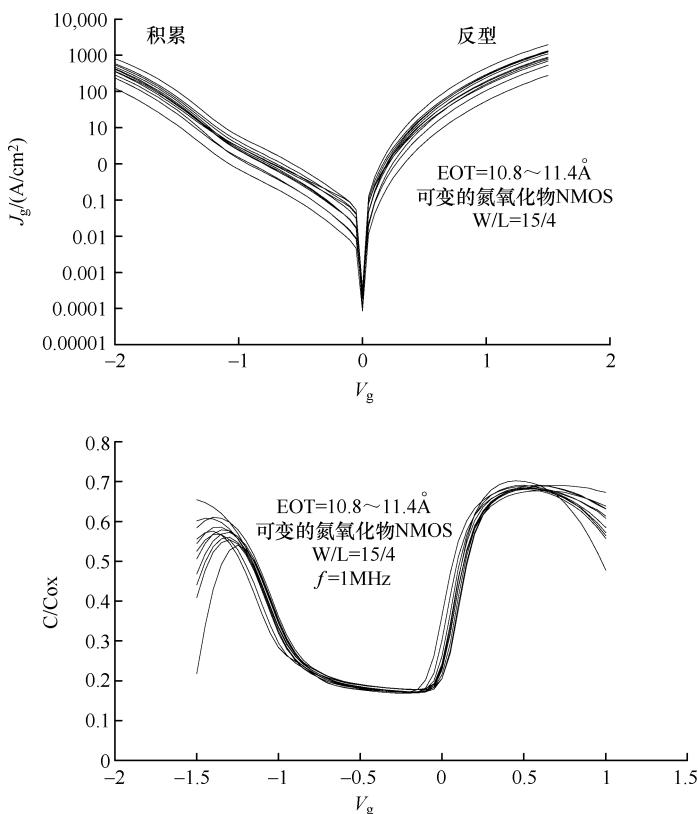

图 2-2 薄氮氧化物的  $J_g - V_g$  即  $C-V$  曲线

(不断增加的氮分降低了隧穿泄漏, 将减小电容在反型和积累时的衰减)

(数据由应用材料公司提供<sup>[13]</sup>)。

近年来，许多重要的工作都集中在精确的测量以及对电容电压曲线的解读上，这在本节的参考资料中有所体现。介质的电学厚度是栅中电荷的质心与衬底之间的距离<sup>[6]</sup>。在栅介质界面附近的多晶硅中，可动电荷载流子的耗尽，特别是反型时，将使电荷质心偏离界面约 0.3nm。这个效应可以建模为氧化层电容串联了一个附加电容<sup>[5]</sup>，这将使得测定的电学厚度大于预期的厚度。相似地，在衬底的反型层或积累层中，载流子被局限在一个靠近表面的很窄的势阱中，它们在表面法线方向上的运动要通过量子力学来分析。一个简单的解析表达式处理是不合适的，而正确的处理要求耦合有效质量的薛定谔方程和泊松方程的自治求解<sup>[14]</sup>。用量子力学的观点分析反型层，发现反型电荷的质心偏离界面 0.3nm。由于多晶硅耗尽和量子力学效应导致的电学厚度在超薄介质中变得日益重要<sup>[5-15]</sup>。因而实际测定的电容值与预计值之间产生了巨大的差异。

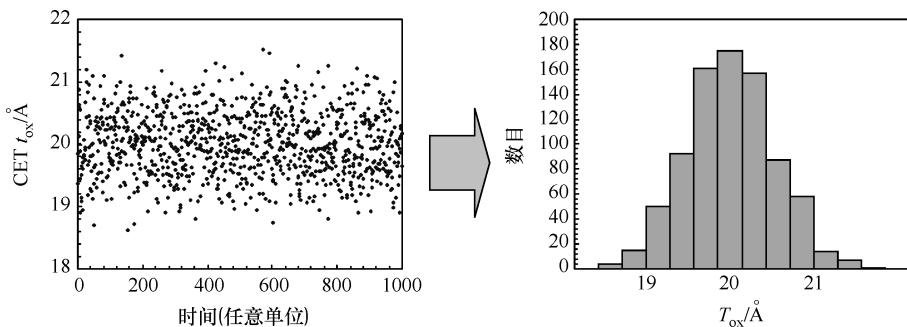

电容的有效厚度（Capacitance Effective Thickness, CET）是指电容介质的电学厚度，可表述为<sup>[12]</sup>

$$\text{CET}(V) = \frac{\epsilon_0 \epsilon_{\text{SiO}_2} A_{\text{gate}}}{C(V)} \quad (2.1.3)$$

式中， $\epsilon_0$  是真空介电常数； $\epsilon_{\text{SiO}_2}$  是  $\text{SiO}_2$  的介电常数； $A_{\text{gate}}$  是栅面积。 $C(V)$  是与给定电压  $V$  对应的电容，它包括了由于多晶硅耗尽和衬底的量子力学效应所增加的串联电容。因此 CET 与电极的类型、电极的功函数以及电极的耗尽有关，也与衬底掺杂和栅电压有关<sup>[12]</sup>。

相比之下，介质的等效氧化层厚度（Equivalent Oxide Thickness, EOT）与电极的性质以及衬底的掺杂均无关。EOT 是指这样的等效氧化层厚度，由 EOT 厚度氧化层产生的 C-V 曲线与采用替代介质的 C-V 曲线相同，可以由下式得出<sup>[13]</sup>：

$$\text{EOT} = \frac{\epsilon_{\text{SiO}_2}}{\epsilon_{\text{high-k}}} \cdot t_{\text{high-k}} \quad (2.1.4)$$

式中， $t_{\text{high-k}}$  是高  $k$  介质的物理厚度；而  $\epsilon_{\text{high-k}}$  是介质的介电常数。由于 SiON 或者其他中、高  $k$  介质的介电常数不知道，EOT 必须依照上面描述的电容测量方法确定来获得<sup>[12]</sup>。一旦 CV 测试完成，接下来的数据校正和解读将是一个挑战。人们提出多种不同模型来分析多晶硅耗尽及量子效应并进而提取 EOT。不同的模型和算法将导致提取的 EOT 结果不同，因此对比由不同方法获得的介质 EOT 时，必须多加注意<sup>[12,13,16,17]</sup>。

**制约超薄  $\text{SiO}_2$  缩小的因素与替代介质** 如前所述，栅介质缩小可以改善器件性并能抑制短沟道效应。但是有几个基本因素制约着  $\text{SiO}_2$  进一步缩小到小于 1.0nm EOT 的水平。当介质材料的禁带宽度达到  $\text{SiO}_2$  的禁带宽度时，每个界面的厚度大约是 0.35 ~ 0.4nm，这样两个界面总厚度就达到 0.7 ~ 0.8nm<sup>[6]</sup>，因此  $\text{SiO}_2$  缩小的绝对物理限制就是 0.7nm。然而随着氧化层厚度的减小，包括过多的

泄漏和有限的甚至零性能增益等在内的其他实际的限制可能会先达到。如式(2.1.2)所示,随着介质物理厚度的减小,隧穿电流将指数增加。另外,随着介质厚度的缩小,硅沟道和多晶硅电极的界面对EOT以及沟道迁移率的相对作用增大<sup>[5,6]</sup>。据报道,随着介质厚度的日益减小,较薄氧化层中较大的迁移率退化将导致 $I_{d\text{ sat}}$ 下的增益比预期的小得多<sup>[62]</sup>。

硅的氮氧化物可以通过热氮化,或在NO、N<sub>2</sub>O或NH<sub>3</sub>中退火,或由SiO<sub>2</sub>的等离子氮化(见图2-3)等方式生成。介质中加入氮将通过几种途径改变材料的特性(见图2-4)。硼的穿通将使PMOS的 $V_{th}$ 发生很大的漂移,并使介质的可靠性衰退,而氧化层中的氮对硼穿通则起到势垒阻挡作用。随着氧化层中氮分的增加,SiO<sub>2</sub>的折射率也将从 $\eta_{\text{SiO}_2} = 1.46$ 增加到 $\eta_{\text{Si}_3\text{N}_4} = 2.0$ 。另外,相对介电常数将随着氮的增加而线性增加,由 $k_{\text{SiO}_2} = 3.9$ 增大到 $k_{\text{Si}_3\text{N}_4} = 7.5$ 。如式(2.1.4)所示,为了保证一定的EOT,如果使用的介质具有较高的k值,就可以采用物理厚度相对较厚的薄膜,这样就可以减小隧穿电流<sup>[5]</sup>。然而,SiO<sub>2</sub>中添加氮将减小禁带宽度,导致电子及空穴隧穿的势垒高度( $\phi_b$ )降低<sup>[5,8,20,21]</sup>。这意味着因较大的SiON物理厚度而减小的直接隧穿效应将部分地被较小的有效势垒高度所抵消<sup>[18,20,21]</sup>。氮氧化物一般在一氧化氮(NO)中生长或者退火。采用NO生成氮化氧化层的过程中,氮的结合受到制约,并且氮一般只堆积在界面上。对超薄氧化层,必须提高氮的百分比(5%~20%)以进一步降低泄漏和阻止硼穿通<sup>[4]</sup>。在生长sub-1.5nm氧化层时,采用等离子氮化可以更好地控制介质中氮的百分比和分布<sup>[4,24,27-29]</sup>。

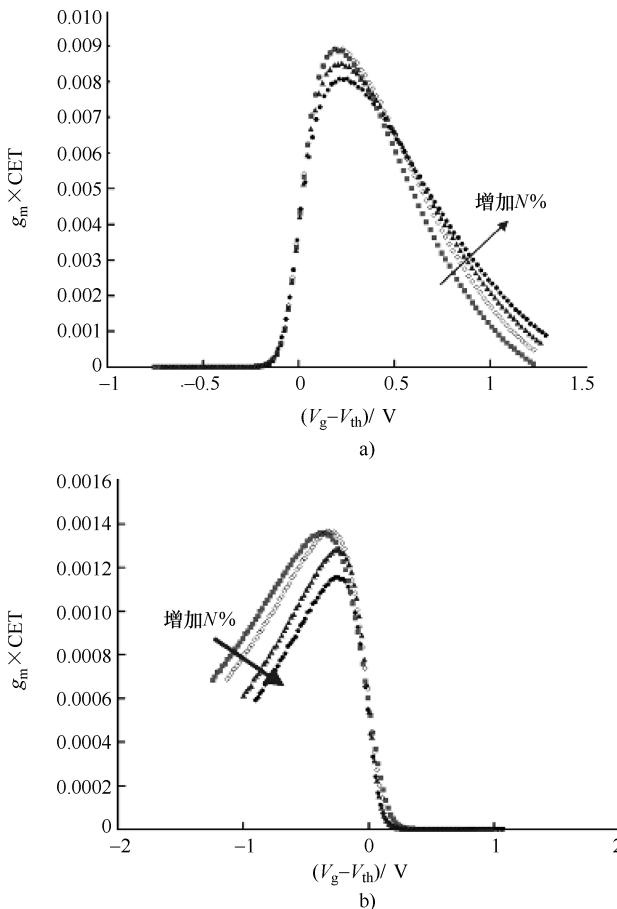

介质中的氮元素影响着NMOS与PMOS器件的迁移率。对PMOS器件,在所有的电场下,空穴迁移率随着氮分的增加而降低。而对NMOS,在低氮分时,电子迁移率的峰值随着氮分的增加而衰退,但是高场下电子迁移率的下降随着氮浓度的增加而有所改善(见图2-5)<sup>[23]</sup>。薄膜中大量的氮会在界面处产生陷阱或者成为载流子散射中心,使迁移率发生巨大的衰退<sup>[10]</sup>。氮对载流子迁移率的影响可以通过氮的剖面分布以及氮元素靠近沟道的程度来调制<sup>[22]</sup>。

为了抑制栅泄漏电流和持续实现介质缩小,针对有更高介电常数的替代介质

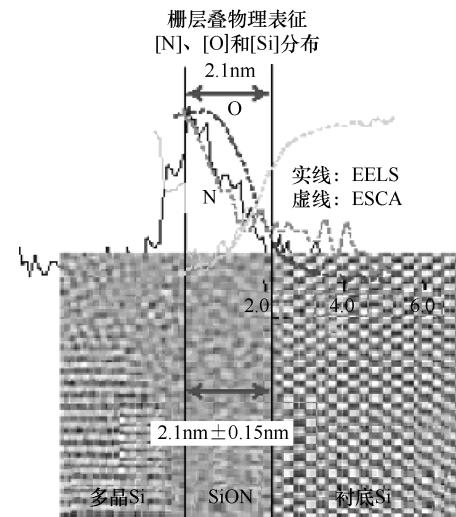

图2-3 电子能量损失谱(EELS)

和化学分析电子能谱(ESCA)

(测量表明:等离子氮化在多晶硅-氮氧化物

界面引入有氮)(来源于参考文献[4])

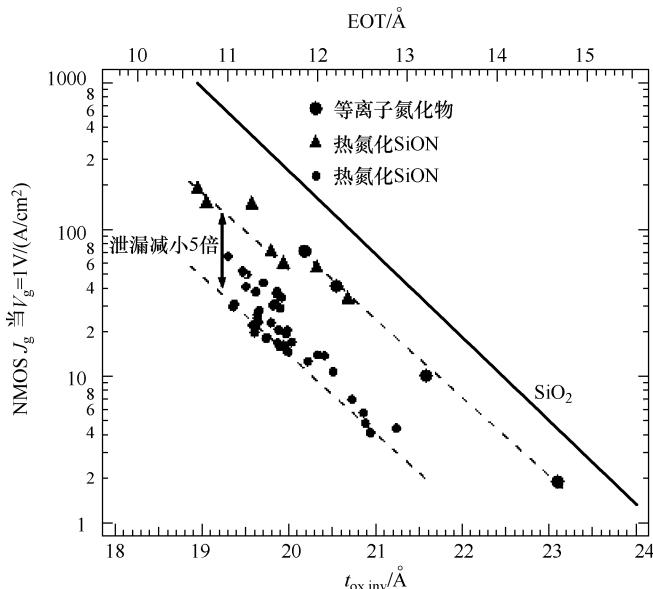

图 2-4 典型的热氮化和等离子 SiON 的  $J_g$ -EOT 关系曲线

(如图 2-2 所示, 增加氮含量使隧穿电流下降, 数据由应用材料公司提供)

材料的热心研究一直在继续。具有高于 SiON 介电常数的材料, 在产生同样的 EOT 时, 采用的物理厚度可以扩大  $k/k_{\text{Si}_3\text{N}_4}$  倍, 因此根据式 (2.1.2) 将可以更好地抑制隧穿电流。氮化硅、氧化铝、氧化锆和氧化铪以及它们的硅酸盐都是正在研究的几种高  $k$  介质。替代介质的重要特性包括介电常数、禁带宽度、硅的能带对齐、热力学稳定性、界面质量、薄膜结构、可靠性、与栅电极以及 CMOS 工艺的兼容性等<sup>[5,6]</sup>。与高  $k$  栅介质材料相关的迁移率衰退 (特别是采用金属栅时) 问题的改善工作已经取得了重大的进展。目前, 与 HfSiON 相关的极富意义的成果已有报道<sup>[25]</sup>。然而, 其他可能的基本特性, 如多晶硅金属氧化层界面的费米能级锁定效应 (这导致阈值电压的巨大漂移) 迟滞了高  $k$  介质的采用<sup>[26]</sup>。高  $k$  介质将很有可能首先用于对泄漏消耗要求非常严格的低功耗应用中。

### 2.1.3 应变工程

从 Stohr 和 Klemm<sup>[30]</sup> 以及 Wang 和 Alexander<sup>[31]</sup> 第一次制备得到均匀的 SiGe 合金到现在已有近 60 年了。Johnson 和 Christian 的开创性工作以及 Braunstein 等人关于单晶以及多晶 SiGe 合金的一系列文章为今天将 SiGe 引入先进的 CMOS 器件奠定了基础<sup>[33-36]</sup>。这些工作包括测量了锗在硅中摩尔百分比发生变化时, 晶格常数和禁带宽度的变化。他们的结论显示, 晶格常数从硅的 5.43 到锗的 5.66 之间呈现线性变化 (基于后来结果的二次拟合)。在锗单晶与硅单晶之间约

图 2-5 等离子氮化长沟道 a) NMOS 和 b) PMOS 器件的归一化跨导

(随着氮分的增加 NMOS 的高场跨导得到改善, 而 PMOS 的高场跨导衰退)

4.2% 的晶格失配导致了 SiGe 合金电子能带结构的重大变化。不像晶格常数在整个组分范围内保持近似线性变化,  $Ge_xSi_{1-x}$  合金的能带开始以较小的斜率线性下降, 而当硅中的锗达到 85% 时将以很陡峭的斜率下降。当硅在锗中的摩尔百分比下降到 15% 时, 合金的导带由一个类似于硅的导带结构 ( $E_g = 1.14\text{eV}$ ) 变到类似于锗的导带结构 ( $E_g = 0.67\text{eV}$ ), 导致能带发生跳变。在合金组分的变化范围内, 价带结构基本保持不变, 其最大值在中心  $k$  (000) 处。合金的导带开始时类似于硅, 其最小值沿着 [100] 晶向在  $0.8\times$  处。但是在硅中锗的组分达到 85% 时, 能带最小值由类似于硅跳变到类似于锗。

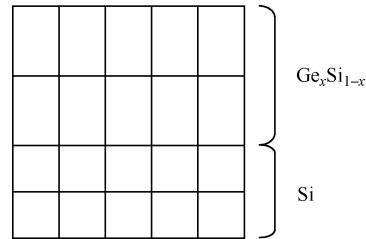

在硅上  $Ge_xSi_{1-x}$  的赝配淀积要求在生长方向上 ([100] Si, 见图 2-6) 对晶格常数进行重大调整。在与生长方向平行的方向上, 在硅中锗组分的整个变化范

围内，都要求晶格常数必须与硅的晶格常数保持一致。硅和锗晶格的金刚石结构变为在与生长方向平行的方向上存在明显压应力的四方结构，因此应变的程度与硅中锗的克分子百分比相关。由硅上  $\text{Ge}_x\text{Si}_{1-x}$  的比例淀积带来的应变通过分割能带而改变了导带和价带的结构。例如，应变合金的价带被分割为重空穴和轻空穴两个能带。因为禁带宽度是价带顶与导带底的能量差，在硅中存在一定锗组分时，应变  $\text{Ge}_x\text{Si}_{1-x}$  的禁带宽度将明显小于非应变合金的禁带宽度<sup>[38-41]</sup>。

$\text{SiGe}$  合金禁带宽度变窄导致了异质结构  $\text{Si}/\text{Ge}-\text{Si}$  中硅和合金之间的能带偏移。在 I 类能带排列中，对应硅上淀积  $\text{Ge}-\text{Si}$  合金，偏移发生在价带而导带基本对齐。而在 II 类能带排列中， $\text{SiGe}$  上赝配生长硅，导带和价带都发生偏移。 $\text{SiGe}$  合金的另一个重要特征是与硅相比具有较高的空穴迁移率，这是因为锗的空穴迁移率较高。另外，由于迁移率是散射和有效质量的函数，因此在应变  $\text{SiGe}$  合金中迁移率比非应变合金有进一步明显提高。较低的有效质量和较小的散射是由于能带图中简并度的提升<sup>[42-47]</sup>。

硅上  $\text{SiGe}$  的赝配生长和用于基础研究的异质结构都采用分子束外延。然而，在实际的生长中， $\text{SiGe}$  的淀积一般采用化学汽相淀积（CVD）的方法。典型的外延 CVD 系统的设计要考虑气氛和减压工艺。原子级的清洁表面是选择性淀积的关键，硅的表面一般都要采用稀释的氢氟酸进行预处理。在淀积之前，晶圆首先在炉内高温、通氢气的气氛下烘培，去掉表面自然形成的氧化层。而淀积过程本身在较低的温度下进行，采用的温度取决于淀积采用材料的化学组成。一般用硅烷或者二氯硅烷作为硅源，用锗烷作为锗源，并且为了提高氧化物和氮化物的选择性，采用  $\text{HCl}$  气体与硅烷和锗烷混合在一起<sup>[48]</sup>。温度小于  $800^\circ\text{C}$  时在硅上可以获得一个近似理想的选择性  $\text{SiGe}$  淀积。独立区域温度控制的反应室设计与最佳灯加热方式的结合，再加上精确的温度控制和气流控制就可以实现均匀的淀积，且掺杂可高达  $10^{21}$ 。气体混合方式、温度和反应室设计的优化，以及掺杂气流与锗气流的分开，可以在整个晶圆上获得锗与掺杂浓度分布标准偏差（ $1\sigma$ ）小于 1% 的均匀性。

## 2.1.4 快速热处理技术

快速热处理（Rapid Thermal Processing, RTP）是一项有着十余年历史的非常重要的半导体制造技术，它的发展历程可以回溯到 20 世纪 60 年代<sup>[49]</sup>。RTP

图 2-6 硅上  $\text{Ge}_x\text{Si}_{1-x}$  的比例淀积导致

$\text{SiGe}$  合金晶格存在压应变

( $\text{Ge}_{0.2}\text{Si}_{0.8}$  的晶格常数比硅约大 1%，

并且在硅上赝配生长的临界

厚度可达几十纳米)

能取代传统的分批装片炉热处理有两个主要原因：优良的气氛控制和减小的热消耗。气氛控制是 RTP 得到广泛应用的最初动力。最初 RTP 工艺的应用是形成硅化锑 ( $TiSi_2$ )，正好使得 RTP 特长得到充分发挥。工艺中要求氮气气氛必须严格控制使环境氧气的水平小于  $10\text{ppm}^{\ominus}$ 。这种低氧含量在低流片量的单片 RTP 反应腔中很容易实现，而在大流片量的批式炉管中则很难可靠地维持。早期 RTP 系统的缺点是温度控制和重复性不够好，但是生长  $TiSi_2$  对温度控制和可重复性不很敏感，而 RTP 较短的工艺时间则具有明显优点，可以减小热退化和横向过度生长或桥接。

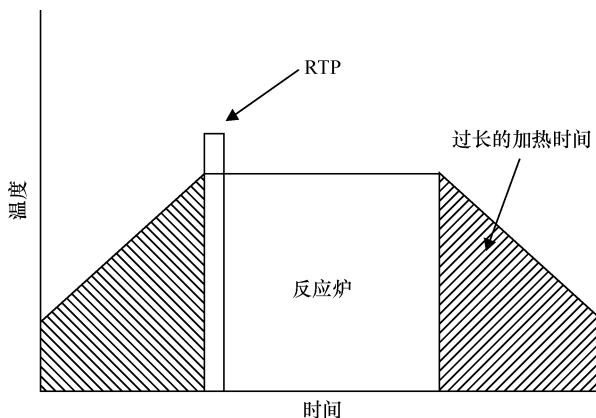

RTP 取代分批装片炉的第二个动力是可以减小晶圆在高温中的暴露时间。在高温氧化或退火时，加热炉中温度缓慢的上升和下降（典型的温度变化速率为  $10^\circ\text{C}/\text{min}$ ）使晶圆长时间的处于高温下，这些过长的时间将导致不必要的掺杂和缺陷扩散。如图 2-7 所示，RTP 使温度上升和下降加速，典型的可以达到  $75^\circ\text{C}/\text{s}$ ，这样就减小了晶圆过多的热暴露和不希望的扩散。

图 2-7 在 RTP 和批式炉之间的“热暴露”对比

**RTP 技术** 快速热处理要求设备具有特定的技术能力，包括精确的气氛控制、高达  $250^\circ\text{C}/\text{min}$  的升温速度、峰值退火温度均匀性（ $3\sigma$  为  $3^\circ\text{C}$ ）、 $300 \sim 1200^\circ\text{C}$  的温度控制范围和不受晶圆发射率影响的温度测量。在多数的 RTP 工序中都要求精确的气氛控制，包括金属的硅化处理、注入退火和热氧化。早期 RTP 设备的气氛控制依赖于大范围的净化，因为炉腔对生产环境是“打开的”，以装卸每个晶圆。这限制了生产量和最终能达到的气氛控制。一种改进的方式是将 RTP 腔装在集簇设备上，为实现纯净的氮气气氛，采用真空装载锁完成快速的气体交换。集簇设备也可以用于单腔或者多腔工序。气流模型的改进使非装载锁系

$\ominus$  ppm，即 parts permillion，百万分之一。

统也可以在高产量的情况下达到低于 1 ppm 的气体纯度。在腔门打开时，这些系统在晶圆输运过程中一般采用高速气体纯化以最大程度地避免氧气的侵入。

在注入退火时，为了达到要求的升温速度，RTP 要求由晶圆和直接支撑晶圆的结构所组成的整个被加热物体的“热质量”尽量得小。大多数 RTP 设备使晶圆与腔体之间热隔离，使用灯辐射方式满足快速升温时的热需求。另外一种方式是将晶圆快速地放入到一个其热质量比晶圆大得多的已加热环境中，此时晶圆引起的环境温度变化将很小，然后晶圆逐渐达到环境温度。

为了在 RTP 要求的较大温度范围内均匀性达到  $3\sigma$ （在一个晶圆内和多个晶圆之间所有测量点的标准偏差的 3 倍）为 3°C 的要求，需要对均匀性实现有效的控制。由于晶圆中心与边缘处表面积与体积之比不相同，在 RTP 加热过程中的不同部分要求不同的能量分布。如图 2-8 所示，在升温过程中，晶圆边缘的温度一般高于中心的温度，然而在温度稳定后和降温时，边缘的温度又会低于中心的温度。在采用灯加热方式的 RTP 设备中，解决这一问题的方法是在腔体的中心和边缘的不同区域采用不同的灯组合，并且在加热过程中调整不同灯的功率，保证不同时刻温度的均匀性。为实现积极实时的温度均匀性控制，最先进的系统采用高速、多点测量和多区域控制。

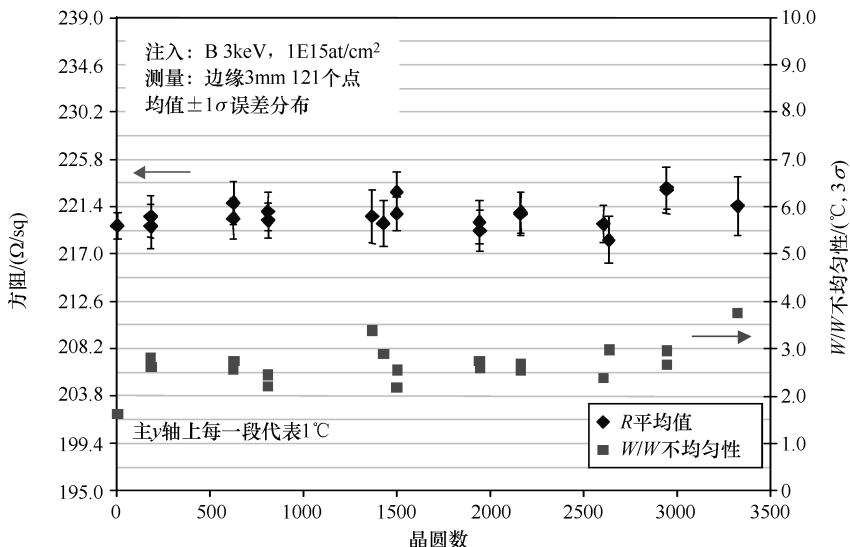

对均匀性控制最具挑战性的工艺是用于现代器件注入离子激活的高温尖峰退火。尖峰退火并不要求保持在峰值温度，而是到达预期的温度后马上降温，实现一个三角形或者尖刺形的温度-时间分布。注入离子的激活是与温度非常敏感的工艺，为了达到晶体管源漏区浅结的要求，需要实现  $3\sigma$  为 3°C 的温度控制。图 2-9 所示为在 300mm 晶圆上距边缘为 3mm 范围内实现了上述温度均匀性的情况。

RTP 设备测温系统采用光学测温，它测量晶圆本身的灰体辐射以确定温度。在老式 RTP 系统中，用热电偶直接接触测量温度，但是这种方式由于热接触方式以及局部的热扰动会引起温度误差和不均匀性已被淘汰。准确的光学测量要求知道测量波长处晶圆发射率的数值（晶圆发射的能量与同样温度下理想黑体发射的能量之比）。测温装置设计采用两种主要的方式来应对这些挑战。一种方式是在晶圆下方创造一个高反射率的环境以实现理想黑体腔的特性，因为这能增强

图 2-8 未能实现有效均匀性控制的中心和边缘温度分布

图 2-9 RTP 尖峰退火在  $3\sigma$  为  $3.2^\circ\text{C}$  控制时的方阻均匀性/可重复性

晶圆的有效发射率并减小可能出现的测量错误。另外，用一个分离的探针实时测量发射率并且对任何存在的误差进行校正<sup>[51]</sup>。第二种方式是实时测量灯功率周期变化的反射系数来获得假设无晶圆发射时的发射率（发射率 = 1 – 反射系数）。然后，用测量的发射率校正光学测温仪的读数<sup>[52]</sup>。

这些技术，包括气氛控制、低的热质量、均匀性控制和温度测量，共同构成了 RTP 设备的核心，并使 RTP 在很宽的温度范围内得到广泛的应用。对未来的 65nm 到 45nm 的器件，RTP 退火的热消耗即使是已经受到了限制，但对某些工艺步骤来说还是太高。一种方案是通过仅在晶圆的表面加热使暴露时间减小到毫秒级。这被称作热通量退火，可以用闪光灯或激光实现<sup>[53,54]</sup>。

**RTP 应用** 随着 RTP 工艺设备的改进和成熟，现在具备了用于完成 CMOS 和 DRAM 制造的所有的热退火和氧化工艺。主要的退火应用包括难熔金属硅化物的形成（例如  $\text{TiSi}_2$ 、 $\text{CoSi}_2$ 、 $\text{NiSi}$ ）、离子注入退火、BPSG 的稳定性和回流，以及接触金属退火（如  $\text{TiN}$ ）。主要的氧化应用包括栅氧氧化和氮化、隔离槽内壁隔离层氧化和牺牲氧化层氧化。

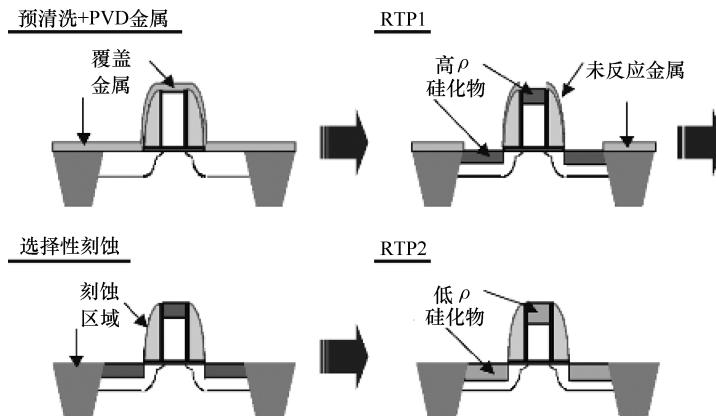

从 20 世纪 80 年代开始，自对准硅化钛技术被引入到 CMOS 工艺中，减小了源漏和棚区方阻，在晶体管与金属互连之间实现较好的欧姆接触。这道工艺是自对准的，因为在覆盖溅射金属后，金属仅在金属源漏和棚区位置直接与硅接触的地方形成硅化物，并不在侧墙隔离层和隔离结构上形成硅化物。近几年，为了进一步缩小器件尺寸，使用的金属已由钛变为钴再到镍。如图 2-10 所示，自对准金属硅化物一般经过两个 RTP 步骤形成。在清洗和溅射或物理汽相淀积（Physi-

cal Vapor Deposition, PVD) 完成覆盖金属膜淀积之后, 第一次 RTP 退火 (通常称为 RTP1) 形成金属硅化物。RTP1 的温度必须高到能使金属-硅发生反应并且生成物要达到足够的厚度和希望的金属硅化物相, 但是温度又要足够低以免金属硅化物横向生长到栅的侧墙隔离层上, 否则将导致栅与源漏短路。气氛控制对 RTP1 来说是关键, 因为如果气体氛围中即使氧的比例只有百万分之几, 金属薄膜也会很快被氧化耗尽。

图 2-10 自对准工艺顺序

在选择性刻蚀移除侧墙隔离层和隔离区域上未反应的金属后, 第二次退火 (RTP2) 通过改变金属硅化物相或组分来减小方阻。RTP2 一般要求温度高于 RTP1 几百度, 这个温度太高以致于在二次退火这一步内不会生成金属硅化物。RTP2 的最高温度一般受到两个因素制约。一是温度太高会出现形态衰退, 称作凝聚。另外如果温度太高可能使硅化物的相或结构发生变化, 导致电阻退化。

钛的硅化物是首次在逻辑应用中被广泛使用的材料。 $TiSi_2$  的 C49 相一般在 RTP1 阶段,  $650^\circ\text{C}$ 、30s 的条件下形成。RTP2 将 C49 相硅化物变为 C54, 可以实现大约  $(13 \sim 16)\mu\Omega \cdot \text{cm}$  的低电阻率, RTP2 的工艺条件一般是  $850^\circ\text{C}$ , 20s 或者更低。随着器件尺寸的缩小, 使得钛硅化物的应用范围很难扩展到  $0.25\mu\text{m}$  以下。当线宽和金属硅化物的厚度进一步减小时, 使 C49 到 C54 相变成核过程中不出现硅化物的凝聚将变得非常困难<sup>[55]</sup>。这些限制要求高温时间必须更短, 而在高温时工艺窗口最宽。

为了改善缩小变窄的线宽, 作为  $TiSi_2$  的替代者, 选用了钴硅化物。在钴自对准硅化物工艺中, RTP1 的工艺条件一般是  $500 \sim 550^\circ\text{C}$ 、30 ~ 60s 形成  $CoSi$ 。RTP2 的工艺条件一般是  $750 \sim 800^\circ\text{C}$ 、30s 使  $CoSi$  变为  $CoSi_2$ , 此时电阻率将降到  $14 \sim 18\mu\Omega \cdot \text{cm}$ 。在覆盖金属淀积期间, 钴一般被钛或 TiN 覆盖以防止其氧化。

覆盖物将在 RTP1 与 RTP2 之间被选择性刻蚀掉。

在线宽缩小到 50nm 之下，钴硅化物也开始受到器件尺寸缩小的制约，并且驱使业界用镍硅化物取代之。一直到 30nm 线宽时，NiSi 还可以保持较低的方阻<sup>[56]</sup>。NiSi 可以用一步 RTP，而不是如图 2-10 所示的两步 RTP 工艺实现，RTP 温度一般在 400 ~ 500°C。然而，栅长小于 100nm 的方阻的减小表明，这会造成窄线条产生过量的硅化。采用两步 RTP 控制 NiSi 的形成可以解决过量的硅化和由多晶耗尽及结泄漏带来的问题。第一步，RTP1，形成富镍相的硅化物 Ni<sub>2</sub>Si，而 RTP2 完成了实现低电阻率相 NiSi 的反应。两步形成 NiSi 要求 RTP 设备具有先进的能力。首先，RTP1 要求较低的工艺温度，250 ~ 350°C。这低于一般光学测量仪的测量范围。第二步，RTP1 要求精确地控制温度均匀性。硅化物的厚度是由反应温度而不是由淀积的镍的厚度决定的，并且硅化物生成反应对温度极其敏感<sup>[57]</sup>。最后，像之前的钛和钴一样，NiSi 要求精确地控制环境气氛，氧的含量要低于 1 ppm。

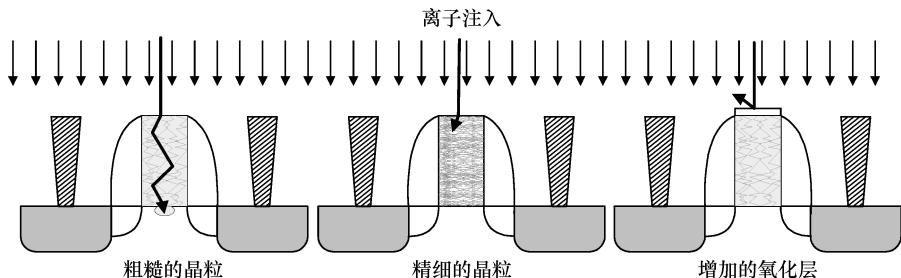

CMOS 工艺主要依赖于离子注入和 RTP 退火以确定对器件性能有决定作用的杂质分布。热退火的作用是修复离子注入带来的损伤并使杂质原子处于替位状态，起到提供载流子的作用。由于 RTP 精确的热消耗控制，使得晶体管尺寸在横向和纵向的缩小成为可能，因此已取代了用于离子注入退火的批式加热炉工艺。如图 2-7 所示，由于减少了过多的热暴露时间，使 RTP 在实现与批式加热炉退火相同的方阻时，能实现更浅的结。

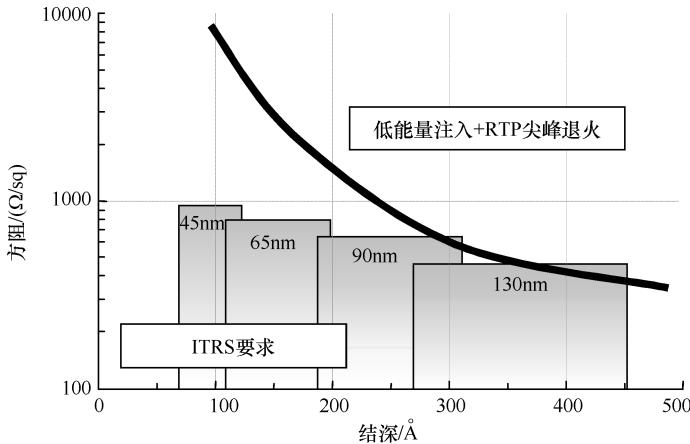

RTP 热消耗已经得到连续的减小，从原先 950 ~ 1050°C 之间 30 ~ 60s 保温时间的退火变为 1050 ~ 1100°C 的 0s 尖峰退火。将升温速度从 50°C/s 提高到大于 250°C/s，可以使 RTP 热消耗得到进一步减小。为了满足国际半导体技术路线图 (International Technology Roadmap for Semiconductors, ITRS) 对源漏和其延伸的轻掺杂结的要求，热消耗还需要得到进一步减小。ITRS 规定了这些结的结深和方阻的目标，如图 2-11 所示。图中同时显示了 RTP 尖峰退火的低能注入耦合的典型性能。

虽然 90nm 的要求可以达到，但 65nm 要求结深和方阻进一步减小。几个技术的应用将使这种缩小成为可能，这些技术包括热熔退火、注入区的固态外延再生长，以及能在 RTP 退火时抑制扩散的离子同步注入。

几个因素能将 RTP 拓展应用到 CMOS 工艺中所有的热退火和氧化。首先，整个工艺流程中热消耗控制是关键器件尺寸能实现缩小的根本。第二，所有的氧化层厚度和退火步骤都已经缩小到单片加工工艺的范围。第三，新颖的工艺，例如现场水汽生成，已经使改善器件性能成为可能<sup>[59,60]</sup>。最后，单片工艺减小了周期时间，减少了工作量，使改善生产效率和生产时间有了可能<sup>[61]</sup>。

总之，RTP 在半导体中是一项关键的和促成性的技术。低温工序和毫秒级热

暴露的扩展能力将使器件的继续缩小成为可能。在未来的几年时间里，单片工艺的经济性和高效率将持续的促使热工艺从批式向 RTP 技术转换。

图 2-11 显示有 RTP 能力和 ITRS 要求的方阻与结深关系曲线

## 2.2 在 CMOS 尺寸缩小中与前道工序相关的器件问题

CMOS 工艺持续缩小到 sub-100nm 范围后，引起了大量在过去不太重要的器件物理和工艺方面的问题。因此，对 CMOS 技术，必须引入一些新的材料和新的器件结构，才能跟上国际半导体技术路线图预测的尺寸缩小步伐。本节我们将研究在逐渐缩小的 CMOS 器件中出现的与前道工艺相关的重要物理效应，并从器件和设计的观点出发来讨论一些新的工艺技术的影响。

### 2.2.1 CMOS 缩小的挑战

在过去的 30 年，传统的体硅 MOSFET 结构得到了成功的缩小。然而，在纳米时代，持续的缩小面临着基本的物理阻碍和经济性制约。下面简要分析影响 MOSFET 缩小的主要问题和因素。

**短沟道效应** 在理想的 MOSFET 中，栅压对沟道导通状态有着完全的控制。然而，当栅长变得更小时，漏区将对沟道电势影响更大。栅长非常短的器件，阈值电压  $V_{th}$  将明显减小，导致关态泄漏激增，在漂移区，阈值电压的变化将变得非常大。为了抑制短沟道效应，必须减小漏与沟道之间的耦合，而增加栅与沟道之间的耦合。漏与沟道之间耦合的减小要求沟道和漏区有较小的耗尽区宽度，这可以由衬底的掺杂分布工程来完成。沟道逆掺杂分布（即掺杂浓度在表面最低，向衬底内部不断增加）和 halo 掺杂分布是减小耗尽区宽度的有效方法。源和漏

结也要求相应减小。由于 halo掺杂有着很高的掺杂浓度，将在漏-衬结附近产生高场，导致能带间的隧穿引起较高的结泄漏。为了增加沟道到栅的耦合，必须采用较薄的栅氧电学厚度。

**等效栅氧厚度缩小** 较薄的栅氧，或者较大的单位面积栅电容，是改善关态和开态器件特性所必需的。现有最新技术使用了具有更好抗杂质穿通作用的氮化工艺，栅氧厚度已经减小到了 $20\text{\AA}$ 以下。对于这样薄的 $\text{SiO}_2$ ，即使电源电压随之减小，直接栅隧穿泄漏还是不能忽略。这引起了很严重的关系功耗问题。为了达到指定的等效氧化层厚度(EOT)，如果采用高 $k$ 介质，可以使用比 $\text{SiO}_2$ 更厚的物理厚度，这是解决这个问题的潜在方案。当前，高 $k$ 介质的一些问题依然在研究，例如迁移率衰退和平带电压漂移。了解了这些工艺技术的挑战后，必须开发出一些电路和系统级的技术以克服栅泄漏电流问题。具体分析不同应用类型的差异（即确定高性能、低工作功耗和待机功耗应用），也有助于工艺技术与设计需求之间实现更好的相互匹配。

与栅介质EOT缩小相关的是多晶硅栅耗尽效应。当器件处于开态时，对典型的多晶硅掺杂浓度，在多晶硅中会存在一个薄耗尽层（约 $1\text{nm}$ ）。这个耗尽层削弱了栅到沟道的容性耦合，或者说减小了栅的过驱动电压。当栅介质的EOT接近 $1\text{nm}$ 时，栅耗尽层的附加影响就变得很重要了。虽然增加栅的有效掺杂浓度很有帮助，完全解决这个问题的一种方式是使用金属栅电极。

沟道中的量子力学效应也给栅氧化层电容引入了一个附加的串联电容。当垂直电场足够高时，在当前和未来CMOS器件中就会出现下述情况，即沟道中载流子的垂直运动（与衬底表面垂直）将被限定在一个势阱中。与这个运动相关的能态将从经典情况下的连续态变为离散态，由此造成的一个影响是载流子分布的峰值位于离开衬底氧化层界面很小距离（约 $1\text{nm}$ ）的地方，这意味着给栅介质EOT又额外增加了几 $\text{\AA}$ 的厚度。与多晶硅栅耗尽效应一样，这也似乎是一个无关要紧的问题，直到 $\text{sub-}100\text{nm}$ 技术节点，这个效应才需要给以关注。量子效应与几个因素有关，如垂直场、衬底掺杂和在超薄体MOSFET中硅体的厚度。这是一个基本的物理限制，不能简单地通过工艺改进解决。

**沟道载流子迁移率** 沟道载流子迁移率直接影响着电路和器件的性能。随着器件的缩小，有几个因素对迁移率产生不良影响。为了控制短沟道效应，通常采用的高沟道掺杂浓度，将导致更多的杂质散射，使迁移率降低。由于有些因素不可缩放，如热电压和硅的禁带宽度（禁带宽度影响阈值电压的设定，但是并没有被认为是影响缩放的基本障碍），电源电压的缩小比例跟不上器件尺寸的缩放比例。因此，沟道中载流子所处的平均垂直电场逐渐增加。根据迁移率模型，较高的垂直电场使迁移率衰退。由于STI工艺在沟道中产生了不希望的应力，因此也引起 $n$ -MOSFET迁移率的衰退。另外，大多数待选的正在评价中的高 $k$ 介质

的界面都比热  $\text{SiO}_2$  棚介质的界面更差。较差的界面也使沟道载流子迁移率衰退并对使用高  $k$  介质的 MOSFET 器件的性能退化有直接的影响。

改善载流子迁移率有几个可能的方案。如前面所介绍的，ITRS 预测了沟道应变工程技术的引入。在一些新颖的器件结构中，如绝缘衬底上的超薄体硅（即 SOI）或者 FinFET，沟道掺杂极轻，这也有助于改善载流子迁移率。

**工艺波动** 工艺波动对设计而言是一个需要考虑的非常重要的问题。随着器件的缩小，关键器件参数如阈值电压  $V_{\text{th}}$  的波动将增加。引起波动的原因很多，主要来源包括掺杂源的波动、氧化层厚度的起伏、特征尺寸（CD）的起伏和线条边缘的不平直。对较小的器件尺寸，沟道中掺杂总量降低，因此统计波动上升了  $1/N^{1/2}$ ，这里  $N$  是杂质总量。虽然最终的  $V_{\text{th}}$  变化依赖于杂质分布，但是从阈值电压的角度而言，将影响器件的进一步缩小。一些要求沟道掺杂浓度非常低的新颖的器件结构，如双栅 MOSFET，可以用来解决这个问题。但是这些器件可能对其他的波动源很敏感（如硅体厚度）。随着器件尺寸减小，CD 和薄膜厚度变化的容差也随之变小。除了工艺改进以实现更好的成品率和性能之外，需要采用更多的鲁棒性设计方法。

**新颖的器件结构** 虽然体硅 MOSFET 的栅长被证实可以降到  $15\text{nm}^{[64]}$ ，但是 CMOS 的最终缩小将可能需要采用新颖的器件结构。最近几年，FinFET 及其几种多栅结构在业界和科研中已被证实可以成功地实现尺寸缩小。超薄体 SOI MOSFET 也是极有前途的选项。缩小器件尺寸的实用解决方法必须是能以性能改进或者减小每项功能开销的形式提供较好的收益。这将要求以一种经济的方式整合各种新颖的工艺和器件革新。

## 2.2.2 量子效应模型

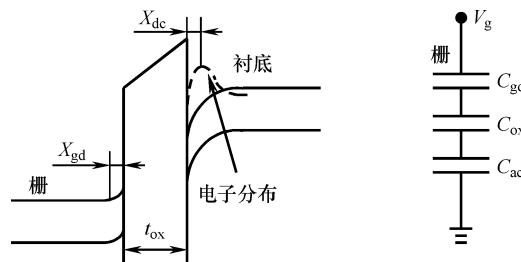

以前，棚氧厚度是棚-沟道电容中支配性的因素。然而，随着棚氧厚度缩减到  $20\text{\AA}$  以下，其他两个因素变得重要。一个因素与沟道中反型层载流子的量子限制效应相关。另一个是在反向栅偏置时棚耗尽层电容。

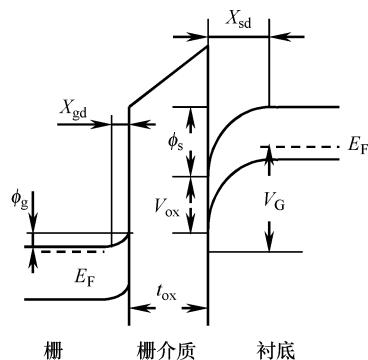

直接影响关态电流的热电压不能缩小。因此，阈值电压必须足够大以使关态泄漏电流可以接受。再结合考虑到驱动电流的要求，就限制了电源电压的缩小。结果是沟道和氧化层中的垂直电场随着器件的缩小而增加，衬底氧化层界面的强垂直电场形成了一个势阱，这将限制反型层载流子在垂直方向的运动。在垂直运动方面，载流子将变成具有离散本征能级的二维电子气。另外，反型层载流子的峰值分布取决于不同能带中所有载流子的波函数，其峰值离衬底氧化层界面  $1 \sim 2\text{nm}$ ，从而在棚电极下产生额外的电容（见图 2-12）。当棚介质 EOT 缩小到  $20\text{\AA}$  以下时，此电容不再可以忽略。

反型层电荷分布的严格分析处理要求对氧化层和衬底区中泊松方程和薛定谔

图 2-12 额外的电容

(左图为反型偏置的  $n^+$  多晶硅栅  $n$  沟道 MOSFET 的能带图。沟道电子位于衬底界面附近势阱的离散能带上。电荷中心与衬底界面距离为  $X_{dc}$  (dc 电荷中心)。多晶硅栅的耗尽宽度是  $X_{gd}$  (在 2.2.3 节讨论)。右图为栅电容层叠的交流等效电路。 $C_{gd}$ 、 $C_{ox}$  和  $C_{ac}$  分别是栅耗尽电容、栅氧化电容和反型电荷 ac 电荷中心带来的电容)

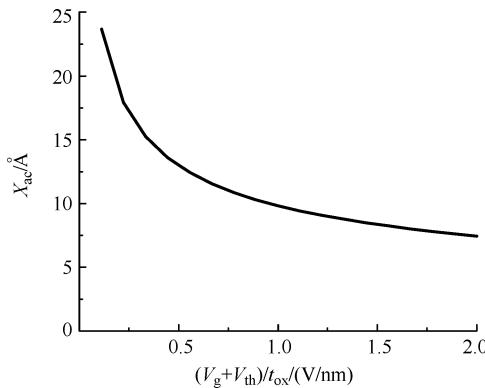

方程自洽求解，这需要采用数值计算方法。反型层载流子分布取决于栅电压和器件参数，如沟道掺杂浓度和栅氧化层厚度。基于数值仿真结果和实验数据，提出的一个经验模型可以对反型电荷 ac 电荷中心有一个简单的精度较好的估算<sup>[65]</sup>。对于薄氧化层和典型沟道掺杂水平情况，在 ac 电荷中心  $X_{ac}$ 、栅电压  $V_g$ 、阈值电压  $V_{th}$ 、和栅氧化 EOT  $t_{ox}$  之间存在如下普遍关系：

$$X_{ac} = 6.20 \times 10^{-5} \left( \frac{V_g + V_{th}}{t_{ox}} \right)^{-0.4} \quad (2.2.1)$$

式中， $V_g$  和  $V_{th}$  的单位是 V (伏特)，而  $X_{ac}$  和  $t_{ox}$  的单位是 cm (厘米)。图 2-13 所示为式 (2.2.1) 表示的关系。在 90nm 节点之下， $X_{ac}$  的范围是 8~10Å，使反型层电容的等效厚度 (CET) 增加 3Å。对大约 10Å 的 EOT 的栅介质，这将明显地引起栅电容的减小。

图 2-13 ac 电荷中心  $X_{ac}$  与  $(V_g + V_{th})/t_{ox}$  之间的普遍关系

上面模型是基于传统的体硅 MOSFET 结构。在一些新颖的器件结构中，如

双栅 MOSFET 或超薄体 SOI MOSFET，由于边界条件的不同，描述数值结果的公式可能会不同。

### 2.2.3 多晶硅栅耗尽效应

当栅氧中存在电场时，静电边界条件使多晶硅靠近氧化层界面附近的能带弯曲。当栅氧足够薄时，硅栅和沟道之间的耗尽区所贡献的电容就需要特别注意了。图 2-12 显示了反型区栅电容各分量的等效电路。等效栅电容（即 CET）与这些电容分量的关系为

$$\begin{aligned} \frac{1}{C_g} &= \frac{1}{C_{gd}} + \frac{1}{C_{ox}} + \frac{1}{C_{ac}} \\ &= \frac{X_{gd}}{\varepsilon_0 \varepsilon_{Si}} + \frac{t_{ox}}{\varepsilon_0 \varepsilon_{ox}} + \frac{X_{ac}}{\varepsilon_0 \varepsilon_{Si}} \end{aligned} \quad (2.2.2)$$

式中，变量的含义与图 2-12 中一致。 $\varepsilon_0 = 8.85 \times 10^{-12} \text{ F/m}$ ，是真空介电常数； $\varepsilon_{Si} = 11.7$ ，是硅的相对介电常数。在式 (2.2.2) 中，栅介质的物理厚度为  $t_{ox}$ ，相对介电常数为  $\varepsilon_{ox}$ 。栅介质的 EOT 由下式给出：

$$\text{EOT} = t_{ox} \frac{\varepsilon_{SiO_2}}{\varepsilon_{ox}} \quad (2.2.3)$$

式中， $\varepsilon_{SiO_2} = 3.9$ ，是  $SiO_2$  的相对介电常数。因此，从电容角度考虑，厚度为  $t_{ox}$  的栅介质与厚度为 EOT 值的  $SiO_2$  膜等效。通常用 CET 描述总的有效栅电容

$$\text{CET} = \frac{\varepsilon_0 \varepsilon_{SiO_2}}{C_G} \approx \text{EOT} + \frac{X_{gd} + X_{ac}}{3} \quad (2.2.4)$$

$X_{gd}$  和  $X_{ac}$  是与偏置有关的，因此 CET 也依赖于栅压  $V_G$ 。在典型的器件工作条件下，栅耗尽和量子效应对 CET 分别贡献有几 Å 的厚度，所以使用超薄栅介质时，CET 将明显大于 EOT（按百分比计算），具体大小由栅介质决定。较薄的 CET 和较高的栅压将转化为较高的反型电荷密度和较好的器件特性，因此，随着每一代工艺技术中采用的电源电压的减小，栅层叠结构的缩小不仅要求栅介质（EOT）变薄而且要求栅耗尽效应缩小 ( $X_{gd}$ )。

采用静力学可以简单估算栅耗尽效应和 CET。考虑一个偏置到反型区的 n - MOSFET 的 n + 型多晶硅（见图 2-14），平带电压 ( $V_{FB}$ ) 和衬底电压降 ( $\phi_s$ )、栅电压降 ( $\phi_g$ )、氧化层电压降 ( $V_{ox}$ ) 之和等于栅压  $V_g$ 。

图 2-14 n - MOSFET 栅正偏置时的能带图

(靠近氧化层界面的多晶硅栅中存在着有限厚度的耗尽层)

$$V_g = V_{FB} + V_{ox} + \phi_s + \phi_g \quad (2.2.5)$$

栅的掺杂浓度一般高于沟道掺杂浓度。因此在亚阈区，氧化层界面电位移的连续性意味着栅极的能带弯曲小于衬底的能带弯曲。在强反型条件下，栅氧上界面的边界条件是

$$\varepsilon_{ox} \frac{V_{ox}}{t_{ox}} = \varepsilon_{Si} E_{gate} \quad (2.2.6)$$

使用耗尽近似和假定栅的掺杂浓度 ( $N_{gate}$ ) 为均匀掺杂时，栅极电场  $E_z$  可以使用高斯定理求解

$$\frac{dE_z}{dz} = \frac{qN_{gate}}{\varepsilon_0 \varepsilon_{Si}} \quad (2.2.7)$$

因此栅的电压降为

$$V_{ox} = \gamma_G \sqrt{\phi_g} \quad (2.2.8)$$

式中， $\gamma_G \equiv \sqrt{2\varepsilon_0 \varepsilon_{Si} N_{gate}} / C_{ox}$ ，其中  $C_{ox} = \varepsilon_{ox} \varepsilon_0 / t_{ox}$ 。

在强反型开始前，大约在  $2\phi_b = 2(k_B T/q) \ln(N_{sub}/n_i)$  时，衬底能带弯曲  $\phi_s$  达到饱和。注意

$$V_{th} = V_{FB} + 2\phi_b + \gamma_S \sqrt{2\phi_b} \quad (2.2.9)$$

式中， $\gamma_S$  的定义与  $\gamma_G$  的定义相似，仅用  $N_{sub}$  代替  $N_{gate}$ 。因此式 (2.2.5) 变为

$$\phi_g + V_{ox} - (V_g + \gamma_S \sqrt{2\phi_b} - V_{th}) = 0 \quad (2.2.10)$$

当  $V_g > V_{th}$  时，栅耗尽宽度  $X_{gd}$  可由式 (2.2.6 ~ 式 2.2.10) 求出

$$X_{gd} = \frac{\varepsilon_0 \varepsilon_{Si}}{C_{ox}} \left[ \sqrt{1 + \frac{2C_{ox}^2}{\varepsilon_0 \varepsilon_{Si} q N_{gate}} (V_g - V_{th} + \gamma_S \sqrt{2\phi_b})} - 1 \right]$$

$$\approx \frac{C_{ox} (V_g - V_{th} + \gamma_S \sqrt{2\phi_b})}{q N_{gate}} \quad (2.2.11)$$

对于给定的栅压、氧化层厚度、栅掺杂浓度和阈值电压，结合电荷质心模型，可以由式 (2.2.4) 和式 (2.2.11) 估计 CET。例如，假定  $EOT = 12\text{\AA}$ ， $V_G = 1.1\text{V}$  和  $V_{th} = 0.3\text{V}$ ，由式 (2.2.1) 得到 ac 电荷中心  $X_{ac} = 9.2\text{\AA}$ 。进一步假定  $N_{sub} = 3 \times 10^{17} \text{cm}^{-3}$  和  $N_{gate} = 1 \times 10^{20} \text{cm}^{-3}$ ，可以估算得到栅耗尽层宽度  $X_{gd} = 15.7\text{\AA}$ 。因此，量子效应和栅耗尽效应一起对 CET 的贡献为  $8.3\text{\AA}$ ，而栅介质的贡献为剩下的  $12\text{\AA}$ 。显然，对于很薄的 EOT，再缩小栅介质对于减小 CET 作用已经不大了，因为多晶硅栅耗尽和量子效应的作用在 CET 中占的百分比已经很高。因为量子效应的贡献不能被减小，因此通过工艺改进或者使用新颖的栅电极材料（如金属栅电极）来减小多晶栅耗尽效应就变得非常关键。国际半导体技术路线图 (ITRS) 预测，在未来几年，量子效应和栅耗尽效应会给 EOT 附加  $8\text{\AA}$ ，而在 2007 年， $65\text{nm}$  中将采用金属栅，它会给 EOT 附加  $5\text{\AA}$ <sup>[66]</sup>。

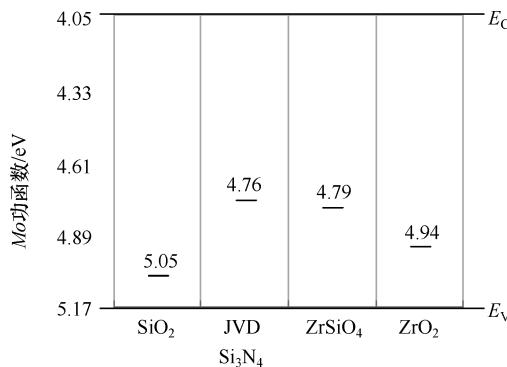

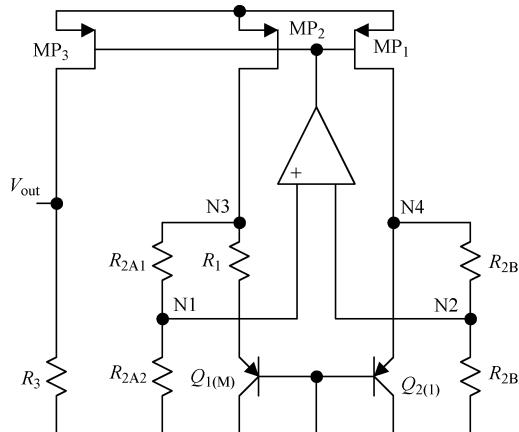

## 2.2.4 金属栅电极

多晶硅栅耗尽问题在几代工艺中都是制约器件性能改善的瓶颈。如前面讨论所指出的，多晶硅栅不能符合最新的 ITRS 要求，使用金属栅电极将是解决这一问题的方案。通常金属栅比金属硅化物多晶硅栅有更低的栅阻抗，这将有助于减小  $RC$  时延，这是采用金属栅的又一个好处。

使用金属栅电极对工艺和集成提出了许多挑战。从器件和设计的角度看，栅的功函数是主要的关注点。沟道掺杂适当时，使用  $n+/p+$  多晶硅电极可以很容易地获得合适的  $n-$  和  $p-$  MOSFET 阈值电压。对于体硅 CMOS，使用金属栅很难满足同样大小栅功函数的要求。一般地，功函数高（类似  $P+Si-$ ）的金属是非活性的，因此很难刻蚀掉，而那些功函数低的金属又活性太高，与栅介质接触时会带来热稳定性问题。在体硅 CMOS 中使用功函数大小适中的金属时，将导致  $n$ - 和  $p$ -MOSFET 的阈值电压大大高于希望值。但是，还是可以在两种类型的器件中使用同一种金属，然后分别调整两种类型器件上的金属功函数以优化这两类器件的阈值电压。当前，一种可接受的金属栅方案仍在研究中。除了获得合适的功函数，功函数分布的严格控制也是金属栅技术中非常重要的问题。

高  $k$  栅介质的使用影响着阈值电压的精确设定。许多高  $k$  介质具有高界面陷阱密度和固定电荷，这将引起显著的  $V_{th}$  漂移和较大的  $V_{th}$  变化。另外，当高  $k$  栅介质与金属栅一起使用时，将发生一项重要的物理效应。首先通过实验观测到，当使用不同栅介质时， $p$ -MOSFET 的钼栅会有不同的栅功函数值（见图 2-15）。这可以用这些介质的界面偶极子具有不同的屏蔽效应来解释<sup>[68]</sup>。多晶硅栅很少受这种效应的影响，因为在禁带宽度中的能带密度可以忽略。理论模型预测，在高  $k$  介质上实现与  $n+/p+$  硅类似的功函数，需要金属功函数有非常大的范围，这给候选的金属电极施加了一个更加严格的限制。

图 2-15 采用  $p$ -MOSFET 测得的在不同栅介质上的钼栅的功函数视在值

(功函数随钼栅下方的栅介质不同而不同，并与真空值不同) (来源于参考文献 [67])

对于沟道掺杂浓度非常低的器件，比如 FinFET 或超薄体 SOI MOSFET，合适的  $V_{th}$  要求栅功函数更靠近硅禁带中央。因此，候选金属的选择会稍稍容易。据仿真预测，对于 FinFET，偏离硅禁带中央  $\pm 0.2\text{eV}$  的栅功函数是适合于 p- 和 n-MOSFET 器件的<sup>[69]</sup>。为了实现使用金属栅得到相对较小的功函数范围，有几项技术可以被采用，例如，掺杂的镍硅化物栅、在钼中注入氮，以及金属混合及合金。然而，一个完整的方案还有待研究。

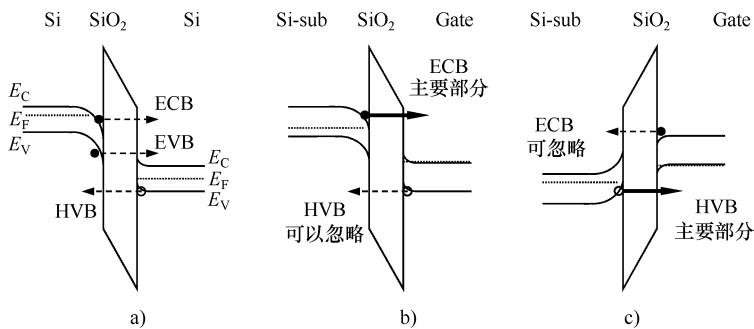

## 2.2.5 栅直接隧穿泄漏电流

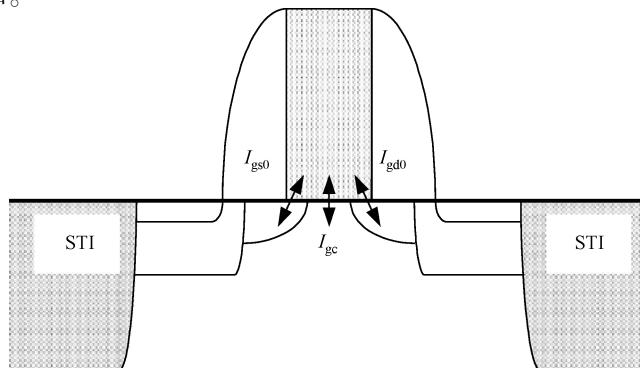

对超薄栅氧，即使在低栅压下，由于直接隧穿过程，会有相当的栅泄漏电流存在。随着器件的缩小，考虑功耗问题时，栅泄漏电流就变成了日益严重的问题。在 65nm 工艺中，EOT 接近 1nm，要求栅泄漏电流比 1nm  $\text{SiO}_2$  泄漏电流小几个数量级（随着应用对象的不同有所不同）。因此，作为  $\text{SiO}_2$  栅氧的替代物，高  $k$  栅介质的研究正紧锣密鼓地进行。

在低于 20Å 的情况下，常规的硅热氧化物不能再作为电子和空穴的有效势垒，因而引起了不可接受的高栅泄漏电流。不像 Fowler-Nordheim 隧穿机制那样，对于直接隧穿电流没有一个简单的解析方程。另外，沟道载流子的量子制约效应在计算沟道电流时不能被忽略。因此，隧穿电流的严格的物理模型包括自治求解薛定谔方程和泊松方程以及计算不同量子态下载流子的分布<sup>[70]</sup>。另一方面，一个相对简单的解析模型，对于电路仿真和栅泄漏的快速估算非常有用。Lee 等人提出了一个半经验的  $\text{SiO}_2$  直接隧穿模型<sup>[71]</sup>。一般情况下，需要采用下述三个直接隧穿分量组成总的栅泄漏电流模型：电子导带（ECB）隧穿、空穴价带（HVB）隧穿和电子价带（EVB）隧穿（见图 2-16）。随着偏置条件的不同，一些机制可以被忽略。例如，当氧化层电压  $|V_{ox}|$  小于硅带隙电压 1.12V 时，不会

图 2-16 a) 一般情况下，建立穿过薄栅氧的直接栅隧穿电流模型需要三个分量。

在低栅压下，b) 对 n-FET 主要贡献是 ECB 隧穿，

c) 对 p-FET 主要贡献是 HVB 隧穿（来源于参考文献 [71] 和 [72]）

发生 EVB 隧穿。在低  $V_g$  ( $< 1.5V$ ) 情况下, 对于 n-FET, 反型偏置栅泄漏主要分量由 ECB 贡献, 而对 p-FET 时, 则是 HVB。

对每种隧穿机制, 直接隧穿电流可以由下式表示:

$$J = \frac{q^3}{8\pi h\phi_b \epsilon_{ox}} C(V_g, V_{ox}, t_{ox}, \phi_b) \exp \left\{ -\frac{8\pi \sqrt{2m_{ox}\phi_b^3}}{3hq|E_{ox}|} \left[ 1 - \left( 1 - \frac{V_{ox}q}{\phi_b} \right)^{3/2} \right] \right\} \quad (2.2.12)$$

式中, 指数项代表在导带边界载流子隧穿概率的 WKB 近似, 而  $C$  基本上是为了在低栅压范围能正确描述的  $J_g - V_g$  变化关系的经验形状因子。

$$C(V_g, V_{ox}, t_{ox}, \phi_b) = \exp \left[ \frac{20}{\phi_b} \left( \frac{|V_{ox}| - \phi_b}{\phi_{b0}} + 1 \right)^\alpha \left( 1 - \frac{|V_{ox}|}{\phi_b} \right) \right] \frac{V_g}{t_{ox}} N \quad (2.2.13)$$

式 (2.2.13) 中的  $N$  与隧穿载流子密度相关。对反型区和积累区,  $N$  的一般表达形式为

$$N = \frac{\epsilon_{ox}}{t_{ox}} \left\{ S \ln \left[ 1 + \exp \left( \frac{V_{ge} - V_{th}}{S} \right) \right] + v_t \ln \left[ 1 + \exp \left( -\frac{V_g - V_{fb}}{v_t} \right) \right] \right\} \quad (2.2.14)$$

在式 (2.2.14) 中,  $S$  是亚阈值摆幅;  $v_t$  是热电压;  $V_{th}$  是 MOSFET 的阈值电压。

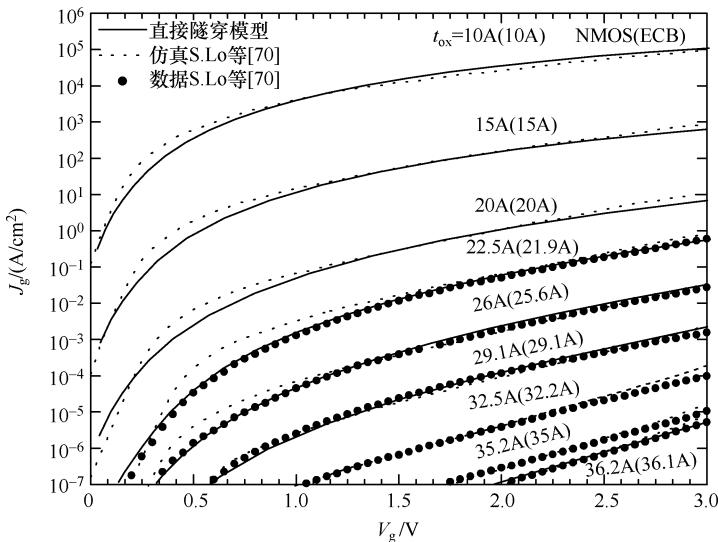

该模型中的拟合参数是有效质量  $m_{ox}$ 、势垒高度  $\phi_b$  和  $\phi_{b0}$  以及  $\alpha$ 。对不同的栅偏置和栅与衬底掺杂类型, 选用合适的参数都会使模型与隧穿电流符合。对于上述隧穿的每个分量, 模型参数是不同的。图 2-17 所示为该模型的精度。图中虚线是数值仿真的结果<sup>[70]</sup>、实线表示解析模型计算结果, 而实心点符号是实际器件的测量数据。可以看到三种结果之间符合得很好。除了  $\text{SiO}_2$ , 上述模型也在单层非  $\text{SiO}_2$  介质应用中得到证明<sup>[72]</sup>。业已表明, 对于采用喷射汽相淀积 (Jet

图 2-17 Lee 与 Hu<sup>[71]</sup> 的直接隧穿模型与实验数据以及仿真结果符合得很好

Vapor Deposited, JVD) 技术生长的氮化硅，直接隧穿泄漏也可以与使用单独一组拟合参数的这个模型符合得很好。表 2-1 总结了在使用  $\text{SiO}_2$  和 JVD 氮化硅栅介质的 n- 和 p-FET 中主要隧穿机制的参数。势垒高度可以通过其他方式获得，因此，实际上仅仅有效质量和  $\alpha$  需要通过实验栅泄漏数据确定。为了更适合于有效的数值实现，这个模型的概念经过适当修改，被包括到 BSIM4 栅泄漏模型中<sup>[73]</sup>。

表 2-1  $\text{SiO}_2$  和 JVD 氮化硅栅介质的直接隧穿模型参数

|                 | $\text{SiO}_2$ |      | JVD 氮化硅 |      |

|-----------------|----------------|------|---------|------|

|                 | ECB            | HVB  | ECB     | HVB  |

| $\phi_b$        | 3.10           | 4.50 | 2.10    | 1.90 |

| $\phi_{b0}$     | 3.10           | 4.50 | 2.10    | 1.90 |

| $m_{\text{ox}}$ | 0.40           | 0.32 | 0.50    | 0.41 |

| $\alpha$        | 0.6            | 0.4  | 0.4     | 1.0  |

应该注意到，使用一些高  $k$  栅介质时，在高  $k$  栅介质和硅衬底之间存在一个薄界面层，这既可以是为了获得更好的薄膜质量而有意引入的，也可能是在高  $k$  层和衬底之间由不希望的化学反应生成的。因此栅绝缘层实际上包括了两个或者更多层不同的介质。由于上述模型是基于单层的概念，并不能被应用到多层介质结构。最近的一项工作将 BSIM4 中的单层隧穿模型拓展到了多层情况下<sup>[74]</sup>。结果表明，通过对多层中的每一层构建合适的用 BSIM 模型里隧穿参数表示的隧穿概率，BSIM 直接隧穿模型也与多层栅介质的实验数据符合得很好。目前，对于明确知道层结构的多层隧穿的实验栅泄漏数据非常有限。随着高  $k$  栅介质工艺技术的进一步改进，模型也需要进一步提炼。

## 2.2.6 寄生电容

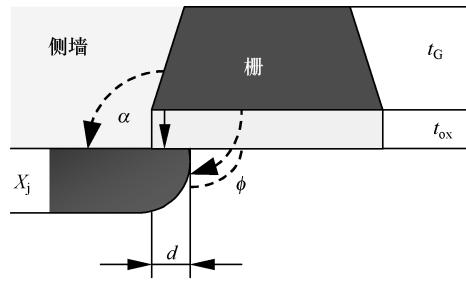

栅与源/漏之间的电容是影响 CMOS 器件和电路性能的重要因素。栅和源-漏之间的耦合，一部分由于直接交叠产生，其不能随着普通工艺技术的缩小而成比例的缩小。因此，对于更短栅长的器件，寄生电容变得更加严重。隔离层介质材料影响着边缘电容。另外，用高  $k$  栅介质取代  $\text{SiO}_2$  栅氧化层也影响着寄生分量。虽然非常准确地计算电容要求二维数值计算，但是一个简单的物理模型可以被用来理解这些机制<sup>[75]</sup>。如图 2-18 中三个箭头所示，栅到漏（或源）电容包含了三个耦合途径：两个边缘分量和栅到漏的直接交叠。侧墙区两侧的边缘电容为

$$C_1 = \frac{\varepsilon_{\text{SPCR}} W}{\alpha} \ln \left( 1 + \frac{t_G}{t_{\text{ox}}} \right) \quad (2.2.15)$$

式中， $W$  是器件的宽度； $t_G$  和  $t_{\text{ox}}$  分别是栅介质和栅的物理厚度； $\alpha$  是如图 2-18 中所示的角度； $\varepsilon_{\text{SPCR}}$  是隔离层介质的介电常数。

直接交叠电容等于

$$C_2 = \frac{\epsilon_{\text{ox}} W (d + \Delta)}{t_{\text{ox}}} \quad (2.2.16)$$

式中,  $d$  是交叠长度; 当  $\alpha$  是  $\pi/2$  时,  $\Delta$  是零。结侧面的耦合电容等于

$$C_3 = \frac{\epsilon_{\text{ox}} W}{\beta} \ln \left( 1 + \frac{x_j \sin \beta}{t_{\text{ox}}} \right) \quad (2.2.17)$$

式中,  $\beta = \pi \epsilon_{\text{ox}} / 2 \epsilon_{\text{Si}}$ 。注意, 当栅下存在自由载流子时, 耦合途径将被屏蔽, 因此在强反型时, 这部分不存在。在上面几个表达式中, 所有的介电常数值的单位是  $\text{F} \cdot \text{cm}$ 。

$C_1$  与器件宽度和侧墙介质的介电常数有着线性关系, 而与栅和栅氧之间厚度之比的关系较弱。假定  $\alpha = \pi/2$ ,  $\epsilon_{\text{SPCR}} = 3.9 \epsilon_0 (\text{SiO}_2)$ ,  $t_{\text{ox}} = 12 \text{\AA}$ ,  $X_g = 1000 \text{\AA}$ , 可以得到  $C_1 = 0.097 \text{fF}/\mu\text{m}$ 。更厚的物理栅介质可以稍稍减小  $C_1$ 。如果使用高  $k$  介质, 使得  $t_{\text{ox}} = 48 \text{\AA}$  (EOT 仍然是  $12 \text{\AA}$ ), 而其他一切都与上面例子中的一样,  $C_1$  只减小到  $0.068 \text{fF}/\mu\text{m}$ 。 $C_1$  减小的关键是确保侧墙介质有较低的介电常数。如果用氮化物侧墙取代  $\text{SiO}_2$ , 由于  $\epsilon_{\text{SiN}} \approx 2 \epsilon_{\text{SiO}_2}$ , 边缘电容将增加到大约为原来的 2 倍。如果在栅介质刻蚀期间, 高  $k$  介质不能从侧墙区的底部完全清除,  $C_1$  也会显著增加。

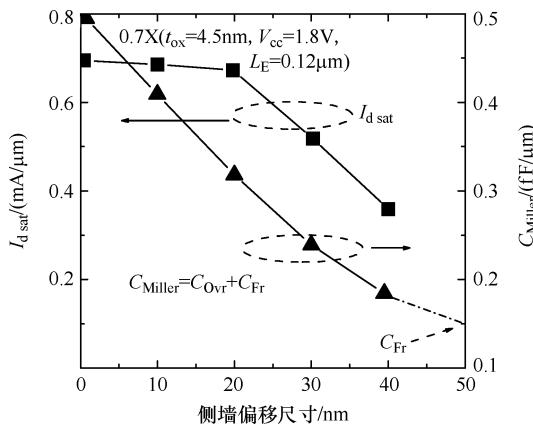

直接交叠电容  $C_2$  随着栅沟道电容  $C_{\text{ox}}$  缩小而线性缩小, 其主要变量是交叠长度  $d$ 。希望  $d$  尽量小, 因为这样可以减小交叠电容。然而, 结果显示, 为了避免短沟 MOSFET 中驱动电流的衰退,  $d$  必须为  $15 \sim 20 \text{nm}$ <sup>[76]</sup>。如果源漏扩展 (SDE) 深度或 SDE 到栅的交叠太小, 会增加沟道的串联阻抗, 引起漏电流衰退。图 2-19 显示了减小 Miller 电容 ( $C_M = C_1 + C_2$ ) 和改善驱动电流  $I_{\text{d sat}}$  之间的折衷。为了避免驱动电流衰退, 要求交叠不能小于一个最小值意味着随着器件的缩小, 交叠电容相对于栅电容  $C_{\text{ox}}$  将变得更大。假定栅介质 EOT =  $12 \text{\AA}$ , 最小交叠为  $15 \text{nm}$ , 会有  $0.43 \text{fF}/\mu\text{m}$ , 而对于  $60 \text{nm}$  的沟道长度, 栅沟道电容是  $1.73 \text{fF}/\mu\text{m}$ 。

寄生电容的另一个来源是源漏结电容。p-n 结存在耗尽区。当结偏置电压改变时, 耗尽宽度随之变化, 从而对电容负载产生影响。在 MOSFET 中, 这些结的一侧一般都是重掺杂, 因此耗尽宽度主要由轻掺杂一侧决定:

$$C_j = \frac{\epsilon_{\text{Si}} \epsilon_0}{X_D} \approx \sqrt{\frac{\epsilon_{\text{Si}} \epsilon_0 N_{\text{sub}}}{2 (\phi_{\text{bi}} + V_R)}} \quad (2.2.18)$$

式中,  $X_D$  是耗尽层宽度;  $N_{\text{sub}}$  是衬底掺杂浓度;  $V_R$  是结上的反偏电压;  $\phi_{\text{bi}}$  是 p-n 结内建电势。式 (2.2.18) 给出的是单位面积结电容。为了使总电容最小, 保持结区下衬底掺杂浓度尽可能低就显得非常重要。另外, 电路版图中结面积也应该尽量小。

图 2-18 MOSFET 的栅与漏之间耦合路径简图 (三个耦合路径均用箭号标出, 器件宽度方向与纸面垂直) (来源于参考文献 [75])

图 2-19 对给定的工艺，侧墙偏移尺寸对 Miller 电容

(交叠电容加边缘电容) 与饱和漏电流的影响<sup>[76]</sup>

(实验表明, 用来控制 SDE 注入与栅边界之间距离的侧墙偏移尺寸为 0 ~ 40nm, 使得 SDE 到栅的交叠可以在 40 ~ 0nm 范围调节。当交叠长度低于 15 ~ 20nm 的最小值时, 漏电流就会发生退化)

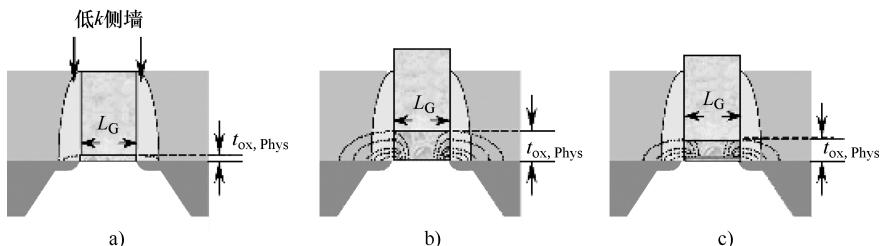

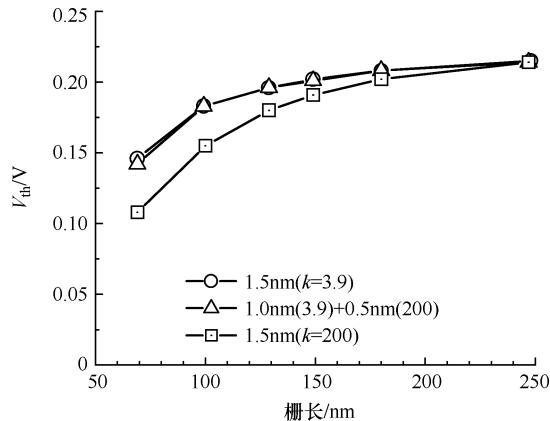

高  $k$  栅介质会增加一个附加的耦合通道, 而这在  $\text{SiO}_2$  中不重要。如图 2-20b 所示, 当栅介质的介电常数很高时, 为了得到给定的 EOT, 它的物理厚度会远大于相应的  $\text{SiO}_2$  的厚度。漏和源的边缘电场通过厚栅介质的侧面影响着沟道。附加的耦合使短沟器件特性衰退。通过仿真对比了图 2-20 所示 3 种情况下  $V_{\text{th}}$  的漂移特性。对于相同的 EOT, 图 2-20 中栅介质分别设定为: 图 2-20a 是  $\text{SiO}_2$ ; 图 2-20b 是高  $k$  介质; 而图 2-20c 是在一个分界层上有高  $k$  介质<sup>[77]</sup>。假定器件的参数相同, 1.5nm 的 EOT 可以采用 1.5nm 的  $\text{SiO}_2$ , 也可以采用  $k=200$  的介质, 或者是在 1.0nm 的  $\text{SiO}_2$  上采用  $k=200$  且  $\text{EOT}=0.5\text{nm}$  的介质来实现。图 2-21 所示为阈值电压与栅长的函数关系。由图可见, 当使用  $k$  值非常高的单层介质时,

图 2-20 3 种情况下  $V_{\text{th}}$  的漂移特性

(对于给定的 EOT 值, 单层高  $k$  介质 (图 b) 的物理厚度比  $\text{SiO}_2$  (图 a) 更大, 一个更现实的栅介质结构是在一个薄的低  $k$  (如  $\text{SiO}_2$ ) 界面层上加一层高  $k$  介质 (图 c)。对超薄  $\text{SiO}_2$  来说, 源-漏与沟道之间的边缘电场是可以忽略的, 而使用高  $k$  介质的情况, 边缘电场增强)

$V_{th}$ 的漂移特性衰退很严重。而采用低  $k$  值的薄分界层可以有效避免这种不希望的作用。仿真结果也表明，即使 EOT 不同，如果物理  $t_{ox}$  与栅长之比相同，也会产生相同量的短沟性能退化。应该注意到，当前最有希望的高  $k$  介质也比仿真中假定的  $k$  值要低得多。因此，除非栅长变得小于  $40 \sim 50\text{nm}$  使  $t_{ox}/L_c$  将变得足够大，否则这个效应不是很重要。总之，从短沟道效应的角度考虑，即使非常高的  $k$  值很有用，但是也是不希望的。

从器件的角度看，使用高  $k$  介质的唯一好处就是减少直接隧穿栅电流。目前，高  $k$  介质存在大量的器件和工艺问题，例如迁移率衰退、平带电压漂移等。不管可制造的高  $k$  方案的可用性，功耗问题必须通过多个领域的前沿技术来解决，包括从器件和工艺到电路和系统设计。

## 2.2.7 需要关注的可靠性问题

器件的可靠性是 CMOS 工艺需要考虑的关键问题。更小的器件尺寸和新材料的使用，如铜/低  $k$  介质、高  $k$  栅介质和金属栅电极，都对 CMOS 器件可靠性有着重要的影响。集成规模不断增大对电路中的每个单元提出了更加严格的安全性要求。测试低失效率复杂电路的开销和时间也是一个严重的挑战。下面简要分析与前道工艺相关的 CMOS 可靠性问题。

**经时介质击穿** 在过去的几十年， $\text{SiO}_2$  经时介质击穿 (TDDB) 的机制一直是一个非常活跃的研究领域，但是尚未得到一个毫无疑义的结论。随着工作电压和栅氧厚度的缩小，新的失效模式如软击穿也变得重要了。最近几年，一个重要的主题就是建立一个通过高压和高温加速寿命实验预测低压工作寿命的正确流程。一个相关的问题是：对于  $\text{SiO}_2$  栅介质缩小的可靠性限制是什么？一些研究者相信随着微观和宏观栅氧均匀性的改善， $\text{SiO}_2$  栅介质可以缩小到  $20\text{\AA}$  以下，这与最近的制造实践结果一致。Weir 等人的一项研究结果证实， $1.2\text{V}、70^\circ\text{C}$  时  $16\text{\AA}$  的氧化层是可能的<sup>[78]</sup>。基于目前的认识和 ITRS 提出的栅泄漏要求， $\text{SiO}_2$  的

图 2-21 阈值电压与栅长的函数关系

(图 2-20 所示的 EOT 均为  $1.5\text{nm}$  的三个栅层叠结构的  $V_{th}$  偏移特性。对于高  $k$  值单层栅介质，由于栅介质侧面增强了漏 - 源与沟道之间的耦合， $V_{th}$  发生了明显的衰退。采用薄的低  $k$  界面层可以有效地防止退化)

缩小可能被直接隧穿泄漏限制，而不是 TDDB 可靠性。

关于高  $k$  介质的 TDDB 可靠性的研究远少于关于  $\text{SiO}_2$  的研究。一般地，许多高  $k$  介质都有更小的禁带宽度与更高的界面和体陷阱密度，这对它们的 TDDB 可靠性有不好的影响。现在已经有一些基于氟的栅介质的研究，这种介质被认为是最有前途的栅介质候选者。一些技术，如衬底和高  $k$  介质的氮化，表现出可以改善  $\text{HfO}_2$  栅介质的击穿电压<sup>[79]</sup>。然而，高  $k$  介质其他不希望的效应，如迁移率衰退，是影响它被采用的主要因素。

**热载流子效应** MOSFET 在正常工作时，高的横向电场会在漏附近产生热载流子，这将损伤栅介质并引起器件特性的衰退，如  $g_m$  衰退和  $V_{\text{th}}$  漂移。随着沟道长度的减小，对于给定的电源电压，沟道中峰值电场将增加。电源电压的降低将减轻这个问题。调整掺杂分布也可以改善热载流子可靠性。在现代 CMOS 技术下，电源电压可以减小到接近于 1V，因此热载流子的能量将小于热发射和碰撞电离所需的最小能量。然而，在电源电压减小到这些关键能量水平以下时，并没有观察到载流子衰退的突然变化<sup>[80]</sup>。另外一些热载流子衰退机制被提出以解释这些实验观察结果。虽然在实际应用中，热载流子不是工艺缩小的阻碍，但是热载流子可靠性将仍然是需要给以适当关注的议题。

**负偏压温度不稳定性** 负偏压温度不稳定性 (NBTI) 是 p-MOSFET 中阈值电压漂移的重要原因。在 NBTI 应力下，源、漏和衬底接地，而栅被偏置到一个负的应力电压。在高温时，这样一个偏置将增加栅氧中正电荷的产生和界面态的产生。因此，导致  $g_m$  衰退和  $V_{\text{th}}$  漂移。在一些模拟和混合信号应用中，需要阈值电压极度稳定。NBTI 是这类电路寿命的限制因素。Reddy 等人的研究报告报道了 NBTI 对现代数字电路的影响<sup>[81]</sup>，结果表明，静态 CMOS 工作时主要的衰退模式是 p-MOSFET NBTI。当工作频率下降时，受 NBTI 应力作用，环形振荡器的相对频率衰退增加。另外还发现，NBTI 应力导致了 SRAM 静态噪声裕量退化。可以预计，随着工艺的缩小，NBTI 对电路的影响日益重要。

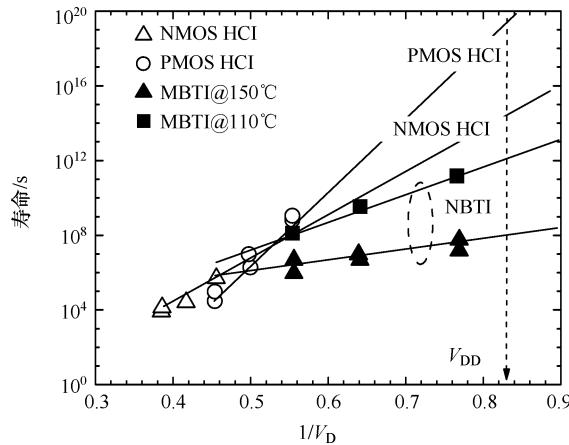

最近一项研究显示，按照  $V_{\text{th}}$  的漂移量达到一定值来定义寿命时，采用超薄氮化栅氧的 p-MOSFET 的寿命将主要由 NBTI 限制。在现代 CMOS 技术中，广泛使用氮化栅氧技术抑制硼穿通。然而，观察表明，氮化将减小 p-MOSFET 的 NBTI 寿命。在 Jeon 等人的研究中<sup>[82]</sup>，使用氮化栅氧厚度为 13Å 的 0.13μm CMOS 工艺制造 MOSFET。图 2-22 所示为在 NBTI 应力、HCl 应力下的 p-MOS 和在 HCl 应力下的 n-MOS 的寿命。由图可见，对 p-MOS，NBTI 应力下的寿命比 HCl 应力下的寿命低几个数量级，因此 NBTI 成为电路寿命的限制因素。将应力温度从 110°C 升到 150°C，NBTI 寿命将更短。对于一些待选的高  $k$  介质，仅有非常有限的数据可以使用，并且对于电路级的广泛研究也很缺乏。可以看到，对当前和未来的 CMOS 技术，NBTI 可靠性对于器件技术和电路设计都是非常重要的议题。

图 2-22 热载流子应力寿命和 0.13 μm CMOS 技术中 PMOS NBTI 应力寿命

(在正常的  $V_{dd}$  值下, n-MOS 和 p-MOS 的 HCI 寿命远长于 NBTI 应力下 PMOS 的寿命)

(来源于参考文献 [82])

## 2.3 后道工序互连线技术

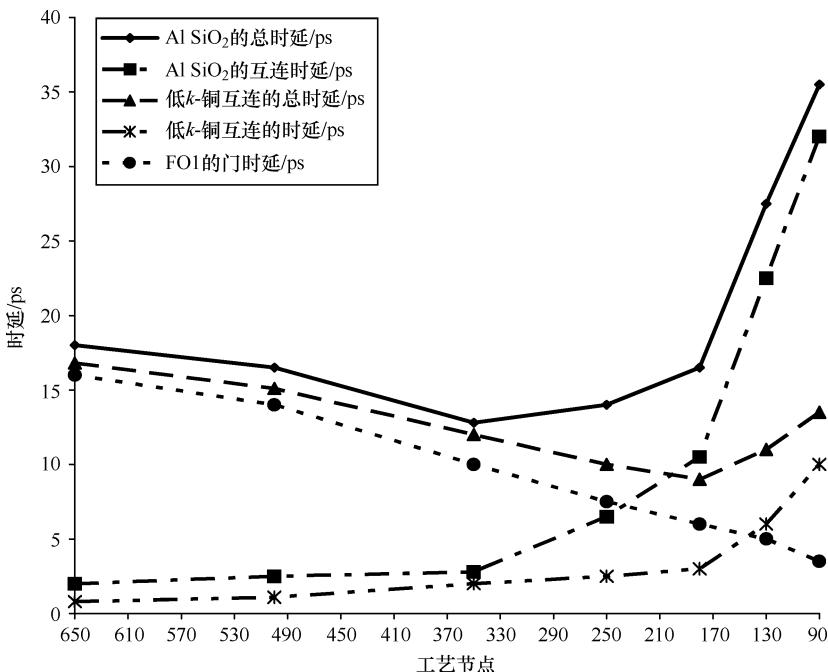

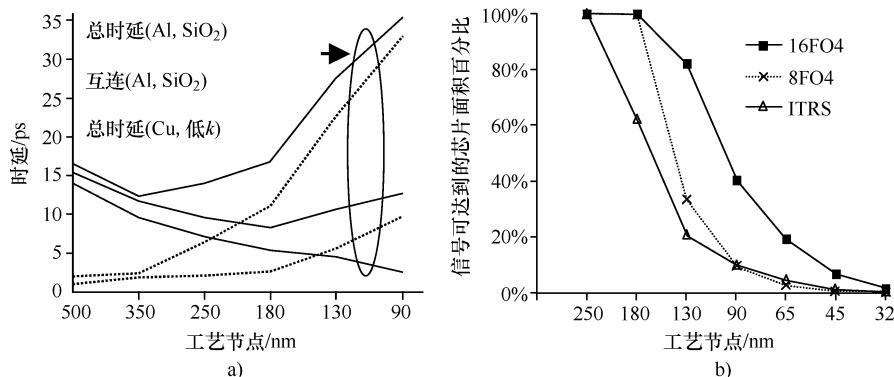

在 350nm 工艺之前, 互连技术的发展在不断改善集成电路密度、性能和每项功能成本方面起着关键的作用。受性能改善的驱使, 互连线缩小的连续进展导致了线条更厚、更窄、线间距减小、单位长度阻抗更低和电路工作频率更快。多层互连及低  $k$  介质提供了比先前铝互连线工艺更快的电路速度、减小的信号干扰和更好的可靠性等优势。然而, 后道工艺 (BEOL) 的关注仍然是电迁移、热特性、工艺控制、多层整合和在未来片上系统 (SoC) 中最重要的高速全局信号等几个关键问题。在纳米时代, 互连线时延已经是总时延的主要部分。如图2-23a

图 2-23 工艺缩小对芯片性能的影响：(总时延中占主要成分的互连线时延)

a) 铝与铜中的互连线和栅时延 b) 一个时钟周期信号可达到的面积百分比

所示，在130nm及更小时，即使是采用铜互连后道工艺，互连线时延会超过门时延。对90nm工艺，互连时延大约占总时延的75%<sup>[1]</sup>。而且，由于芯片功能的不断增加，单个芯片的面积随着工艺的减小而增大，因而如图2-23b<sup>[83]</sup>中所示，在一个周期内将信号送到芯片的各个部分变得越来越困难。为实现频率提升，全局性信号需要采用流水线传递，当信号通路跨越功能模块时，将导致较高的等待时间和功率消耗。由于这些缩放效应，所有电路性能优化的重点就要从门级逻辑设计变成以互连为中心的设计。

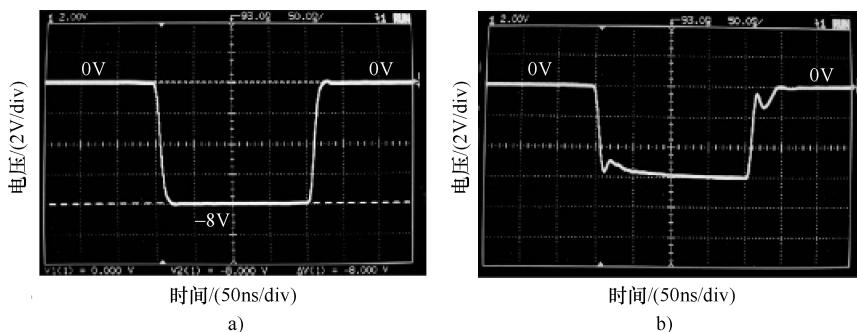

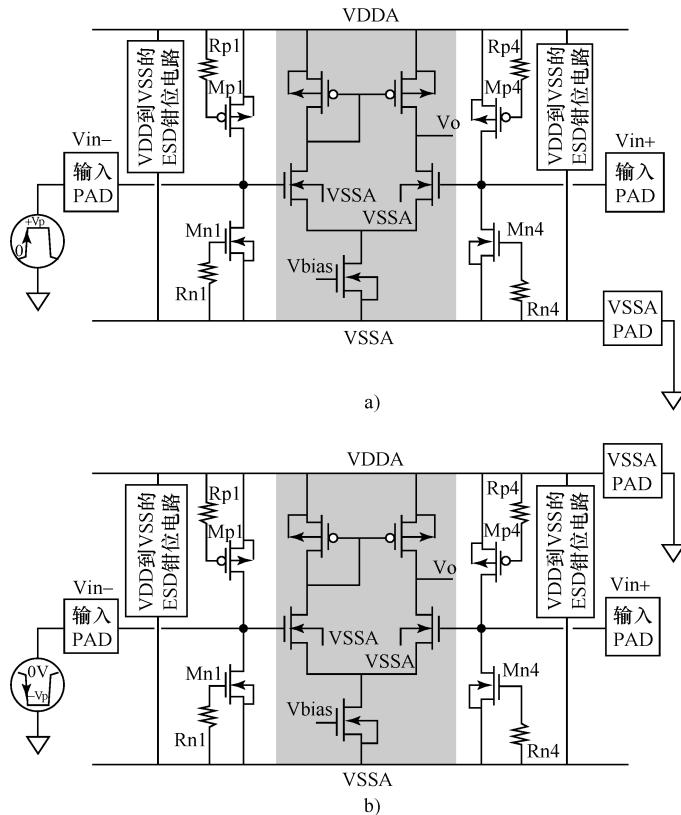

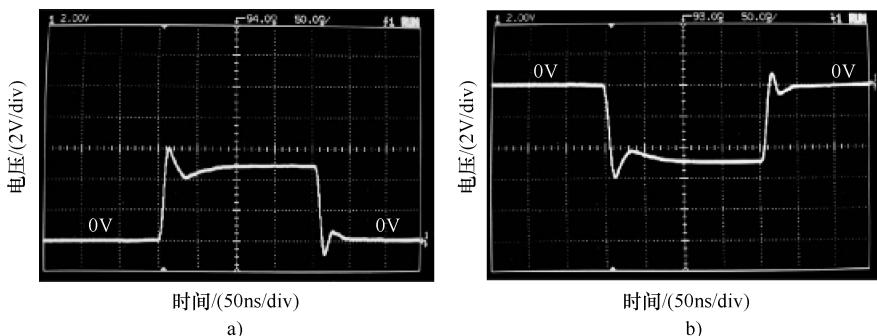

### 2.3.1 互连缩放

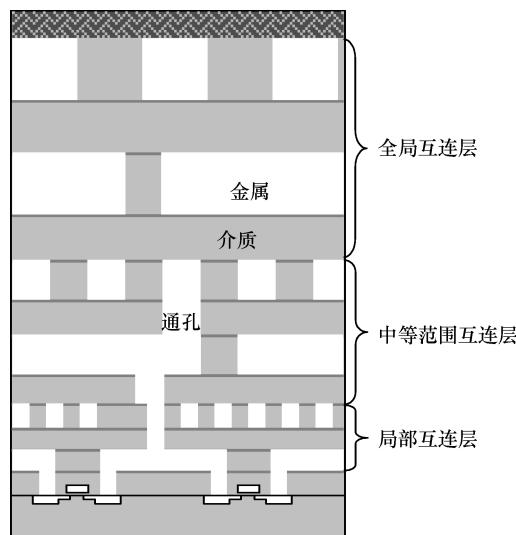

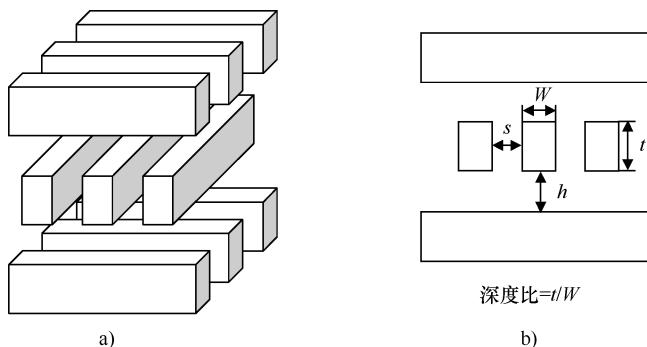

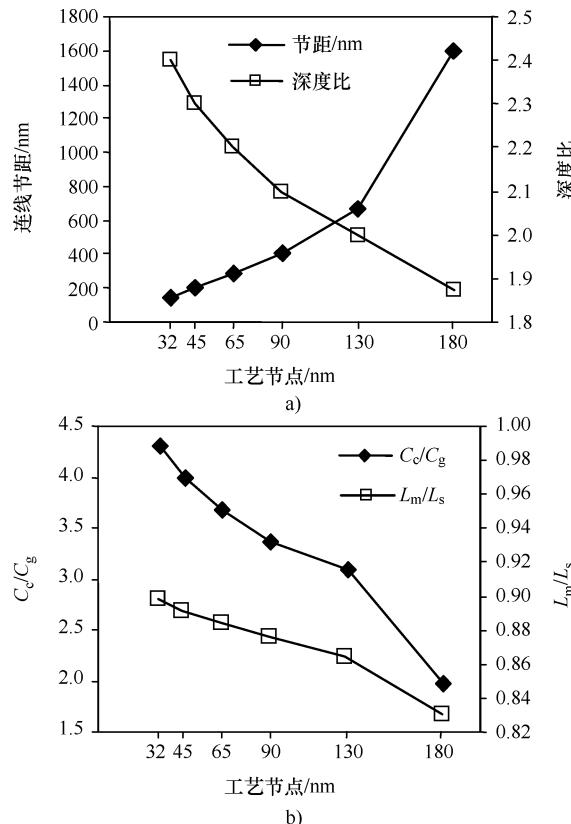

与FEOL缩放能提高电路性能相比，由于互连线横截面面积的快速减小，互连尺寸的缩小却会产生较长的时延。为了应对RC时延的增加，从几何结构和材料方面，已经采用了各种的改进。如图2-24所示，典型多层结构的特性包括：

- 大纵横比（纵横比定义为互连的厚度与宽度之比）。因为金属到地的电容( $C_g$ )约与线宽成比例，而金属阻抗( $R$ )与横截面面积(线宽与线厚度的乘积)有关。当互连节距减小时，较大的纵横比可以实现较小的RC时延。这个趋势在全局互连中极受欢迎，而在局部互连时，较低的纵横比也是可以接受的，因为局部互连的连线较短，信号的路径时延对RC时延的增加不敏感。与高纵横比相关的两个问题需要加以注意。首先，要用金属完全填充一个深而窄的槽是很困难的。因此，纵横比大于4的互连和通孔的形成变得不可靠，特别是对于双镶嵌结构工艺。第二，对于较大的纵横比，互连线厚度的增加会导致与相邻互连之间产生较大的耦合电容( $C_c$ )，这会增加RC时延成分并且增加信号耦合噪声。这两个不希望的影响限制了未来技术换代中的这种缩放。

- 分层互连。在多层金属化中，缩减局部互连节距并增加其他互连层次中的厚度和宽度，可以满足更高的电路密度、减小的RC时延和更小的阻性损耗要求<sup>[83]</sup>。在过去的10年，可用的金属互连层数增加了3倍<sup>[84]</sup>，目前工艺(约90~180nm)中有6~10层金属，图2-24为一个多层互连实例示意图。局部范围和中等范围互连一般用于连接功能块内部的门，而全局互连一般用于实现不同功能单元之间的互连。除了信号传输(如数据

图2-24 90nm时多层互连结构的典型截面图

总线），宽而厚的全局互连也用于时钟和电源线，或构成片上螺旋电感。同一层上的金属互连一般是平行分布，而与相邻层次上的互连线走向垂直。最近，对于全局性互连，对角线走向互连的引入比传统的直角互连结构的路径时延减小了 19.8%，并且线长减小 29.3%<sup>[85]</sup>。然而，在以前，这个技术对数据库的大小、光学邻近修正和掩膜写时间都提出了很大的挑战。这些问题的解决是未来技术成为可能的关键；电子设计自动化（EDA）公司和掩膜制造公司正在努力工作，以实现对角线走向互连。

● 局部和全局互连的不同缩小方式。为了与衬底上 MOSFET 的密度相匹配并维持  $RC$  时延，局部互连的节距与长度的缩小速度比垂直尺寸快得多。全局互连的缩小是由芯片边缘的长度决定的，其长度会随着栅尺寸的增大而增加。因此，全局互连的信号时延随着一代工艺到下一代工艺而增加，限制了整个芯片性能的提高（见图 2-23）。为了支持高性能处理器性能改善要求的频率提升，需要采用补偿技术，如增加转发器和流水线全局信号。

● 铜互连和低  $k$  介质。因为互连缩小是制约电路速度提高的主要瓶颈，业界做了很多的工作努力把新的 BEOL 材料整合到硅工艺中。两项主要的改进包括将金属材料铝改为铜、采用低  $k$  介质取代二氧化硅层。这些方式不仅有效地减小了单位长度互连的  $RC$  寄生参数，而且有助于改善 BEOL 的电迁移可靠性。另一方面，对互连最困难的挑战包括工艺集成、互连尺寸控制和电气可靠性。当工艺进入纳米时代，即使是低  $k$  铜，对于希望未来全局信号更快的要求来说也是不够的<sup>[85]</sup>。为了持续这种成功，新的 BEOL 技术包括材料和结构都是必需的。

### 2.3.2 铜互连技术

使用双镶嵌结构的铜互连制造是 1997 年由 IBM 引入的<sup>[86]</sup>。该技术的主要性能优点是铜的电阻率 ( $1.8 \mu\Omega \cdot \text{cm}$ ，或者工艺完成后有效值为  $2.2 \mu\Omega \cdot \text{cm}$ ) 大约比铝的电阻率 ( $3.3 \mu\Omega \cdot \text{cm}$ ) 低 40%。因此对于同样的横截面，铜互连的  $RC$  时延大约比铝互连低 30% ~ 40%。铜互连的其他优点还包括由于铜原子具有较大的质量而改善了电迁移可靠性，以及由于一些工艺步骤的简化而降低了成本：因为在铝工艺中使用的干法腐蚀对刻蚀铜互连图形无效，作为替代，开发出了一种基于化学机械抛光（CMP）的镶嵌工艺。总的来说，随着低  $k$  介质 ( $k < 3$ ) 的使用、从  $\text{Al}/\text{SiO}_2$  到铜/低  $k$  介质的转变使更高的互连密度、较少的金属层次、更快的信号传输和允许更大的电流密度成为可能，满足了当代超大规模集成电路系统高性能和高密度的要求。

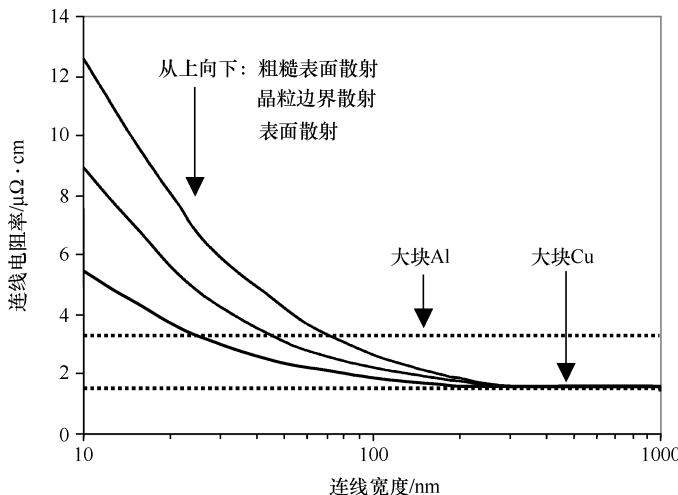

使用铜技术除了带来优点，对于成功的纳米规模集成，从材料和工艺的角度来说，还存在严重的挑战。从材料方面来看，有两个主要的问题：材料电阻率和电迁移。当金属互连的截面尺寸下降到 sub-100nm 范围，电子在铜中的输运面临几个基本的物理限制。图 2-25 对作为线宽函数的铜线电阻率做了理论性预

测<sup>[87]</sup>。在 100nm 时，线宽接近铜晶粒尺寸，形态不完整（如表面粗糙散射）和晶粒边界散射将使铜的电阻率增加 100%（注意温度每升高 10°C 电阻率将升高约 3.6%）。这些效应可以通过严格地控制铜的生长或生成单晶铜得到减缓。然而，在 100nm 工艺中，即使在单晶化后，由于铜被包在一个很窄的槽中，从而限制了晶粒尺寸和电阻率的改善。而且，在 45nm 工艺中，当线条尺寸接近铜中电子的平均自由程（39.3nm）时，金属表面散射将最终阻碍电子的传导。在这种环境下，铜电阻率的剧烈增加也必然导致 RC 信号时延和电源互连线上 IR 压降的极大增加。

图 2-25 单个物理效应导致铜电阻率的增加（铜和铝的体电阻率作为参考<sup>[88]</sup>）

对于片上金属互连，要考虑的其他重要的材料属性是抗电迁移的能力。当互连上流过很大的电流密度时，金属原子将在电流的作用下沿着互连运动，这样将会在下游形成高浓度的积累，而在互连上留下不希望的空洞。由于铜的原子质量（63）大于铝（27），铜线本质上对这些不希望的电迁移效应有着更好的鲁棒性。依赖于测试条件和不同的金属层次，关键的失效电流密度  $J_{\text{crit}}$ ，对于铜线来说是铝线的两倍<sup>[8]</sup>。实验数据显示，在同样的电流密度下，铜的电迁移寿命是铝的 100 倍<sup>[86]</sup>。除了较高的  $J_{\text{crit}}$  值，铜较高的熔化温度（1034°C，而铝是 660°C）也对静电放电（ESD）可靠性有益处。另一方面，随着 MOSFET 密度和电路性能的改进，片上互连必须在更窄的互连传递日益增加的开关电流，互连抗电迁移的能力对器件的鲁棒工作很重要，因此当前铜工艺仍需要改善，特别是控制金属界面、晶粒尺寸和杂质<sup>[89,90]</sup>。

通常使用镶嵌工艺实现的铜互连涉及多道后工序，包括互连图形的形成、槽金属填充和使用 CMP 实现金属平坦化。尽管先进的技术要求对前道和后道工艺 (FEOL 和 BEOL) 中较小的特征尺寸都进行精确的光刻，而对于铜互连，槽填充和 CMP 控制还有独特的要求。例如，在镶嵌工艺中，首先在绝缘层中刻出槽，

然后通过电镀均匀地填充金属导体。通孔的形成采用相似的工艺。一个很重要的问题是铜的沉积质量，应该避免引起夹断和产生空洞，这两个不希望的现象将导致电阻增大和可靠性退化。虽然 IBM 已经实现了  $0.2\mu\text{m}$  宽、 $4:1$  纵横比互连线的无空洞填充，但是线宽的快速缩小和纵横比的增加要求一个更鲁棒的电镀工艺<sup>[86,91]</sup>。

在铜沉积步骤之后，金属和介质的表面使用化学机械技术抛光。虽然 CMP 工艺有较高的铜去除率，由于金属和介质的材料属性的不同，这种抛光是金属侵蚀和凹陷的来源。图 2-26 所示为  $2\mu\text{m}$  铜线在 CMP 步骤后的横截面 SE 微观图；研究者已经提出了一个描述金属侵蚀和凹陷的物理模型<sup>[92,93]</sup>。因为铜比介质软，它对化学浆料更加敏感，因此它的抛光速率更快。所以金属厚度比预期的要薄（侵蚀效应）并且在抛光后它的表面呈半球形（凹陷效应）。由于侵蚀，较高金属密度的区域将会有更大的损失，但是这个效应可以通过采用哑元金属图形的填充得到有效减小，控制金属密度的均匀性。然而，接地金属的填充增加了总的寄生电容，而悬空金属填充增加线间的容性耦合<sup>[92]</sup>。凹陷效应与金属的宽度有关，对较宽的金属，凹陷更严重。为了减小凹陷效应，对于较宽的互连，可以采用开槽，或者开孔（乳酪状孔）的方式以提高其有效硬度。采用开槽和开孔技术时，通常这些孔沿着电流流向排列以使电流集边效应最小，这将可以获得更好的电阻率。这在较宽的时钟线和电源分布网络中特别受欢迎。另外一种减小金属凹陷效应的方法是将较宽的互连分割成几条较窄的互连。然而，对于相同的有效电阻或电迁移限制，这个技术将消耗更多的面积。此外，开槽和开孔步骤要求对数据库进行后处理，这就要求指导工艺的设计规则必须考虑导致的电迁移极限和互连电阻率的衰退。研究显示，对于全局互连来说，考虑总面积开销和信号时延，互连分割的最优范围是  $2 \sim 4$  倍（即分割后，线宽的最优值是  $3 \sim 5\mu\text{m}$ ）<sup>[93]</sup>。注意这些方式并不单单在工艺控制中使用，在设计时也应予以考虑，特别是对高频信号趋肤深度小于互连宽度的情况。

图 2-26 CMP 处理后，金属凹陷和腐蚀效应的 SEM 横截面图与模型

### 2.3.3 低 $k$ 介质的挑战

为了满足减小互连寄生电容的要求，在  $130\text{nm}$  工艺中，多层互连结构中采