普通高等教育“十三五”电子信息类规划教材

# 可编程逻辑器件 与 EDA 技术

PROGRAMMABLE LOGIC DEVICES AND EDA TECHNOLOGY

丁山○编

免费电子课件

普通高等教育“十三五”电子信息类规划教材

# 可编程逻辑器件与 EDA 技术

丁山 编

机械工业出版社

本书由浅入深系统地介绍了常用的可编程逻辑器件的基本工作原理，详细介绍了 VHDL 硬件描述语言、新一代 FPGA 设计套件 Vivado 的性能和使用方法以及 FPGA 的开发方法。全书内容新颖，举例充实。读者通过本书的学习可以初步掌握 EDA 的基本内容及实用技术。

本书共 14 章，主要内容包括绪论、CPLD 与 FPGA 的结构原理、VHDL 入门基础、VHDL 硬件描述语言、有限状态机设计、VHDL 优化设计、Vivado 集成设计环境导论、Vivado 工程模式下设计基础、创建和封装用户 IP 核、数字电子系统的设计实现、键控流水灯实验设计、抢答器实验设计、数字钟实验设计、UART 实验设计，内容丰富，叙述上浅显易懂，程序实例具有典型性。本书免费提供所有例题的源代码、电子课件，有很大的参考价值，欢迎选用本书作为教材的教师登录 [www.cmpedu.com](http://www.cmpedu.com) 下载或发邮件到 wangkang-maizi9@126.com 索取。

本书可作为高等院校电子信息类、计算机类等相关专业的教材，也可以作为电子技术工程技术人员的参考用书。

## 图书在版编目（CIP）数据

可编程逻辑器件与 EDA 技术/丁山编.—北京：机械工业出版社，2017.11

普通高等教育“十三五”电子信息类规划教材

ISBN 978-7-111-58375-2

I. ①可… II. ①丁… III. ①可编程逻辑器件—高等学校—教材 ②电子电路—电路设计—计算机辅助设计—高等学校—教材 IV. ①TP332.1 ②TN702

中国版本图书馆 CIP 数据核字（2017）第 263582 号

机械工业出版社（北京市百万庄大街 22 号 邮政编码 100037）

策划编辑：王康 责任编辑：王康 刘丽敏

责任校对：潘蕊 封面设计：张静

责任印制：常天培

涿州市京南印刷厂印刷

2018 年 1 月第 1 版第 1 次印刷

184mm×260mm · 18 印张 · 437 千字

0001—3000 元

标准书号：ISBN 978-7-111-58375-2

定价：45.00 元

凡购本书，如有缺页、倒页、脱页，由本社发行部调换

电话服务 网络服务

服务咨询热线：010-88379833 机工官网：[www.cmpbook.com](http://www.cmpbook.com)

读者购书热线：010-88379649 机工官博：[weibo.com/cmp1952](http://weibo.com/cmp1952)

教育服务网：[www.cmpedu.com](http://www.cmpedu.com)

封面无防伪标均为盗版 金书网：[www.golden-book.com](http://www.golden-book.com)

# 前　　言

随着半导体产业进入深纳米的时代，可编程逻辑器件向高密度、高速度、低价格方向迅速发展，EDA 技术在电子信息、通信、自动控制及计算机应用等领域的重要性日益突出。目前 EDA 技术已经成为电子信息类专业一门重要的专业基础课程，是电子信息类专业学生必须掌握的专业基础知识和基本技能。为了使学生掌握 EDA 基本设计工具和设计方法，在 EDA 开发软件上本书使用在 FPGA 市场占有率第一的 Xilinx 公司推出和发布的 Vivado 设计套件。该套件是一款基于业界标准的开放式开发环境，可以利用 Xilinx 公司推出的领先一代的硬件、软件和 I/O 全面可编程的 SoC-Zynq7000 系列实现数字系统、DSP 系统和嵌入式系统的设计。作者力图将 EDA 技术最新发展成果、现代电子设计最前沿理论和技术、国际上业界普遍接受和认可的 EDA 软硬件开发平台的使用方法奉献给广大读者。

本书力求全面、实用，对例题做到详细分析和解释，既可以帮助读者学习理解知识和概念，降低学习难度，又具有启发性，帮助读者更加轻松、迅速地理解和掌握本书内容。

本书在内容的组织上共分 14 章，各章的具体内容如下：

第 1 章为绪论，主要概述了 EDA 技术及其重要性，EDA 包含的知识体系结构，如 HDL、EDA 的工作软件等，比较了传统电子设计方法与 EDA 技术各自的特点。同时对 EDA 技术的发展历程、特点和优势，以及利用 EDA 进行工程设计的流程进行了简要介绍。

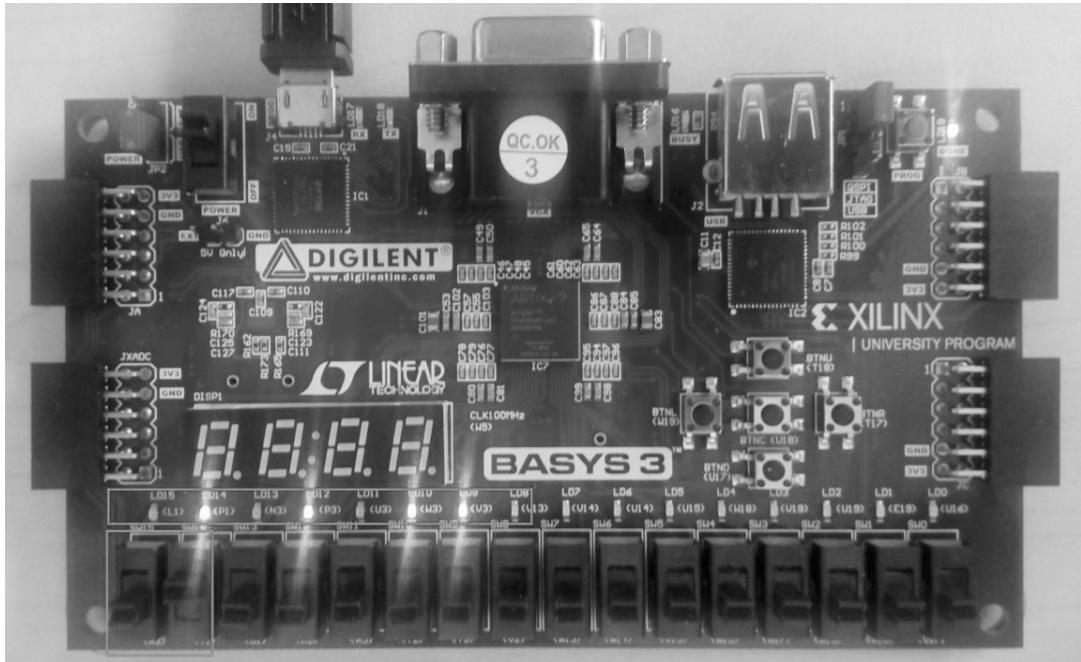

第 2 章主要介绍了可编程逻辑器件的基本结构和工作原理，以及相关的编程、测试和配置方法。首先对可编程逻辑器件进行了概述，主要介绍了可编程逻辑器件的发展历史，并对可编程逻辑器件通过不同的划分方式进行了分类；接着重点介绍了高密度可编程逻辑器件 CPLD 和 FPGA 的结构原理和工作特点；然后详细地阐述了 JTAG 边界扫描技术的硬件测试原理，并对 CPLD 的编程方法和配置方式进行了介绍；最后介绍了本书使用的 Basys3 开发板。

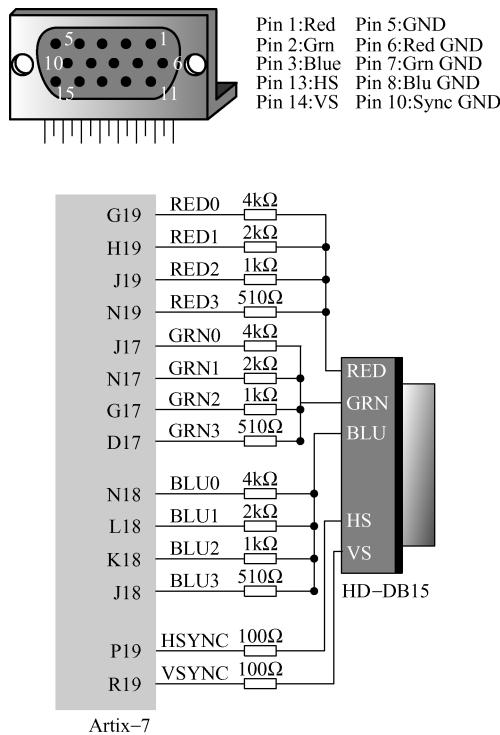

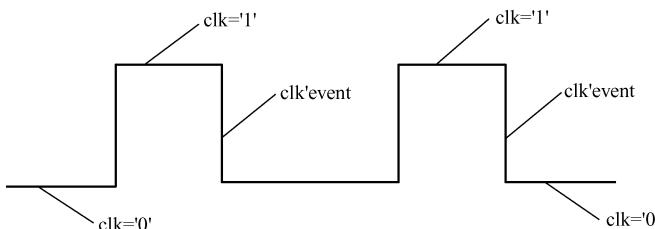

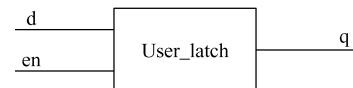

第 3 章主要讲述了 VHDL 语言的基本语法知识，是使用 VHDL 进行 EDA 设计的基础。首先介绍了 VHDL 程序的基本结构，一个完整的 VHDL 设计由库、程序包、实体、结构体和配置组成，其中实体和结构体是基本组成部分；然后介绍了 VHDL 语言中的文字规则、数据对象、数据类型和操作符等内容；最后介绍了 VHDL 中预定义的属性。

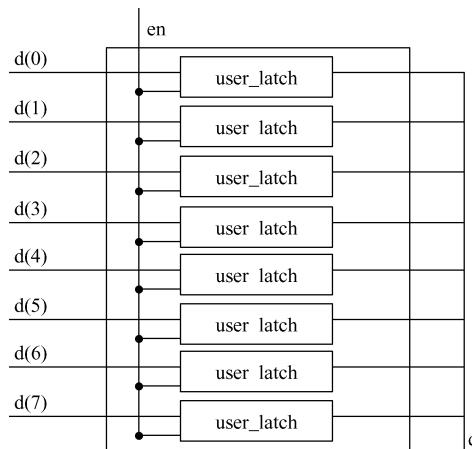

第 4 章主要讲述了 VHDL 语句的基本内容。VHDL 中的语句可以分为两大类：顺序语句和并行语句。在此基础上介绍了各种语句的语法以及使用方法、程序包的构成和配置、子程序的概念及其使用方法，并给出常用设计举例。

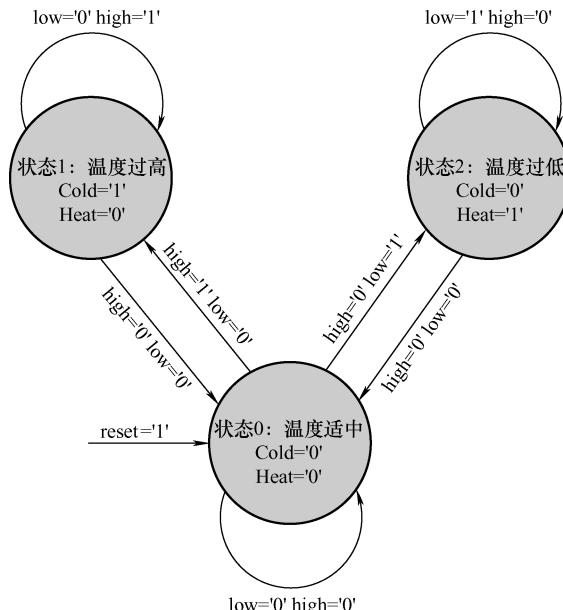

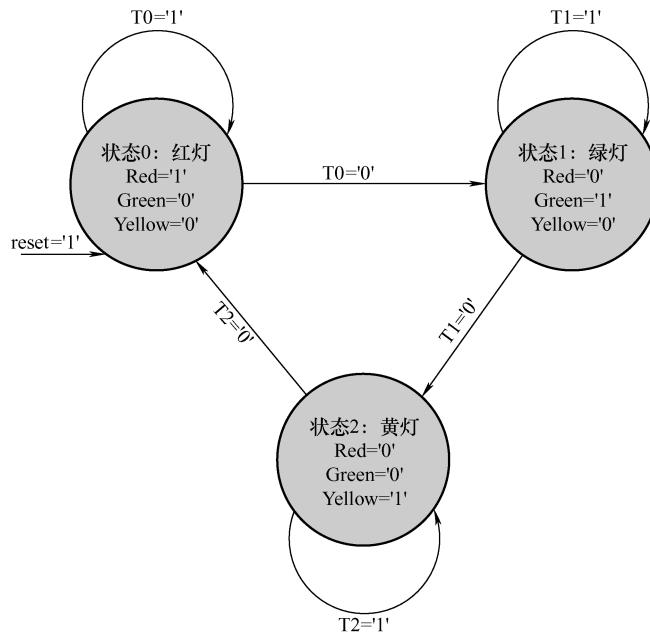

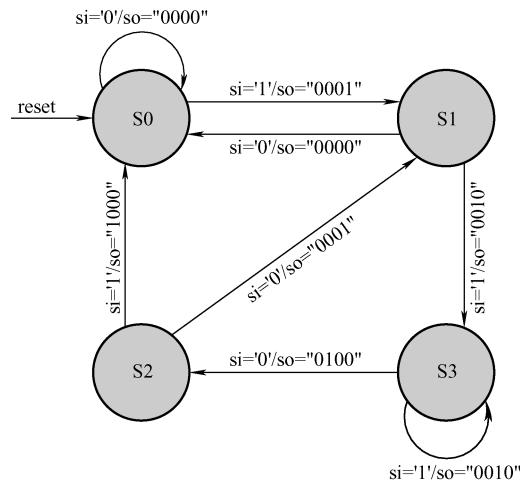

第 5 章主要讲述了有限状态机的基本概念、特点和基本结构等基础内容。在此基础上，对 Moore 型状态机和 Mealy 型状态机的结构、特性和设计方法进行了详细的举例说明；然后介绍了状态位置直接输出型编码、顺序编码、枚举类型编码及一位热码编码四种不同的状态编码方式，以及程序直接导引法及状态编码检测法两种安全状态机的设计方法；最后比较全面地对有限状态机进行了介绍。

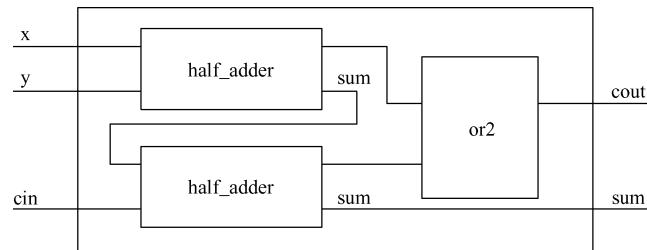

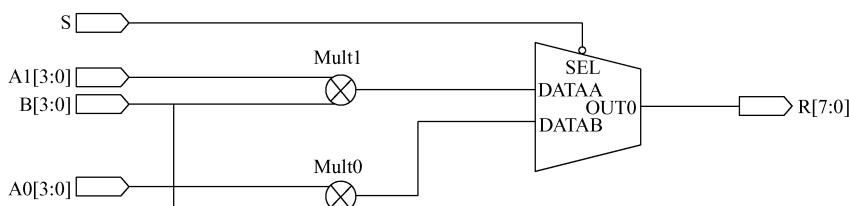

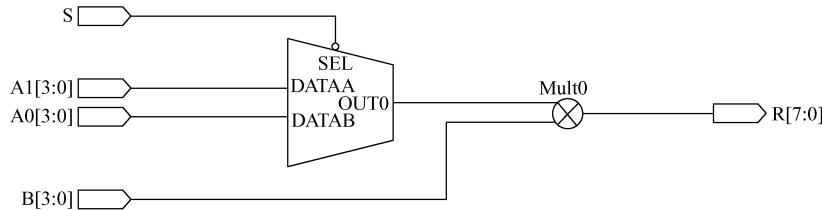

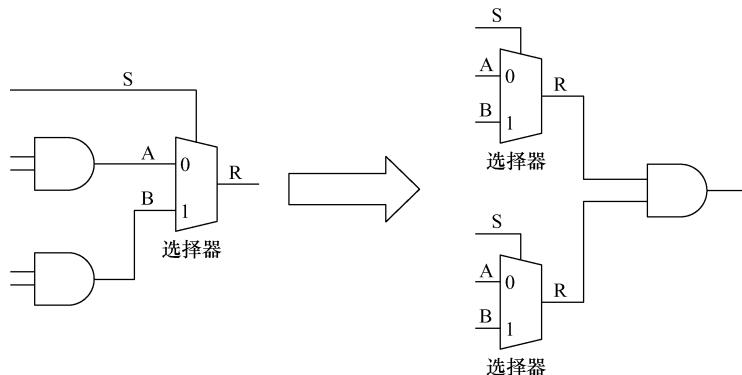

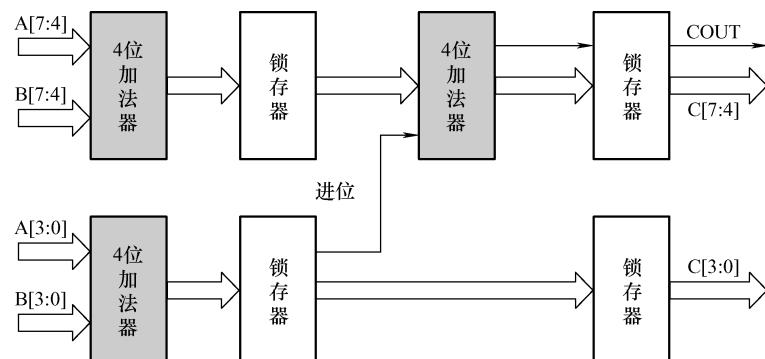

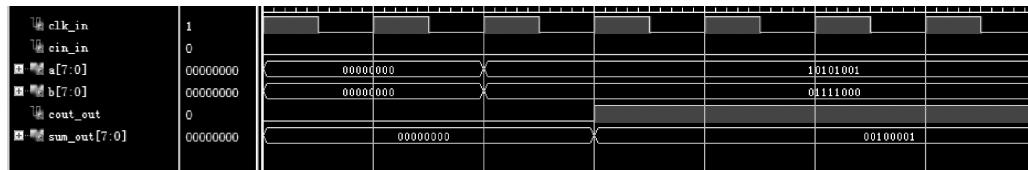

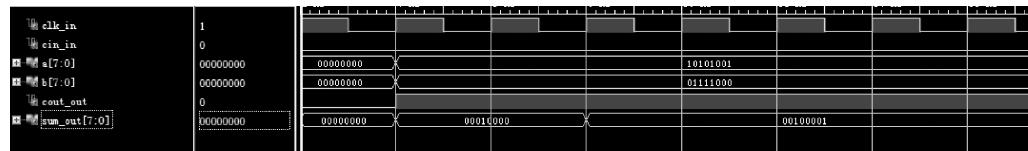

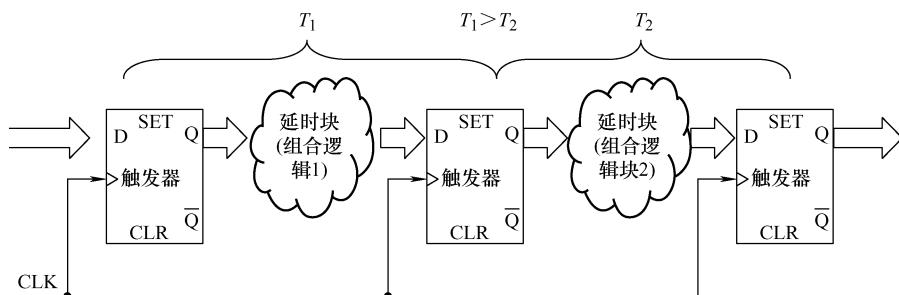

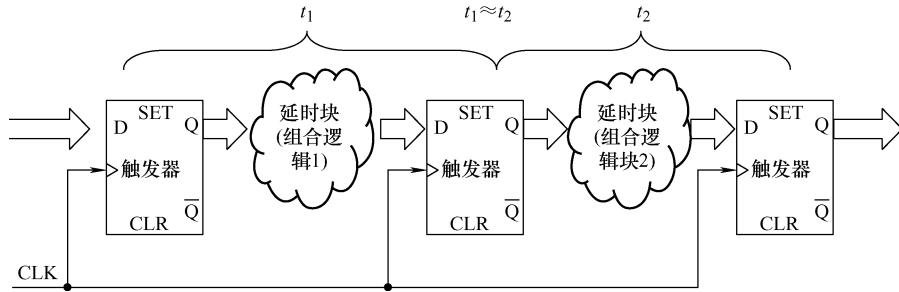

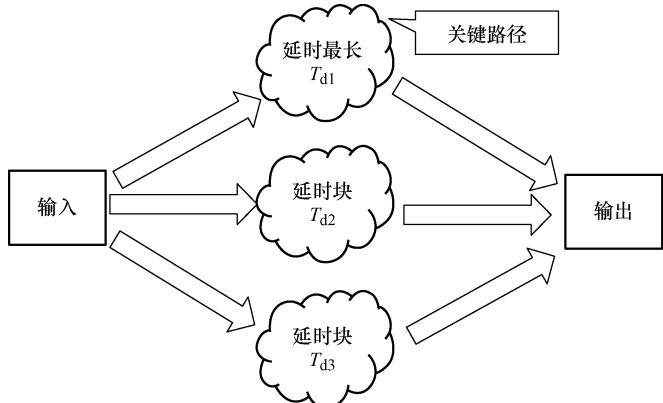

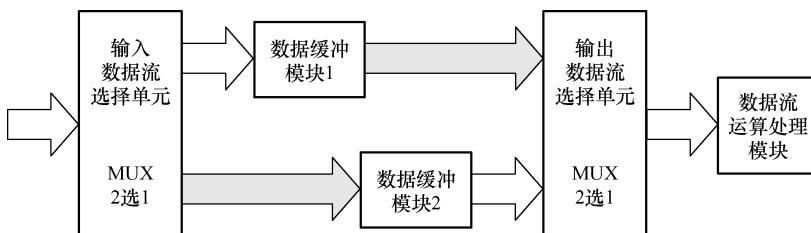

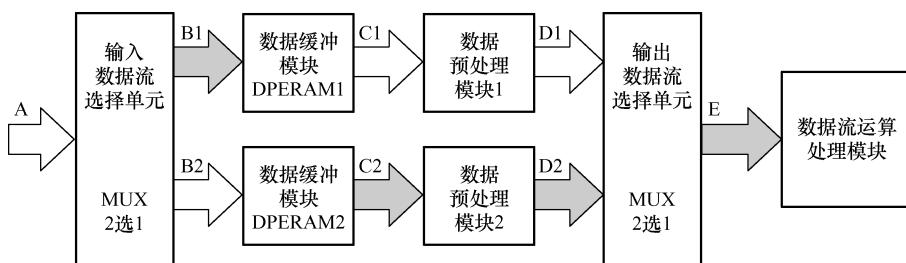

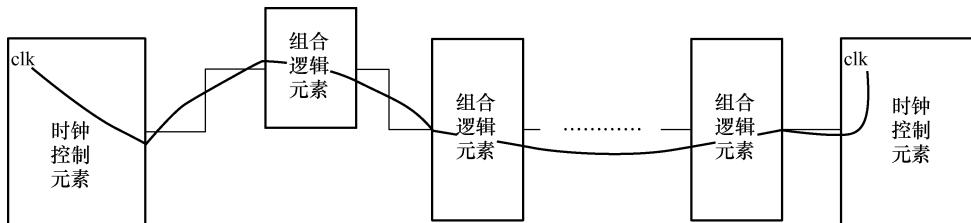

第 6 章介绍了 EDA 的硬件系统设计中 VHDL 的优化设计。首先介绍了 FPGA/CPLD 的

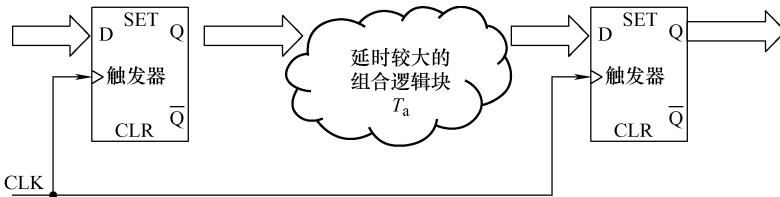

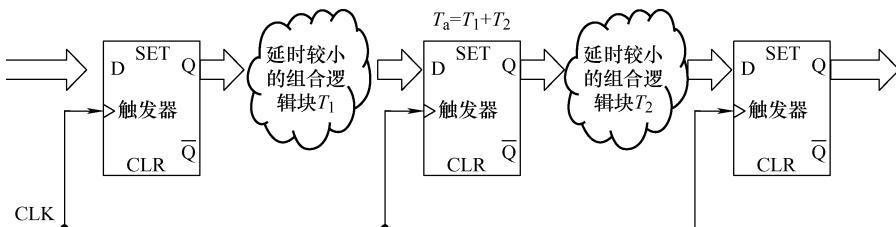

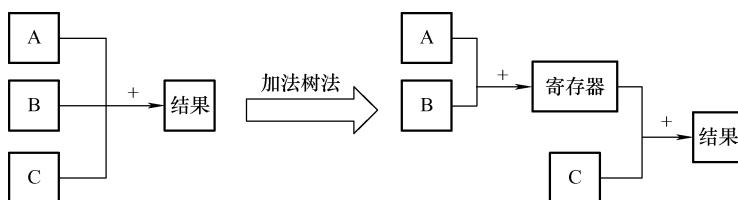

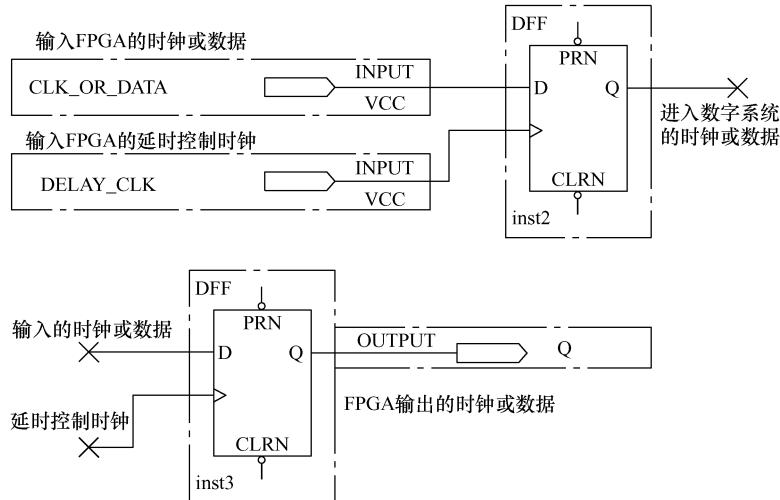

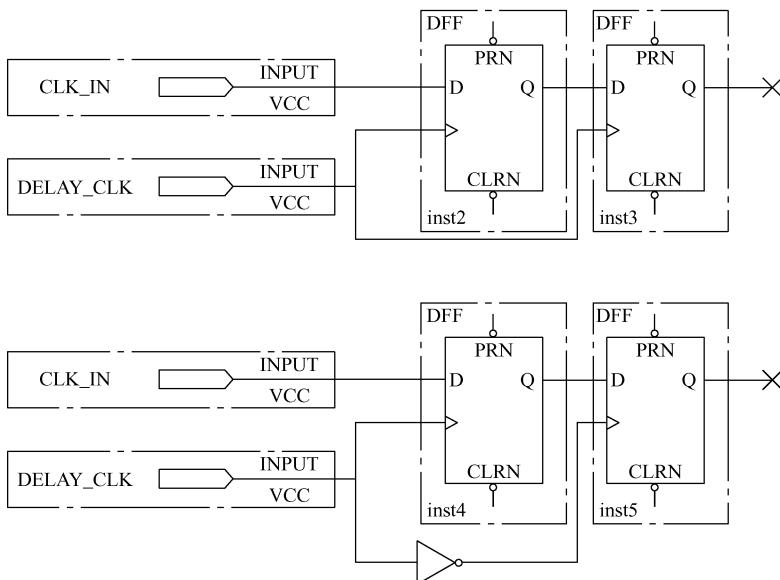

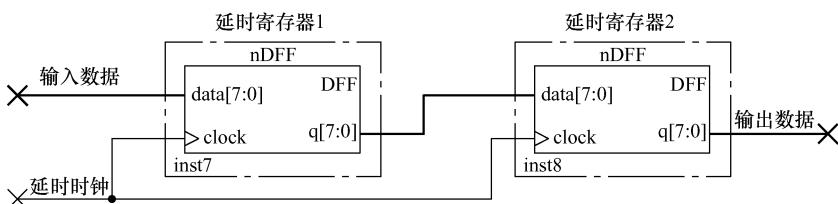

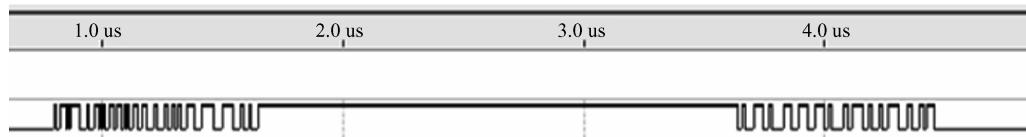

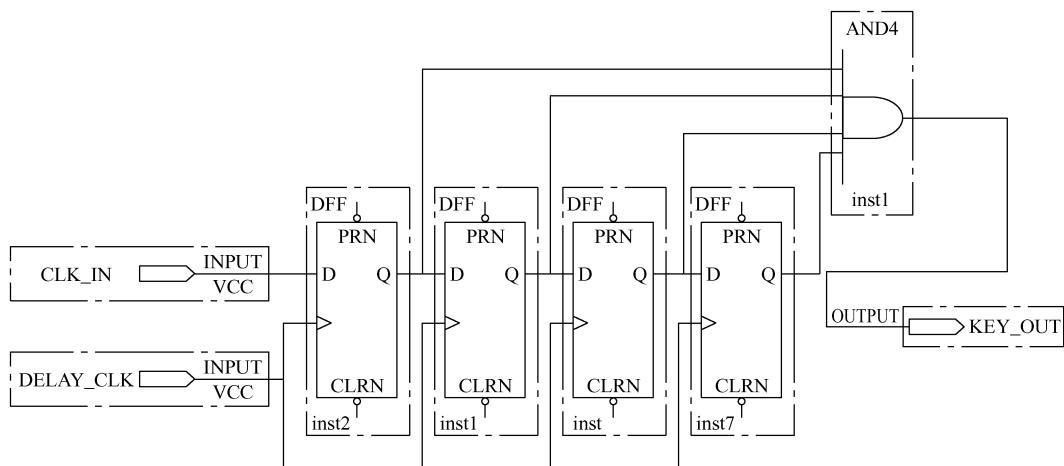

资源利用优化。资源优化主要包括资源共享、逻辑优化和串行化。由于对于大多数的设计来说，速度优化比资源优化更重要，所以介绍了速度优化，并依次阐述了流水线设计、寄存器配平、关键路径法、乒乓操作法和加法树法。最后详细介绍了如何排除和避免毛刺或随机干扰信号，主要包括延时方式去毛刺、逻辑方式去毛刺和定时方式去毛刺。

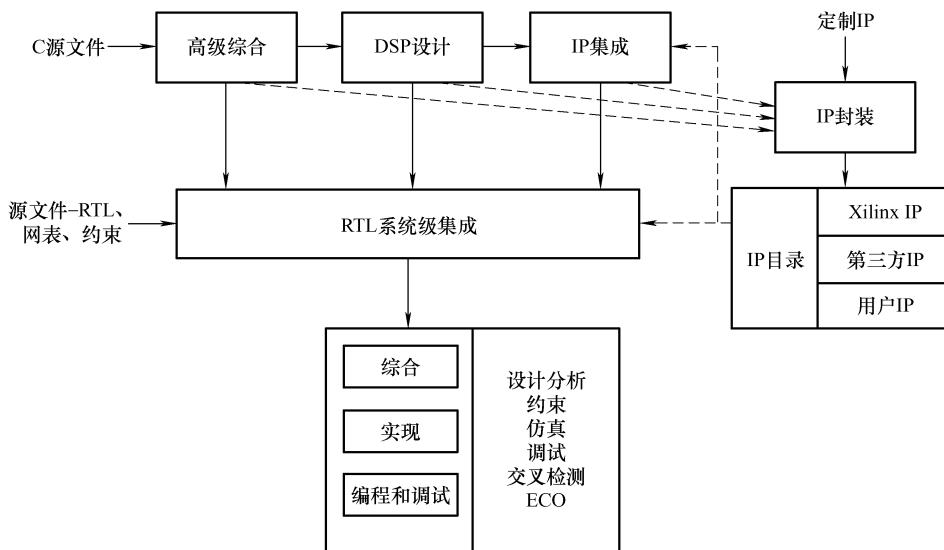

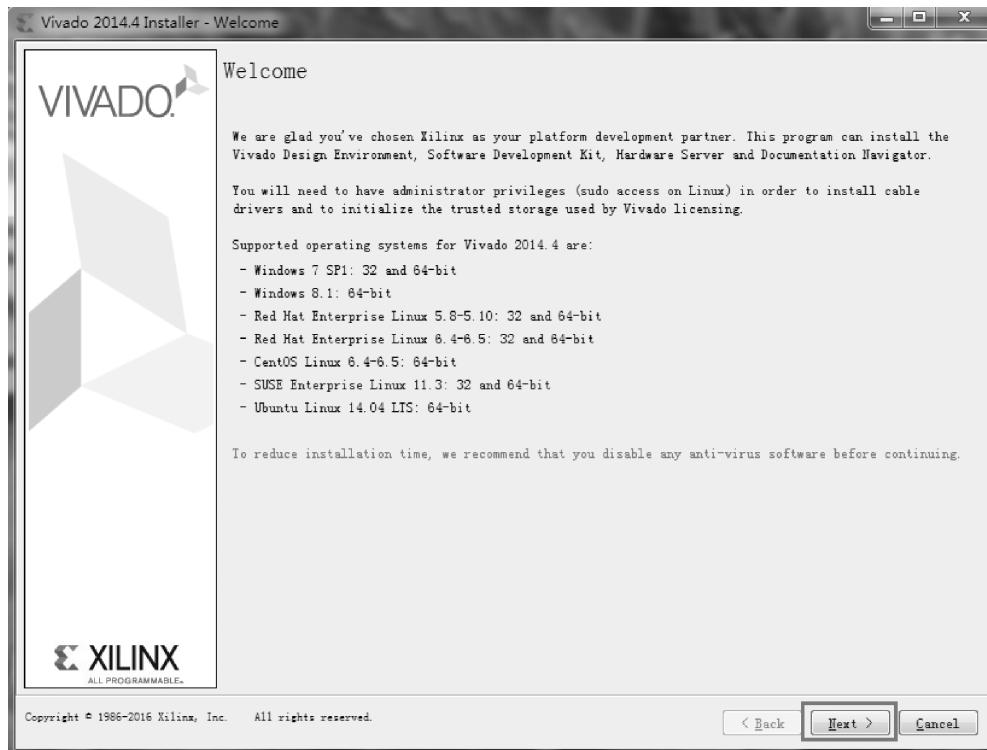

第 7 章介绍了 Vivado 设计套件的基本知识以及 Vivado 设计套件的界面信息。首先，简单介绍了 Vivado 设计套件的特性；其次介绍了使用 Vivado 设计套件的系统级设计流程；然后介绍了 Vivado 设计套件的安装过程；之后介绍了各个工程文件夹存放的文件类型以及网表文件的相关知识；最后介绍了 Vivado 设计套件的基本界面信息。

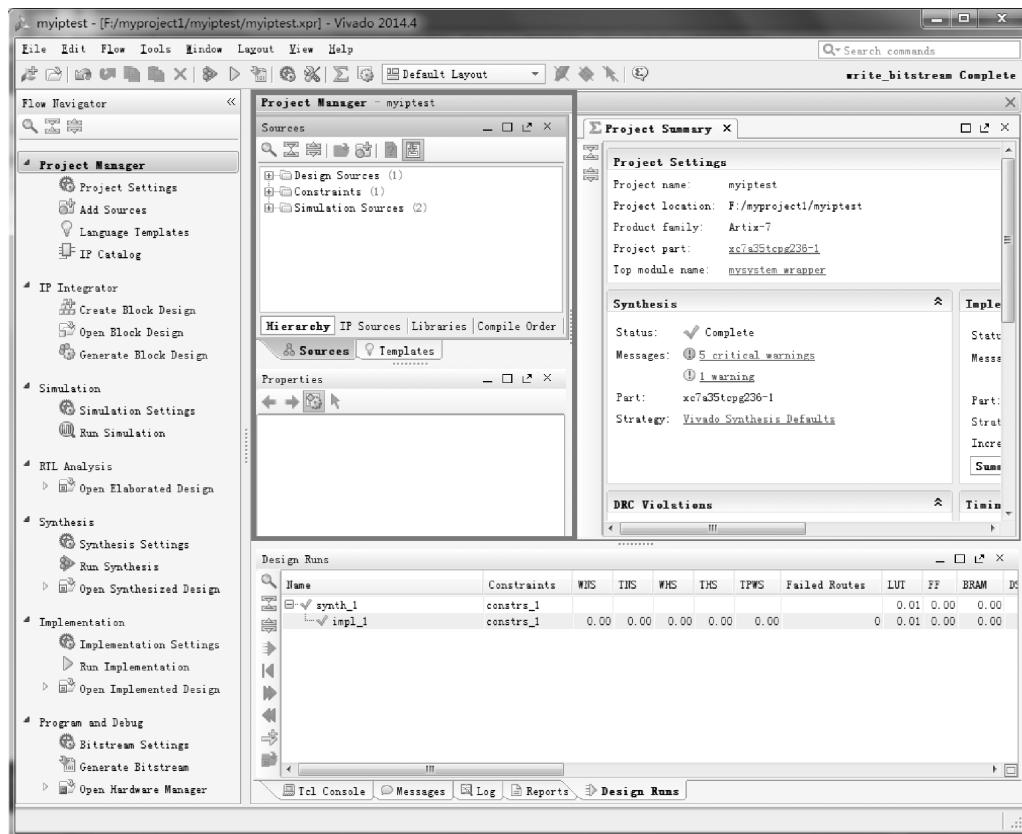

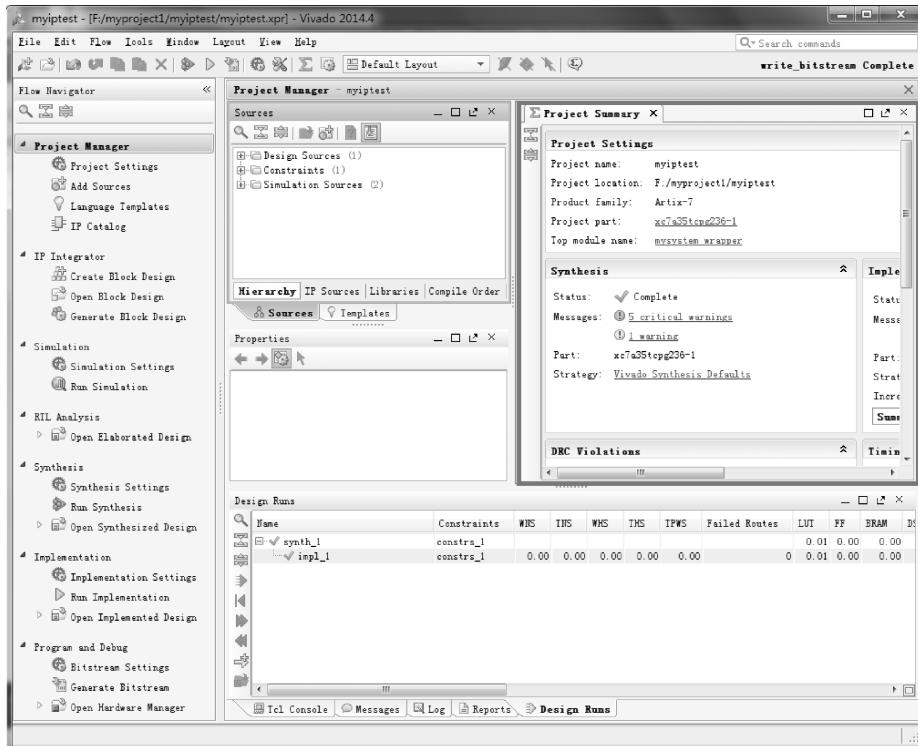

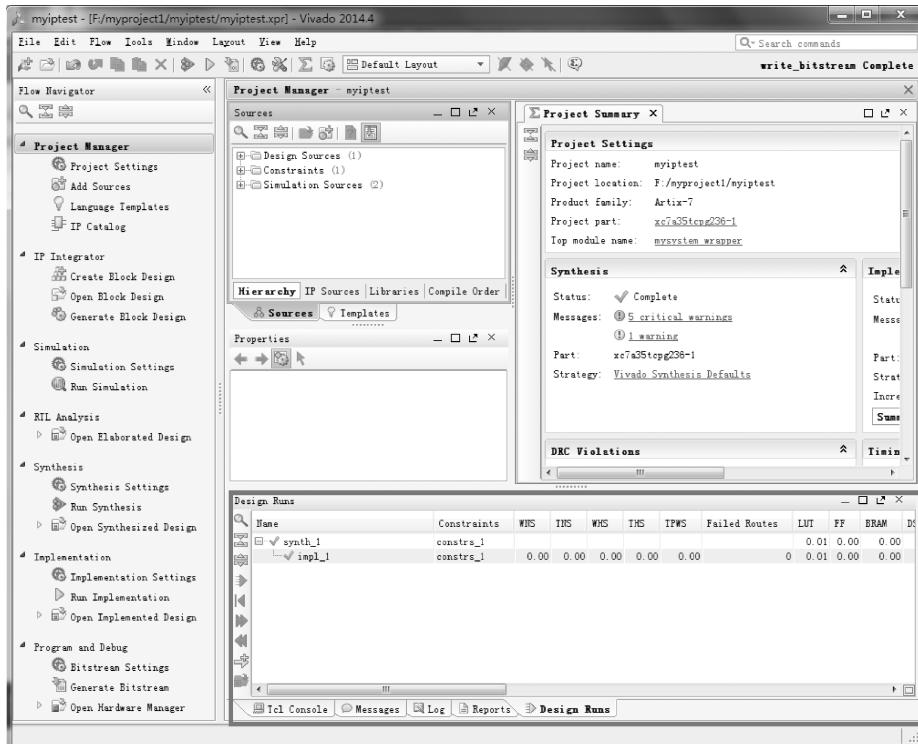

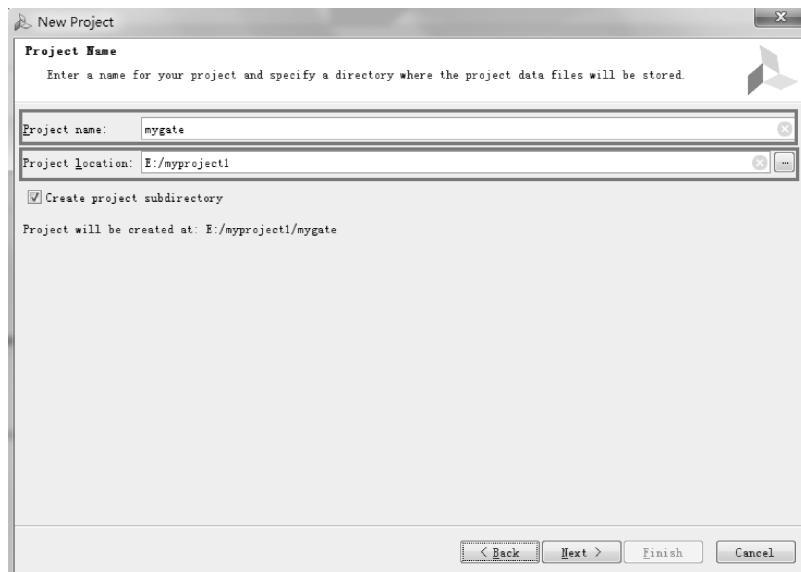

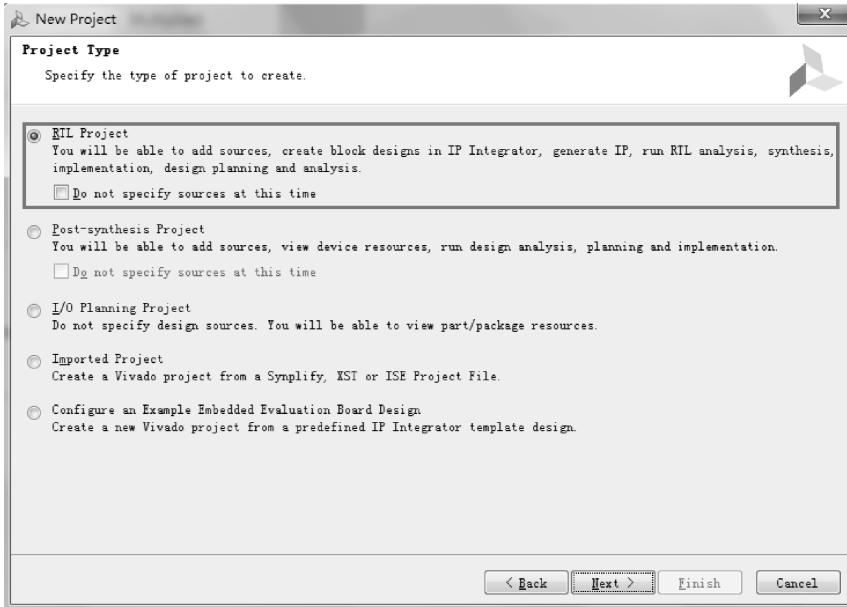

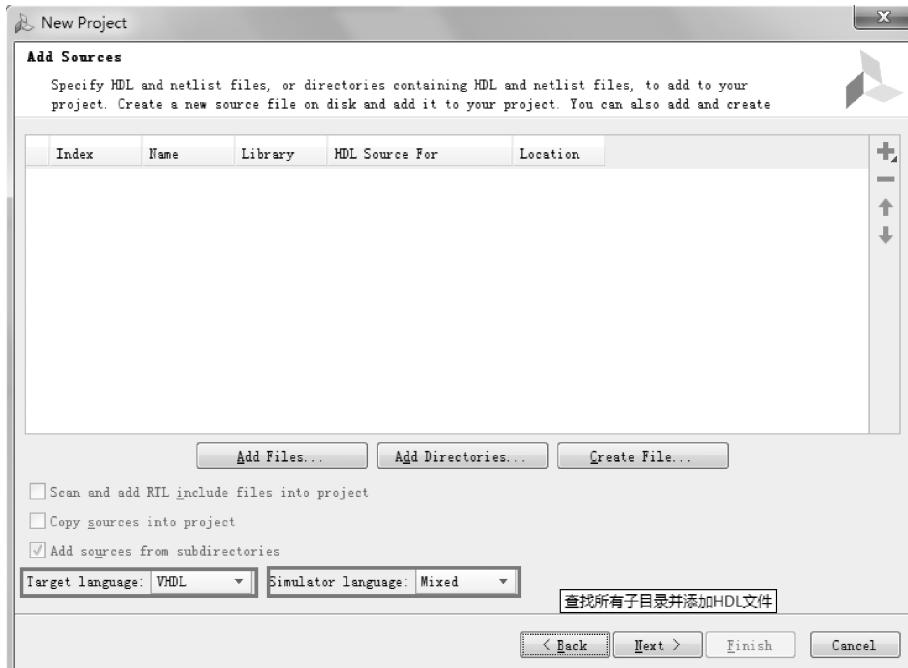

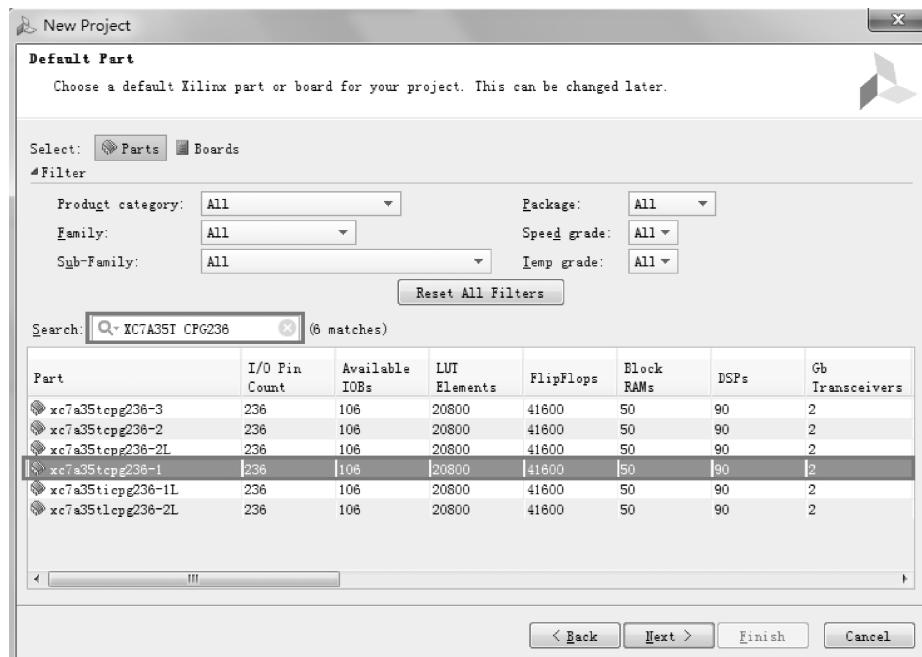

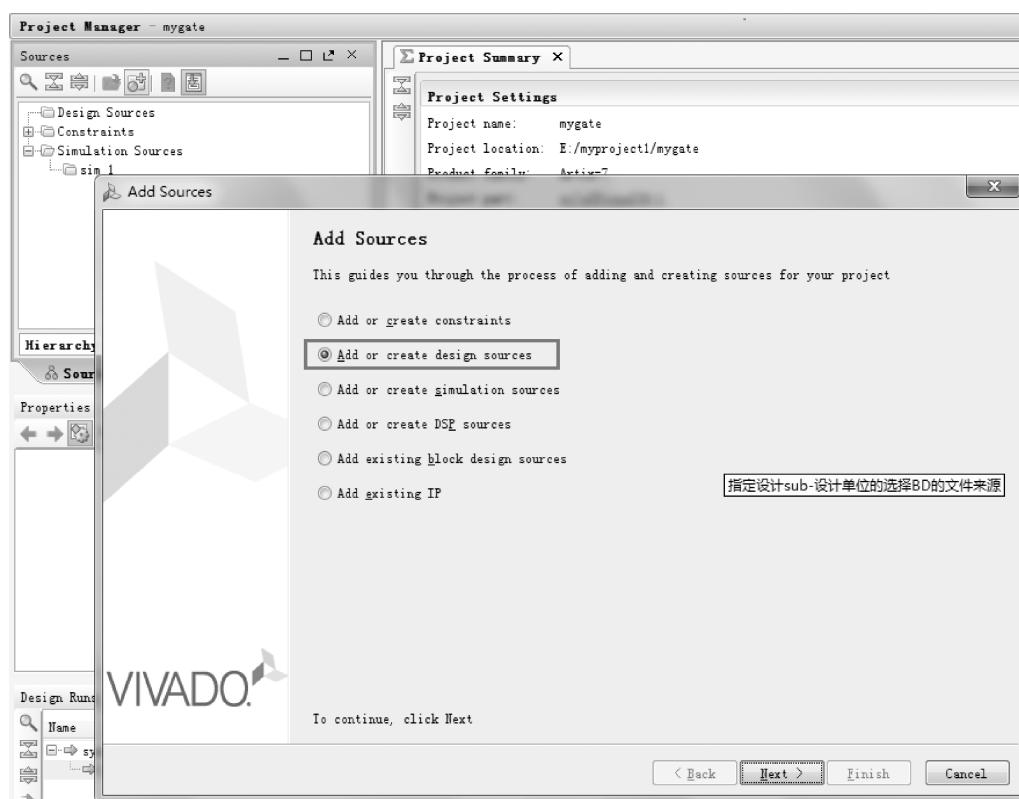

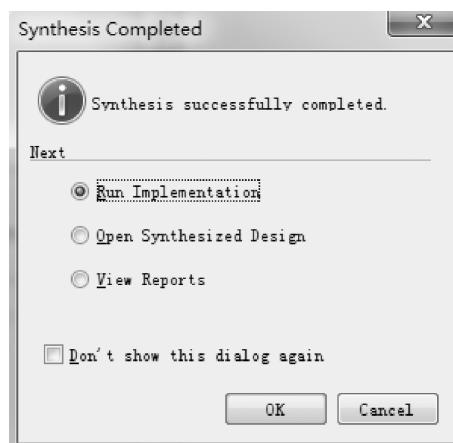

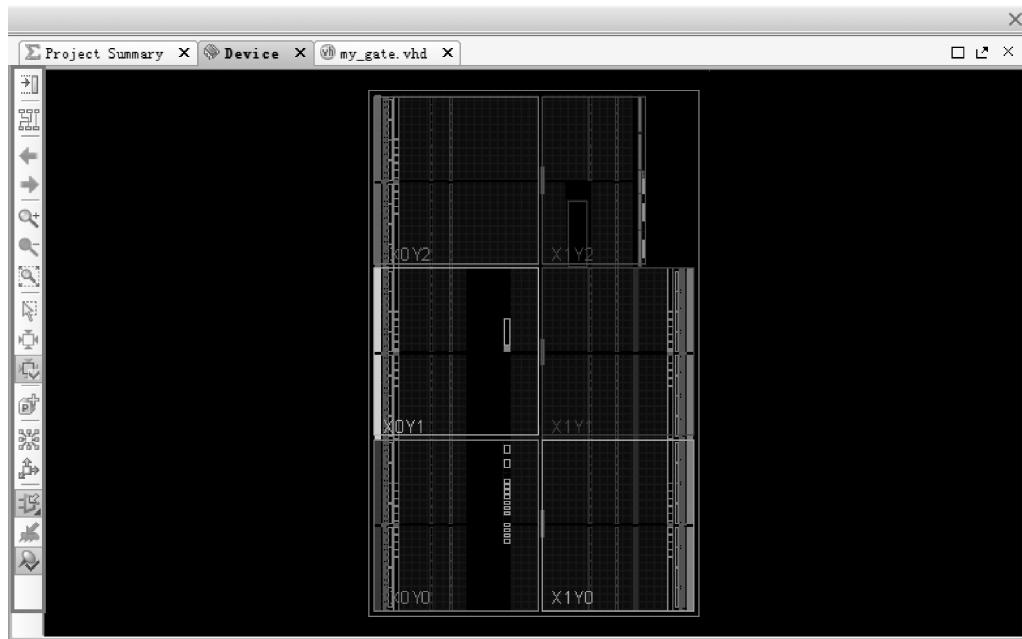

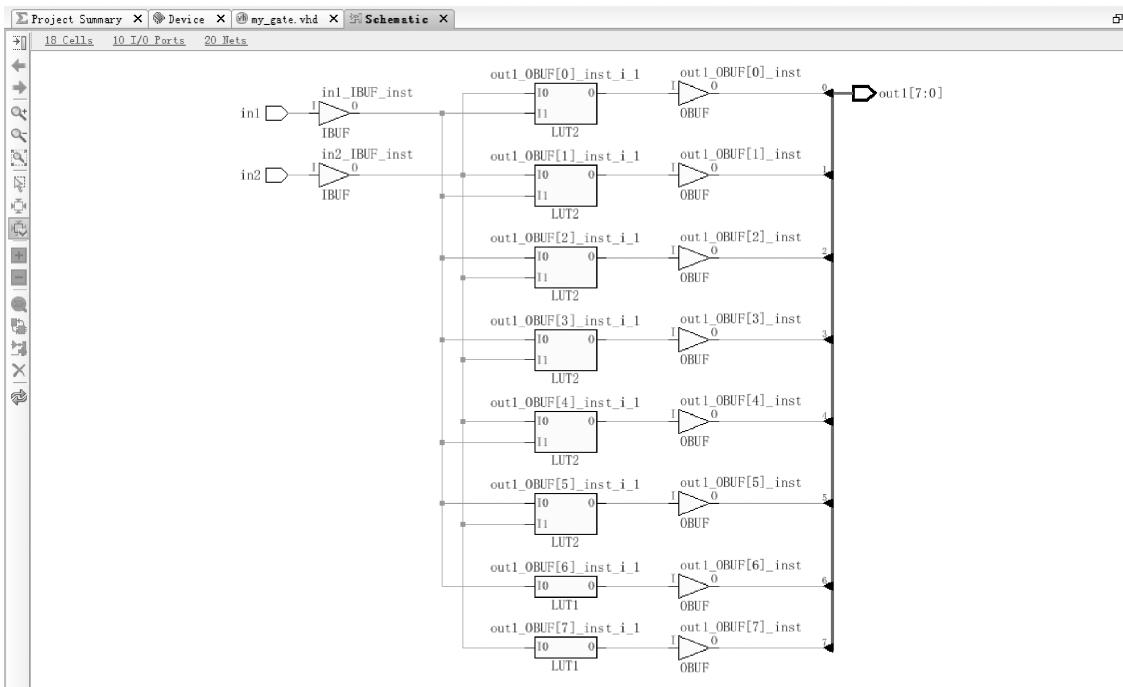

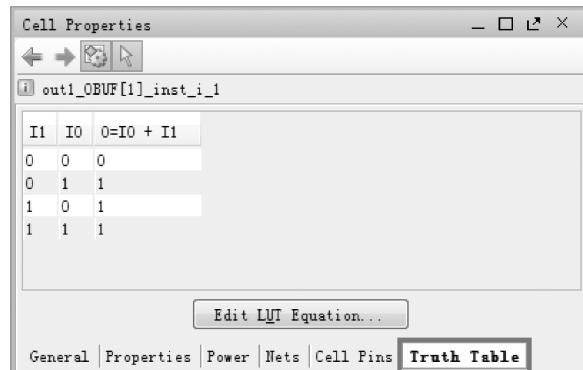

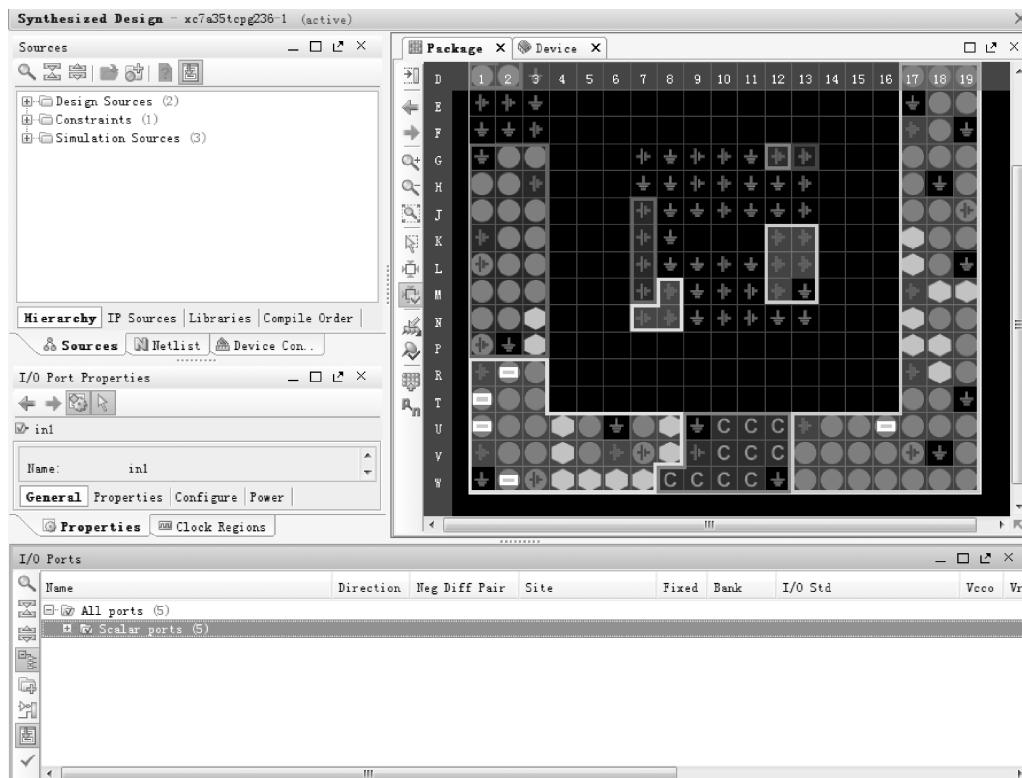

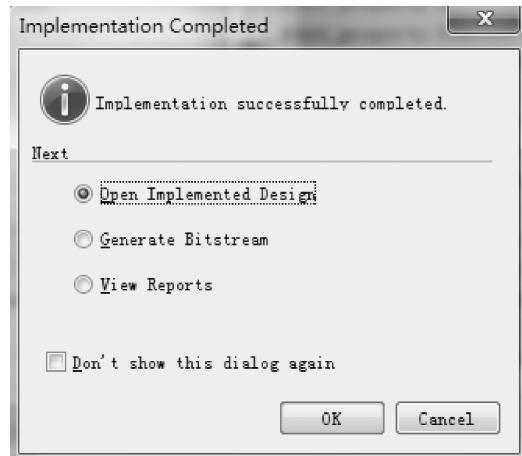

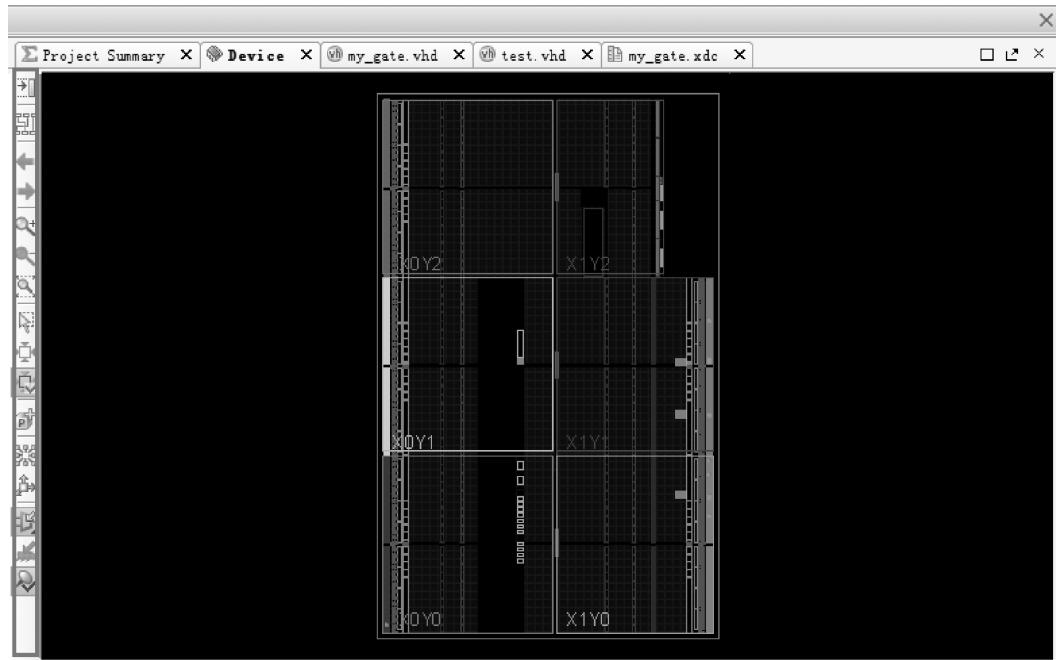

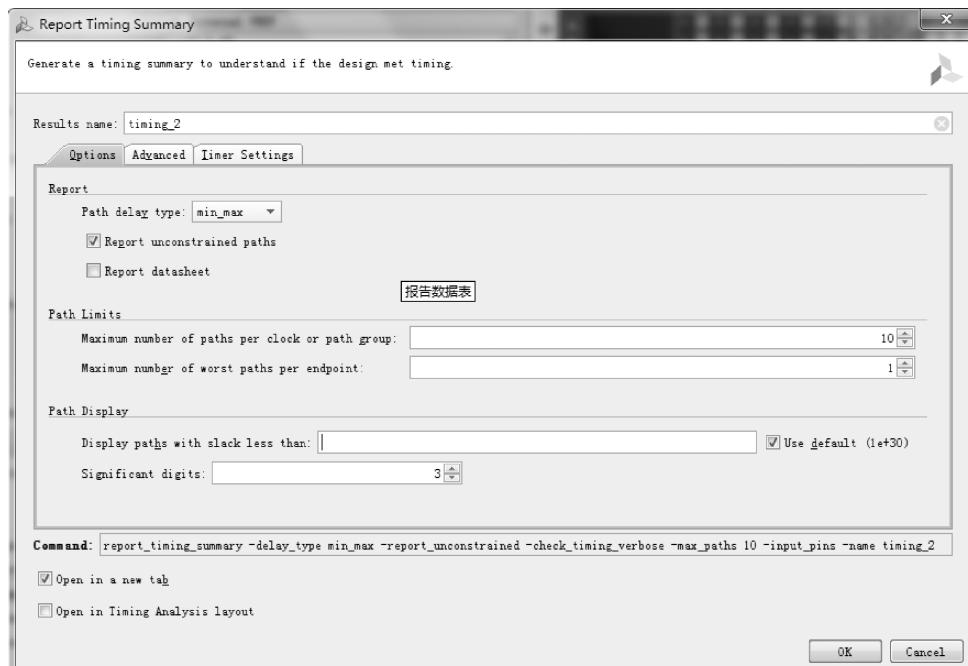

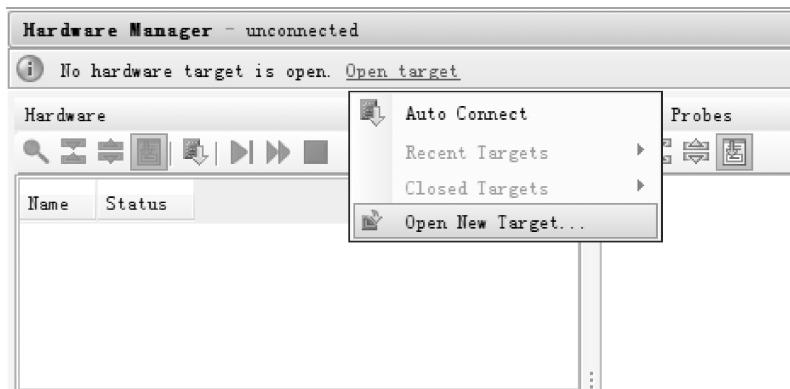

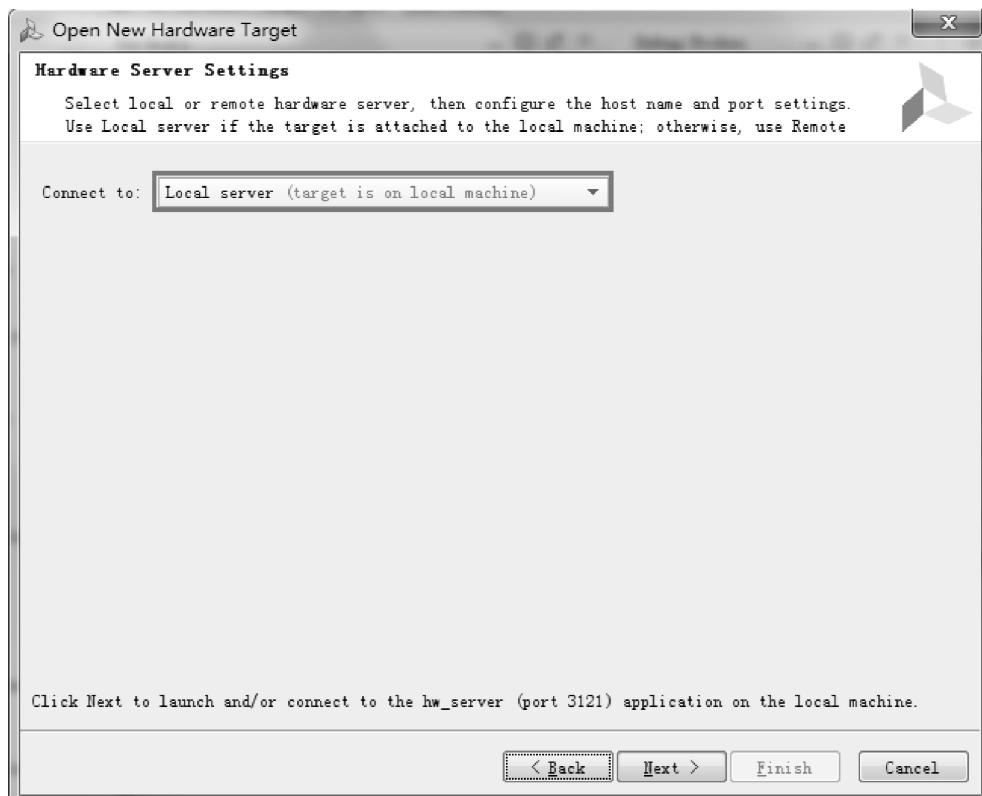

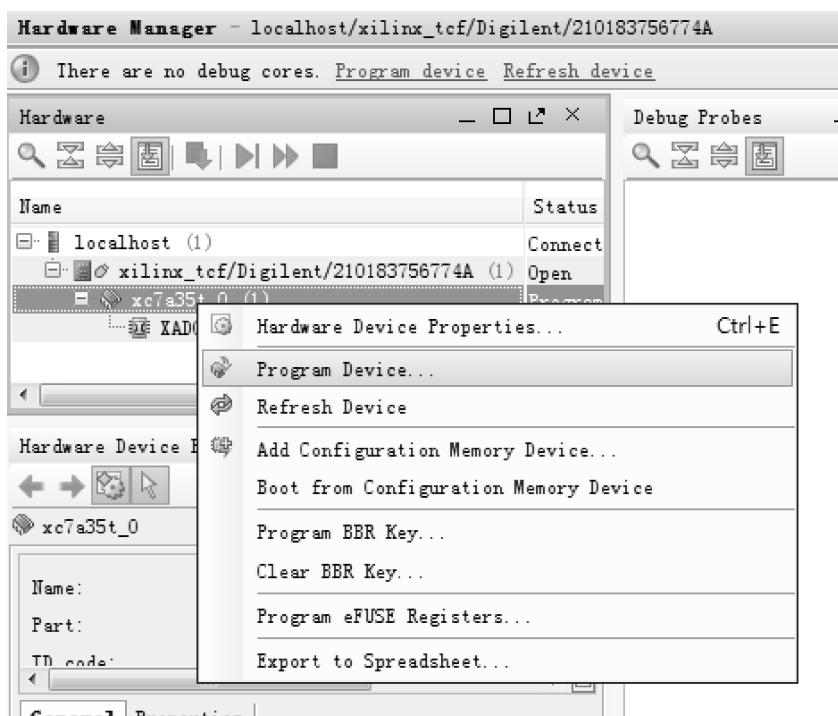

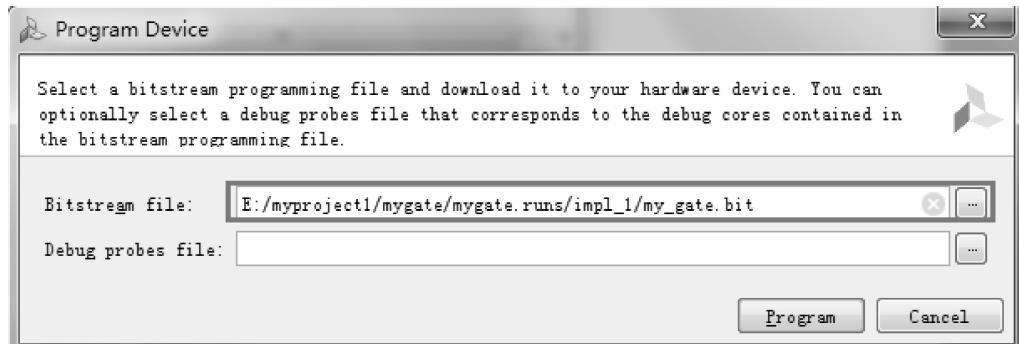

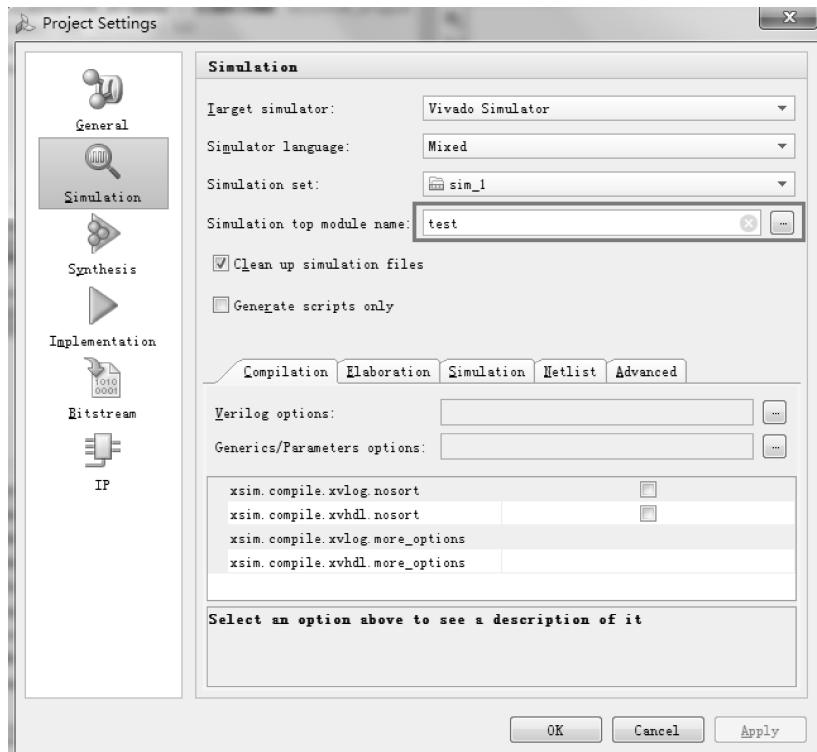

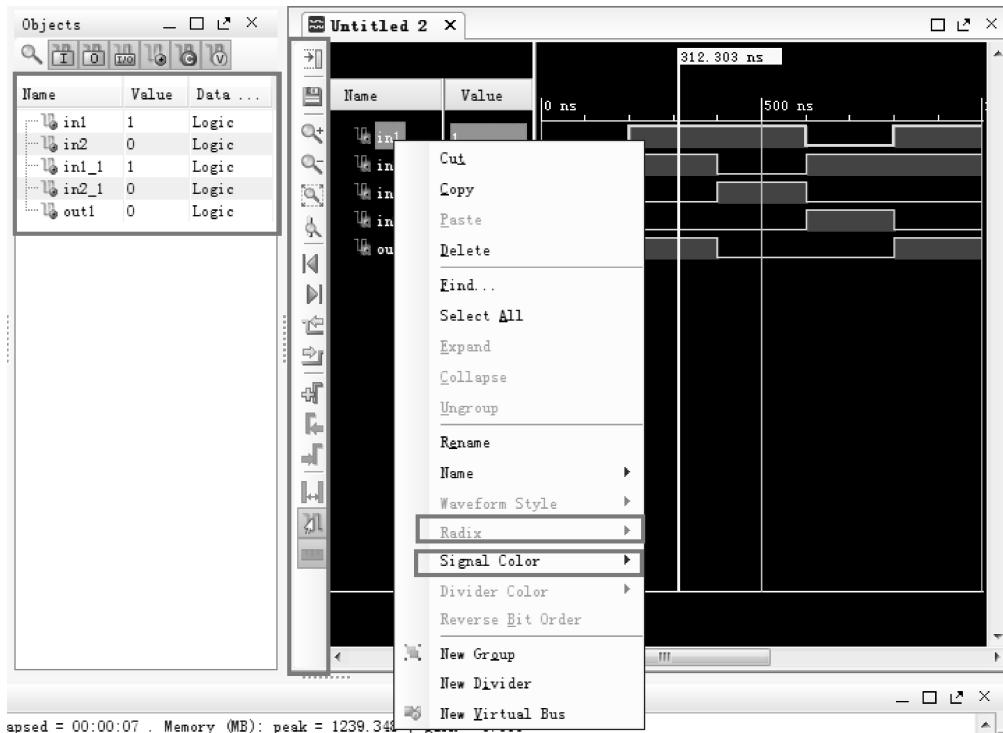

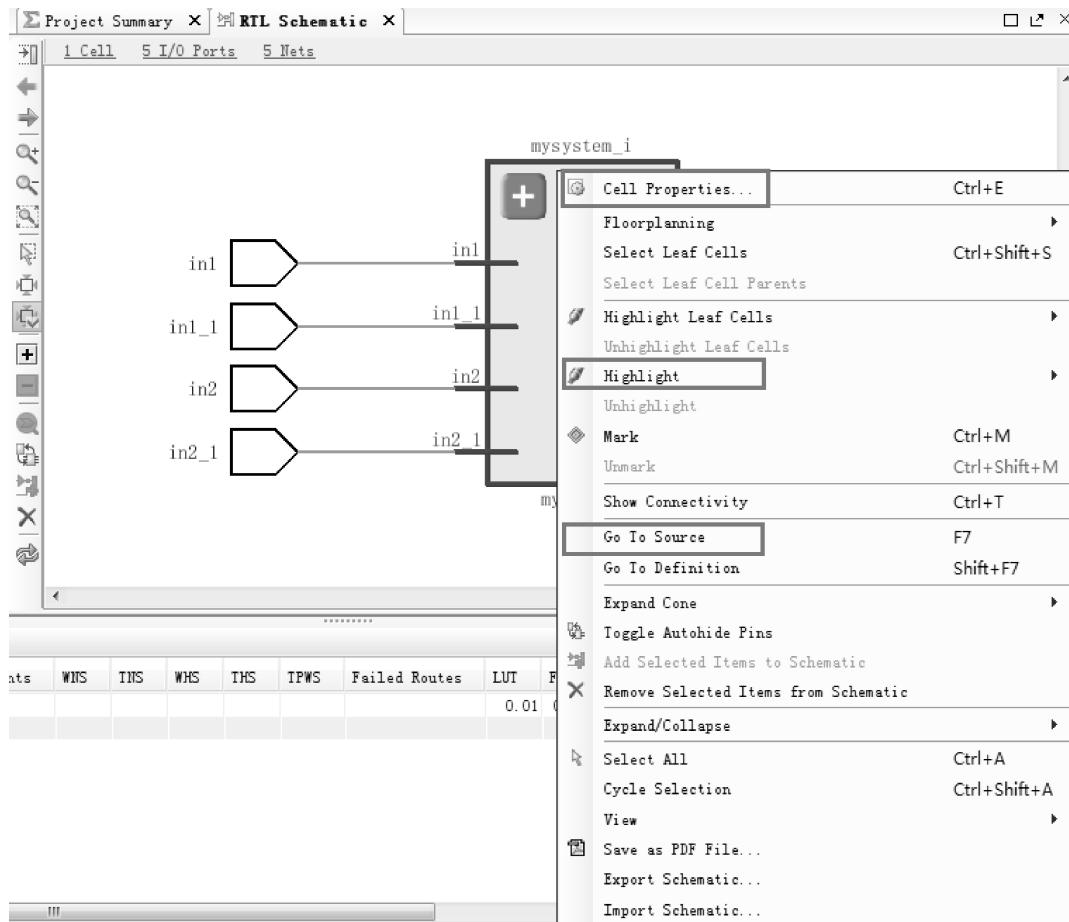

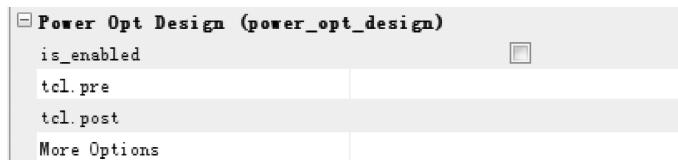

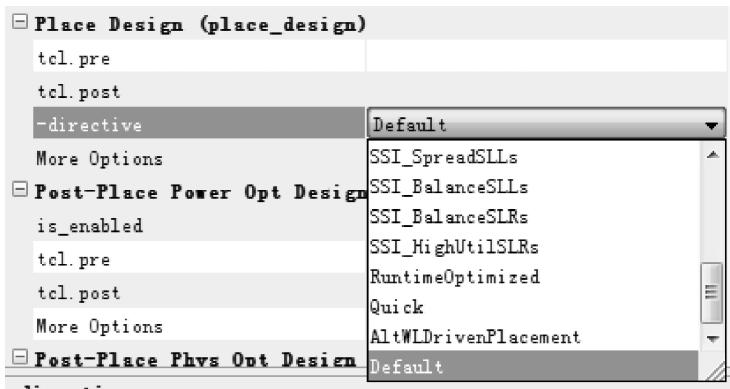

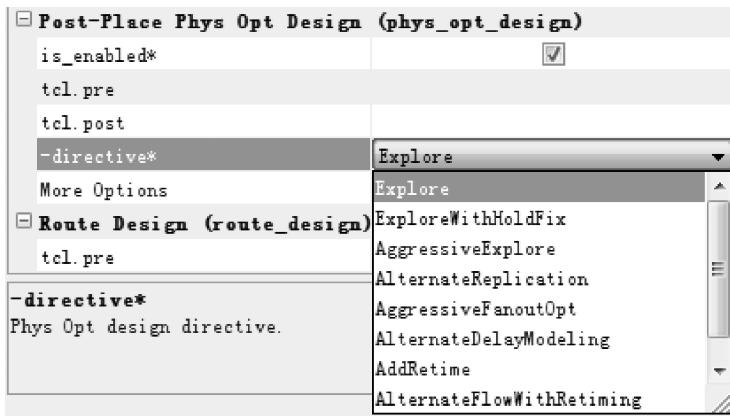

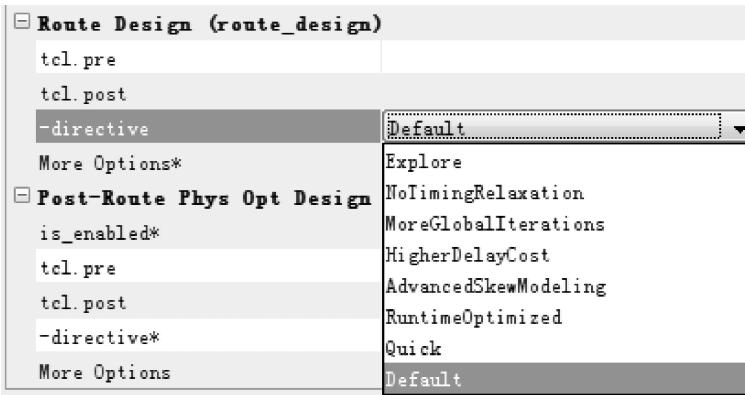

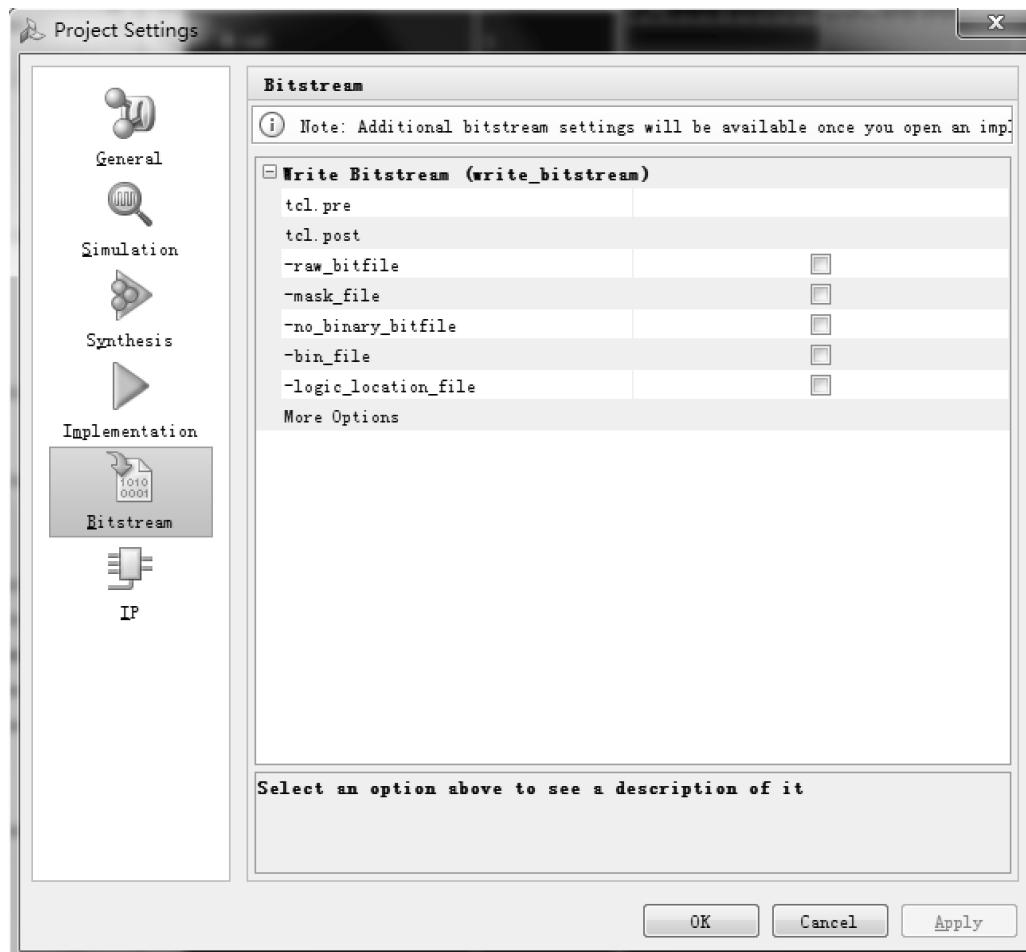

第 8 章介绍了在 Vivado 集成开发环境的工程模式下设计工程的基本设计实现流程。工程模式下的基本设计实现主要步骤包括：创建一个新的设计工程、创建并添加新的设计文件、RTL 详细描述和分析、设计综合、行为级仿真、建立约束、设计实现和分析、静态时序分析、设计时序仿真以及生成编程文件并下载到目标芯片。

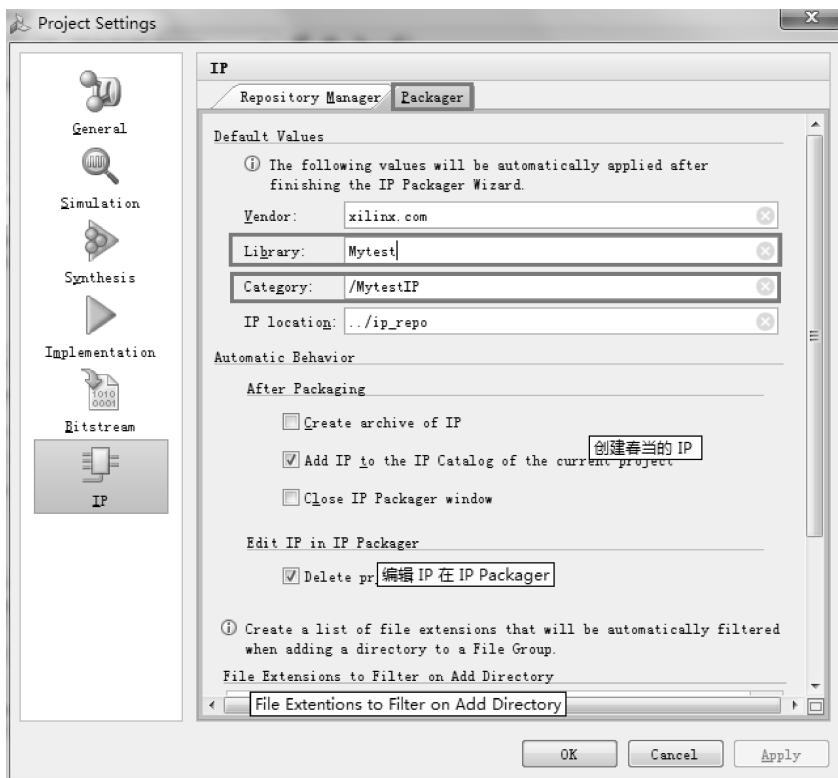

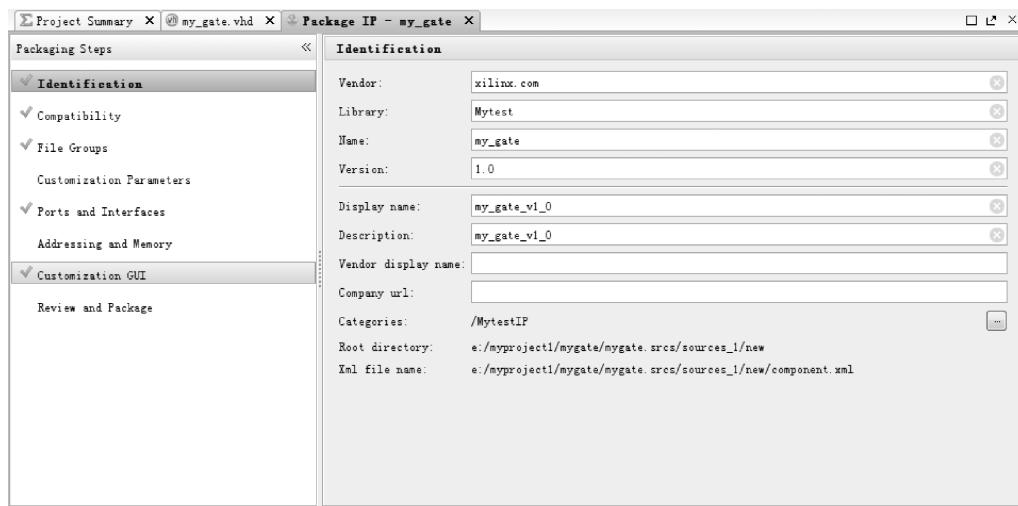

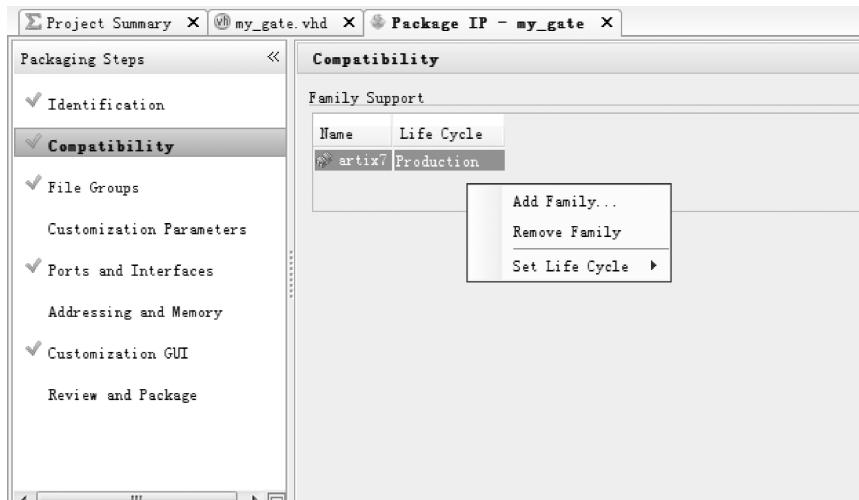

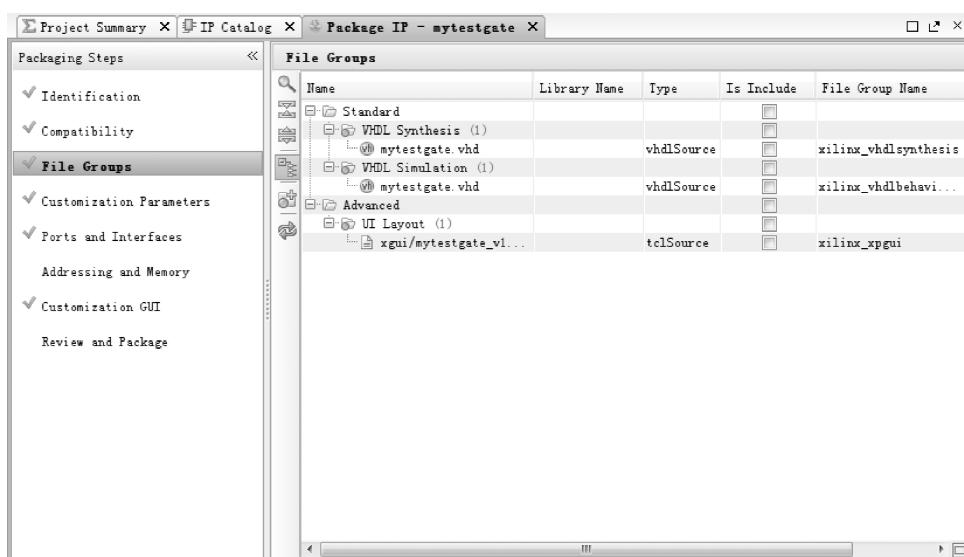

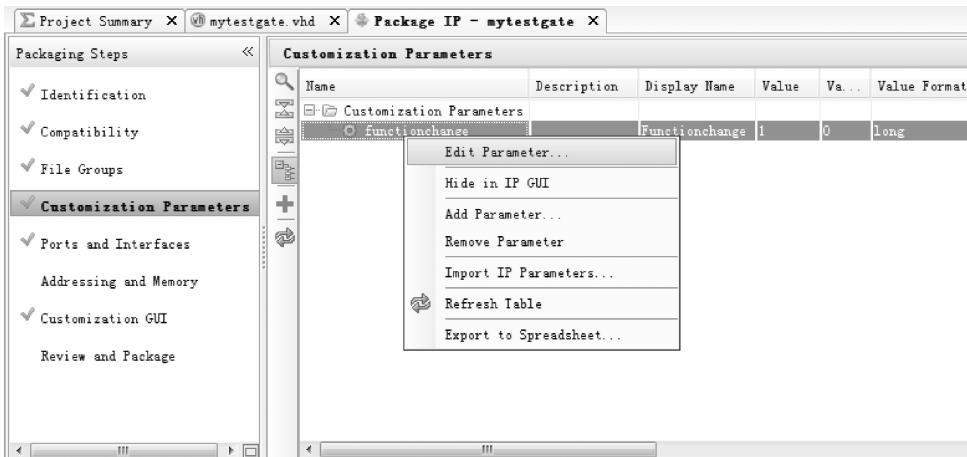

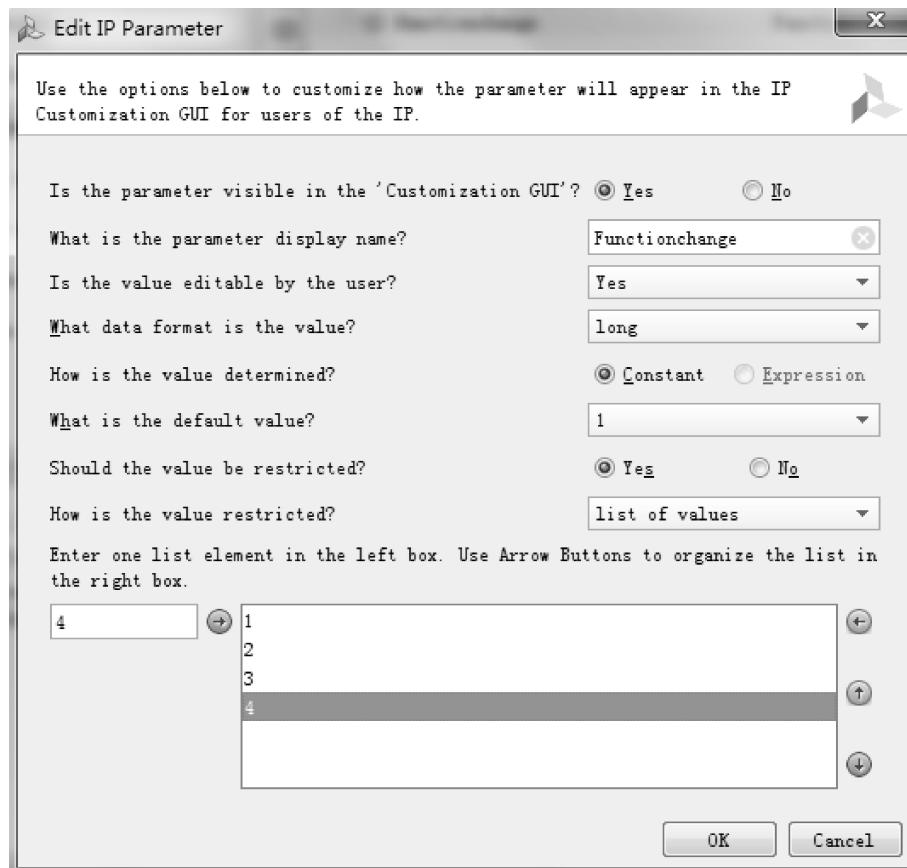

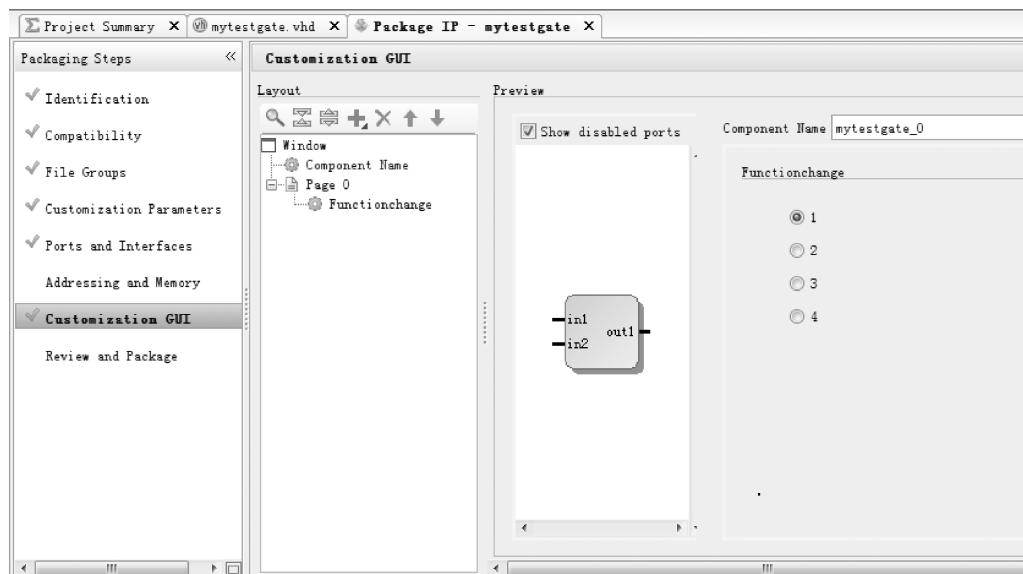

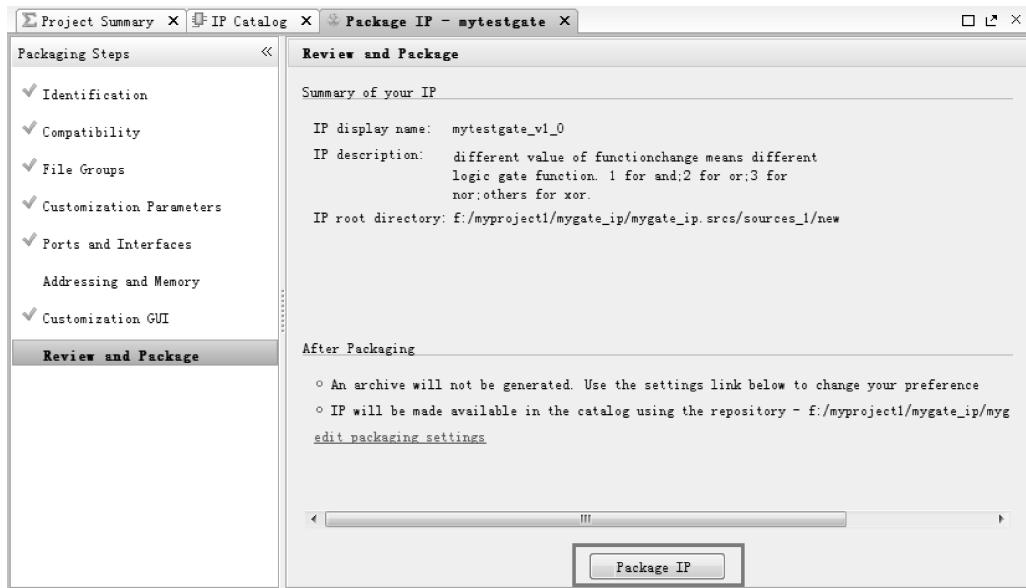

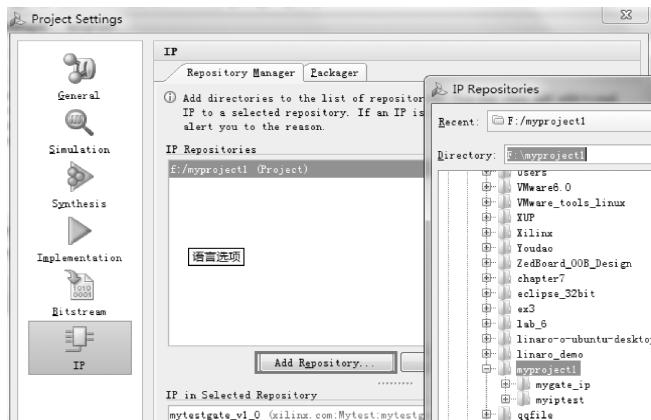

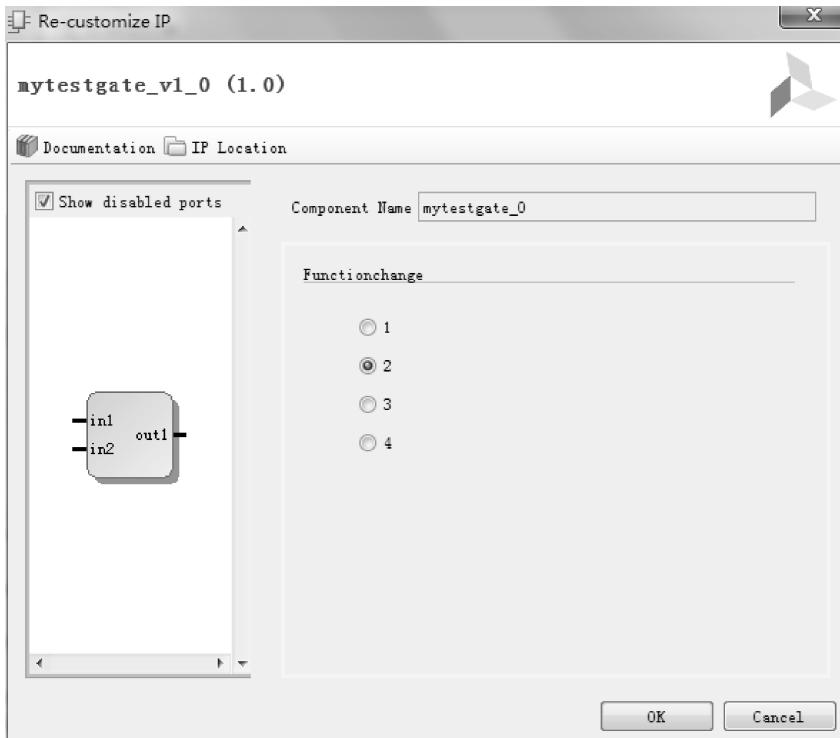

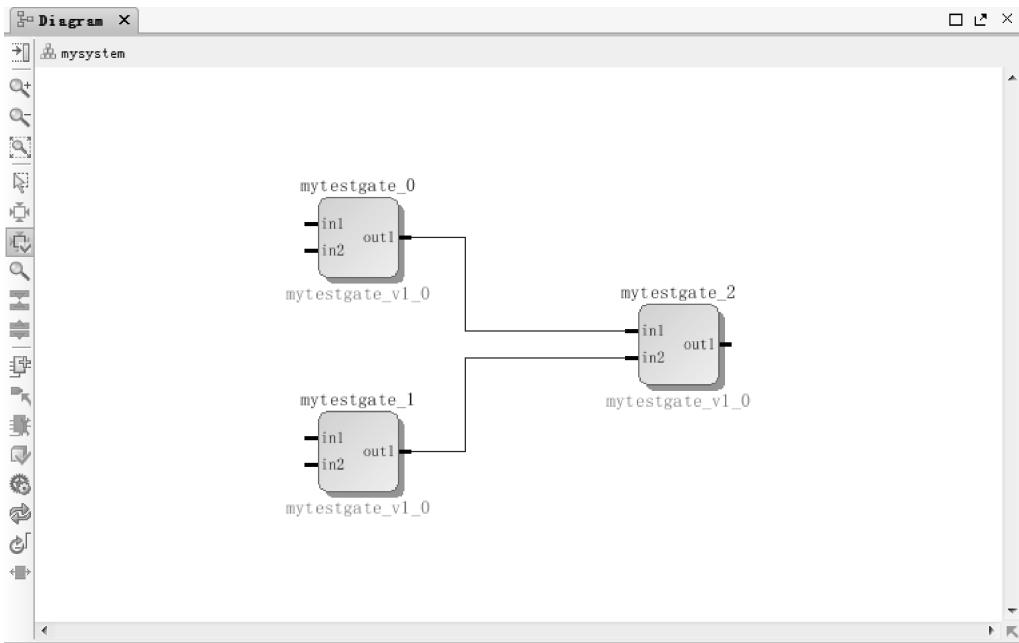

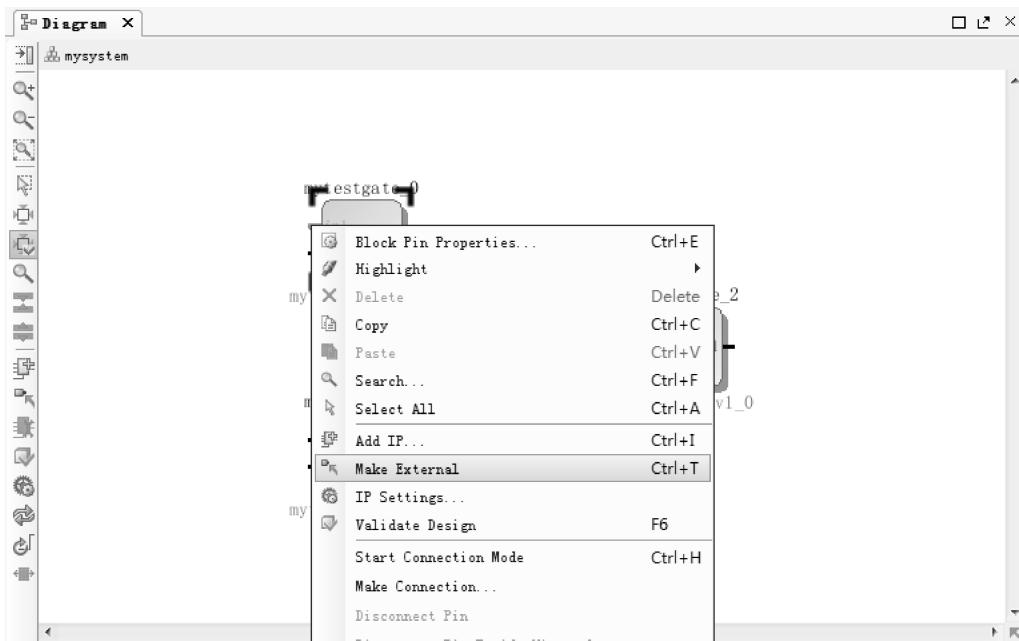

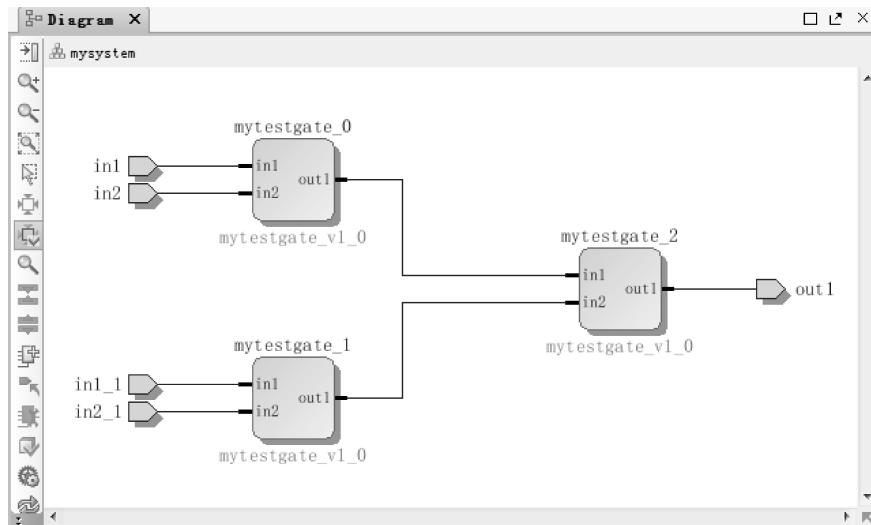

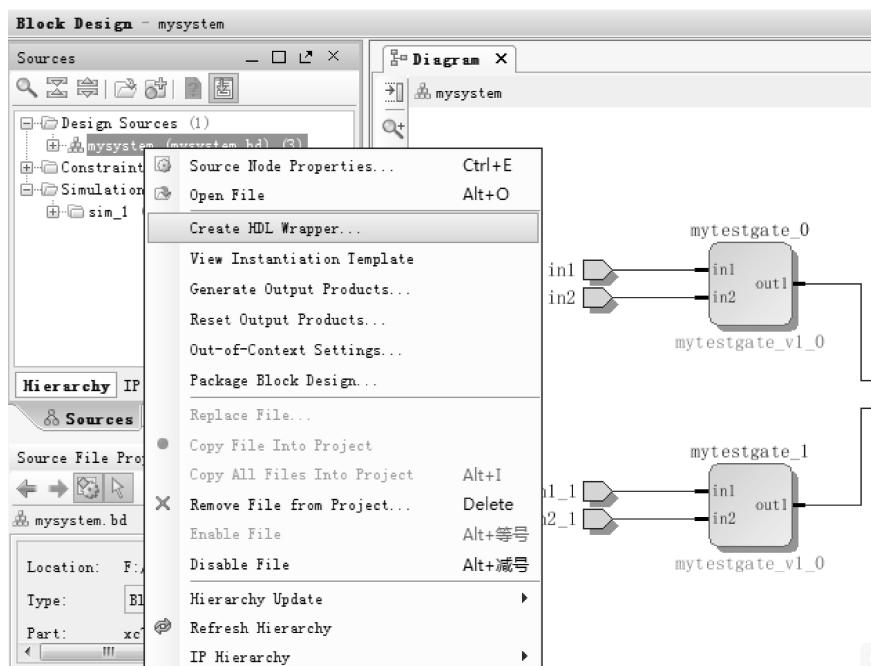

第 9 章介绍了 Vivado 集成设计环境下创建和封装用户 IP 的基本流程。创建和封装用户 IP 的主要步骤包括：创建一个用于定制用户 IP 的工程、设置定制 IP 的库名和目录以及封装 IP。

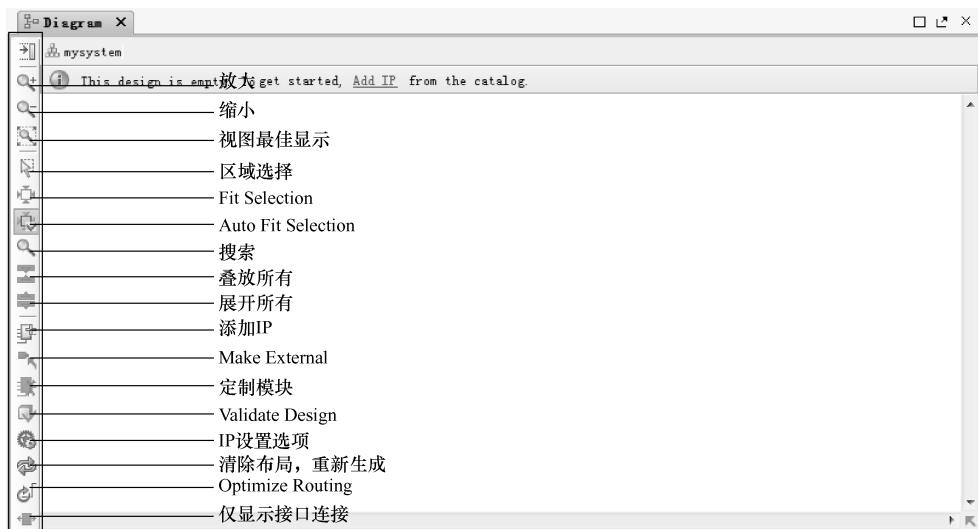

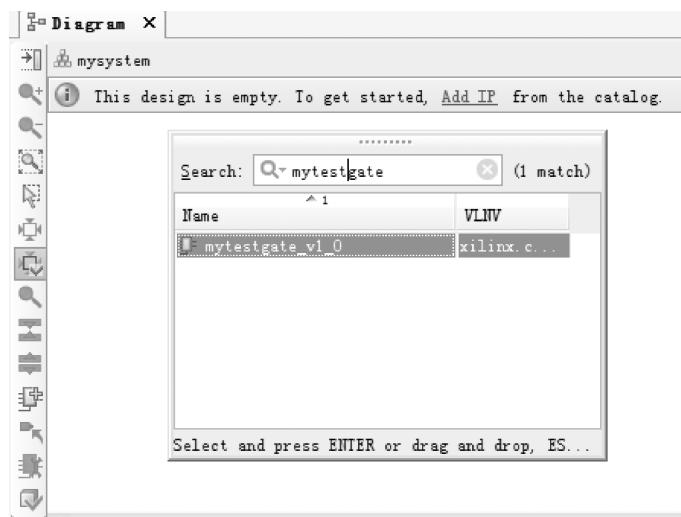

第 10 章介绍了在 Vivado 集成开发环境下基于 IP 的简单系统的设计实现流程。基于 IP 的系统设计实现主要步骤包括：创建一个新的设计工程、创建基于 IP 的系统、行为级仿真、设计综合、建立约束、设计实现和分析、静态时序分析、设计时序仿真以及生成编程文件并下载到目标芯片。

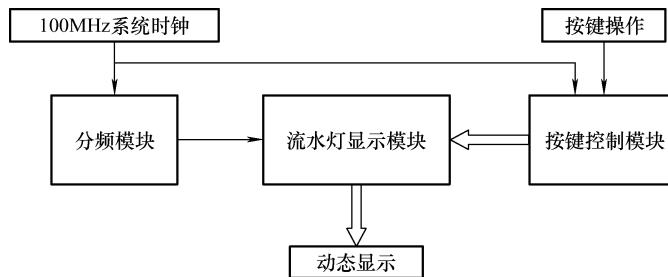

第 11 章介绍了如何使用 Vivado 集成开发环境和 Basys3 开发板设计实现键控流水灯实验的设计。首先介绍了键控流水灯的设计要求和功能描述；其次介绍了键控流水灯的层次化设计方案，主要包括三部分内容，分别是分频模块；流水灯显示模块和按键控制模块；最后对键控流水灯设计进行了硬件测试。

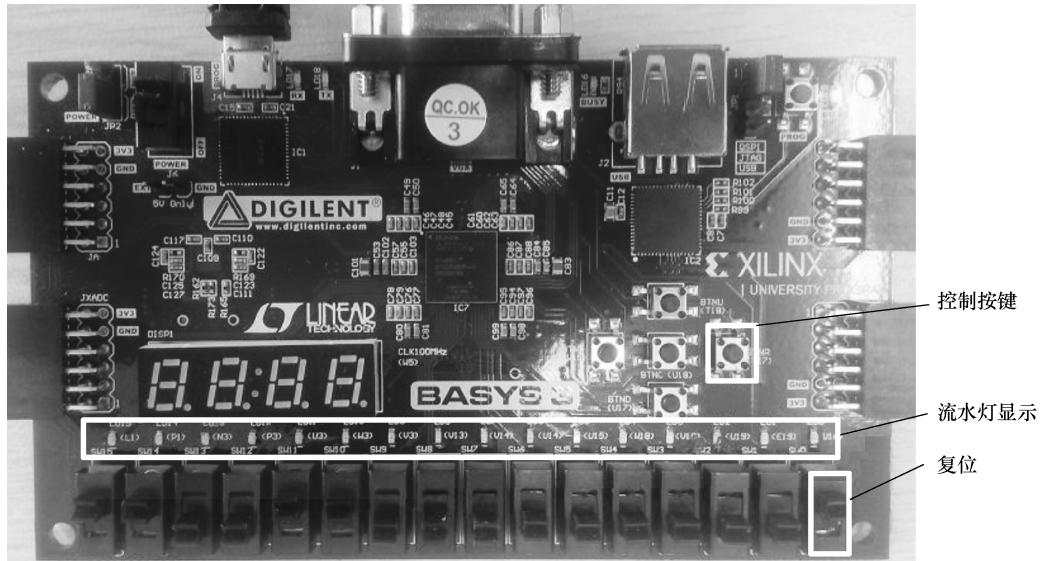

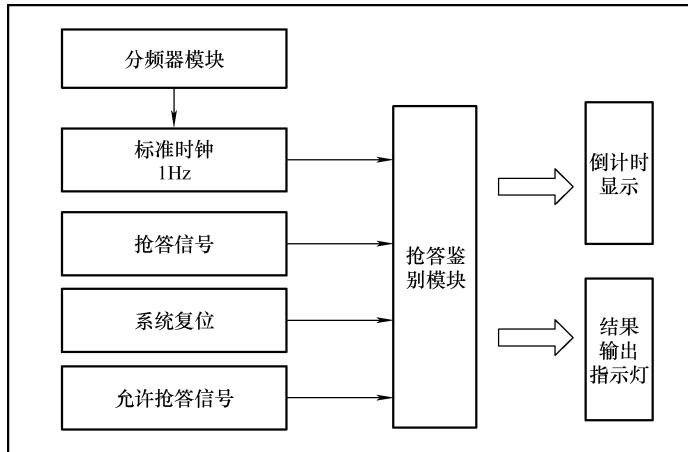

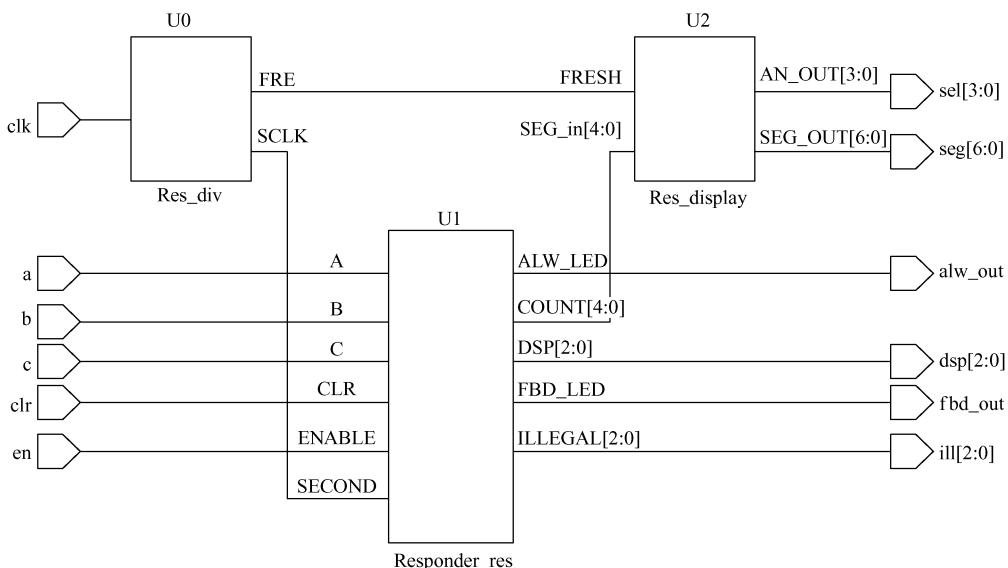

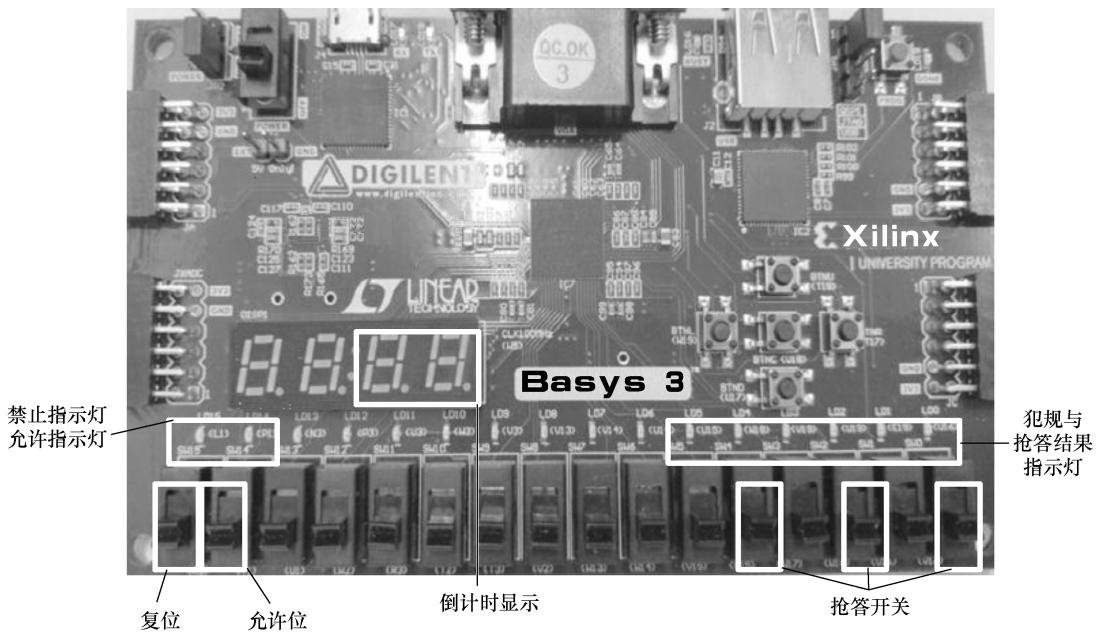

第 12 章介绍了抢答器实验设计。首先介绍了抢答器的设计要求和功能描述；其次制订了三人抢答器的层次化设计方案，主要包括三部分内容，分别是分频器模块、抢答鉴别器模块和数码管显示模块；然后对抢答器进行了顶层设计和仿真；最后对抢答器的设计进行了硬件测试。

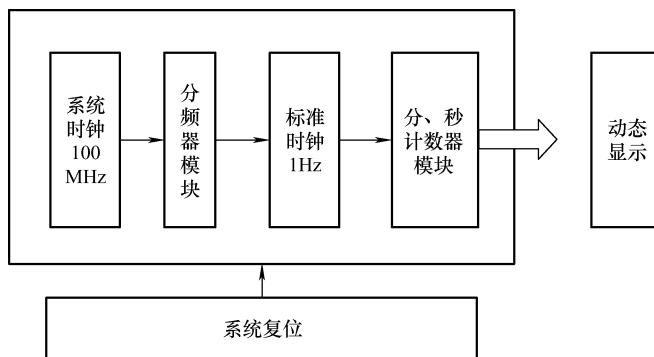

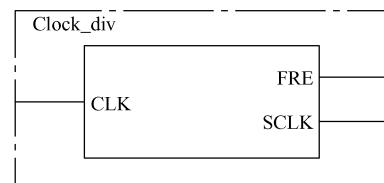

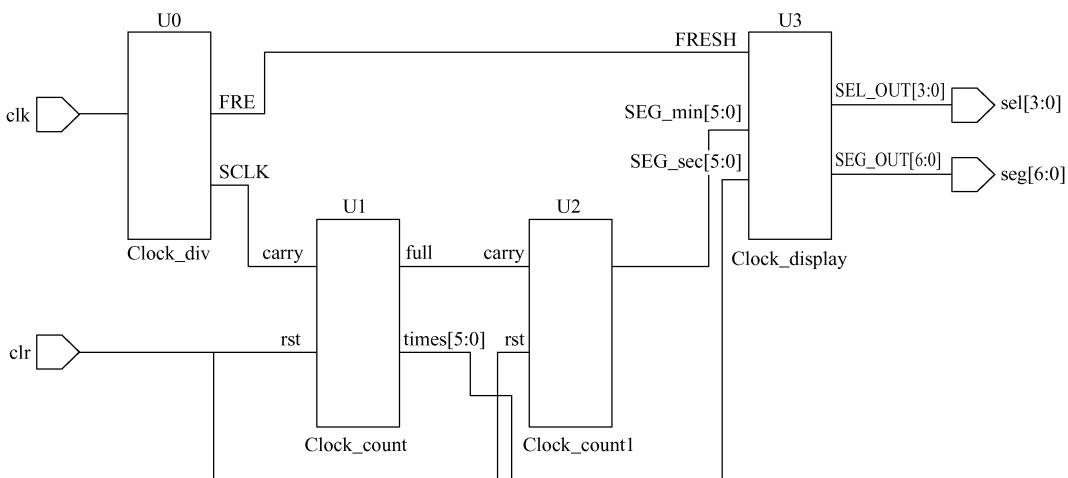

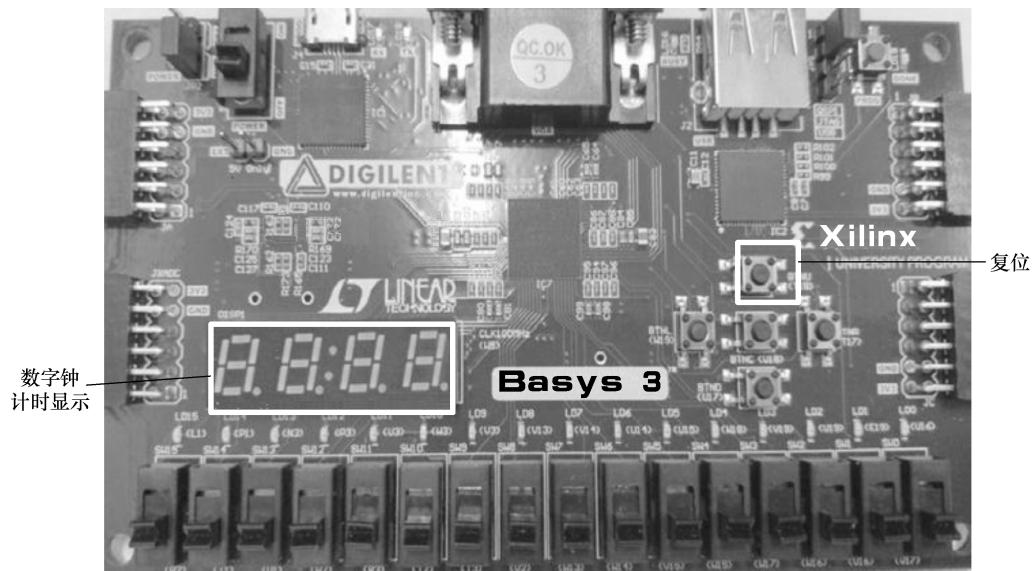

第 13 章主要介绍了一个简单的数字钟实验设计，首先介绍了数字钟的设计要求和功能描述；然后介绍了数字钟的层次化设计方案，主要包括三部分内容，分别是分频器模块、计数模块和数码管显示模块；之后对数字钟进行了顶层设计和仿真；最后对本次设计进行了硬件测试。

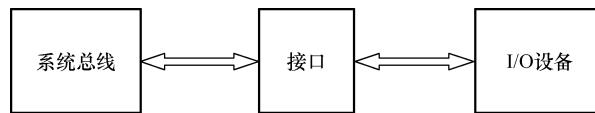

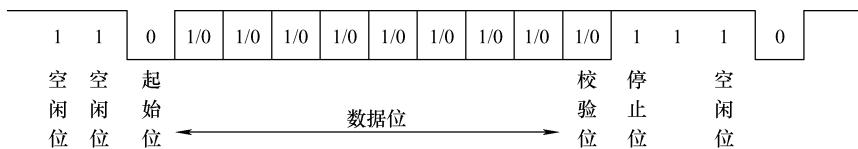

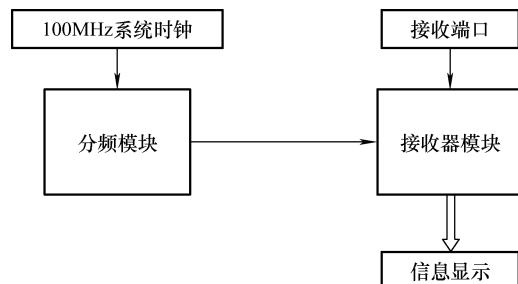

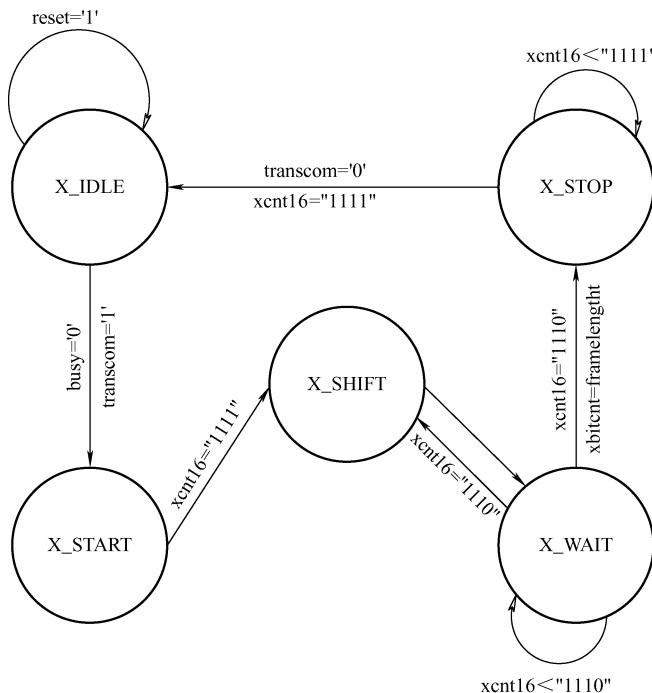

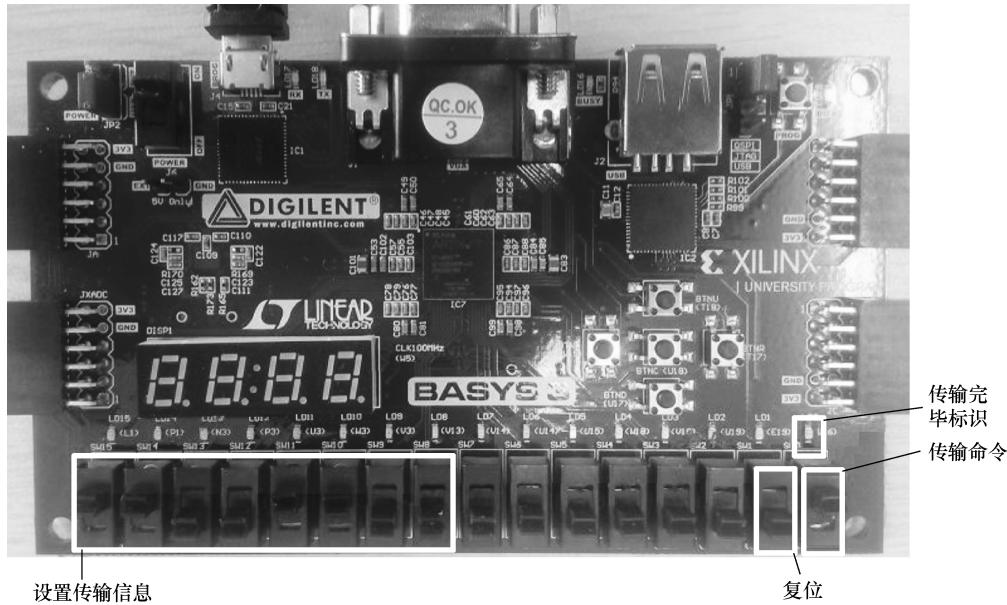

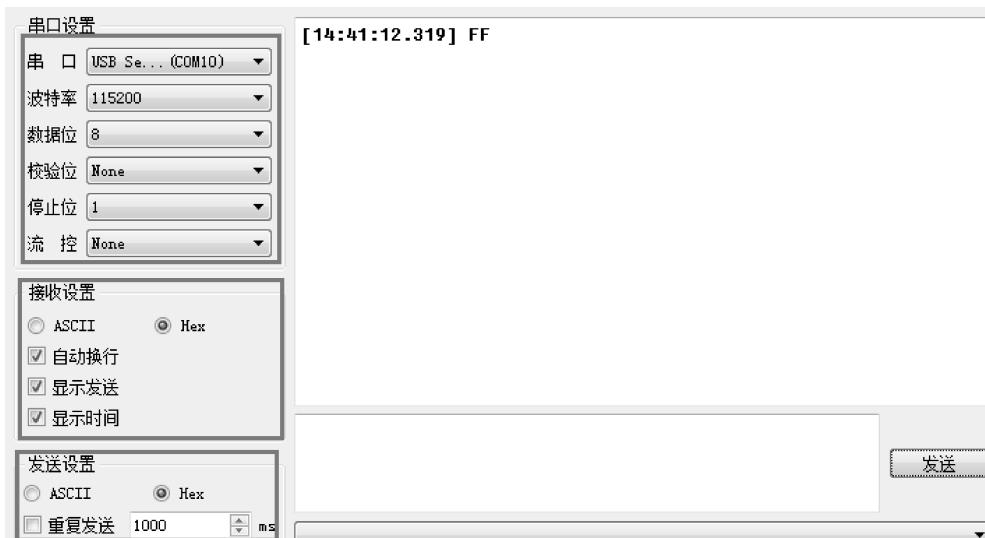

第 14 章介绍了如何使用 Vivado 集成开发环境和 Basys3 开发板进行简单的 UART 实验设计，实验分为两部分，一部分是接收器的设计实现，另一部分是发送器的设计实现。在两部分中分别介绍了接收器和发送器的层次化设计方案，并对其进行了硬件测试。

本书内容充实，系统全面，重点突出，阐述循序渐进，由浅入深。书中所有例题均在 Vivado 环境下运行通过。本书配有免费的电子课件，欢迎选用本书作为教材的教师登录 [www.cmpedu.com](http://www.cmpedu.com) 下载或发邮件到 wangkang-maizi9@126.com 索取。

参加本书编写、校对及程序测试工作的还有吴金辉、王辉等，在此表示感谢。

由于作者水平有限，书中难免有错误和不足之处，恳请各位专家和读者批评指正。

# 目 录

## 前 言

|                              |    |

|------------------------------|----|

| <b>第1章 绪论</b>                | 1  |

| 1.1 EDA 技术概要                 | 1  |

| 1.1.1 EDA 技术的含义              | 1  |

| 1.1.2 EDA 技术的发展历程            | 1  |

| 1.1.3 EDA 的基本特征              | 3  |

| 1.1.4 EDA 技术的优势              | 5  |

| 1.2 EDA 技术的实现目标              | 7  |

| 1.3 硬件描述语言                   | 8  |

| 1.3.1 VHDL                   | 8  |

| 1.3.2 Verilog HDL            | 9  |

| 1.3.3 VHDL 和 Verilog HDL 的比较 | 9  |

| 1.4 常用的 EDA 工具               | 10 |

| 1.4.1 设计输入编辑器                | 11 |

| 1.4.2 综合器                    | 11 |

| 1.4.3 仿真器                    | 13 |

| 1.4.4 适配器                    | 13 |

| 1.4.5 编程下载                   | 14 |

| 1.5 EDA 的工程设计流程              | 14 |

| 1.6 Vivado 概述                | 17 |

| 1.7 EDA 技术的发展趋势              | 17 |

| 本章小结                         | 19 |

| 习题                           | 19 |

|                              |    |

|------------------------------|----|

| <b>第2章 CPLD 与 FPGA 的结构原理</b> | 20 |

| 2.1 PLD 概述                   | 20 |

| 2.1.1 PLD 入门                 | 20 |

| 2.1.2 常见的 PLD                | 21 |

| 2.1.3 PLD 的优点                | 22 |

| 2.1.4 PLD 的发展趋势              | 23 |

| 2.2 简单 PLD 的结构原理             | 24 |

| 2.2.1 逻辑符号表示方法               | 25 |

| 2.2.2 PROM 的结构原理             | 25 |

| 2.2.3 PLA 的结构原理              | 26 |

| 2.2.4 PAL 的结构原理              | 26 |

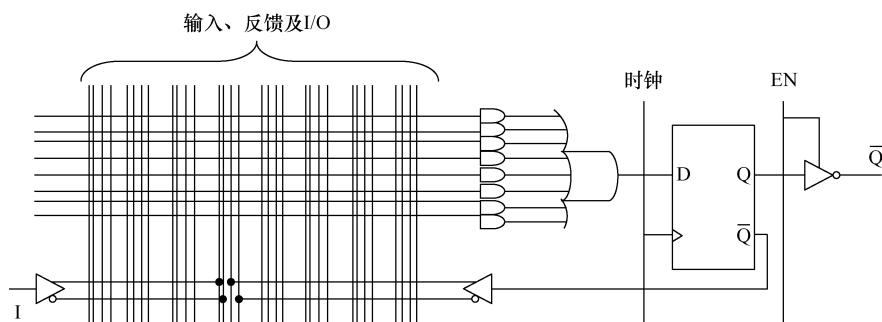

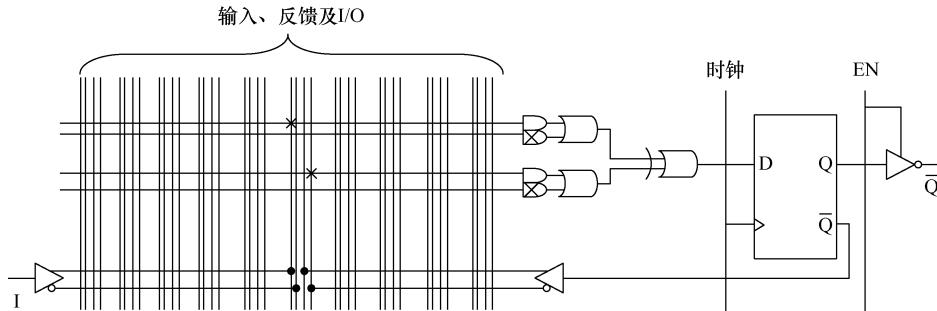

| 2.2.5 GAL 的结构原理              | 31 |

|                              |    |

|------------------------------|----|

| 2.3 CPLD 的结构原理               | 35 |

| 2.3.1 CPLD 的基本结构             | 35 |

| 2.3.2 基于乘积项的可编程逻辑器件          | 36 |

| 2.4 FPGA 的结构原理               | 39 |

| 2.4.1 查找表型 FPGA 的逻辑结构        | 41 |

| 2.4.2 Xilinx 公司 7 系列 FPGA 简介 | 43 |

| 2.4.3 FPGA 与 CPLD 的区别        | 47 |

| 2.5 硬件测试                     | 48 |

| 2.6 CPLD/FPGA 的编程与配置         | 49 |

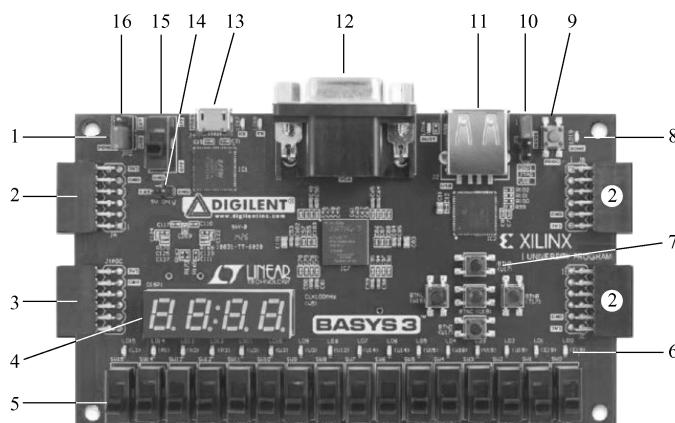

| 2.7 Basys3 开发板介绍             | 50 |

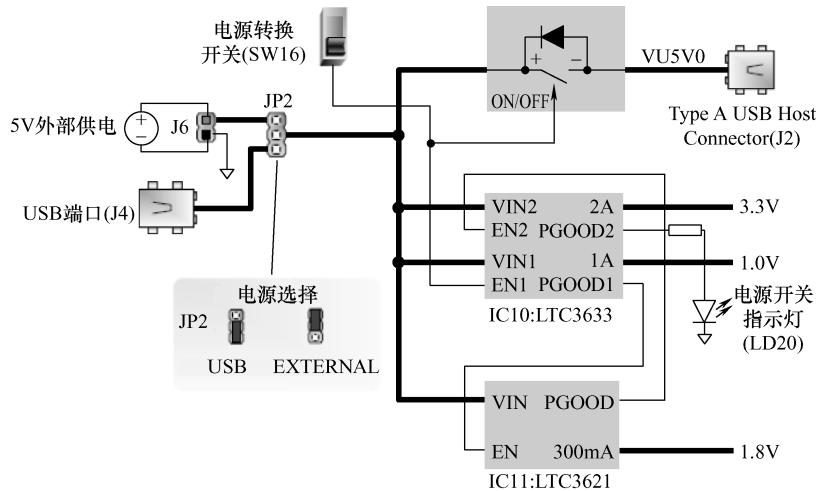

| 2.7.1 电源电路                   | 51 |

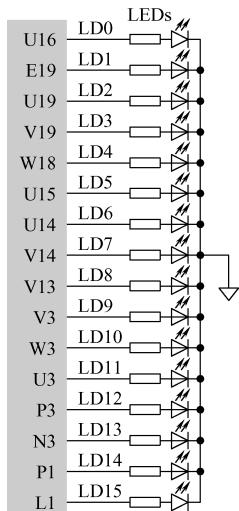

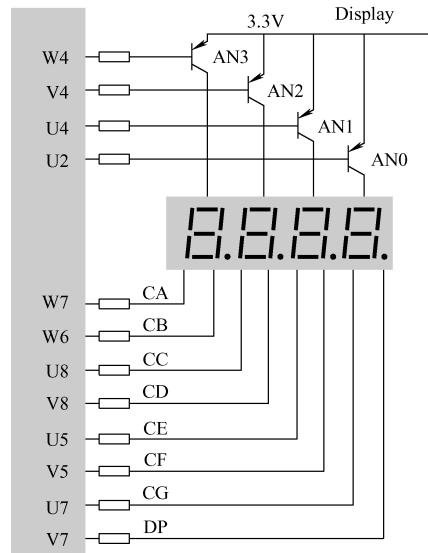

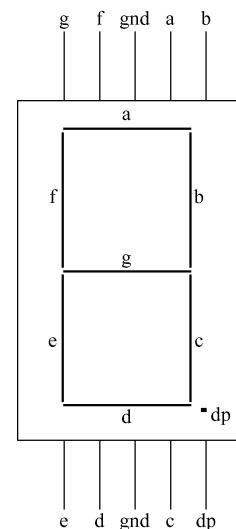

| 2.7.2 LED 灯电路和数码管电路          | 51 |

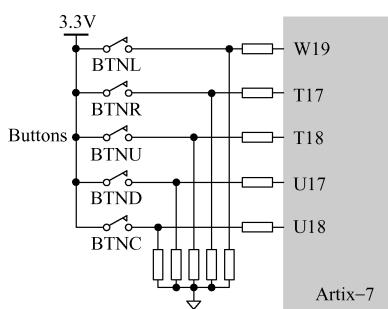

| 2.7.3 按键电路和拨码开关电路            | 52 |

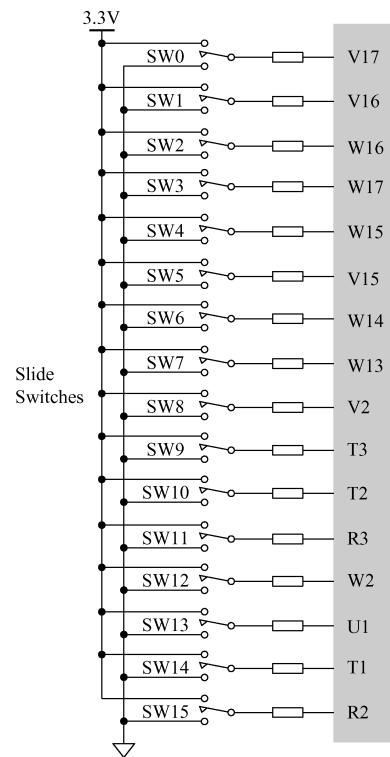

| 2.7.4 VGA 显示电路和 I/O 扩展电路     | 53 |

| 本章小结                         | 53 |

| 习题                           | 54 |

| <b>第3章 VHDL 入门基础</b>         | 55 |

| 3.1 VHDL 的基本结构               | 55 |

| 3.1.1 实体                     | 56 |

| 3.1.2 结构体                    | 57 |

| 3.1.3 库、程序包和配置               | 57 |

| 3.2 VHDL 的文字规则               | 59 |

| 3.2.1 数字型文字                  | 60 |

| 3.2.2 字符串型文字                 | 60 |

| 3.2.3 标识符                    | 60 |

| 3.2.4 下标                     | 61 |

| 3.3 VHDL 的数据对象               | 62 |

| 3.3.1 常数                     | 62 |

| 3.3.2 变量                     | 62 |

| 3.3.3 信号                     | 62 |

| 3.3.4 文件                     | 63 |

| 3.4 VHDL 的数据类型               | 63 |

| 3.4.1 VHDL 预定义数据类型           | 64 |

| 3.4.2 用户自定义数据类型              | 67 |

| 3.4.3 数据类型间的转换               | 68 |

|                                  |            |                            |     |

|----------------------------------|------------|----------------------------|-----|

| 3.5 VHDL 的操作符 .....              | 69         | 5.3.1 单进程 Moore 型状态机 ..... | 120 |

| 3.6 VHDL 预定义属性 .....             | 73         | 5.3.2 多进程 Moore 型状态机 ..... | 122 |

| 本章小结 .....                       | 75         | 5.4 Mealy 型状态机的设计 .....    | 125 |

| 习题 .....                         | 76         | 5.5 状态编码 .....             | 127 |

| <b>第4章 VHDL 硬件描述语言 .....</b>     | <b>77</b>  | 5.5.1 顺序编码 .....           | 127 |

| 4.1 进程语句 .....                   | 77         | 5.5.2 枚举类型编码 .....         | 128 |

| 4.2 赋值语句 .....                   | 78         | 5.5.3 状态位直接输出型编码 .....     | 128 |

| 4.3 顺序描述语句 .....                 | 80         | 5.5.4 一位热码编码 .....         | 129 |

| 4.3.1 IF 语句 .....                | 80         | 5.6 安全状态机设计 .....          | 129 |

| 4.3.2 CASE 语句 .....              | 82         | 5.6.1 程序直接导引法 .....        | 129 |

| 4.3.3 LOOP 语句 .....              | 83         | 5.6.2 状态编码检测法 .....        | 130 |

| 4.3.4 NEXT 语句和 EXIT 语句 .....     | 84         | 本章小结 .....                 | 130 |

| 4.3.5 WAIT 语句 .....              | 85         | 习题 .....                   | 130 |

| 4.3.6 RETURN 语句 .....            | 86         |                            |     |

| 4.3.7 NULL 语句 .....              | 87         |                            |     |

| 4.4 元件例化语句 .....                 | 87         |                            |     |

| 4.5 生成语句 .....                   | 90         |                            |     |

| 4.6 块语句 .....                    | 91         |                            |     |

| 4.7 程序包和配置 .....                 | 93         |                            |     |

| 4.7.1 程序包 .....                  | 93         |                            |     |

| 4.7.2 配置 .....                   | 94         |                            |     |

| 4.8 子程序 .....                    | 95         |                            |     |

| 4.8.1 过程 .....                   | 96         |                            |     |

| 4.8.2 函数 .....                   | 97         |                            |     |

| 4.9 其他语句 .....                   | 99         |                            |     |

| 4.10 常用设计举例 .....                | 100        |                            |     |

| 4.10.1 结构体的三种描述方式 .....          | 100        |                            |     |

| 4.10.2 组合逻辑电路设计 .....            | 102        |                            |     |

| 4.10.3 时序逻辑电路设计 .....            | 107        |                            |     |

| 本章小结 .....                       | 113        |                            |     |

| 习题 .....                         | 113        |                            |     |

| <b>第5章 有限状态机设计 .....</b>         | <b>114</b> |                            |     |

| 5.1 概述 .....                     | 114        |                            |     |

| 5.1.1 状态机的特点 .....               | 114        |                            |     |

| 5.1.2 状态机的分类 .....               | 115        |                            |     |

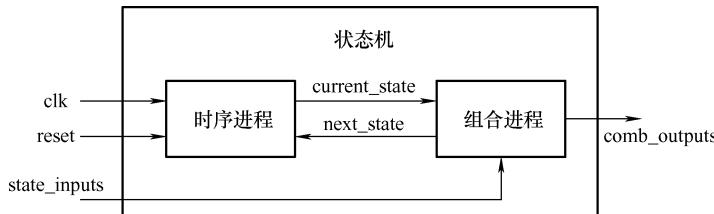

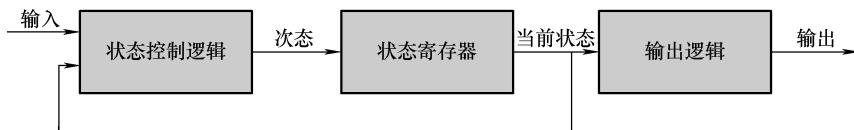

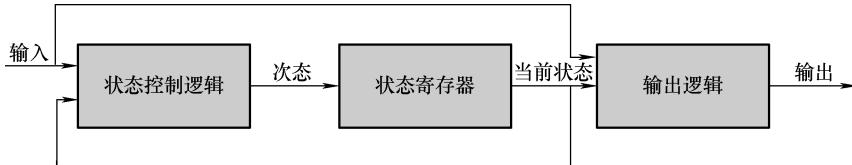

| 5.2 VHDL 状态机的一般形式 .....          | 116        |                            |     |

| 5.2.1 一般状态机的结构 .....             | 116        |                            |     |

| 5.2.2 状态机的设计流程 .....             | 118        |                            |     |

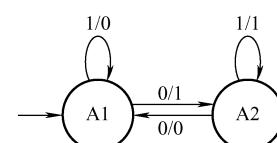

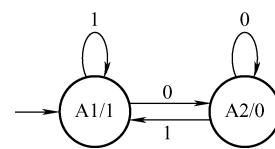

| 5.2.3 状态机的状态转移图描述 .....          | 118        |                            |     |

| 5.2.4 状态机的状态说明部分 .....           | 119        |                            |     |

| 5.3 Moore 型状态机的设计 .....          | 120        |                            |     |

|                                  |            | 5.3.1 单进程 Moore 型状态机 ..... | 120 |

|                                  |            | 5.3.2 多进程 Moore 型状态机 ..... | 122 |

|                                  |            | 5.4 Mealy 型状态机的设计 .....    | 125 |

|                                  |            | 5.5 状态编码 .....             | 127 |

|                                  |            | 5.5.1 顺序编码 .....           | 127 |

|                                  |            | 5.5.2 枚举类型编码 .....         | 128 |

|                                  |            | 5.5.3 状态位直接输出型编码 .....     | 128 |

|                                  |            | 5.5.4 一位热码编码 .....         | 129 |

|                                  |            | 5.6 安全状态机设计 .....          | 129 |

|                                  |            | 5.6.1 程序直接导引法 .....        | 129 |

|                                  |            | 5.6.2 状态编码检测法 .....        | 130 |

|                                  |            | 本章小结 .....                 | 130 |

|                                  |            | 习题 .....                   | 130 |

|                                  |            |                            |     |

| <b>第6章 VHDL 优化设计 .....</b>       | <b>132</b> |                            |     |

| 6.1 资源优化 .....                   | 132        |                            |     |

| 6.1.1 资源共享 .....                 | 132        |                            |     |

| 6.1.2 逻辑优化 .....                 | 135        |                            |     |

| 6.1.3 串行化 .....                  | 136        |                            |     |

| 6.2 速度优化 .....                   | 138        |                            |     |

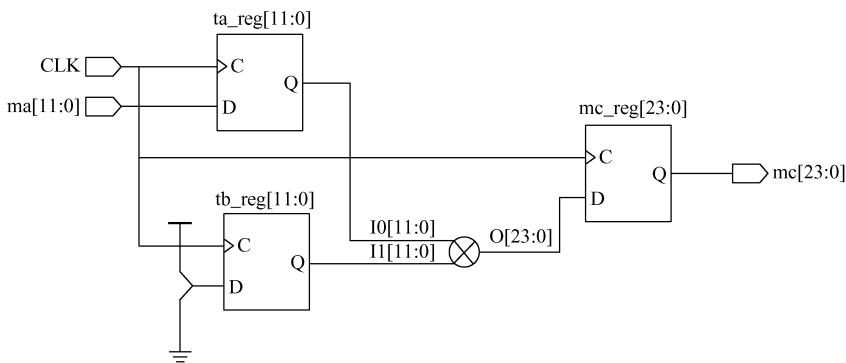

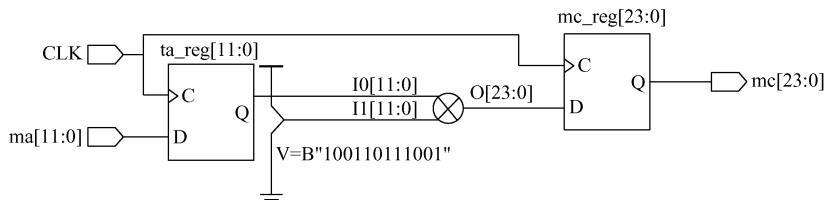

| 6.2.1 流水线设计 .....                | 138        |                            |     |

| 6.2.2 寄存器配平 .....                | 141        |                            |     |

| 6.2.3 关键路径法 .....                | 142        |                            |     |

| 6.2.4 兵兵操作法 .....                | 142        |                            |     |

| 6.2.5 加法树法 .....                 | 144        |                            |     |

| 6.3 硬件毛刺剔出 .....                 | 144        |                            |     |

| 6.3.1 延时方式 .....                 | 145        |                            |     |

| 6.3.2 逻辑方式去毛刺 .....              | 147        |                            |     |

| 6.3.3 定时方式去毛刺 .....              | 147        |                            |     |

| 本章小结 .....                       | 149        |                            |     |

| 习题 .....                         | 149        |                            |     |

|                                  |            |                            |     |

| <b>第7章 Vivado 集成设计环境导论 .....</b> | <b>150</b> |                            |     |

| 7.1 Vivado 设计套件 .....            | 150        |                            |     |

| 7.1.1 单一的、共享的、可扩展的<br>数据模型 ..... | 150        |                            |     |

| 7.1.2 标准化 XDC 约束文件 SDC .....     | 150        |                            |     |

| 7.1.3 多维度解析布局器 .....             | 151        |                            |     |

| 7.1.4 IP 封装器、集成器和目录 .....        | 151        |                            |     |

| 7.1.5 Vivado HLS .....           | 152        |                            |     |

| 7.1.6 Tcl 特性 .....               | 152        |                            |     |

| 7.2 Vivado 系统级设计流程 .....         | 153        |                            |     |

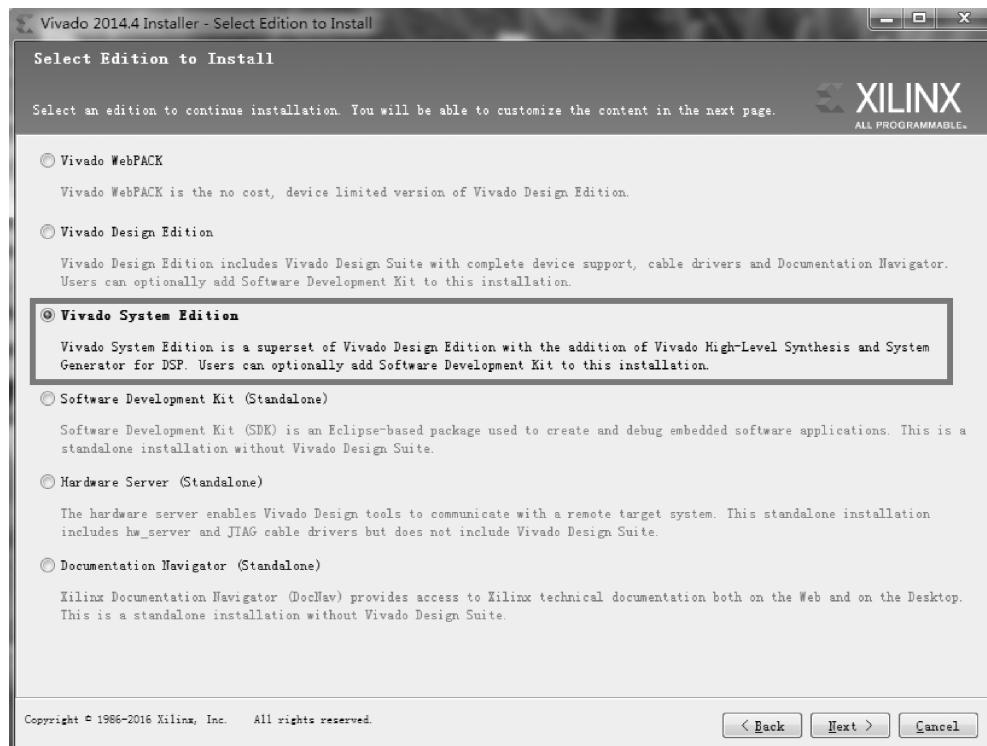

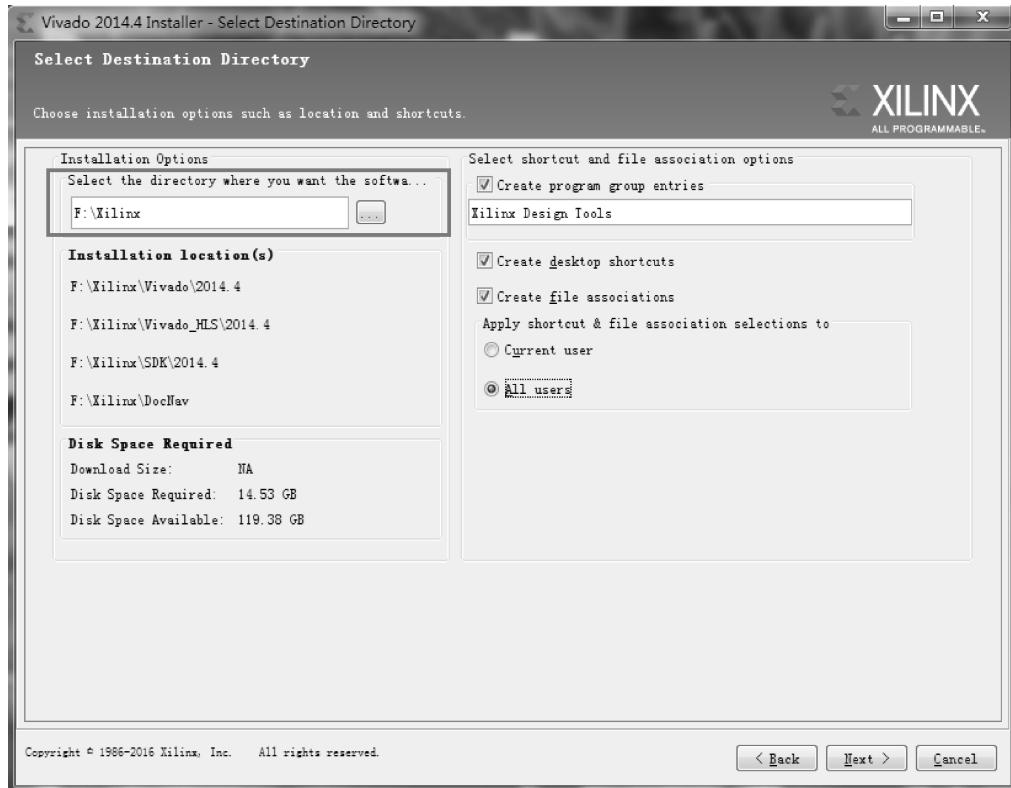

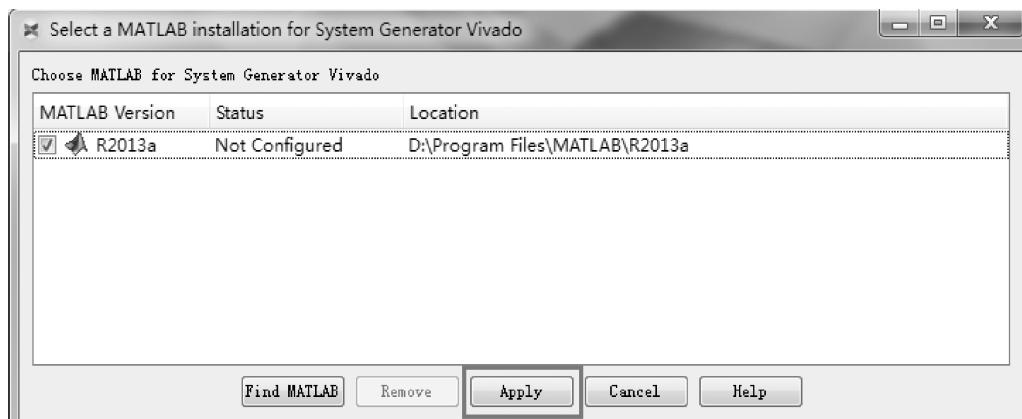

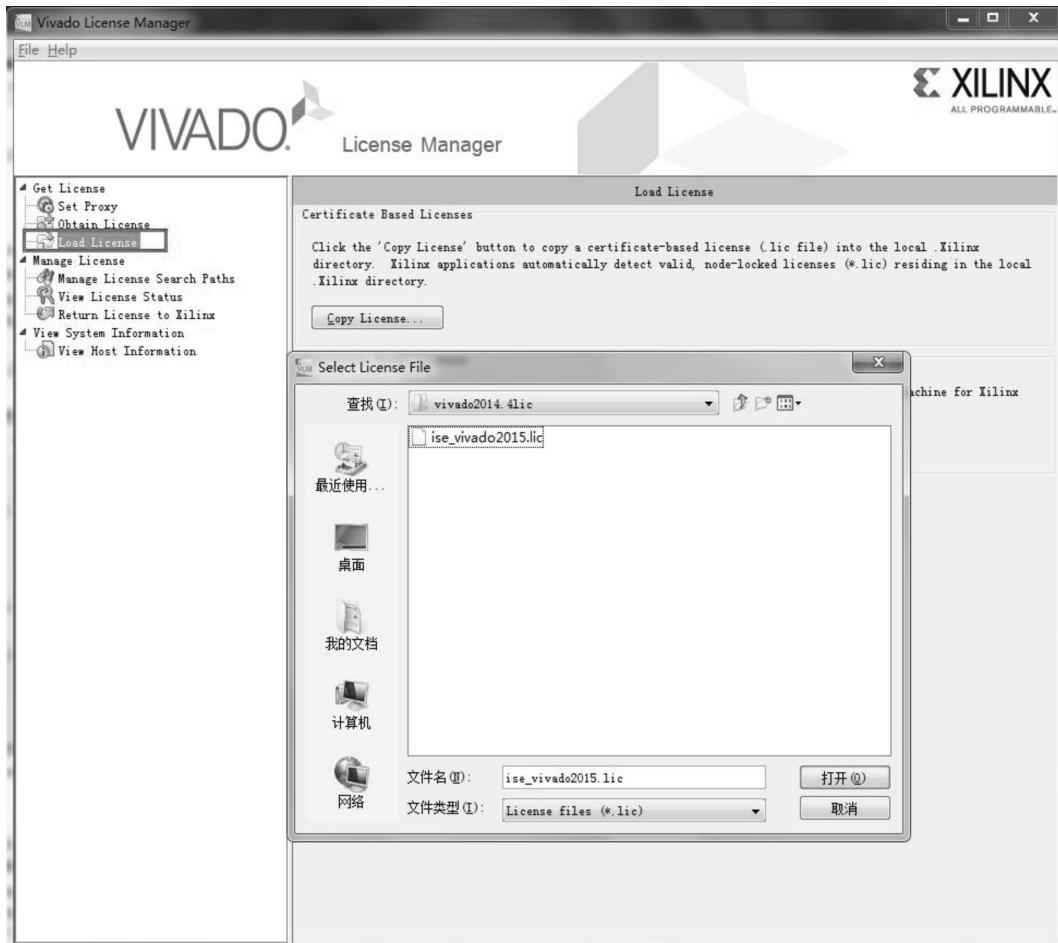

| 7.3 Vivado 设计套件的安装 .....         | 154        |                            |     |

|                                     |            |                            |     |

|-------------------------------------|------------|----------------------------|-----|

| 7.3.1 下载 .....                      | 154        | 10.7 创建实现约束 .....          | 211 |

| 7.3.2 安装 .....                      | 154        | 10.8 设计实现和分析 .....         | 213 |

| 7.4 Vivado 中工程数据的目录结构 .....         | 157        | 10.9 静态时序分析 .....          | 221 |

| 7.5 Vivado 网表文件 .....               | 158        | 10.10 设计时序仿真 .....         | 222 |

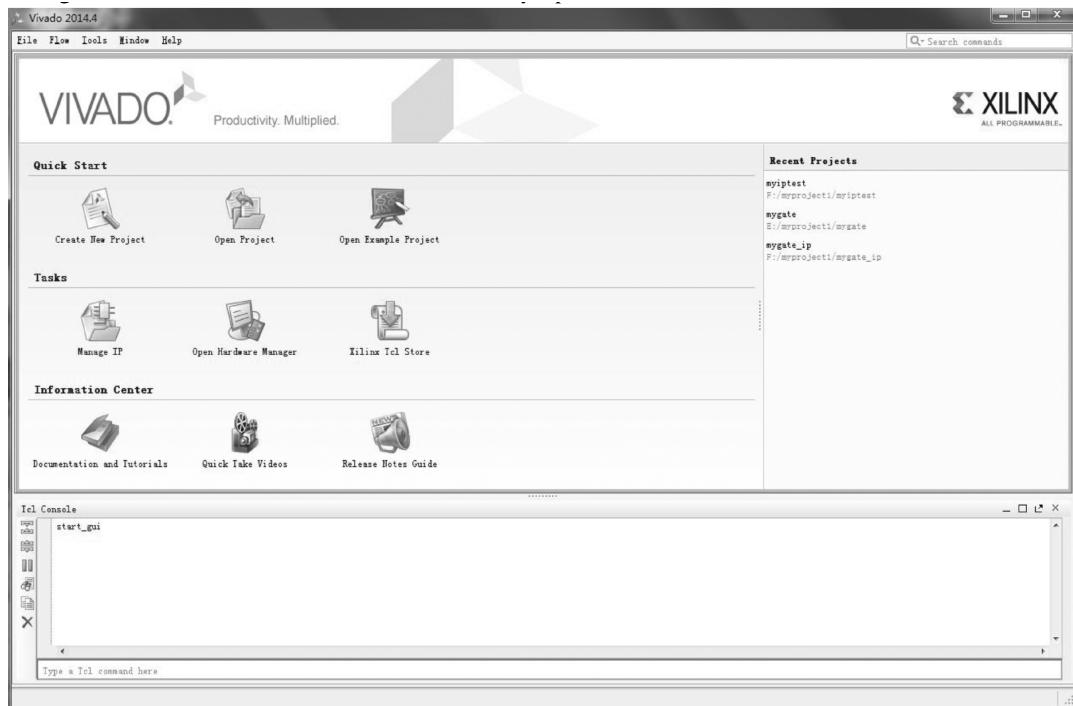

| 7.6 Vivado 集成设计环境主界面 .....          | 159        | 10.11 生成编程文件并下载到目标芯片 ..... | 222 |

| 7.6.1 “Quick Start” 分组 .....        | 159        | 本章小结 .....                 | 224 |

| 7.6.2 “Tasks” 分组 .....              | 160        | 习题 .....                   | 224 |

| 7.6.3 “Information Center” 分组 ..... | 160        |                            |     |

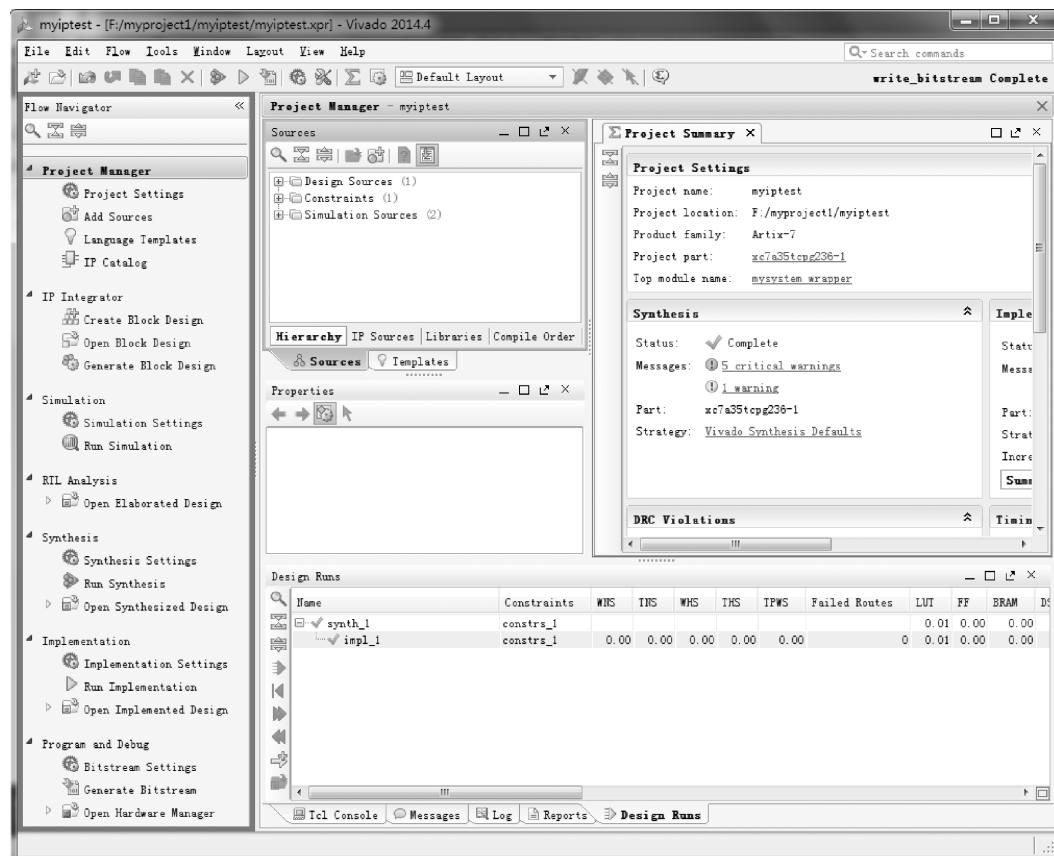

| 7.7 Vivado 设计主界面 .....              | 161        |                            |     |

| 7.7.1 流程处理主界面 .....                 | 161        |                            |     |

| 7.7.2 工程管理器主界面 .....                | 162        |                            |     |

| 7.7.3 工作区窗口 .....                   | 163        |                            |     |

| 7.7.4 设计运行窗口 .....                  | 163        |                            |     |

| 本章小结 .....                          | 165        |                            |     |

| <b>第 8 章 Vivado 工程模式下设计基础 .....</b> | <b>166</b> |                            |     |

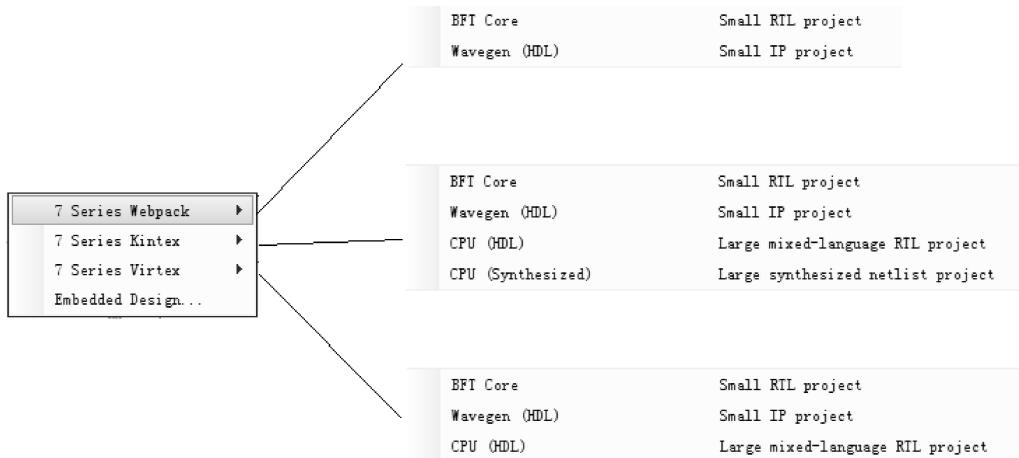

| 8.1 创建一个新的设计工程 .....                | 166        |                            |     |

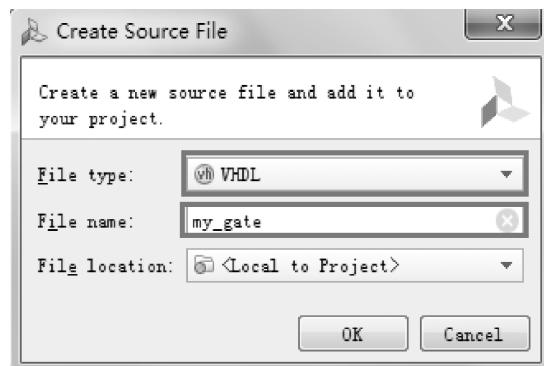

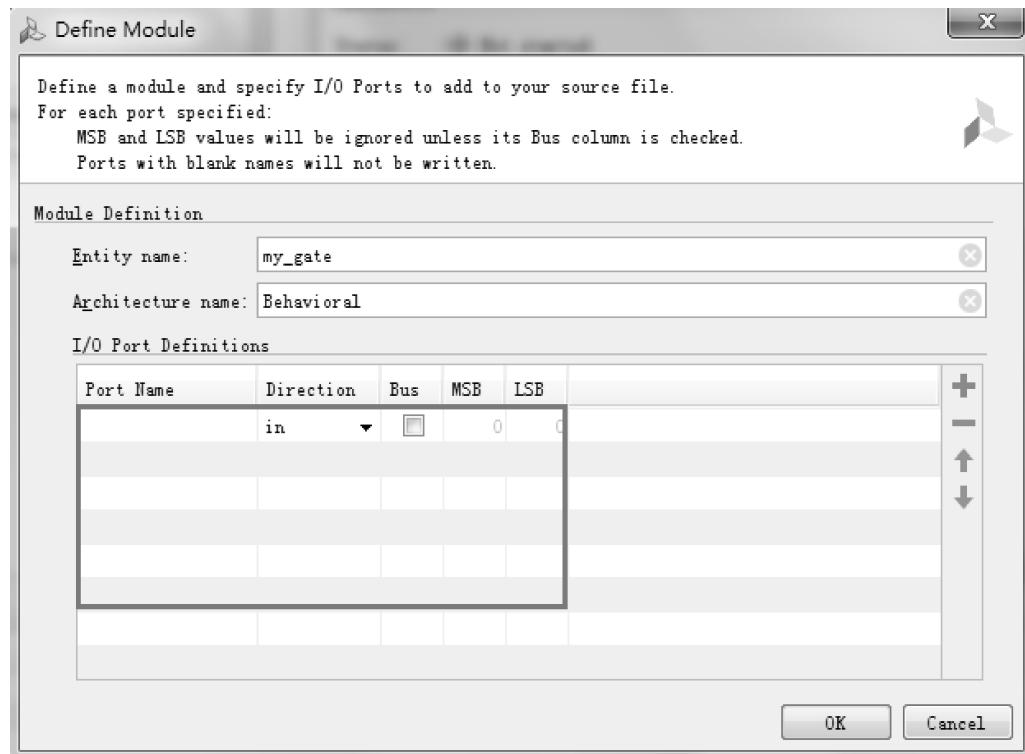

| 8.2 创建并添加新的设计文件 .....               | 169        |                            |     |

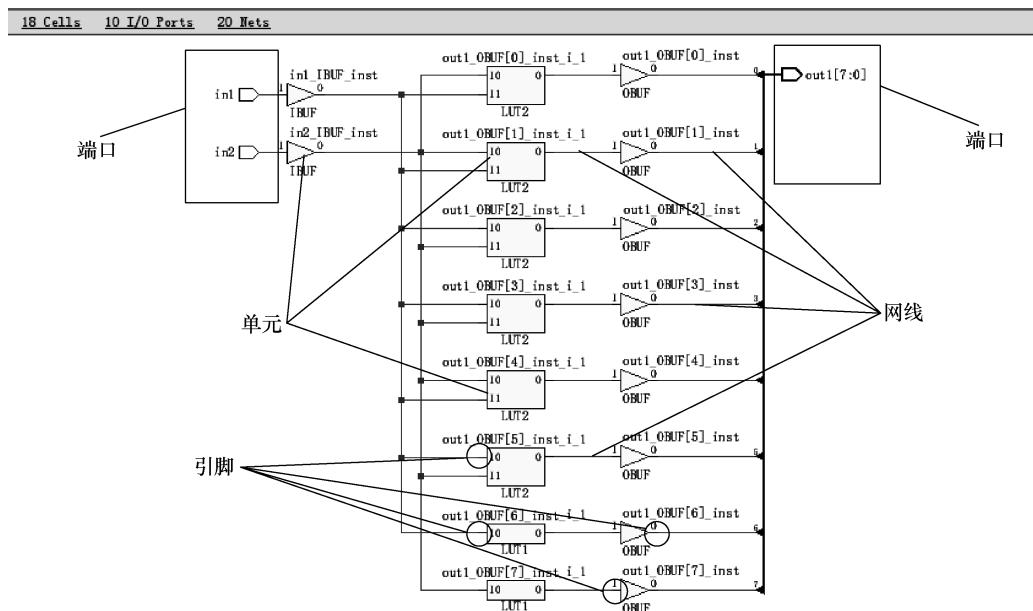

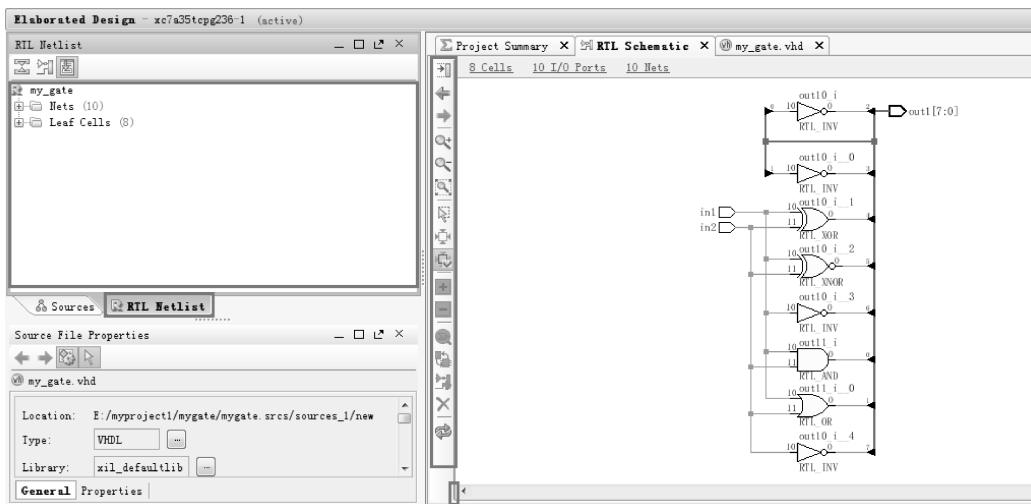

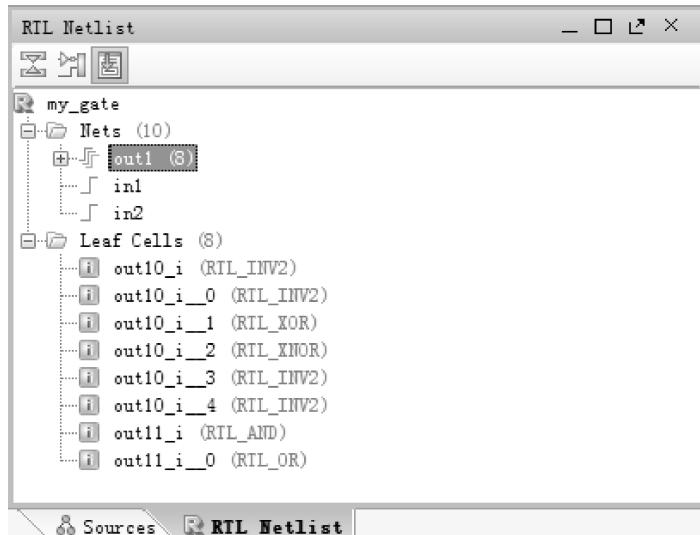

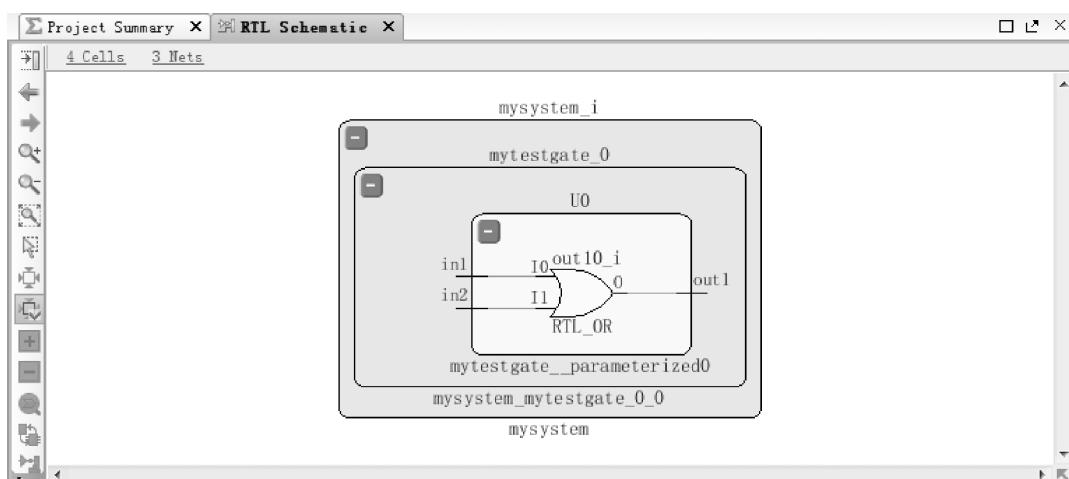

| 8.3 RTL 详细描述和分析 .....               | 172        |                            |     |

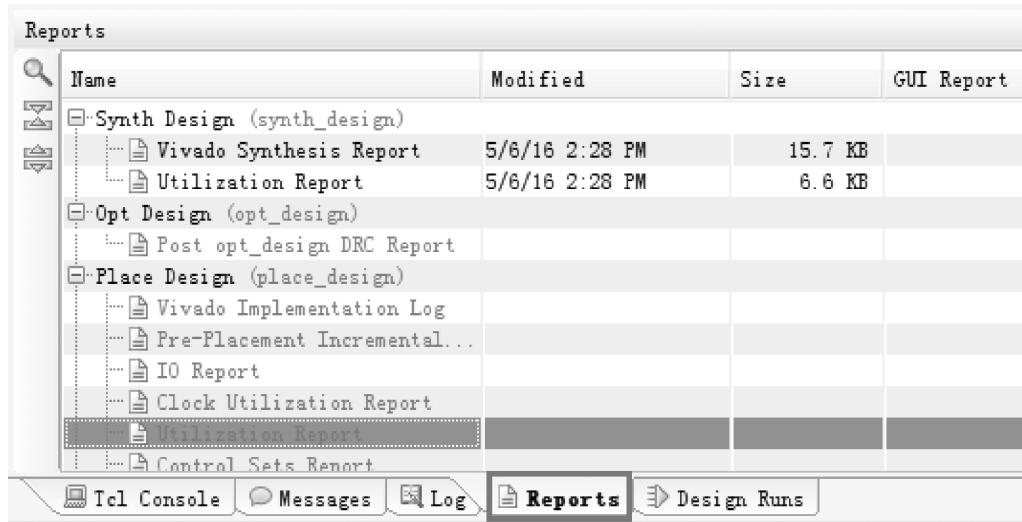

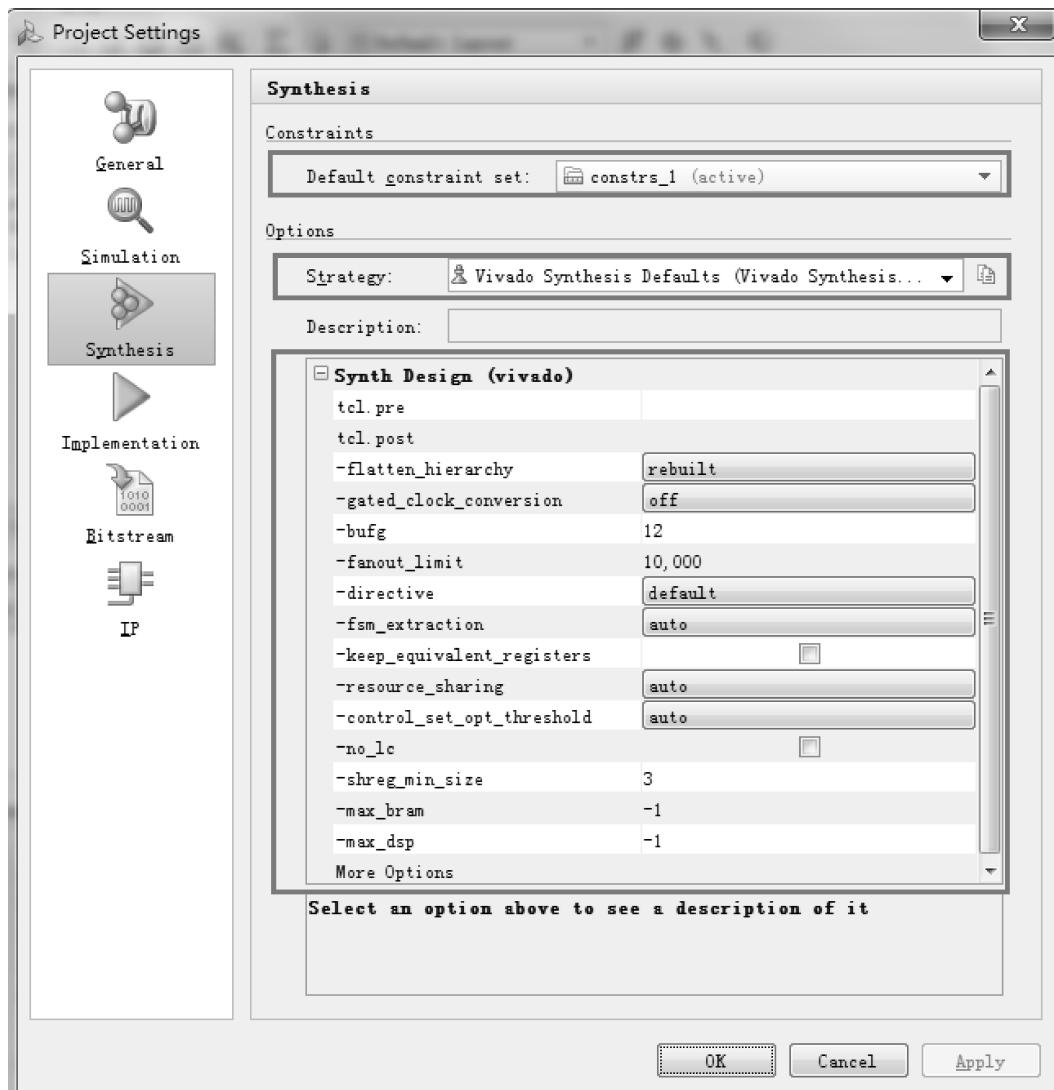

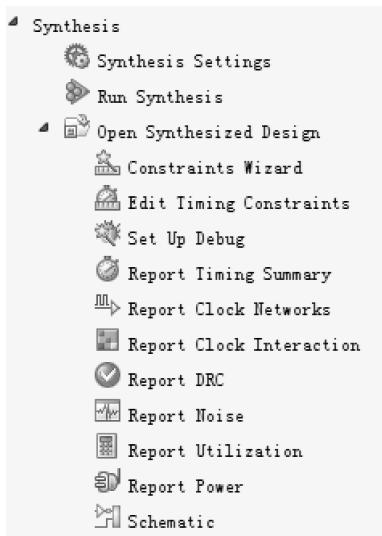

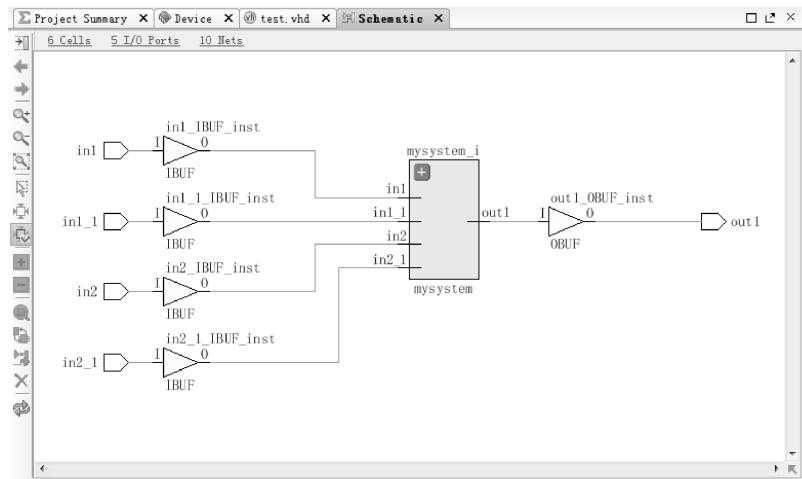

| 8.4 设计综合和分析 .....                   | 173        |                            |     |

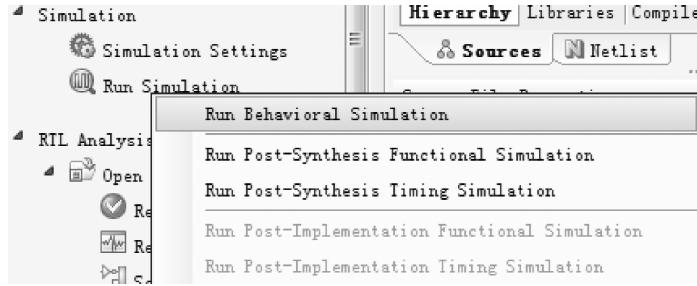

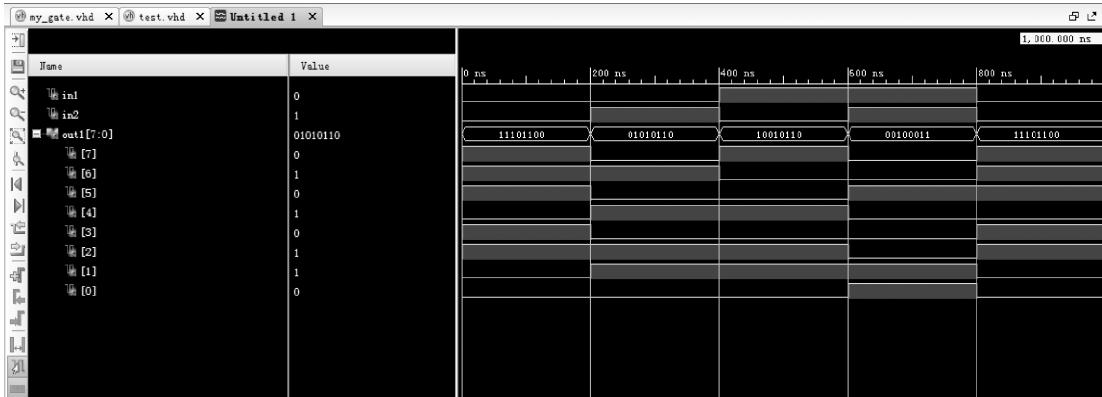

| 8.5 设计行为级仿真 .....                   | 176        |                            |     |

| 8.6 创建实现约束 .....                    | 178        |                            |     |

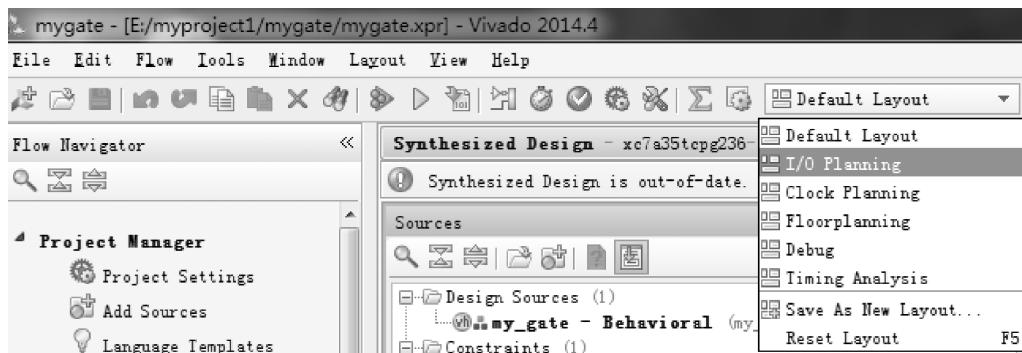

| 8.7 设计实现和分析 .....                   | 181        |                            |     |

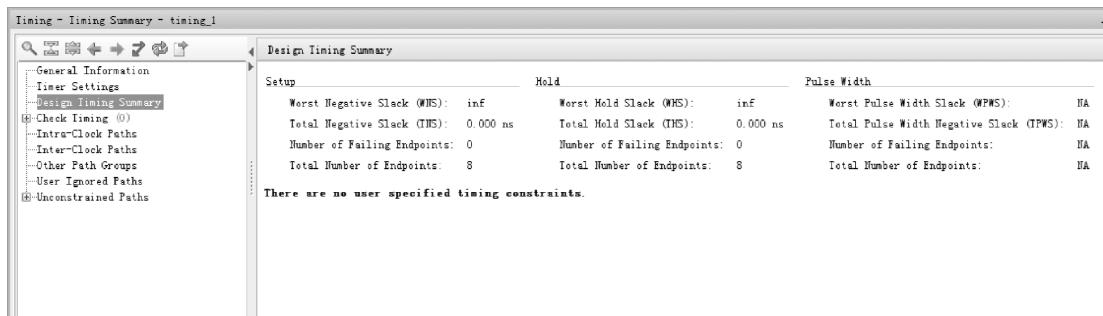

| 8.8 静态时序分析 .....                    | 182        |                            |     |

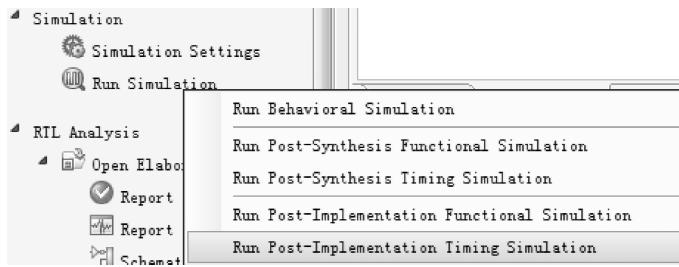

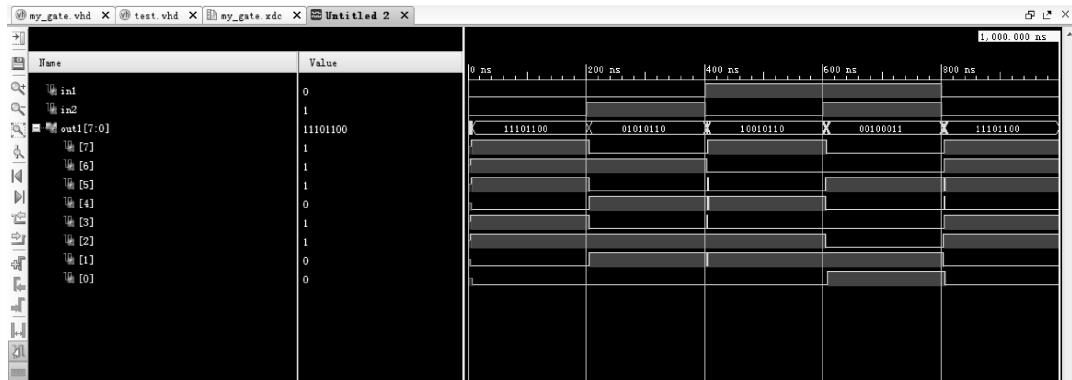

| 8.9 设计时序仿真 .....                    | 185        |                            |     |

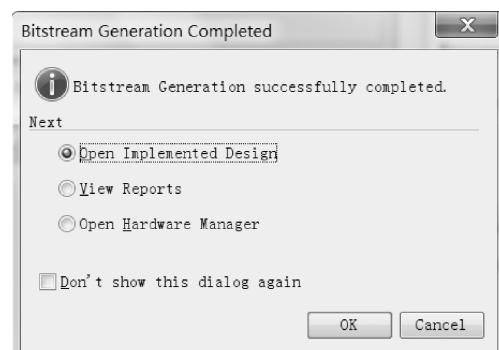

| 8.10 生成编程文件并下载到目标芯片 .....           | 185        |                            |     |

| 本章小结 .....                          | 188        |                            |     |

| 习题 .....                            | 189        |                            |     |

| <b>第 9 章 创建和封装用户 IP 核 .....</b>     | <b>190</b> |                            |     |

| 9.1 IP 核概述 .....                    | 190        |                            |     |

| 9.2 创建用于定制用户 IP 的工程 .....           | 191        |                            |     |

| 9.3 设置定制 IP 的库名和目录 .....            | 192        |                            |     |

| 9.4 封装定制 IP 的实现 .....               | 193        |                            |     |

| 本章小结 .....                          | 197        |                            |     |

| 习题 .....                            | 197        |                            |     |

| <b>第 10 章 数字电子系统的设计实现 .....</b>     | <b>198</b> |                            |     |

| 10.1 创建一个新的设计工程 .....               | 198        |                            |     |

| 10.2 设置调用 IP 的路径 .....              | 198        |                            |     |

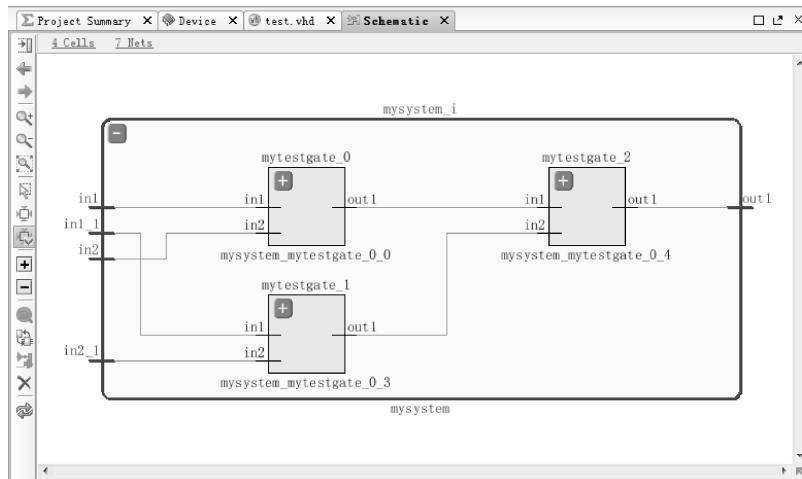

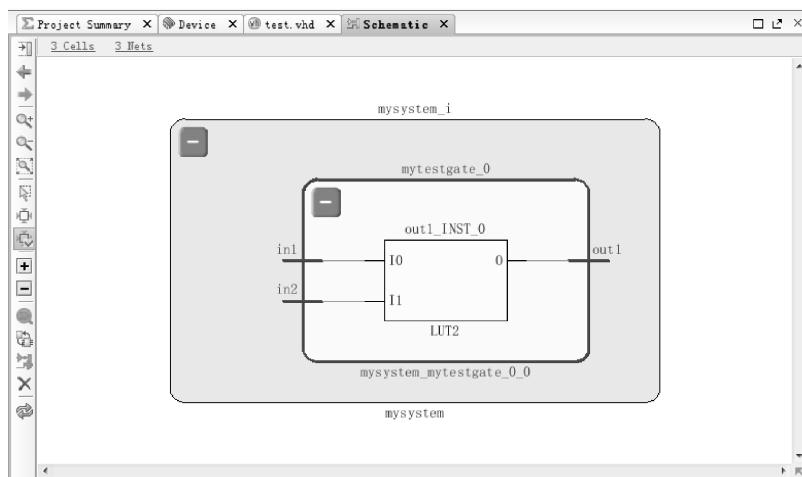

| 10.3 创建基于 IP 的系统 .....              | 199        |                            |     |

| 10.4 系统行为级仿真 .....                  | 203        |                            |     |

| 10.5 RTL 详细描述和分析 .....              | 205        |                            |     |

| 10.6 系统设计综合与分析 .....                | 207        |                            |     |

| 10.7 创建实现约束 .....                   | 211        |                            |     |

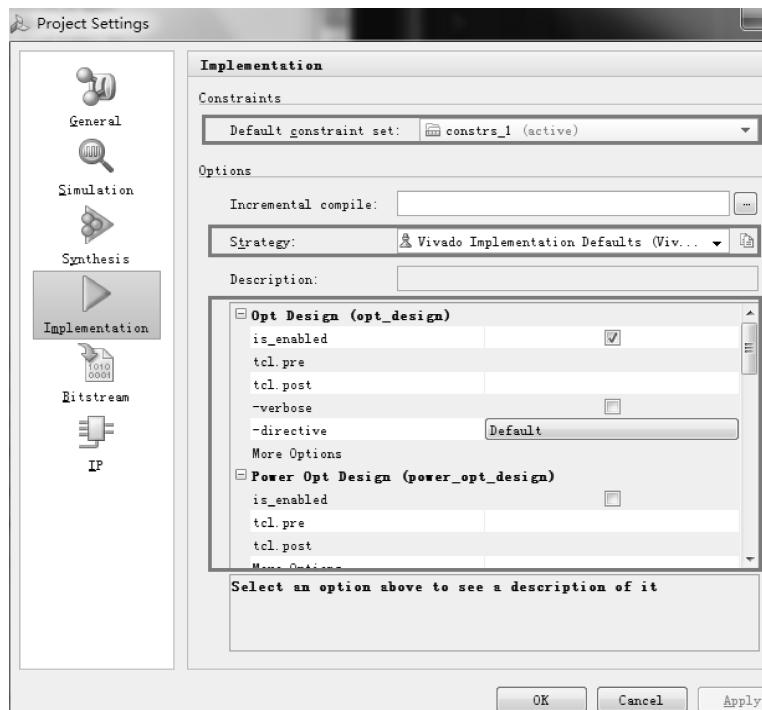

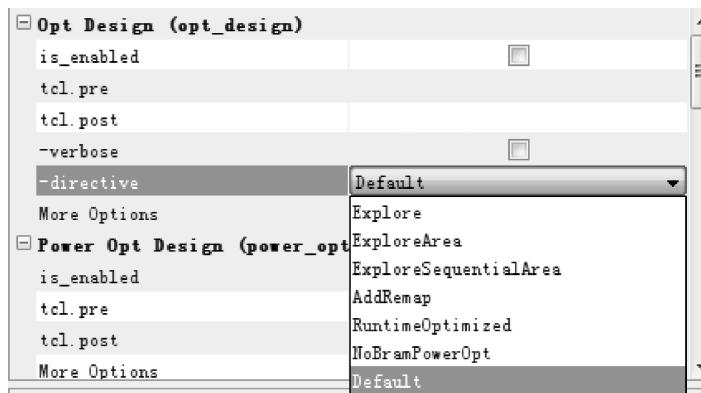

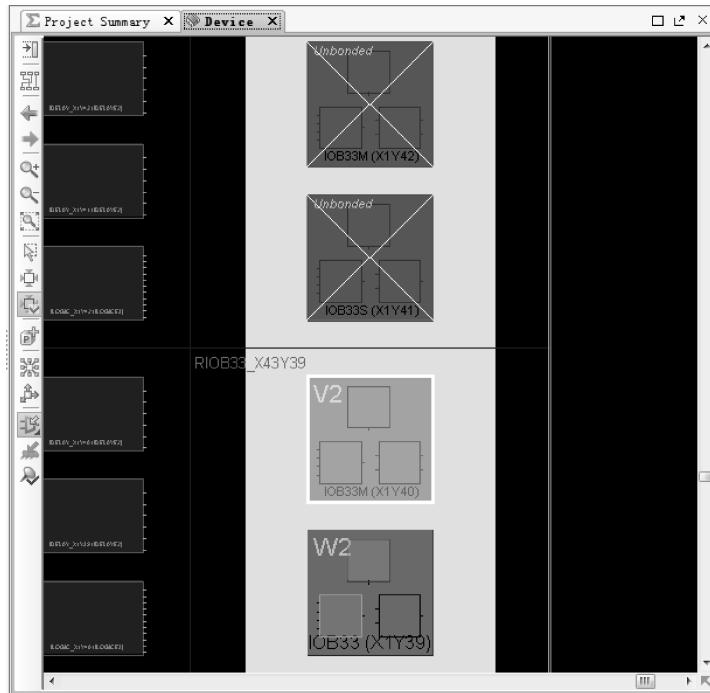

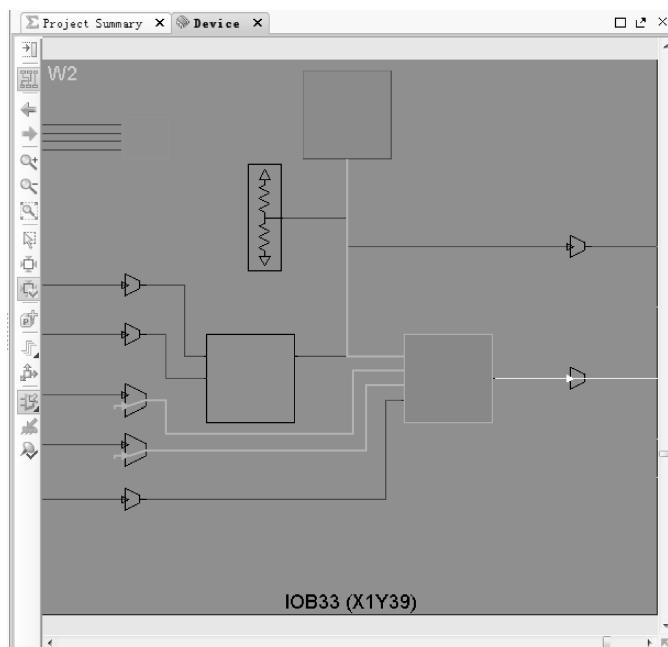

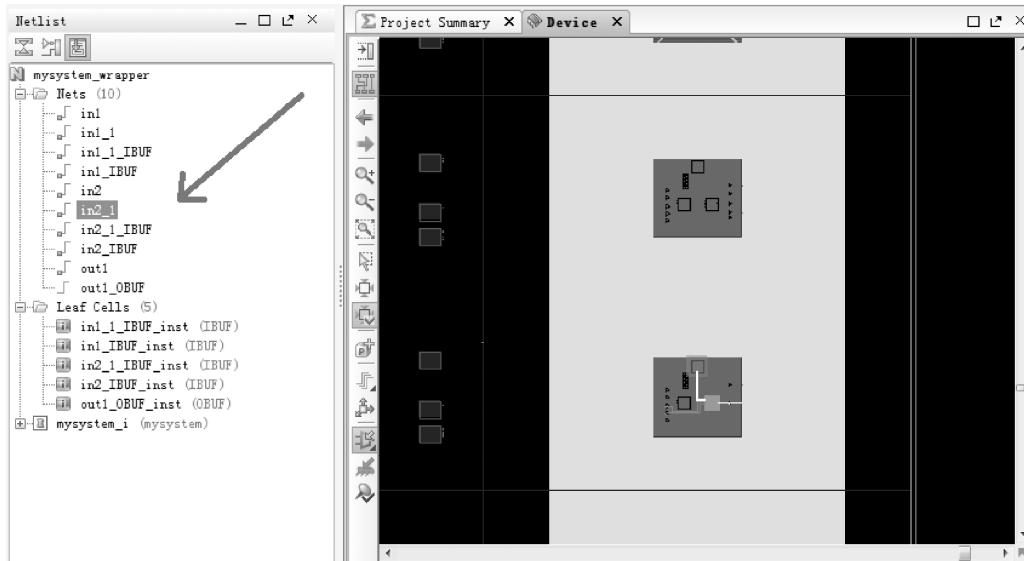

| 10.8 设计实现和分析 .....                  | 213        |                            |     |

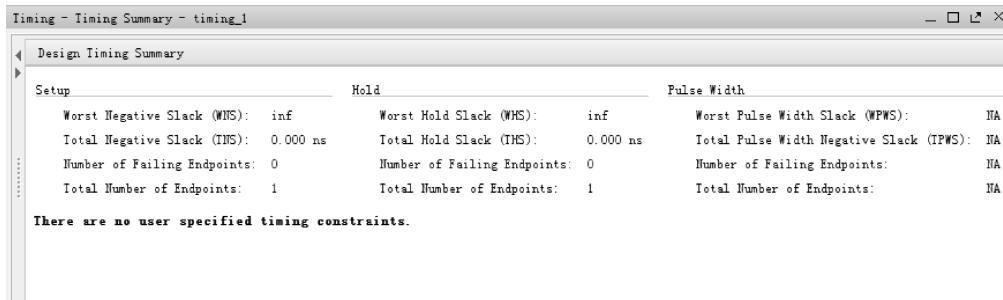

| 10.9 静态时序分析 .....                   | 221        |                            |     |

| 10.10 设计时序仿真 .....                  | 222        |                            |     |

| 10.11 生成编程文件并下载到目标芯片 .....          | 222        |                            |     |

| 本章小结 .....                          | 224        |                            |     |

| 习题 .....                            | 224        |                            |     |

| <b>第 11 章 键控流水灯实验设计 .....</b>       | <b>225</b> |                            |     |

| 11.1 设计要求 .....                     | 225        |                            |     |

| 11.2 功能描述 .....                     | 225        |                            |     |

| 11.3 键控流水灯的层次化设计方案 .....            | 225        |                            |     |

| 11.3.1 分频模块 .....                   | 226        |                            |     |

| 11.3.2 流水灯显示模块 .....                | 227        |                            |     |

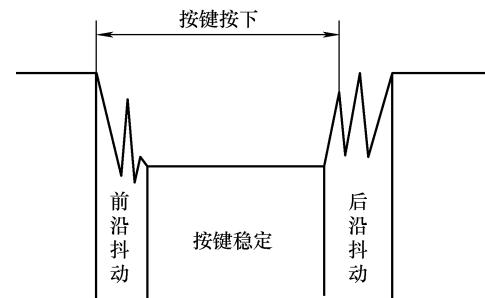

| 11.3.3 按键控制模块 .....                 | 229        |                            |     |

| 11.3.4 键控流水灯的设计 .....               | 232        |                            |     |

| 11.3.5 引脚约束 .....                   | 233        |                            |     |

| 11.3.6 硬件测试 .....                   | 235        |                            |     |

| 本章小结 .....                          | 235        |                            |     |

| <b>第 12 章 抢答器实验设计 .....</b>         | <b>236</b> |                            |     |

| 12.1 设计要求 .....                     | 236        |                            |     |

| 12.2 功能描述 .....                     | 236        |                            |     |

| 12.3 抢答器的层次化设计方案 .....              | 237        |                            |     |

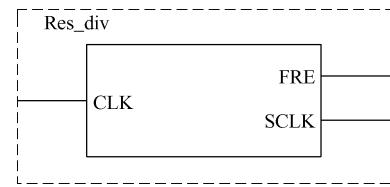

| 12.3.1 分频器模块 .....                  | 237        |                            |     |

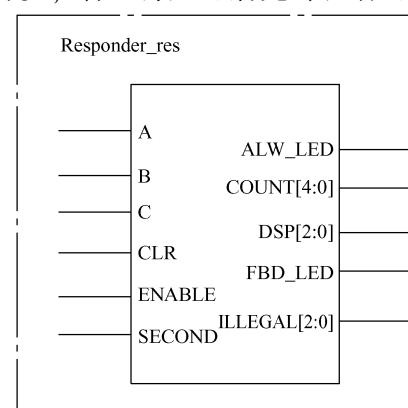

| 12.3.2 抢答鉴别器模块的设计 .....             | 239        |                            |     |

| 12.3.3 数码管显示模块的设计 .....             | 242        |                            |     |

| 12.3.4 抢答器的顶层设计 .....               | 244        |                            |     |

| 12.3.5 引脚约束 .....                   | 246        |                            |     |

| 12.3.6 硬件测试 .....                   | 248        |                            |     |

| 本章小结 .....                          | 248        |                            |     |

| <b>第 13 章 数字钟实验设计 .....</b>         | <b>249</b> |                            |     |

| 13.1 设计要求 .....                     | 249        |                            |     |

| 13.2 功能描述 .....                     | 249        |                            |     |

| 13.3 数字钟的层次化设计方案 .....              | 250        |                            |     |

| 13.3.1 分频器模块 .....                  | 250        |                            |     |

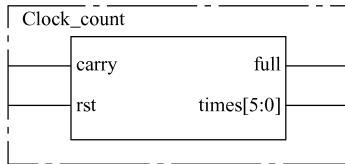

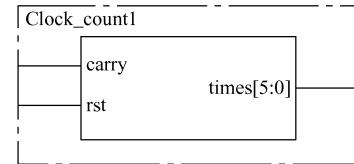

| 13.3.2 计数模块的设计 .....                | 251        |                            |     |

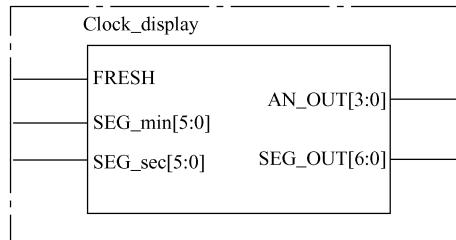

| 13.3.3 数码管显示模块的设计 .....             | 253        |                            |     |

| 13.3.4 数字钟的顶层设计 .....               | 256        |                            |     |

| 13.3.5 引脚约束 .....                   | 258        |                            |     |

| 13.3.6 硬件测试 .....                   | 259        |                            |     |

| 本章小结 .....                          | 259        |                            |     |

|                         |     |

|-------------------------|-----|

| <b>第 14 章 UART 实验设计</b> | 260 |

| 14.1 设计要求               | 260 |

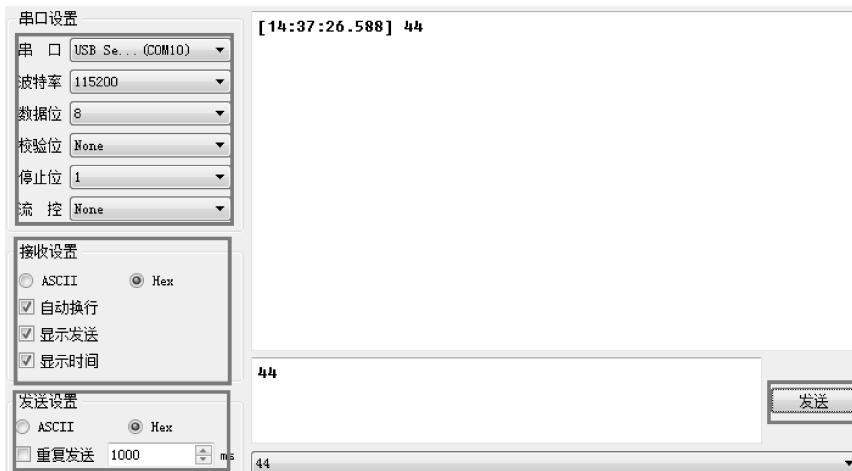

| 14.2 原理描述               | 260 |

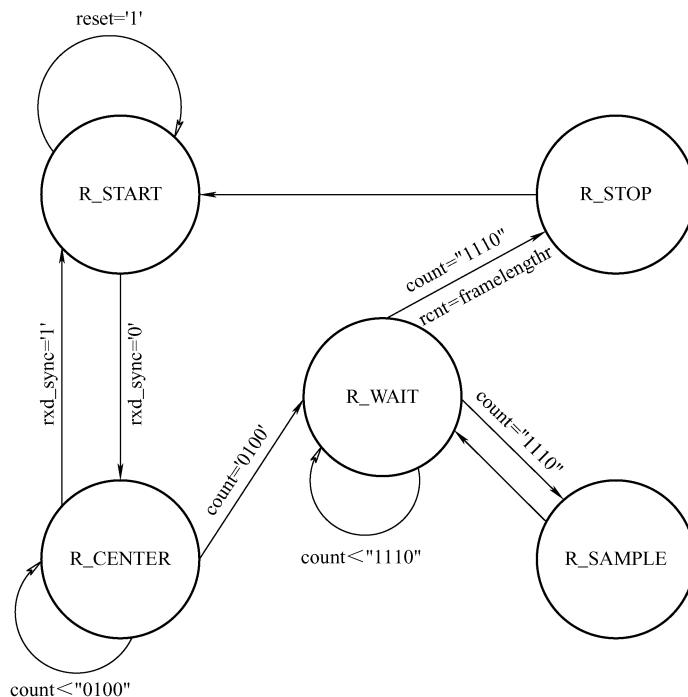

| 14.3 接收器的层次化设计方案        | 262 |

| 14.3.1 分频模块             | 263 |

| 14.3.2 接收器模块            | 264 |

| 14.3.3 接收器              | 268 |

| 14.3.4 引脚约束             | 269 |

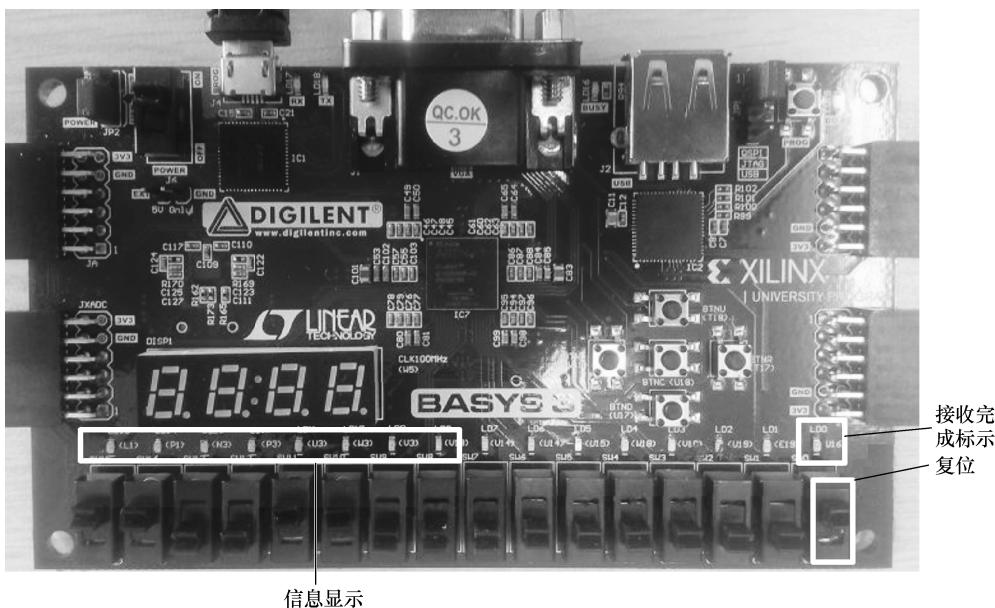

| 14.3.5 硬件测试             | 270 |

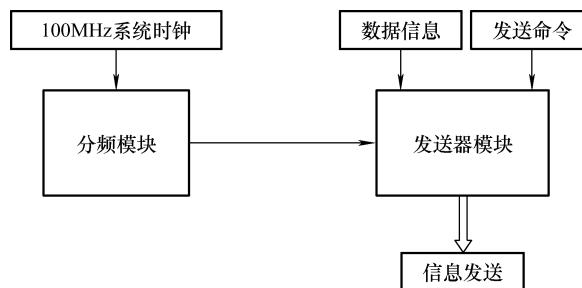

| 14.4 发送器的层次化设计方案        | 271 |

| 14.4.1 分频模块             | 272 |

| 14.4.2 发送器模块            | 272 |

| 14.4.3 发送器              | 276 |

| 14.4.4 引脚约束             | 277 |

| 14.4.5 硬件测试             | 278 |

| 本章小结                    | 279 |

| <b>参考文献</b>             | 280 |

# 第 1 章

## 绪 论

### 1.1 EDA 技术概要

#### 1.1.1 EDA 技术的含义

电子设计自动化（Electronics Design Automation, EDA）是一种以计算机为基础的工作平台，是利用电子技术、计算机技术、智能化技术等多种应用学科的最新成果进行电子产品设计的自动设计技术；是一种帮助电子设计工程师从事电子元件产品和系统设计的综合技术。

#### 1.1.2 EDA 技术的发展历程

在计算机技术的推动下，20世纪末电子技术获得了飞速发展，现代电子产品几乎渗透于社会的各个领域，有力地推动了社会生产力的发展和社会信息化程度的提高，同时又促使现代电子产品性能的进一步提高，产品更新换代的节奏也越来越快。

EDA 技术作为现代电子设计技术的核心，它依赖功能强大的计算机，在 EDA 工具软件平台上，对以硬件描述语言（Hardware Description Language, HDL）为系统逻辑描述手段完成的设计文件，自动地完成逻辑简化、逻辑分割、逻辑综合、结构综合（布局布线），以及逻辑优化和仿真测试等功能，直至实现既定性能的电子线路系统功能。EDA 技术使得设计者的工作几乎仅限于利用软件的方式，即利用硬件描述语言 HDL 和 EDA 软件来完成对系统硬件功能的实现。

在现代高新电子产品的设计和生产中，微电子技术和现代电子设计技术是相互促进、相互推动又相互制约的两个技术环节。前者代表了物理层在广度和深度上硬件电路实现的发展，后者则反映了现代先进的电子理论、电子技术、仿真技术、设计工艺和设计技术与最新的计算机软件技术有机的融合和升华。因此，可以说 EDA 技术是这两者的结合。

EDA 技术在硬件方面融合了大规模集成电路制造技术、IC 版图设计技术、ASIC 测试和封装技术、FPGA（Field Programmable Gate Array）和 CPLD（Complex Programmable Logic Device）编程下载技术、自动测试技术等；在计算机辅助技术工程方面融合了计算机辅助设计（CAD）、计算机辅助制造（CAM）、计算机辅助测试（CAT）、计算机辅助工程（CAE）技术以及多种计算机语言的设计概念；而在现代电子学方面则容纳了更多的内容，如电子线路设计理论、数字信号处理技术、嵌入式系统和计算机设计技术、数字系统建模和优化技术及微波技术等。因此 EDA 技术为现代电子理论和设计的表达与实现提供了可能性。在现代技术的所有领域中，许多得以飞速发展的科学技术，多属计算机辅助技术，而非自动化技

## 2 可编程逻辑器件与EDA技术

术。显然，最早进入真正的设计自动化技术领域非电子技术莫属，这就是电子技术始终处于所有科学技术发展的最前列的原因之一。

EDA 技术融合多学科于一体，渗透于各学科之中，已不是某一学科的分支或某种新的技术，而是一门综合性学科。它打破了软硬件间的壁垒，使计算机的软件技术与硬件实现、软件性能和硬件指标、设计效率和产品性能合二为一，它代表了电子设计技术和应用技术的发展方向。

EDA 技术的发展经历了一个由浅入深的过程。EDA 技术伴随着计算机、集成电路、电子系统设计的发展，经历了计算机辅助设计（CAD）、计算机辅助工程设计（CAE）和电子系统设计自动化（ESDA）三个发展阶段。

20 世纪 70 年代到 80 年代初为 CAD 阶段，也是 EDA 技术发展的初级阶段。随着中小规模集成电路的开发应用，传统的手工制图设计印制电路板和集成电路的方法已无法满足设计精度和效率的要求，因此工程师们开始进行二维平面图形的计算机辅助设计，以便解脱复杂、机械的版图设计工作，这就产生了第一代 EDA 工具。这一阶段由于受到计算机的运行速度、存储量和图形功能等方面的限制，电子 CAD 和 EDA 技术没有形成系统，仅是一些孤立的软件程序。这些软件程序在逻辑仿真、印制电路板布局布线和 IC 版图编辑等方面取代了计算机辅助设计的概念。但这些软件一般只有简单的人机交互能力，能处理的电路规模不是很大，计算和绘图的速度都受到限制，而且由于没有采用统一的数据库管理技术，程序之间的数据传输和交换也不方便。

20 世纪 80 年代中后期为 CAE 阶段，也是 EDA 技术发展的中级阶段。这一阶段计算机与集成电路技术得到了高速发展，CAD 软件主要用来实现模拟与数字电路仿真、集成电路的布线布局、IC 版图参数提取与验证、印制电路板的布图与检验、设计文档制作等各设计阶段的自动设计。将这些工具软件集成为一个有机的 EDA 系统，在工作站或超级微机上运行，它具有直观、友好的图形界面，可以用电路原理图的形式输入，以图形菜单的方式选择各种仿真工具和不同的规模功能。每个工具软件都有自己的元器件库，工具之间由统一的数据库进行数据存放、传输和管理。与初期的 CAD 相比，这一阶段的软件除了能进行纯粹的图形绘制功能外，又增加了电路功能设计和结构设计，并且通过电气连接网络表将两者结合在一起，以实现工程设计，这就是计算机辅助工程（CAE）的概念。

20 世纪 90 年代以后是设计自动化阶段，也是 EDA 技术发展的高级阶段。这个时期微电子技术以惊人的速度发展，一个芯片上可以集成几千万只晶体管，超高速数字集成电路的工作效率已经达到  $10\text{Gbit/s}$ ，射频集成电路的最高工作频率已超过  $6\text{GHz}$ ，电子系统朝着多功能、高速度、智能化的趋势发展。另一方面，随着集成度的提高，一个复杂的电子系统可以在一个集成电路芯片上实现，这就要求 EDA 系统能够从电子系统的功能和行为描述开始，综合设计出逻辑电路，并自动地映射成可供生产的 IC 版图，这一过程称为集成电路的高级设计。因此，20 世纪 90 年代后的 EDA 系统真正具有了自动化设计能力，EDA 技术被推向成熟和实用，用户只要给出电路的性能指标要求，EDA 系统就能对电路结构和参数进行自动化处理和综合，寻找最佳设计方案，通过自动布局布线功能将电路直接形成集成的电路版图，并对版图的面积及电路延时特性进行优化处理。

EDA 技术在进入 21 世纪后，得到了更大的发展，突出表现在以下几个方面：

(1) 使电子设计成果以自主知识产权（Intellectual Property, IP）的方式得以明确表达

和确认成为可能。系统芯片的设计思想有别于普通的 IC 设计，它是以 IP 核为基础，以硬件描述语言 HDL 为主要设计手段，借助于以计算机为平台的 EDA 工具而进行的。IP 的原来含义是知识产权、著作权等。在 IC 设计领域可将其理解为实现某种功能的设计。美国著名的 Dataquest 咨询公司则将半导体产业的 IP 定义为用于 ASIC 或 FPGA/CPLD 中的预先设计好的电路功能模块。

随着信息技术的飞速发展，用传统的手段来设计高复杂度的系统级芯片，设计周期将变得冗长，设计效率降低。解决这一设计危机的有效方法是复用以前的设计模块，即充分利用已有的或第三方的功能模块作为宏单元，进行系统集成，形成一个完整的系统，这就是集成电路设计复用的概念。这些已有的或由第三方提供的具有知识产权的模块（或内核）称为 IP 核，它在现代 EDA 技术和开发中具有十分重要的地位。

(2) 在仿真验证和设计两方面都支持标准硬件描述语言的功能强大的 EDA 软件不断推出。

(3) 电子技术全方位进入 EDA 时代。除了日益成熟的数字技术外，传统的电路系统设计建模理念发生了重大的改变：软件无线电技术的崛起；模拟电路系统硬件描述语言的表达和设计的标准化；系统可编程模拟器件的出现；软硬件技术；软硬件功能机器结构的进一步融合等。

(4) EDA 使得电子技术领域各学科的界限更加模糊，学科之间更加包容，如模拟与数字、软件与硬件、系统与器件、ASIC 与 FPGA 等。

(5) 更大规模的 FPGA 和 CPLD 器件的不断推出。

(6) 基于 EDA 工具的同于 ASIC 设计的标准单元已涵盖大规模电子系统及复杂 IP 核模块。

(7) 软硬件 IP 核在电子行业的产业领域、技术领域和设计应用领域得到了广泛的应用。

(8) SoC 高效低成本设计技术的成熟。

(9) 系统级、行为验证级硬件描述语言，如 SystemC、System Verilog 等的出现，使复杂电子系统的设计，特别是验证趋于更加高效和简单。

### 1.1.3 EDA 的基本特征

现代 EDA 技术的基本特征是采用高级语言描述，具有系统级仿真和综合能力、开放式的设计环境、丰富的元器件模型库等。EDA 技术就是依赖功能强大的计算机，在 EDA 工具软件的平台上，对以硬件描述语言 HDL 为系统逻辑描述手段完成的设计文件，自动完成逻辑编译、逻辑化简、逻辑分割、逻辑综合、布局布线和仿真测试，直至实现既定的电子线路系统功能。EDA 技术使得设计者的工作仅限于利用软件的方式，即利用硬件描述语言和 EDA 软件来完成对系统硬件功能的实现。

#### 1. 硬件描述语言设计输入

用硬件描述语言进行电路与系统的设计是当前 EDA 技术的一个重要特征，硬件描述语言输入是现代 EDA 系统的主要输入方式。统计资料表明，在硬件描述语言和原理图两种输入方式中，前者约占 70% 以上，并且这个趋势还在继续增长。与传统的原理图输入设计方法相比，硬件描述语言更适用于规模日益增大的电子系统，它还是进行逻辑综合优化的重要

工具。硬件描述语言使得设计者在比较抽象的层次上描述设计的结构和内部特征，其突出优点是：语言的公开可利用性；设计与工艺的无关性；宽范围的描述能力；便于组织大规模系统的设计；便于设计的复用和继承等。

## 2. “自顶向下”设计方法

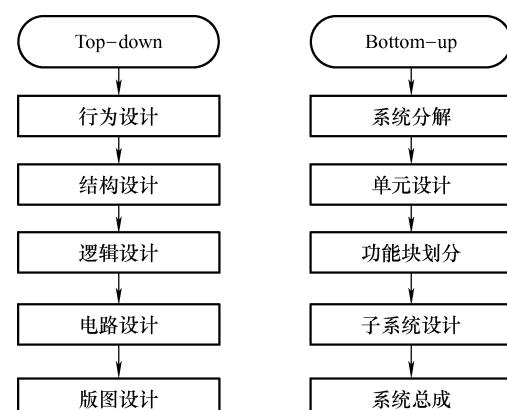

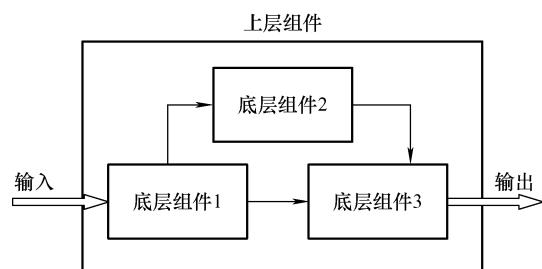

近10年来，电子系统的设计方法发生了很大的变化。过去，电子产品设计的基本思路一直是先选用标准通用集成电路芯片，再用这些芯片和其他元器件自上而下地构成电路、子系统和系统。这样设计出的电子系统所用元器件的种类和数量均较多、体积功耗大、可靠性差。随着集成电路技术的不断进步，半导体集成电路也由早期的单元集成、部件电路集成，发展到整机电路集成和系统电路集成。电子系统的设计方法也由过去的集成电路厂家提供芯片，整机系统用户采用这些芯片组成电子系统的自底向上（Bottom-up）设计方法改变为一种新的自顶向下（Top-down）设计方法。在这种新的设计方法中，由整机系统用户对整个系统进行方案设计和功能划分，系统的关键电路用一片或几片专用集成电路来实现，而且这些专用集成电路是由系统和电路设计师亲自参与设计的，直至完成电路到芯片版图的设计，再交由IC工厂投片加工，或者用可编程ASIC（CPLD和FPGA）现场编程实现。如图1.1所示为电子系统两种不同的设计步骤。

“自顶向下”法是一种概念驱动的设计方法。该方法要求在整个设计过程中尽量运用概念（即抽象）去描述和分析设计对象，而不要过早地考虑实现该设计具体电路、元器件和工艺，以便抓住主要矛盾，避免纠缠在具体细节上，这样才能控制住设计的复杂性。整个设计在概念上的演化从顶层到底层应当逐步由概括到展开，由粗略到精细。只有当整个设计在概念上得到验证与优化后，才能考虑具体问题。

在进行“自顶向下”的设计时，首先从系统级设计入手，在顶层进行功能框图的划分和结构设计；在框图一级进行仿真、纠错，并用硬件描述语言对高层次的系统行为进行描述；在功能一级进行验证，然后用逻辑综合优化工具生成具体的门级逻辑电路的网表，其对应的物理实现级可以是印制电路板或专用集成电路。而“自底向上”的设计方法一般是在系统划分和分解的基础上先进行单元设计，在单元的精心设计后逐步向上进行功能块设计，然后进行子系统的设计，最后完成系统的总体设计。“自顶向下”的设计方法有利于在早期发现结构设计中的错误，提高设计的一次成功率，因而在现代EDA系统中被广泛采用。

## 3. 逻辑综合与优化

逻辑综合是20世纪90年代电子学领域兴起的一种新的设计方法，是以系统级设计为核心的高层次设计。逻辑综合是将最新的算法与工程界多年积累的设计经验结合起来，自动地将用真值表、状态图或VHDL硬件描述语言等所描述的数字系统转化为满足设计性能指标要求的逻辑电路，并对电路进行速度、面积等方面的优化。

逻辑综合的作用是根据一个系统的逻辑功能与性能要求，在一个包含众多结构、功能和

图1.1 “自顶向下”与“自底向上”设计

性能均已知的逻辑元器件的逻辑单元库的支持下，寻找出一个逻辑网络结构最佳的实现方案。

逻辑综合的过程主要包含以下两个方面。

(1) 逻辑结构的生成与优化：主要是进行逻辑简化与优化，达到尽可能地用较少的元器件和连线形成一个逻辑网络结构（逻辑图），满足系统逻辑功能的要求。

(2) 逻辑网络的性能优化：利用给定的逻辑单元库，对已生成的逻辑网络进行元器件配置，进而估算实现该逻辑网络的芯片的性能与成本。性能主要指芯片的速度，成本主要指芯片的面积与功耗。速度与面积或速度与功耗是矛盾的。这里有一步，允许使用者对速度与面积或速度与功耗相矛盾的指标进行性能与成本的折中，以确定合适的元器件配置，完成最终的、符合要求的逻辑网络结构。

#### 4. 开放性和标准化

开放式的设计环境也称为框架结构（Framework）。框架是一种软件平台结构，它在EDA系统中负责协调设计过程和管理设计数据，实现数据与工具的双向流动，为EDA工具提供合适的操作环境。框架结构的核心是可以提供与硬件平台无关的图形用户界面，工具之间的通信、设计数据和设计流程的管理等，以及各种与数据库相关的服务项目。

任何一个EDA系统只要建立一个符合标准的开放式框架结构，就可以接纳其他厂家的EDA工具一起进行设计工作。框架结构的出现，使国际上许多优秀的EDA工具可以合并到一个统一的计算机平台上，成为一个完整的EDA系统，充分发挥每个设计工具的技术优势，实现资源共享。在这种环境下，设计者可以更有效地运用各种工具，提高设计质量和效率。

近年来，随着硬件描述语言等设计数据格式的逐步标准化，不同设计风格和应用的要求导致各具特色的EDA工具被集成在同一个工作站上，从而使EDA框架标准化。新的EDA系统不仅能够实现高层次的自动逻辑综合、版图综合和测试码生成，而且可以使各个仿真器对同一个设计进行协同仿真，从而进一步提高EDA系统的工作效率和设计的正确性。

#### 5. 库

EDA工具必须配有丰富的库，包括元器件图形符号库、元器件模型库、工艺参数库、标准单元库、可复用的电路模块库、IP库等，才能够具有强大的设计能力和较高的设计效率。

在电路设计的每个阶段，EDA系统需要各种不同层次、不同种类的元器件模型库的支持。例如：原理图输入时需要元器件外形库；逻辑仿真时需要逻辑单元的功能模型库；电路仿真时需要模拟单元和器件的模型库；版图生成时需要使用不同层次和不同工艺的底层版图库；测试综合时需要各种测试向量库等。每一种库又分为不同层次的单元或元素库，例如，逻辑仿真的库又按照行为级、寄存器级和门级分别设库。而VHDL输入所需的库更为庞大和齐全，几乎包含了上述所有库的内容。各种模拟库的规模和功能是衡量EDA工具优劣的一个重要标识。

### 1.1.4 EDA技术的优势

传统的数字电子系统或IC设计中，手工设计占了较大的比例。手工设计一般先按电子系统的具体功能要求进行功能划分，然后对每个子模块画出真值表，用卡诺图进行手工逻辑

简化，写出布尔表达式，画出相应的逻辑线路图，再据此选择元器件和设计电路板，最后进行实测与调试。手工设计方法的缺点包括：

- (1) 复杂电路的设计和调试都十分困难。

- (2) 由于无法进行硬件系统仿真，如果某一过程存在错误，则查找和修改都十分困难。

- (3) 设计过程中产生大量文档，不易管理。

- (4) 对于 IC 设计而言，设计实现过程与具体生产工艺直接相关，因此可移植性差。

- (5) 只有在设计出样机或生产出芯片后才能进行实测。

相比之下，采用 EDA 技术进行电子系统的设计有很大的优势。

(1) 用 HDL 对数字系统进行抽象的行为与功能描述以及具体的内容线路结构描述，从而可以在电子设计的各个阶段、各个层次进行计算机模拟验证，保证设计过程的正确性，可以大大地降低设计成本、缩短设计周期。

(2) EDA 工具之所以能够完成各种自动设计过程，关键是有各类库的支持，如逻辑仿真时的模拟库、逻辑综合时的综合库、版图综合时的版图库、测试综合时的测试库等。这些库都是 EDA 公司与半导体生产厂商紧密合作、共同开发的。

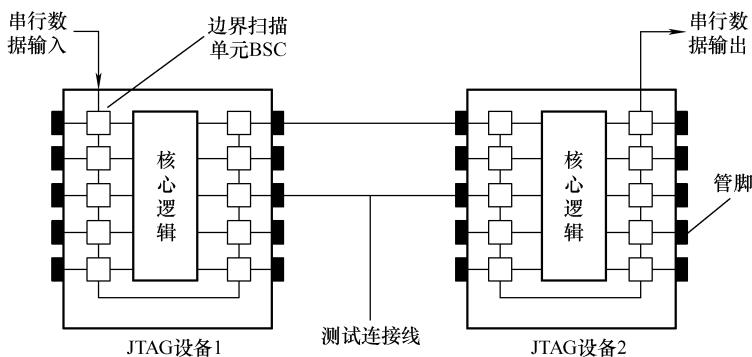

- (3) 某些 HDL 也是文档型的语言（如 VHDL），极大地简化了设计文档的管理。

(4) EDA 技术中最为瞩目的功能，即最具现代电子设计技术特征的功能是日益强大的逻辑设计仿真测试技术。EDA 仿真测试技术只需通过计算机就能对所设计的电子系统从各种不同层次的系统性能特点完成一系列准确的测试与仿真操作，在完成实际系统的安装后，还能对系统上的目标器件进行逻辑边界扫描测试。这一切都极大地提高了大规模系统电子设计的自动化程度。

(5) 无论传统的应用电子系统设计得如何完美，使用了多么先进的功能器件，都掩盖不了一个无情的事实，即该系统对于设计者来说，没有任何自主知识产权可言，因为系统中的关键性器件往往并非出自设计者之手，这将导致该系统在许多情况下的应用直接受到限制。基于 EDA 技术的设计则不同，由于 HDL 表达成功的专用功能设计在实现目标方面有很大的可选性，它既可以用不同来源的通用 FPGA/CPLD 实现，也可以直接以 ASIC 来实现，设计者拥有完全的自主权。

(6) 传统的电子设计方法至今没有任何标准规范加以约束，因此，设计效率低、系统性能差、开发成本高、市场竞争小。而 EDA 技术的设计语言是标准化的，不会由于设计对象的不同而改变；它的开发工具是规范化的，EDA 软件平台支持任何标准化的设计语言；它的设计成果是通用性的，IP 核具有规范的接口协议。良好的可移植与可测试性为系统开发提供了可靠的保证。

(7) 从电子设计方法学来看，EDA 技术最大的优势就是能将所有设计环节纳入统一的自顶向下的设计方案中。

(8) EDA 不但在整个设计流程上充分利用计算机的自动设计能力、在各个设计层次上利用计算机完成不同内容的仿真模拟，而且在系统板设计结束后仍可利用计算机对硬件系统进行完整全面的测试。而传统的设计方法，如单片机仿真器，只能在最后完成的系统上进行局部的且仅限于软件的仿真调试，而在整个设计的过程是无能为力的。至于硬件系统测试，由于现在的许多系统主板层数多，而且许多器件是 BGA (Ball - Grid Array) 封装，所有引脚都在芯片的内部，焊接后普通的仪器仪表无法接触到所需的信号点，因此无法测试。

## 1.2 EDA 技术的实现目标

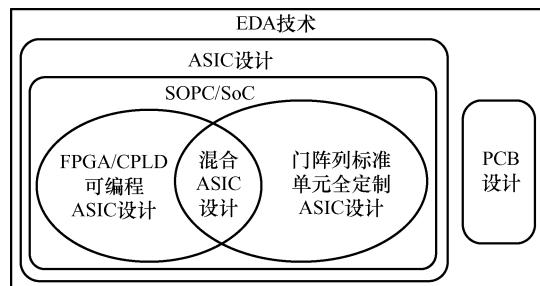

一般地，利用 EDA 技术进行电子系统设计，最后的目标是完成专用集成电路（ASIC）或印制电路板（PCB）的设计与实现。其中 PCB 设计指的是电子系统的印制电路板设计，从电路原理图到 PCB 上元件的布局、布线、阻抗匹配、信号完整性分析及板级仿真，到最后的电路板机械加工文件生成，这些都需要相应的计算机 EDA 工具软件辅助设计者来完成，这是早期 EDA 技术最基本的应用。ASIC 作为最终的物理平台，集中容纳了用户通过 EDA 技术将电子应用系统的既定功能和技术具体实现的硬件实体。一般而言，专用集成电路就是具有专门用途和特定功能的独立集成电路器件。根据这个定义，作为 EDA 技术最终实现目标的 ASIC，可以通过三种途径完成，如图 1.2 所示。

图 1.2 EDA 技术实现目标

### 1. 超大规模可编程逻辑器件

FPGA 和 CPLD 是实现这一途径的主流器件，其特点是直接面向用户、具有极大的灵活性和通用性、使用方便、硬件测试和实现快捷、开发效率高、成本低、技术维护简单、工作可靠性高等。FPGA 和 CPLD 的应用是 EDA 技术有机融合软硬件电子设计技术、SoC 和 ASIC 设计，以及对自动化设计与自动实现最经典的诠释。由于 FPGA 和 CPLD 的开发工具、开发流程和使用方法与 ASIC 有类似之处，因此这类器件通常也被称为可编程专用 IC 或可编程 ASIC。

### 2. 半定制或全定制 ASIC

基于 EDA 设计技术的半定制或全定制 ASIC，根据其实现工艺，可统称为掩膜 ASIC，或直接称 ASIC。可编程 ASIC 与掩膜 ASIC 相比，不同之处在于前者具有面向用户的灵活多样的可编程性。

掩膜 ASIC 大致分为门阵列 ASIC、标准单元 ASIC 和全定制 ASIC。

(1) 门阵列 ASIC 门阵列芯片包括预定制的相连的 PMOS 和 NMOS 晶体管行。设计中，用户可以借助 EDA 工具将原理图或硬件描述语言模型映射为相应门阵列晶体管配置，创建一个指定金属互联路径文件，从而完成门阵列 ASIC 的开发。由于有掩膜的创建过程，门阵列有时也称掩膜可编程逻辑门阵列（MPGA）。但是 MPGA 本身与 FPGA 完全不同，它不是用户可编程的，也不属于可编程逻辑范畴，而是实际的 ASIC。MPGA 出现在 FPGA 之前，FPGA 技术源自 MPGA。

(2) 标准单元 ASIC 目前大部分 ASIC 是使用库中不同大小的标准单元设计的，这类芯片一般称作基于单元的集成电路（CBIC）。在设计者一级，库包括不同复杂性的逻辑元件：SSI 逻辑块、MSI 逻辑块、数据通道模块、储存器、IP 乃至系统级模块。库包含每个逻辑单元在硅片级的完整布局，使用者只需利用 EDA 软件工具与逻辑块描述打交道即可，完全不必关心深层次电路布局的细节。标准单元布局中，所有扩散、接触点、过孔、多晶通道及金属通道都已完全确定。当该单元用于设计时，通过 EDA 软件产生的网表文件将单元布局块

“粘贴”到芯片布局之上的单元行上。标准单元 ASIC 设计与 FPGA 设计的开发流程相近。

(3) 全定制芯片 全定制芯片中，在针对特定工艺建立的设计规则下，设计者对于电路的设计有完全的控制权，如线的间隔和晶体管大小的确定。该领域的一个例外是混合信号设计，使用通信电路的 ASIC 可以定制设计其模拟部分。

### 3. 混合 ASIC

混合 ASIC (不是指数模混合 ASIC) 主要指既具有面向用户的 FPGA 可编程功能和逻辑资源，同时也含有可方便调用和配置的硬件标准单元模块，如 CPU、RAM、ROM、硬件加法器、乘法器、锁相环等。

## 1.3 硬件描述语言

硬件描述语言 (HDL) 就是可以描述硬件电路的功能、信号连接关系及定时 (时序) 关系的语言，也是一种用形式化方法来描述数字电路和设计数字系统的语言。数字系统的设计者可以利用这种语言来描述自己的设计思想，然后利用 EDA 工具进行仿真，自动综合到门级电路，再用 ASIC 或 FPGA 实现其功能。

HDL 的发展至今已有 30 多年的历史，它是 EDA 技术的重要组成部分，也是 EDA 技术发展到高级阶段的一个重要标志。目前已经存在许多硬件描述语言，其中 VHDL 和 Verilog HDL 是影响最为广泛的两种，并已成为 IEEE 的工业标准硬件描述语言，得到众多 EDA 公司的支持，在电子工程领域，已经成为事实上的通用硬件描述语言。

### 1.3.1 VHDL

VHDL 诞生于 1983 年，由美国国防部 (DOD) 发起创建。后来 IEEE (The Institute of Electrical and Electronics Engineers) 对其进一步发展，于 1987 年作为“IEEE 标准 1076”发布，从而正式成为硬件描述语言的业界标准之一。随着 VHDL 标准版本 (IEEE Std 1076) 的公布，各 EDA 公司相继推出了自己的 VHDL 设计环境，或宣布自己的设计工具可以使用和支持 VHDL。此后，VHDL 在电子设计领域得到了广泛应用，并逐步取代了原有的非标准硬件描述语言。1993 年，IEEE 对 VHDL 进行了修订，从更高的抽象层次和系统描述能力上扩展了 VHDL 的内容，公布了新版本 VHDL，即 IEEE1076—1993 版本。现在公布的最新 VHDL 标准版本是 IEEE1076—2008。

VHDL 主要用于描述数字系统的结构、行为、功能和接口。除了含有许多具有硬件特征的语句外，VHDL 的语言形式和描述风格与句法与一般的计算机高级语言十分类似。应用 VHDL 进行工程设计的优点是多方面的，具体如下。

(1) 与其他的硬件描述语言相比，VHDL 具有更强的行为描述能力，从而决定了它成为系统设计领域最佳的硬件描述语言。强大的行为描述能力是避开具体的器件结构，从逻辑行为上描述和设计大规模电子系统的重要保证。

(2) VHDL 最初是作为一种仿真标准格式出现的，因此 VHDL 既是一种硬件电路描述和设计语言，也是一种标准的网表格式，还是一种仿真语言。它有丰富的仿真语句和库函数，设计者可以在任何系统的设计早期随时对设计进行仿真模拟，查验所设计系统的功能特性，从而对整个工程设计的结构和功能的可行性做出决策。

(3) VHDL 语句的行为描述能力和程序结构决定了它具有支持大规模设计和分解已有设计的再利用功能，满足了大规模系统设计要由多人甚至多个开发组共同并行工作来实现的市场需求。VHDL 中设计实体的概念、程序包的概念、设计库的概念为设计的分解和并行工作提供了有力的支持。

(4) 对于用 VHDL 完成的一个确定的设计，可以利用 EDA 工具进行逻辑综合和优化，并自动地把 VHDL 描述设计转变成门级网表，生成一个更高效、更高速的电路系统。此外，设计者还可以很容易地从综合优化后的电路获得设计信息，再返回去更新修改 VHDL 的设计描述，使之更为完善。这种方式突破了门级设计的瓶颈，极大地减少了电路设计的时间和可能发生的错误，降低了开发成本。

(5) VHDL 对设计的描述具有相对独立性，设计者可以不懂硬件的结构，也不必管最终设计实现的目标器件是什么，而进行独立的设计。正因为 VHDL 的硬件描述语言与具体的工艺技术和硬件结构无关，VHDL 设计程序的硬件实现目标器件有广阔的选择范围，其中包括各系列的 CPLD、FPGA 及各种门阵列实现目标。

(6) 由于 VHDL 具有类属描述语句和子程序调用等功能，对于已完成的设计，在不改变源程序的条件下，只需改变端口类属参量或函数，就能轻易地改变设计的规模和结构。

### 1.3.2 Verilog HDL

Verilog HDL 是在 C 语言的基础上发展而来的硬件描述语言，具有简洁、高效、易用的特点，是目前应用最为广泛的硬件描述语言之一。Verilog HDL 可以用来进行各种层次的逻辑设计，也可以用它进行数字逻辑系统的仿真验证、时序分析和逻辑综合等。在 ASIC 设计领域，Verilog HDL 已经成为了事实上的标准。

Verilog HDL 于 1983 年由 GDA (GateWay Design Automation) 公司的 Phil Moorby 首创，1989 年 Cadence 公司收购了 GDA 公司，Verilog HDL 成为了 Cadence 公司的私有财产。1990 年，Cadence 公司决定公开 Verilog HDL，于是成立了 OVI (Open Verilog International) 组织来负责 Verilog HDL 的发展。基于 Verilog HDL 的优越性，IEEE 先后推出了两个 Verilog 标准，即 IEEE Std. 1364—1995 (Verilog—1995) 和 IEEE Std. 1364—2001 (Verilog—2001)，后者在前者的基础上对 Verilog HDL 进行了若干改进和扩充，使其功能更强、使用更方便。

Verilog HDL 适合算法级 (Algorithm – level)、寄存器传输级 (Register Transfer Level, RTL)、门级 (Gate – level) 和版图级 (Layout – level) 等各个层次的设计和描述。

在采用 Verilog HDL 进行设计时，由于 Verilog HDL 的标准化，可以很容易地把完成的设计移植到不同厂家的不同芯片中去。用 Verilog HDL 所完成的设计，其信号参数是很容易改变的，可以任意修改，以适应不同规模的应用。在仿真验证时，测试向量也可以用该语言来描述。此外，采用 Verilog HDL 进行设计还具有与工艺无关性的优点，这使得工程师在功能设计、逻辑验证阶段可以不必过多地考虑门级及工艺实现的具体细节，只需要利用系统设计时对芯片的需要，施加不同约束条件，即可设计出实际电路。

### 1.3.3 VHDL 和 Verilog HDL 的比较

一般硬件描述语言可以在三个层次上进行电路描述，其描述层次依次可分为行为级、RTL 级和门电路级。VHDL 的特点决定了它更适用于行为级（也包括 RTL 级）的描述，有

人将它称为行为描述语言；而 Verilog HDL 属于 RTL 级硬件描述语言，通常只适用于 RTL 级和更低层次的门电路级描述。

由于任何一种硬件描述语言的源程序始终都要转化成门电路级才能被布线器或适配器所接受，因此，VHDL 源程序的综合通常要经过行为级到 RTL 级再到门电路级的转化；而 Verilog HDL 源程序的综合过程要稍简单些，只需要经过 RTL 级到门电路级的转化。

与 Verilog HDL 相比，VHDL 是一种高级描述语言，适用于电路高级建模，比较适合于 FPGA/CPLD 目标器件的设计或间接方式的 ASIC 设计；而 Verilog HDL 则是一种较低级的描述语言，更适用于描述门级电路，易于控制电路资源，因此更适合于直接的集成电路或 ASIC 设计。

VHDL 与 Verilog HDL 的共同特点是：能形式化地抽象表示电路的结构和行为；支持逻辑设计中层次与领域的描述；可借用高级语言的精巧结构来简化电路的描述，具有电路仿真与验证机制以保证设计的正确性；支持电路描述由高层到底层的综合转换；便于文档管理；易于理解和设计重用。VHDL 与 Verilog HDL 的主要区别在于逻辑表达的描述级别。VHDL 虽然也可以直接描述门电路，但这方面的能力却不如 Verilog HDL，而 Verilog HDL 在高级描述方面不如 VHDL。Verilog HDL 的描述风格接近于电路原理图，从某种意义上说，它是电路原理图的高级文本表示方式；VHDL 最适于描述电路的行为，然后由综合器根据功能要求来生成符合要求的电路网表。

Verilog HDL 的最大优点是易学易用、入门容易，只要有 C 语言的编程基础，设计者可以在 2~3 个月内掌握这种设计技术；VHDL 入门相对较难，一般很难在短时间内真正掌握其设计技术，但在熟悉以后，其设计效率明显高于 Verilog HDL，生成的电路性能也与 Verilog HDL 生成的电路不相上下。

由于 VHDL 和 Verilog HDL 各有所长，所以市场占有量相差不多。在美国 Verilog HDL 和 VHDL 的应用比例是 60% 和 40%，在中国台湾地区各为 50%，在中国大陆地区则为 10% 和 90%。中国大陆和美国相比，有较大差距的原因，是由于 VHDL 在语言风格上具有规范、严谨的特点，再加上引入到国内的时间较早，因此国内高校普遍都以 VHDL 作为主要授课内容；相反，由于 Verilog HDL 在编程风格上具有灵活、简洁的特点，更适合美国人的口味，在美国的许多著名高校如斯坦福大学、南加州大学等都以 Verilog HDL 作为主要授课内容。

目前，大多数高档 EDA 软件都支持 VHDL 和 Verilog HDL 混合设计，因而在工程应用中，有些电路模块可以用 VHDL 设计，其他电路模块则可以用 Verilog HDL 设计。各取所长，已成为 EDA 应用技术发展的一个重要趋势。

## 1.4 常用的 EDA 工具

EDA 工具在 EDA 技术应用中占据极其重要的位置。EDA 的核心是利用计算机实现电子设计的全部自动化，因此，基于计算机环境的 EDA 软件的支持是必不可少的。

由于 EDA 整个流程设计不同技术环节，每一个环节中必须有对应的软件包或专用 EDA 工具独立处理，包括对电路模型及对 VHDL 进行描述的逻辑综合等。因此，单个 EDA 工具往往只涉及 EDA 流程中的某一步骤。这里就以 EDA 设计流程中涉及的主要软件包为 EDA

工具分类，并做简单介绍。EDA 工具大致可以分为 5 个模块：①设计输入编辑器；②HDL 综合器；③仿真器；④适配器；⑤下载器。

当然这种分类不是绝对的，现在也有集成的 EDA 开发环境，如 Xilinx 公司的 Vivado 开发环境。

### 1.4.1 设计输入编辑器

在 FPGA/CPLD 设计中的设计输入编辑器或称设计输入环境，可以接受不同的设计输入表达方式，如原理图输入方式、状态图输入方式、波形输入方式以及 HDL 的文本输入方式。在各可编程逻辑器件厂商提供的 EDA 开发工具中一般都含有这类输入编辑器。

通常，专业的 EDA 工具供应商也提供相应的设计输入工具，这些工具一般与该公司的其他电路设计软件整合，这一点尤其体现在原理图输入环境上。如 Innovada 的 eProduct Designer 中的原理图输入管理工具 DxDesigner，既可作为 PCB 设计的原理图输入，又可作为 IC 设计、模拟仿真和 FPGA 设计的原理图输入环境。比较常见的还有 Cadence 的 OrCAD 产品中的 Capture 工具等。这一类的工具一般都设计成通用型的原理图输入工具。由于针对 FPGA/CPLD 设计的原理图要含有特殊原理图库（含原理图中的 Symbol 原件）的支持，因此其输出并不与 EDA 流程的下一步设计工具直接相连，而要通过网表文件（如 EDIF 文件）来传递。

由于 HDL（包含 VHDL、Verilog-HDL 等）的输入方式是文本格式，所以它的输入实现要比原理图输入简单得多，用普通的文本编辑器即可完成。如果要求 HDL 输入时有语法色彩提示，可用带语法提示功能的通用文本编辑器，如 UltraEdit \ Vim \ XEmacs 等。当然，EDA 工具中提供的 HDL 编辑器会更好用些，如 Aldec 的 Active HDL 中的 HDL 编辑器、Altium 的 Altium Designer 中的 HDL 编辑器。另一方面，由于可编程逻辑器件规模的增大，涉及可选性大为增加，需要有完善的输入文档管理，Mentor 的 HDL Designer Series 就是此类工具的一个典型代表。

有的 EDA 设计输入工具把图形设计与 HDL 文本设计相结合，如在提供 HDL 文本编辑器的同时提供状态机编辑器，用户可用图形（状态机）来描述状态机，最后生成 HDL 文本输出。如 Mentor 公司的 FPGA Advantage（含 HDLDesigner Series）、Active HDL 中的 Active State 等。尤其是 HDL Designer Series 中的各种输入编辑器，可以接受诸如原理图、状态图、表和图等输入形式，并将它们转成 VHDL / Verilog 文本表达方式，很好地解决了通用性（HDL 输入的优点）与易用性（图形法的优点）之间的矛盾。

设计输入编辑器在多样性、易用性和通用性方面的功能不断增强，标志着 EDA 技术中自动化设计程度的不断提高。

### 1.4.2 综合器

由于目前通用的 HDL 语言为 VHDL 和 Verilog-HDL，这里介绍的 HDL 综合器主要是针对这两种语言的。

硬件描述语言诞生的初衷是用于电路逻辑的建模和仿真，但直到 Synopsys 公司推出了 HDL 综合器后，才改变了人们的看法，于是可以将 HDL 直接用于电路的设计。

由于 HDL 综合器是目标器件硬件结构细节、数字电路设计技术、化简优化算法以及计

算机软件的复杂综合体，而且 HDL 可综合子集迟迟未能标准化，所以相比于形式多样的设计输入工具，成熟的 HDL 综合器并不多。比较常用的性能良好的 FPGA/CPLD 设计的 HDL 综合器有如下 3 种：

- (1) Synopsys 公司的 FPGAComputer、FPGAEexpress 综合器。

- (2) Synplicity 公司的 Synplify pro 综合器。

- (3) Mentor 子公司 Exemplar Logic 的 Leonardo spectrum 综合器。

较早推出综合器的是 Synopsys 公司，它为 FPGA/CPLD 开发推出的综合器是 FPGAEexpress 及 FPGA compiler，两者差别不是很大。为了处理方便，最初由 Synopsys 公司在综合器中增加了一些用户自定义类型，如 Std\_logic 等，后被纳入 IEEE 标准。对于其他综合器也是都只能支持 VHDL 中的可综合子集。FPGA compiler 中带有一个原理图生成浏览器，可以把综合出的网表用原理图的方式画出来，便于验证设计，还附带有强大的延时分析器，可以对关键路径进行简单分析。

Synplicity 公司的 Synplify pro 综合器除了有原理图生成器、延时分析器外，还带有一个 FSM compiler（有限状态机编辑器），可以从提交的 VHDL/Verilog 设计文本中提出存在的有限状态机设计模块，并用状态图的方式显示出来，用表格说明状态的转移条件及输出。Synplify pro 的原理图浏览器可以定位于原理图中原件中 VHDL/Verilog 源文件的对应语句，便于调试。

Exemplar 公司的 Leonardo spectrum 综合器也是一个很好的 HDL 综合器，它同时可用于 FPGA/CPLD 和 ASIC 设计两类工程目标。Leonardo spectrum 作为 Mentor 公司的 FPGAAadvantage 中的组成部分，可以与 FPGAAadvantage 的设计输入管理工具和仿真工具很好的结合。

当然也有应用于 ASIC 设计的 HDL 综合器，如 Synopsys 的 Design Compiler、Synplicity 的 SynplifyASIC 和 Cadence 的 synergy 等。

HDL 综合器在把可综合的 VHDL/Verilog 语言转化为硬件电路时，一般要经过两个步骤：

第一步，HDL 综合器对 VHDL/Verilog 进行分析处理，这个过程是一个通用电路原理图形成的过程。

第二步，对实现目标器件的结构进行优化，使之满足各种约束条件，并优化关键路径等。

HDL 综合器的输出文件一般是网表文件，如 EDIF 格式（Electronic Design Interchange Format），文件后缀是 .edf，是一种用于设计数据交换的工业标准文件格式的文件，或是直接用 VHDL/Verilog 语言表达标准格式的网表文件，或是应对 FPGA 器件厂商的网表文件，如 Xilinx 的 XNF 网表文件和 Altera 的 VQM 网表文件。

由于综合器只能完成 EDA 设计流程中的一个独立设计步骤，所以它往往被其他 EDA 环境调用，以完成全部流程。它的调用方式一般有两种：另一种是前台模式，再被调用时，显示的是最常见的窗口界面；另一种称为后台模式或控制台模式，被调用是不出现图形界面，就在后台运行。

综合器的使用也有两种模式：图形模式和命令行模式（shell 模式）。

### 1.4.3 仿真器

仿真器有基于元件（逻辑门）的仿真器和 HDL 语言的仿真器之分，基于元件的仿真器缺乏 HDL 仿真器的灵活性和通用性。在此主要介绍 HDL 仿真器。

在 EDA 设计技术中，仿真的地位十分重要。行为模型的表达、电子系统的建模、逻辑电路的验证乃至门级系统的测试，每一步都离不开仿真器的模拟检测。在 EDA 发展的初期，快速进行电路逻辑仿真是当时的核心问题，即使在现在，各设计环节的仿真仍然是整个 EDA 工程流程中最耗时间的一个步骤。因此仿真器的仿真速度、仿真的准确性及易用性成为衡量仿真器的重要指标。按仿真器对设计语言不同的处理方式分类，可分为编译型仿真器和解释型仿真器。

编译型仿真器的仿真速度很快，但需要预处理，因此不便即时修改；解释型仿真器的仿真速度一般，可随时修改仿真环境和条件。

按处理的硬件描述语言类型分，HDL 仿真器可分为：①VHDL 仿真器；②Verilog 仿真器；③MixedHDL 仿真器（混合 HDL 仿真器，同时处理 VHDL 和 Verilog）；④其他 HDL 仿真器（针对其他 HDL 语言的仿真）。

Model Technology 的 ModelSim 是一个出色的 VHDL/Verilog 混合仿真器。它也属于编译型仿真器，仿真执行速度快。

Cadence 公司的 Verilog - XL 是最好的 Verilog 仿真器之一，Verilog - XL 的前身与 Verilog 语言一起诞生。

按仿真电路描述级别的不同，HDL 仿真器可以单独或综合完成以下各仿真步骤：系统级仿真、行为级仿真、RTL 级仿真、门级时序仿真。

按仿真时是否考虑硬件延时分类，可分为功能仿真和时序仿真。根据输入仿真文件的不同，可以由不同的仿真器完成，也可由同一个仿真器完成。

几乎各个 EDA 厂商都提供基于 VHDL/Verilog 的仿真器，常用的 HDL 仿真器除上面提及的 ModelSim 与 Verilog - XL 外，还有 Aldec 的 Active HDL、Synopsys 的 VCS、Cadence 的 NC - Sim 等。

### 1.4.4 适配器

适配器（布局布线器）的任务是完成目标系统在器件上的布局布线。适配即结构综合，通常都由可编程逻辑器件的厂商提供的专门针对器件开发的软件来完成，这些软件可以单独存在或嵌入在厂商的针对自己产品的集成 EDA 开发环境中。例如 Lattice 公司在其 ispEXPERT Compiler；而 Altera 公司的 EDA 集成开发环境 Quartus II 中都含有嵌入的适配器；Xilinx 的 ISE 和 Vivado 中也同样含有自己的适配器。适配器最后输出的是各厂商自己定义的下载文件，以下载到器件中实现设计。适配器输出如下多种用途的文件：

- (1) 时序仿真文件，如 MAX + Plus II 的 SCF 文件等。

- (2) 适配技术报告文件。

- (3) 面向第三方 EDA 工具的输出文件，如 EDIF、Verilog 或 VHDL 格式的文件。

- (4) FPGA/CPLD 编程下载文件，如用于 CPLD 编程的 JEDEC、POF、ISP 等格式的文件和用于 FPGA 配置的 SOF、JAM、BIT、POF 等格式的文件。

### 1.4.5 编程下载

下载器（编程器）的功能是把设计下载到对应的实际器件，实现硬件设计。软件部分一般都由可编程逻辑器件的厂商提供的专门针对器件下载或编程软件来完成。

## 1.5 EDA 的工程设计流程

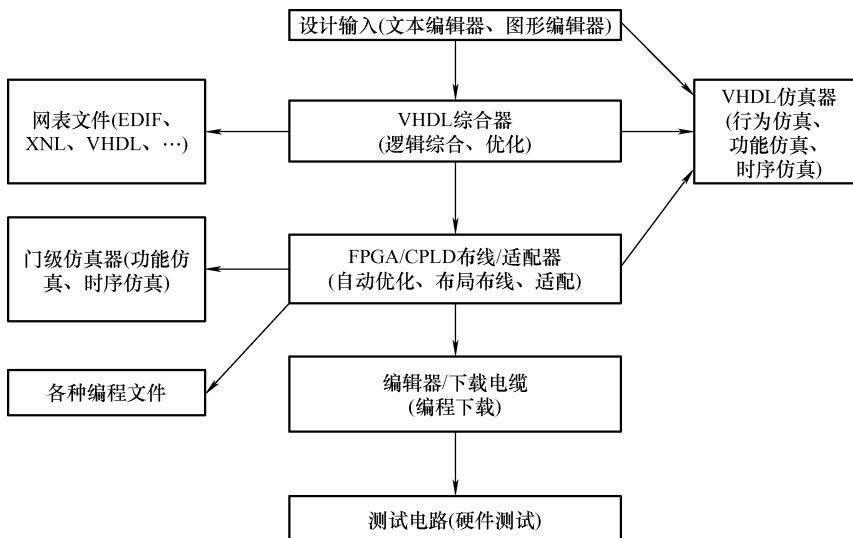

完整地了解利用 EDA 技术进行设计开发的流程对于正确选择和使用 EDA 软件、优化设计项目、提高设计效率十分有益。一个完整的 EDA 设计流程既是自顶向下设计方法的具体实施途径，也是 EDA 工具软件本身的组成结构。在实践中进一步了解支持这一设计流程的诸多设计工具，有利于有效地排除设计中出现的问题，提高设计质量和总结设计经验。本节主要介绍 FPGA 开发设计流程。EDA 的工程设计流程如图 1.3 所示。

图 1.3 EDA 的工程设计流程

### 1. 设计输入

将电路系统以一定的表达方式输入计算机，是在 EDA 软件平台上对 FPGA/CPLD 开发的最初步骤。通常，使用 EDA 工具的设计输入为图形输入和 HDL 文本输入。

图形输入通常包括原理图输入、状态图输入和波形图输入 3 种常用方法。

状态图输入方法就是根据电路的控制条件和不同的转换方式，用绘图的方法，在 EDA 工具的状态图编辑器上绘出状态图，然后由 EDA 编译器和综合器将此状态变化流程图形编译综合成电路网表。

波形图输入方法则是将待设计的电路看成是一个黑盒子，只需要告诉 EDA 工具黑盒子电路的输入和输出时序波形图。EDA 工具即能据此完成黑盒子电路设计。

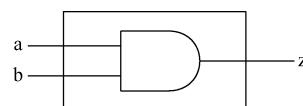

这里主要讨论原理图输入设计方法。这是一种类似于传统电子设计方法的原理图编辑输入方式，即在 EDA 软件的图形编辑界面上绘制能完成特定功能的电路原理图。原理图由逻辑器件（符号）和连接线构成，图中的逻辑器件可以是 EDA 软件库中预制功能模块，如与

门、非门、或门、触发器以及各种含 74 系列器件功能的宏功能块，甚至还有一些类似于 IP 的功能块。当原理图编辑绘制完成后，原理图编辑器将对输入的图形文件进行排错，之后再将其编译成适用于逻辑综合的网表文件。

用原理图表达的输入方法的优点主要在于不需要增加新的相关知识（诸如 HDL 等）；设计过程形象直观，适用于初学或者教学演示等。然而，其缺点同样十分明显。

(1) 由于图形设计并未标准化，不同的 EDA 图形处理工具对图形的设计规则、存档格式和图形编译方式都不同，因此图形文件兼容性差，难以交换和管理。

(2) 随着电路设计规模的扩大，原理图输入描述方式必然引起一系列难以克服的困难，如电路功能原理的易读性下降，错误排查困难，整体调整和结构升级困难。例如，将一个 4 位的单片机设计升级为 8 位单片机几乎难以在短时间内实现。

(3) 由于在原理图中已确定了设计系统的基本电路结构和元件，留给综合器和适配器的优化选择的空间已十分有限，因此难以实现用户所希望的面积、速度以及不同风格和综合优化。显然，原理图的设计方法明显偏离了电子设计自动化最本质的含义。

(4) 在设计中，由于必须直接面对硬件模块的选用，因此行为模块的建立将无从谈起，从而无法实现真实意义上的自顶向下的设计方案。

HDL 文本输入与传统的计算机软件语言编辑输入基本一致。就是将使用了某种硬件描述语言的电路设计文本，如 VHDL 或 Verilog HDL 的源程序，进行编辑输入。

可以说，应用 HDL 的文本输入方法克服了上述原理图输入法的所有弊端，为 EDA 技术的应用和发展打开了一个广阔的天地。当然在一定的条件下，情况会有所改变。目前有些 EDA 输入工具可以把图形的直观与 HDL 的优势结合起来。如状态图输入的编辑方式，即用图形化状态机输入工具，用图形的方式表示状态图。当填好时钟信号名、状态转换条件、状态机类型等要素后，就可以自动生成 VHDL/Verilog 程序。又如，在原理图输入方式中，连接用 HDL 描述的各个电路模块，直观地表述系统的总体框架，再用自动 HDL 生成工具生成相应的 VHDL 或 Verilog 程序。

总体来看，纯 HDL 输入设计仍然是最基本、最有效和最通用的输入方法。

## 2. 综合

前面已经对综合的概念做了介绍。一般来说，综合是仅对 HDL 而言的。利用 HDL 综合器对设计进行综合是十分重要的一步，因为综合过程将把软件设计的 HDL 描述与硬件结构挂钩，是将软件转化为硬件电路的关键步骤，是文字描述与硬件实现的一座桥梁。综合就是将电路的高级语言（如行为描述）转换成低级的，可与 FPGA/CPLD 的基本结构相映射的网表文件或程序。当输入的 HDL 文件在 EDA 工具中检测无误后，首先面临的是逻辑综合，因此要求 HDL 源文件中的语句都是可综合的。

在综合后，综合器一般都可以生成一种或多种文件格式网表文件，如 EDIF、VHDL、Verilog、VQM 等标准格式，在这种网表文件中用各自的格式描述电路的结构。如在 VHDL 网表文件采用 VHDL 的语法，用结构描述的风格重新诠释综合后的电路和结构。

整个综合过程就是将设计者在 EDA 平台上编辑输入 HDL 文本、原理图或状态图形描述，依据给定的硬件结构组件和约束控制条件进行编译、优化、转化和综合，最终获得门级电路甚至更底层的电路描述网表文件。由此可见，综合器工作前，必须给定最后实现的硬件结构参数，它的功能就是将软件描述与给定的硬件结构用某种网表文件的方式对应起来，成

为相应的映射关系。如果把综合理解为映射过程，那么显然这种映射不是唯一的，并且综合的优化也不是单方向的。为达到速度、面积、性能的要求，往往需要对综合加以约束，称为综合约束。

### 3. 布局布线

布局布线的输入文件是综合后的网表文件，Quartus II 软件中布局布线包含分析布局布线、优化布局布线、增量布局布线和通过反标保留分配等。

### 4. 时序仿真与功能仿真

在编程下载前必须利用 EDA 工具对适配生成的结果进行模拟测试，就是所谓的仿真。仿真就是让计算机根据一定的算法和一定的仿真库对 EDA 设计进行模拟测试，以验证设计，排除错误。仿真是在 EDA 设计过程中的重要步骤。时序与功能门级仿真通常有 PLD 公司的 EDA 开发工具直接提供（当然也可以选用第三方的专业仿真工具），它可以完成两种不同级别的仿真测试：

(1) 时序仿真，就是接近真实器件运行特性的仿真，仿真文件中包含了器件硬件特性参数，因而，仿真精度高。但时序仿真的仿真文件必须来自针对具体器件的综合器与适配器。综合后所得的 EDIF、VQM 等网表文件通常作为 FPGA 适配器的输入文件，产生的仿真网表文件中包含了精确的硬件延迟信息。

(2) 功能仿真，是直接对 HDL、原理图描述或其他形式的逻辑功能进行测试模拟，以了解其实现的功能是否满足原设计要求。仿真过程不可涉及任何具体器件的硬件特性。甚至不经历综合与适配阶段，在设计项目编辑编译后即可进入门级仿真进行模拟测试。直接进行功能仿真好处是设计耗时短，对硬件库、综合器等没有任何要求。对于规模比较大的设计项目，综合与适配在计算机上的耗时是十分可观的，如果每一次修改后的模拟都必须进行时序仿真，显然会极大地降低开发效率。因此，通常的做法是，首先进行功能仿真，待确定设计文件所表达的功能接近或满足设计者原有的意图时，即逻辑功能满足要求后，再进行综合、适配和时序仿真，以便把握设计项目在硬件条件下的运行情况。

如果仅限于 Quartus II 本身的仿真器，即使功能仿真，其设计文件也必须是可综合的，且需经历综合器的综合。只有使用 ModelSim 等专业仿真器才能实现对 HDL 设计代码不经综合的直接功能仿真。

### 5. 适配

适配器也称为结构综合器，它的功能是将由综合器产生的网表文件配置于指定的目标器件中，使之产生最终的下载文件，如 SOF、JAM、JEDEC、POF 等格式的文件。适配所选定的目标器件必须属于原综合器指定的目标器件系列。通常，EDA 软件中的综合器可有专业的第三方 EDA 公司提供，而适配器则需由 FPGA/CPLD 供应商提供。因为适配器的适配对象直接与器件的结构细节相对应。

适配器将综合后的网表文件针对某一具体的目标器件进行逻辑映射操作，其中包括底层器件配置、逻辑分割、逻辑优化、逻辑布局布线操作。适配完成后可以利用适配所产生的仿真文件做精确的时序仿真测试，同时产生可用于编程的文件。

### 6. 编程下载

把适配后生成的下载或配置文件，通过编程器或编程电缆向 FPGA 或 CPLD 下载，以便

进行硬件调试和验证。通常，将对 CPLD 的下载称为编程，对 FPGA 中的 SRAM 进行直接下载的方式称为配置，但对于反熔丝结构和 Flash 结构的 FPGA 的下载和对 FPGA 的专用配置 ROM 的下载仍称为编程。当然也有根据下载方式分类的。

## 7. 硬件测试

最后是将含有载入了设计文件的 FPGA 或 CPLD 的硬件系统进行统一测试，以便最终验证设计项目在目标系统上的实际工作情况，以排除错误，改进设计。

# 1.6 Vivado 概述

由于本书给出的实验和设计多是基于 Vivado 的，所以在此对它做一些介绍。

美国 Xilinx（赛灵思）公司是全球领先的可编程逻辑完整解决方案的供应商，研发、制造并销售应用范围广泛的高级集成电路、软件设计工具以及定义系统功能的 IP 核，长期以来一直推动着 FPGA 的发展。

Xilinx 公司于 2012 年发布了新一代 Vivado 集成开发环境，使得新一代 FPGA 的设计环境和设计方法发生了重大变化。Xilinx 公司的 Vivado 设计套件包含了高度集成的设计环境和新一代系统到 IC 级别的工具，这些均建立在共享的可扩展数据模型和通用调试环境基础上。Vivado 设计套件采用了用于快速综合和验证 C 语言算法 IP 的 ESL 设计，实现重用的标准算法和 RTL IP 封装技术，标准 IP 封装和各类系统构建模块的系统集成以提高系统仿真速度。Vivado 工具也可将各类可编程技术结合在一起，扩展实现多达 1 亿个等效 ASIC 门的设计。

2014 年年初，Xilinx 新一代 UltraScale 结构的 FPGA 也进入量产阶段。这些都标志着未来在高性能数据处理方面 FPGA 将发挥越来越重要的作用。Xilinx 新一代开发环境 Vivado 突出基于知识产权（Intellectual Property, IP）核的设计方法，更加体现系统级设计的思想，进一步增强了设计者对 FPGA 底层布局和布线的干预能力，以及允许设计者通过选择不同的设计策略，对不同的实现方法进行探索，从中找到最佳的解决方案。这些设计思想和设计方法，大大提高了 FPGA 的设计效率。

# 1.7 EDA 技术的发展趋势

随着 Xilinx 等公司几十万门规模的 FPGA 的上市，以及大规模的芯片组和高速、高密度印制电路板的应用，EDA 技术在仿真、时序分析、集成电路自动测试、高速印制电路板设计及操作平台的扩展等方面面临着新的巨大挑战。这些就是新一代的 EDA 技术未来的发展趋势。新一代 EDA 技术将向着功能强大、简单易学、使用方便的方向发展。

## 1. 开发工具的发展趋势

面对当今飞速发展的电子产品市场，电子设计人员需要更加实用、快捷的开发工具，使用统一的集成化设计环境，改变优先考虑具体物理实现方式的传统设计思路，将精力集中到设计构思、方案比较和寻找优化设计等方面，以最快的速度开发出性能优良、质量一流的电子产品。开发工具的发展趋势如下。

(1) 具有混合信号处理能力 由于数字电路和模拟电路的不同特性，模拟集成电路EDA工具的发展远远落后于数字电路EDA开发工具。但是，由于物理量本身多以模拟形式存在，实现高性能复杂电子系统的设计必然离不开模拟信号。20世纪90年代以来，EDA工具厂商都比较重视数模混合信号设计工具的开发。美国Cadence、Synopsys等公司开发的EDA工具已经具有了数模混合设计能力，这些EDA开发工具能完成含有模-数转换、数字信号处理、专用集成电路宏单元、数-模转换和各种压控振荡器在内的混合系统设计。

(2) 高效的仿真工具 在整个电子系统设计过程中，仿真花费时间最多的工作，也是占用EDA工具时间最多的一个环节。可以将电子系统设计的仿真过程分为两个阶段：设计前期的系统级仿真和设计过程中的电路级仿真。系统级仿真主要验证系统的功能，如验证设计的有效性等；电路级仿真主要验证系统的性能，决定怎样实现设计，如测试设计的精度、处理和保证设计要求等。要提高仿真的效率，一方面要建立合理的仿真算法；另一方面要更好地解决系统级仿真中系统模型的建模和电路级仿真中电路模型的建模技术。在未来的EDA技术中，仿真工具将有较大的发展空间。

(3) 理想的逻辑综合、优化工具 逻辑综合功能是将高层次系统行为设计自动翻译成门级逻辑的电路描述，做到了实际与工艺的独立。优化则是对于上述综合生成的电路网表，根据逻辑方程功能等效的原则，用更小、更快的综合结果替代一些复杂的逻辑电路单元，根据指定目标库映射成新的网表。随着电子系统的集成规模越来越大，几乎不可能直接面向电路图做设计，要将设计者的精力从烦琐的逻辑图设计和分析中转移到设计前期算法开发上。逻辑综合、优化工具就是要把设计者的算法完整高效地生成电路网表。

## 2. 系统描述方式的发展趋势

(1) 描述方式简便化 20世纪80年代，电子设计开始采用新的综合工具，设计工作由逻辑图设计描述转向以各种硬件描述语言为主的编程方式。用硬件描述语言设计，更接近系统行为描述，且便于综合，更适于传递和修改设计信息，还可以建立独立于工艺的设计文件；不便之处是不太直观，要求设计师具有硬件语言描述能力，但是编程能力需要长时间的培养。

到了20世纪90年代，一些EDA公司相继推出了一批图形化的设计输入工具。这些输入工具允许设计师用他们最方便并熟悉的设计方式（如框图、状态图、真值表和逻辑方程）建立设计文件，然后用EDA工具自动生成综合所需的硬件描述语言文件。图形化的描述方式具有简单直观、容易掌握的优点，是未来主要的发展趋势。

(2) 描述语言高效化和统一化 C/C++语言是软件工程师在开发商业软件时的标准语言，也是使用最为广泛的高级语言。许多公司已经提出了不少方案，尝试在C语言的基础上设计下一代硬件描述语言。随着算法描述抽象层次的提高，使用C/C++语言设计系统的优势将更加明显，设计者可以快速而简洁地构建功能函数，通过标准库和函数调用技术，创建更庞大、更复杂和更高速的系统。

但是，目前的C/C++语言描述方式与硬件描述语言之间还有一段距离，还有待于更多EDA软件厂家和可编程逻辑器件公司的支持。随着EDA技术的不断成熟，软件和硬件的概念将日益模糊，使用单一的高级语言直接设计整个系统将是一个统一化的发展趋势。

## ● 本章小结

本章主要讲述了 EDA 技术及其重要性，EDA 包含的知识体系结构，如 HDL、EDA 的工作软件等，比较了传统电子设计方法与 EDA 技术各自的特点。同时对 EDA 技术的发展历程、特点和优势，以及利用 EDA 进行工程设计的流程进行简要介绍。

EDA 技术是以计算机为工作平台，以 HDL 为逻辑描述的表达方式，以 EDA 工具软件为开发环境，以 FPGA/CPLD 为设计载体，以 ASIC、SoC 芯片为目标器件，以电子系统设计为应用方向的电子产品自动化设计过程。EDA 技术是现代电子设计技术的发展方向和核心，其内容丰富，涉及广泛，从教学和应用的角度出发，应掌握以下几个方面的知识点：掌握 EDA 工具概念和发展历程；了解 EDA 技术的主要应用领域；掌握 EDA 工具的设计流程；了解常用的 EDA 集成开发环境；掌握 EDA 的学习重点和学习方法。

## ● 习 题

1. 1 简述 EDA 技术的发展历程。

1. 2 EDA 技术与 ASIC 设计和 FPGA 开发有什么关系？

1. 3 与软件描述语言相比，VHDL 有什么特点？

1. 4 EDA 设计流程包含几个步骤？

1. 5 EDA 设计工具有哪些主要模块？

1. 6 简述在 EDA 技术中，自顶向下的设计方法的优点。

1. 7 简述 IP 在 EDA 技术的应用和发展中所起的作用。

## 第 2 章

# CPLD与FPGA的结构原理

可编程逻辑器件与 EDA 技术的结合，改变了现代电子系统的设计方式。随着微电子技术的发展，单片集成电路的集成度越来越高，这也使得 PLD 的内部结构越来越复杂。现在的 PLD 内部的功能模块越来越丰富，具备了传统的 PLD 所没有的片内存储器（ROM 和 RAM）、锁相环（PLL）、数字信号处理（DSP）、定时器、嵌入式微处理器（CPU）等模块。所以，了解和掌握 PLD 的内部结构和工作原理变得比较困难。但是由于 EDA 软件已经发展到相当完善，用户可以在不必详细了解 PLD 内部结构的情况下，使用原理图输入或 HDL 语言等方法来完成自己的 PLD 设计。对于初学者，应该了解 PLD 开发软件和开发流程，不过了解 PLD 的内部结构，可以让我们合理地使用其内部功能模块和布线资源，有助于提高设计的效率和可靠性。

## 2.1 PLD 概述

可编程逻辑器件（Programmable Logic Device，PLD）是一种半定制集成电路，用户可以通过编程实现自己所需要的功能。PLD 是现代数字电子系统向着超高集成度、超低功耗、超小型封装和专用化方向发展的重要基础。对于 PLD，设计人员可利用价格低廉的软件工具快速开发、仿真和测试其设计。然后，可快速将设计编程到器件中，并立即在实际运行的电路中对设计进行测试。

### 2.1.1 PLD 入门

PLD 采用的是 CMOS 工艺，其内部集成了大量功能独立的分立元件，它们可以是基本逻辑门、由基本逻辑门构成的宏单元，以及与阵列、或阵列等。依据不同需求，芯片内元件的种类、数量可以有不同的设置。此外，芯片内还有大量可配置的连线，在器件出厂时，芯片内的各个元件、单元相互间没有连接，芯片暂不具有任何逻辑功能。芯片内的各个元件、单元如何连接，由用户根据自身设计的电路功能要求通过计算机编程决定。

从 20 世纪 70 年代发展起来的 PLD 经历了从低密度的 PLD 到逻辑规模较大的高密度 PLD 的发展历程。在此发展历程当中，PLD 产生了多种结构，形成了不同的产品。

20 世纪 70 年代，采用熔丝编程的只读存储器（Programmable Read—Only Memories，PROM）和可编程逻辑阵列（Programmable Logic Array，PLA）可以称作是最早的 PLD，它可以根据用户的需要写入相应的信息来完成一定的逻辑功能。

20 世纪 70 年代末，AMD 公司推出了可编程逻辑器件（Programmable Array Logic，PAL），并对 PLA 器件进行了改进。

20 世纪 80 年代初，Lattice 公司推出了另外一种新型的可编程逻辑器件（Generic—

Programmable Array Logic, GAL), 采用了电可擦写工艺, 克服了 PAL 器件存在的缺点, 应用起来更加灵活和方便。

1985 年, 美国 Xilinx 公司首家推出的一种新型的可编程逻辑器件 (Field Programmable Gate Array, FPGA)。1986 年, Altera 公司推出了一种新型可擦除、可编程的逻辑器件 (Erasable Programmable Logic Device, EPLD), 可以用紫外线或电擦除。

20 世纪 80 年代末, Lattice 公司又提出了在系统可编程技术 (In System Programmable, ISP) 技术, 与此同时, Lattice 公司推出了一系列具备在系统可编程能力的 CPLD 器件, 使 CPLD 的应用领域得到了巨大的扩展。

20 世纪 90 年代后, 由于半导体工艺的发展, PLD 飞速发展, 以 FPGA 和 CPLD 为代表的 PLD 不断涌现。目前 PLD 的规模越来越大、速度越来越快、电路结构越来越灵活, 并且出现了集成了微处理器、数字信号处理单元和存储器等的内嵌复杂功能块的 PLD。PLD 的发展使得一个数字系统已经可以装配在一块 PLD 芯片上, 即所谓的片上系统 SoC。

PLD 的出现和发展大大改变了传统的系统设计方法, 这种方法使得电子系统设计变得更加简单方便、灵活快速。因此, 掌握可编程逻辑器件和相应的设计技术已经成为从事电子系统设计的设计工程师和科研人员的一项重要设计手段和技能。

## 2.1.2 常见的 PLD

目前生产 PLD 的厂家有很多, 其中主要包括 Xilinx、Altera、Lattice、Atmel、Actel、AMD、Intel 等。各个厂家又有不同的系列和产品名称, 器件的种类和分类更是大不相同。常见的分类方式有按互连结构分类、按编程工艺分类、按器件结构分类、按集成度分类。

### 1. 按互连结构分类

PLD 按照互连结构分类可以分为确定型 PLD 和统计型 PLD。确定型 PLD 是指互连结构每次用相同的互连线来实现布线, 所以线路的时延是可以预测的。包括简单的 PLD 器件和 CPLD 器件。目前除了 FPGA 以外的器件, 基本上都属于这一类结构。统计型 PLD 是指设计系统每次执行相同的功能, 但是却能给出不同的布线模式, 我们无法预知确切的线路时延, 统计型 PLD 的代表是 FPGA。

### 2. 按编程工艺分类

由于 PLD 在编程工艺上存在很大差别, 所以可以按照编程工艺划分为以下几类。

熔丝开关是最早的可编程元件, 由熔断丝组成, 根据设计的熔丝图的文件来烧断对应的熔丝, 达到编程的目的。

反熔丝型技术是对熔丝技术的改进, 编程时, 在需要连接处的反熔丝开关元件两端加上编程电压, 反熔丝将由高阻抗变为低阻抗, 实现两点间的连接, 编程后器件内的反熔丝模式决定了相应器件的逻辑功能。

以上两种结构在进行编程后不能修改, 只能进行一次编程, 因此又被称为一次可编程 OTP (One Time Programmable, OTP) 器件。熔丝型器件的缺点是占用面积大、要求大电流、难于测试。

UEPROM 型器件又被称为紫外线擦除/电可编程器件。使用者需要用较高的编程电压进行编程, 当需要进行再次编程时, 可以利用紫外线对其进行擦除。因此, UEPROM 型器件可以进行多次编程。

E<sup>2</sup>PROM 编程器件又被称为电可擦写编程器件，可以采用电擦除，而不再需要紫外线对其进行擦除。

SRAM 型器件又被称为 SRAM 查找表结构的器件。SRAM 型器件使用静态存储器 SRAM 存储配置数据，这种 SRAM 配置存储器具有很强的抗干扰能力，每次掉电后配置的存储数据会消失，在每次上电后又会重新进行配置。

### 3. 按器件结构分类

PLD 按照与阵列和或阵列的编程情况可以将可编程逻辑器件分成以下 4 类。

第一类是与阵列固定、或阵列可编程的 PLD，其中以可编程只读存储器 PROM 为代表。可编程只读存储器 PROM 是组合逻辑阵列，它包含一个固定的与阵列和一个可编程的或阵列。

第二类是与阵列和或阵列都可以进行编程的 PLD，其中以 PLA 作为这类可编程逻辑器件的代表。与 PROM 相同的是，PLA 也是组合型逻辑阵列，但是 PLA 的两个逻辑阵列均可进行编程。

第三类是与阵列可编程、或阵列固定的 PLD，其中以 PAL 作为这类 PLD 的代表。

第四类是具有可编程输出逻辑宏单元的通用 PLD，以通用型可编程阵列逻辑 GAL 器件为主要代表。

### 4. 按集成度分类

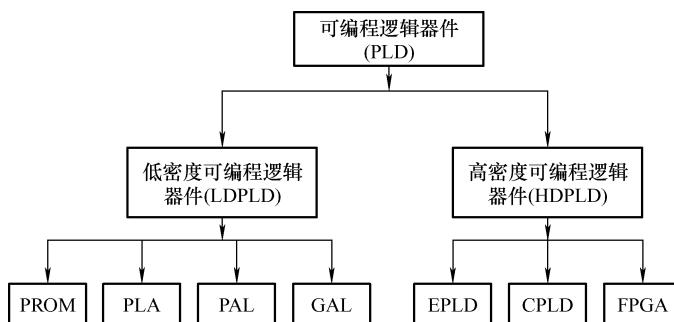

如果从集成度上分类，可以分为低密度 PLD (LDPLD) 和高密度 PLD (HDPLD)，如图 2.1 所示。通常，当 PLD 中集成度不超过 500 门时，则认为它是低密度 PLD，反之则为高密度 PLD。依照这个标准，PROM、PLA、PAL 和 GAL 器件属于低密度 PLD，而 EPLD、CPLD 和 FPGA 属于高密度 PLD。

图 2.1 PLD 按集成度分类

### 2.1.3 PLD 的优点

尽管 PLD 在制作工艺、结构和性能等方面存在很大的不同之处，但是它们都是由用户通过编程来决定其最终功能的逻辑器件。随着科技的不断发展和制作工艺的不断进步，PLD 在性能上有了巨大地提升。PLD 的出现和发展使得传统的电子系统设计方法得以改变，并在现代电子系统的设计当中发挥着重要的作用。由于 PLD 自身的特点，所以它具有不同于固定逻辑器件的优点。

### 1. 研制周期短

对于固定逻辑器件，设计人员根据器件复杂性的不同，从设计、原型到最终生产所需要的时间可从数月至1年多不等。如果器件工作不符合要求，或者应用要求发生了变化，那么开发者需要重新开发全新的设计。而对于PLD，设计人员可利用价格低廉的软件工具快速开发、仿真和测试其设计，这使得PLD的设计非常便捷，能够在短时间内达到我们的编程目标，从而缩短了产品的研制周期。

### 2. 设计成本低

固定逻辑器件在从芯片制造厂制造出来以前，客户需要投入的所有成本，这些成本包括工程资源、昂贵的软件设计工具、用来制造芯片不同金属层的昂贵光刻掩膜组，以及初始原型器件的生产成本。这些费用动辄数万元，并且只有在生产批量很大的情况下才有价值。在生产时，如果器件工作不符合要求或者应用要求发生变化，那么会产生巨额的损失。相比较而言，如果采用PLD，设计者可快速将设计编程到器件中，并立即在实际运行的电路中对设计进行测试，从而降低了投资风险。在设计阶段，设计者可以根据客户的需求通过编程修改电路，直到对设计工作感到满意为止。一旦设计完成，便能立即进行生产，这也比采用固定逻辑器件的成本要低。

### 3. 设计具有灵活性

PLD在设计过程中具有很大的灵活性，因为对于PLD的设计者来说，设计者只需要反复地对编程文件进行简单的修改就可以了，而且设计改变的结果可立即在工作器件中看到，因此设计者可以及时发现设计当中的问题，便于设计者对设计进行完善。事实上，由于有了PLD，设计者甚至可以为已经安装在现场的产品增加新功能或者进行升级。要实现这一点，只需要通过因特网将新的编程文件下载到PLD当中就可以在系统中创建出新的硬件逻辑。

## 2.1.4 PLD的发展趋势

随着市场对大量精密但相对成本较低的终端产品的需求日益增加，设计工程师需要利用速度更快、密度更高和相对更经济的IC产品，这使得PLD在现代电子系统设计当中的位置越来越重要。在未来的发展当中，PLD主要朝着以下几个方向发展。

### 1. 高密度、低压、低功耗

由于当今社会对便携式应用产品的需求越来越大，对PLD的高密度、低压、低功耗要求越来越高。随着集成电路制造技术的不断发展，PLD已经从最初的几百门发展到了现在的几百万门，而且PLD还在不断地向着更高密度的水平发展。伴随着节能潮流的兴起，很多公司也把降低功耗作为产品设计的目标。如Xilinx公司把越来越多的硬核加入到FPGA之中，以此来改进PLD的性能，从而提高速度、降低功耗。

### 2. IP内核库更完善，IP内核的重用更加成熟

由于通信系统越来越复杂，PLD的设计也越来越复杂，这要求IP库的资源能够高效地完成复杂片上系统设计，因此就要求IP核进一步的完善。而IP内核的重用又是SOPC发展的重要条件，IP内核丰富与重用是以后PLD追求的一个目标。

### 3. 向系统可重构的方向发展

系统内可重构是指可编程 ASIC 在置入用户系统后仍可以具有改变内部功能的能力。我们可以像软件那样通过编程来改变系统内部的硬件功能，这样便会使得电子系统的设计和升级变得非常简单，进一步增强了电子系统的灵活性和适应性，从而给现代复杂的电子系统设计和实现提供更加便利的途径。

### 4. 向高速可预测延时器件的方向发展

随着信息化的到来，现代电子系统需要处理越来越多的数据，这就要求数字系统需要具备大的数据吞吐量和高速数据处理能力。只有具备高速的硬件系统和高速的系统时钟，电子系统才能完成对多媒体数字图像的处理。因此，PLD 朝着高速发展是必然的趋势。又因为用户在进行系统重构时，可能会因为重新布线而导致系统的延时特性发生改变，从而造成重构后的系统不稳定，而不稳定的系统带来的损失也是无法想象的，所以为了保证高速系统的稳定性，PLD 的延时预测性也是十分重要的。

### 5. 向混合编程技术发展

自 PLD 发展以来，有关 PLD 的研究和开发大部分都是针对数字逻辑电路，在未来几年这一局面将有所改变，模拟电路和数模混合电路的可编程技术将得到进一步的发展。将系统可编程模拟技术引进模拟电路的应用领域，为现代电路与系统的设计开拓了更为广阔的前景。与实现逻辑功能的数字在系统可编程大规模集成电路一样，设计者通过使用电子设计自动化软件在计算机上设计、修改模拟电路、进行电路特性的仿真，最后将编程文件下载到芯片当中。PLD 的出现节省了试验和开发的时间，提高了设计的效率，使得模拟电子系统的设计和数字系统的设计变得一样简便，将成为今后模拟电子电路设计的一个发展方向。

## 2.2 简单 PLD 的结构原理

简单的 PLD (SPLD) 主要包括 PROM、PLA、PAL 和 GAL 等早期出现的一些低密度 PLD，这些逻辑器件的主要特点是易于编程，对开发软件的要求低，逻辑规模比较小，在 20 世纪 80 年代得到了广泛的应用。

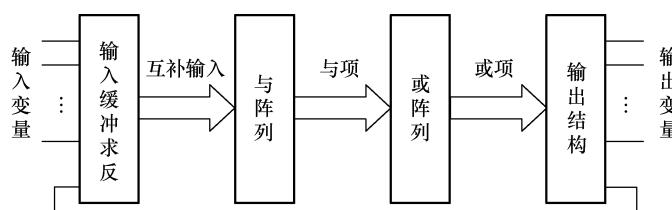

PLD 的基本结构是由与阵列、或阵列、输入电路和输出电路组成，如图 2.2 所示。其中，与阵列和或阵列是电路的主体，主要用来实现组合逻辑函数。输入电路主要是对输入信号进行预处理，输入电路使输入信号具有足够的驱动能力，并产生互补输入信号。输出电路主要用来对输出信号进行处理，它可以提供不同的输出方式。

图 2.2 PLD 的基本结构

## 2.2.1 逻辑符号表示方法

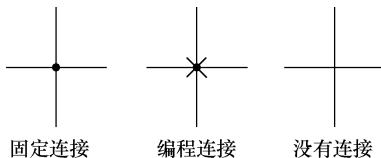

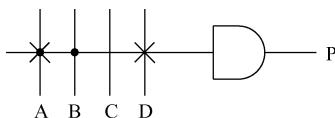

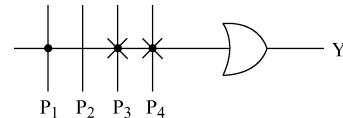

为了更为方便地介绍简单 PLD 器件的结构原理，我们首先了解一些常用的电路符号。由于 PLD 的特殊结构，表示内部结构的符号和通用的逻辑门符号之间存在一定的差别。基于 PLD 电路设计的需要，我们分别来介绍输入互补缓冲器电路符号、与门的表示方法以及或门的表示方法。在 PLD 电路设计中，存在 3 种连接表示方法，用于表示固定连接、编程连接和没有连接，若列线与行线相交的交叉处有“·”，表示有一个耦合元件固定连接（即不可编程）；若有“×”，则表示是编程连接（即可编程）；若交叉处无标记，则表示没有进行连接，如图 2.3 所示。

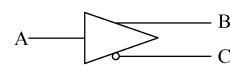

图 2.4 所示是 PLD 电路中最简单和常用的输入互补缓冲器电路符号，输入信号 A 经过输入缓冲电路后，提供原始变量 B 和反变量 C。

图 2.3 电路连接表示

图 2.4 PLD 的互补缓冲器

与门的输出称为乘积项，图 2.5 中与门输出为  $P = ABD$ 。

或门也可以采用类似的方法表示，也可以采用传统的方法表示，图 2.6 中的或门输出为  $Y = P_1 + P_3 + P_4$ 。

图 2.5 与门的表示方法

图 2.6 或门的表示方法

## 2.2.2 PROM 的结构原理

可编程只读存储器是 20 世纪 70 年代初期出现的第一代 PLD，它除了可以用作只读存储器，也可以用作 PLD 使用。

PROM 的内部结构由固定的与阵列和可编程的或阵列组成。在 PROM 基础上，先后出现了紫外线擦除可编程只读存储器 EPROM 和电擦写可编程只读存储器 E<sup>2</sup>PROM。

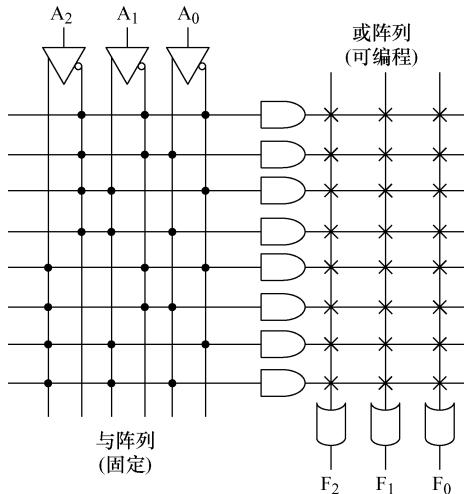

PROM 作为 PLD 阵列时其逻辑阵列如图 2.7 所示。 $A_0$ 、 $A_1$ 、 $A_2$  是输入信号，经过输入缓冲电路，产生互补信号。PROM 经过 8 个不可编程的与阵列分别产生  $A_0$ 、 $A_1$ 、 $A_2$  最小项，然后再经过可编程的或阵列选择需要的最小项进行或运算。例如要实现  $F_1 = A_0 A_2$ ，则经过编程的 PROM 结构如图 2.8 所示。

若 PROM 有  $n$  个输入变量，则 PROM 会产生  $2^n$  个最小项（乘积项），随着输入变量的增加，PROM 阵列的规模按 2 的幂次增加。因此 PROM 受到结构的限制，多输入变量的组合逻辑函数不适合用单个 PROM 来编程表达。

图 2.7 PROM 阵列结构

图 2.8 用 PROM 实现组合逻辑功能

### 2.2.3 PLA 的结构原理

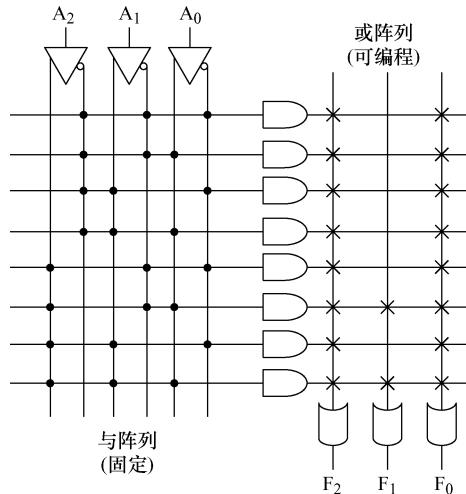

用 PROM 实现组合逻辑函数，输入变量的增加会引起存储容量的增加，芯片的利用率大大降低。因此，在 PROM 等 PLD 器件以后，出现了结构更加灵活的可编程逻辑器件，产品主要是可编程逻辑阵列 (Programmable Logic Array, PLA)。PLA 对 PROM 进行了改进，能够完成各种数字逻辑功能。

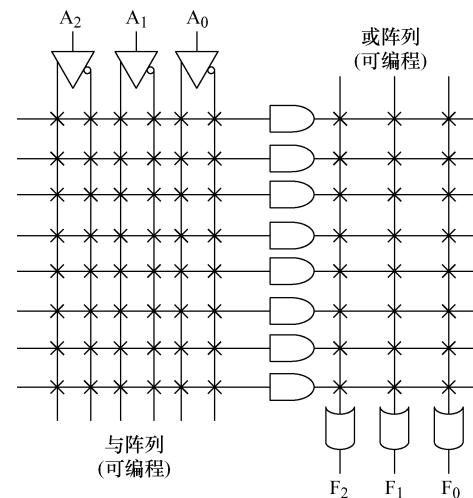

与 PROM 不同，PLA 的与阵列和或阵列都可以编程，PLA 的阵列结构如图 2.9 所示。PLA 使用时需要有逻辑函数的最简与或表达式，虽然这使得芯片的利用率很高，但是对于多输出函数需要提取、利用公共的与项，涉及的软件算法比较复杂，尤其对多输入多输出逻辑函数的处理上就更加困难。除此之外，由于 PLA 的两个阵列均需要编程，将不可避免地使编程后器件的运行速度降低，因此，受到限制的 PLA 只可以在小规模逻辑上应用。如今，PLA 的芯片已经被淘汰了，但在全定制 ASIC 设计中仍然借鉴其面积利用率较高的优势，逻辑函数的化简则由设计者手工完成。

图 2.9 PLA 的阵列结构

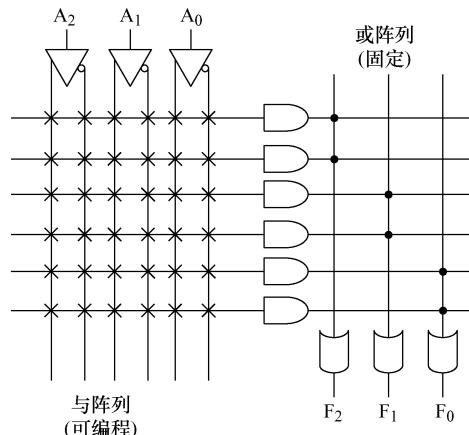

### 2.2.4 PAL 的结构原理

虽然 PLA 的芯片利用率很高，但是其与阵列和或阵列都可以编程的特点造成软件算法过于复杂，运行速度慢。人们在 PLA 之后又推出了可编程阵列逻辑 (Programmable Array Logic, PAL)。与 PLA 的结构相似，PAL 的结构中也包含与阵列、或阵列，不同的是 PAL 的或阵列是固定的，与阵列是可编程的。PAL 的阵列结构如图 2.10 所示。

### 1. PAL 器件的基本结构

PAL 的与阵列可编程、或阵列的固定结构，避免了 PLA 存在的一些问题，大大简化了设计的算法，运行速度得到了提高。PAL 的阵列结构使得送到或门的乘积项数目是固定的，这不但大大简化了设计的算法，也使得单输出的乘积项数有限。

与阵列和或阵列只能实现组合逻辑电路，而对于时序电路却无能为力。因为时序电路是由组合电路以及存储单元（锁存器、触发器等）构成，所以我们只要在已经解决的组合电路部分之上加上锁存器和触发器等就可以实现时序电路。因此，PAL 在输出电路部分增加了寄存器单元用于完成时序电路功能。

PAL 器件是在 PLA 器件之后第一个具有典型实际意义的可编程逻辑器件。PAL 和 SSI (Small – Scale Integration)、MSI (Middle – Scale Integration) 通用标准器件相比具有以下优点：

- (1) 提高了功能密度，节省了空间。通用一片 PAL 可以代替 4 ~ 12 片 SSI 或 2 ~ 4 片 MSI。

- (2) 提高了设计的灵活性，并且编程和使用都比较方便。

- (3) 在器件中加入了上电复位功能和加密功能，可以防止非法复制。

不同型号的 PAL 具有不同的 I/O 结构，因此，PAL 的应用设计者在设计不同功能的电路时，需要根据功能的不同来选择不同 I/O 结构的 PAL，这种情况使得 PAL 的生产和使用很不方便。此外，PAL 采用熔丝编程技术的工艺进行生产，只可以进行一次编程，使得修改很不方便。现在 PAL 芯片在实际应用当中已经遭到淘汰，在中小规模的应用中，取而代之的是 GAL。

一般 PAL 器件具有固定的输出和反馈结构，不同型号的 PAL 器件有不同的输出和反馈结构，可以适用于各种组合逻辑电路和时序逻辑电路的设计。

### 2. PAL 器件输出和反馈结构

PAL 器件根据输出及反馈电路的结构可分为几种基本类型，即专用输出的基本门阵列结构、可编程 I/O 结构、寄存（时序）输出结构、“异或”结构和算术选通反馈结构。

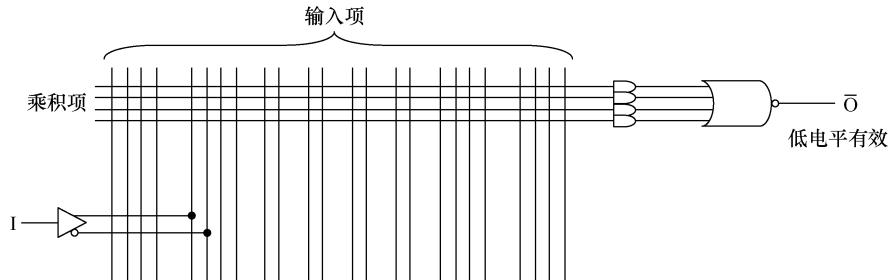

(1) 专用输出的基本门阵列结构 专用输出结构如图 2.11 所示，组合逻辑宜采用这种结构。图中的输出部分采用“或非”门，因而也被称为低电平有效器件；若输出采用“或”门，则称为高电平有效器件；若将输出部分的“或非”门改为互补输出的“或”门，则称为互补输出器件。PAL 器件输出高电平有效，记号为 H，输出低电平有效，记号为 L；互补输出，记号为 C。

在目前常见的 PAL 器件当中，PAL10H8 和 PAL14H4 为“或”门输出结构，PAL10L8 和 PAL10L4 为“或非”门输出结构，PAL16C1 为互补输出结构。

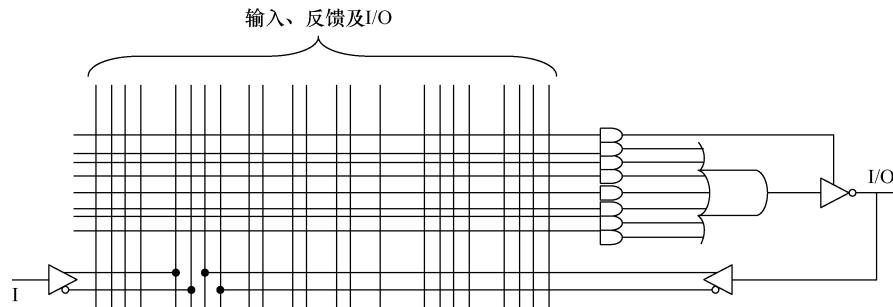

(2) 可编程 I/O 结构 异步可编程 I/O 结构如图 2.12 所示。该电路的“或”门将 7 个乘积项相加，器件输出通过一个三态缓冲器接 I/O 端。三态缓冲器的控制端由最上面一个“与”门来控制。当这个“与”门输出为 '1' 时，三态门被选通，“或”门的输出可以通过缓冲器输出，此时的 I/O 端口作为输出端用，并利用其下方的缓冲器将输出信号反馈到

图 2.10 PAL 的阵列结构

图 2.11 PAL 的专用输出结构

“与”阵列；当“与”门输出作为‘0’时，三态门禁止，即成高阻状态，此时的 I/O 端口只能作为输入端用，外部信号可以通过下面的缓冲器输入到“与”阵列。因此这种结构的引脚既可以作为输出用，又可以作为输入用。另外，在一个 PAL 器件中，两组“与”门的最上面“与”门的输出不一定相同，从而输出函数在时间上可能不一致，此性能称为“异步”。

图 2.12 异步可编程 I/O 结构

目前具有可编程 I/O 结构的 PAL 主要有 PAL16L8、PAL20L10 等。

(3) 寄存(时序)输出结构 寄存(时序)输出结构如图 2.13 所示。这种结构的 PAL 适用于时序电路，与组合输出结构不同的是：“或”门输出到后面一个 D 触发器(上升沿触发)，未直接送回“与”阵列。当系统时钟上升沿到来时，“或”门的输出存入 D 触发器，D 触发器的 Q 端通过三态缓冲器到达输出端，输出端又通过下方的缓冲器反馈到“与”门阵列，这样就使得 PAL 能记忆原先的状态，从而实现时序逻辑功能。另外，该结构中的 D 触发器受系统时钟控制，三态缓冲器受同一系统使能信号控制，所以这种结构容易实现同步逻辑。

图 2.13 寄存(时序)输出结构

具有这种结构的 PAL 主要有 PAL16R8、PAL16R6、PAL16R4 等。PAL16R8 中 8 个输出端都为寄存器型，不含组合输出结构，8 个寄存器输出端同步，属于 Moore 型电路。PAL16R6 中的中间 6 个输出端口属于寄存器结构，因此这 6 个输出端同步，而上下两个输出为组合型，这样 PAL16R6 中既有组合输出结构，又有时序输出结构，可实现 Mealy 型时序逻辑。

(4) “异或”结构 “异或”结构如图 2.14 所示。它的特点是把乘积项分成两个和项，并在寄存器型的基础上增加了一个“异或”门。两个和项经过“异或”门进行“异或”(XOR) 运算后，在系统时钟的上升沿时存入 D 触发器，再从 Q 端经三态缓冲输出。

图 2.14 “异或”结构

属于“异或”输出结构的 PAL 主要有 PAL20X4、PAL20X8、PAL20X10 等。用这种结构的 PAL 可以很方便地实现计数器等。

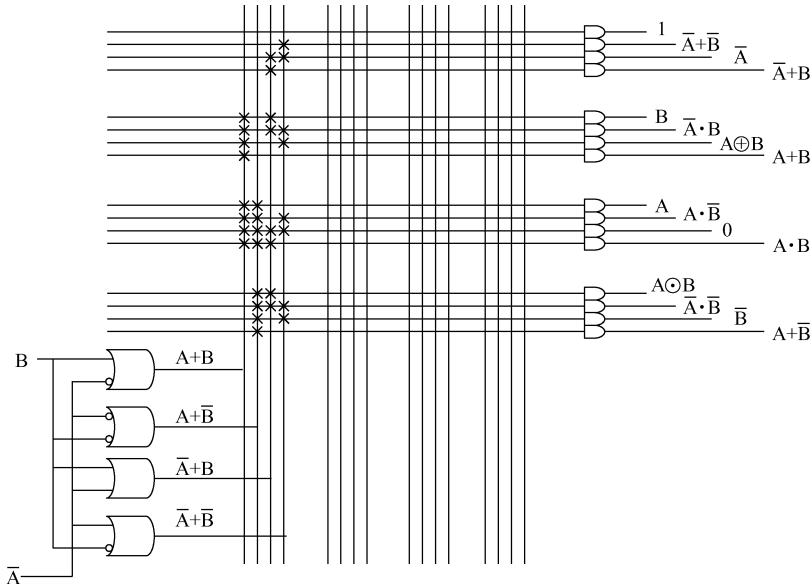

(5) 算术选通反馈结构 算术选通反馈结构如图 2.15 所示。这种结构是在“异或”结构的基础上加入反馈选通电路。该电路可以对反馈信号 A 和输入信号 B 进行逻辑运算，产生 4 种不同形式的“或”门输出分别为  $(A + B)$ 、 $(A + \bar{B})$ 、 $(\bar{A} + B)$  和  $(\bar{A} + \bar{B})$ ，把这 4 种逻辑的结果送到“与”阵列中，使得“与”阵列中的输入含有“或”运算因子，最后通过“与”阵列的编程，可以获得 16 种可能的逻辑组合。图 2.16 表示如何对 PAL 的门阵列编程，以获得 16 种可能的值。

图 2.15 算术选通反馈结构

图 2.16 算术选通电路

算术选通反馈结构的 PAL 器件对实现快速算术操作（如加、减、大于、小于等）很方便。典型的产品有 PAL16A4（8个输入、4个寄存器输出、4个可编程 I/O 输出、4个反馈输入、4个算术选通反馈输入）。此外，PAL 还有乘积项公用输出型，宏单元输出型等输出电路结构类型。

### 3. PAL 器件的命名符号

图 2.17 所示为典型 PAL 器件的符号，各个符号代表着不同的意义：

PAL      C      16      R      8      ××××

① 生产厂家对 PAL 器件的命名，前面一半还有厂家的标志。

图 2.17 典型 PAL 器件的符号

② 代表制造工艺：空白代表 TTL，C 代表 CMOS。

③ 代表 PAL 器件的最大阵列输入数。

④ 代表输出电路类型，如 H 代表高电平输出有效；R 代表带寄存器输出。

⑤ 代表最大的组合输出端数目或最大的寄存器数目。

⑥ 表示器件功耗级别、速度等级、封装形式等信息。

### 4. PAL 器件编号

一般 PAL 器件根据输入输出端口数以及输出结构进行编号，根据 PAL 器件编号的输出结构代码，就可以确定 PAL 器件的输出结构特性。表 2.1 列出了常用的 PAL 器件编号。例如，编号为 PAL16L8 表示该 PAL 器件有 16 个输入端和 8 个输出端的可编程逻辑输入输出组合型，并且为输出端口低电平有效。在有些结构复杂的器件中，还可以采用复合表示法。例如，PAL22RXP10 表示为带有“异或”结构的寄存器输出器件，并且输出极性可编程。

表 2.1 常用的 PAL 器件编号

| 结构代码 | 含    义          | 器件编    号          |

|------|-----------------|-------------------|

| H    | 高电平输出有效         | PAL10H8           |

| L    | 低电平输出有效         | PAL16L8           |

| P    | 输出极性可编程         | PAL16P8           |

| C    | 互补输出            | PAL16C1           |

| X    | 带“异或”门输出或算术选通反馈 | PAL20X10, PAL16X4 |

| R    | 带寄存器输出          | PAL16R8           |

| S    | 带乘积项公用          | PAL20S10          |

| V    | 单元乘积项数目不同或宏单元输出 | PALCE16V8         |

| RA   | 带异步寄存器输出        | PAL16RA8          |

| MA   | 带异步宏单元          | PALCE29MA16       |

## 2.2.5 GAL 的结构原理

1985 年，在 PAL 的基础上，Lattice 公司设计出了通用阵列逻辑器件（Generic Array Logic，GAL）。GAL 在 PAL 之上主要进行了两点改进。首先，GAL 采用了 E<sup>2</sup>PROM 工艺，具有电可擦除重复编程的特点，从根本上解决了熔丝型可编程逻辑器件一次可编程的问题；其次，GAL 对输出 I/O 结构做了很大的改进，其输出部分增加了输出逻辑宏单元（Output Logic Macro Cell，OLMC）。OLMC 设有多种组态，可以配置成为专用组合输出、专用输入、组合双向口，寄存器输出、寄存器输出双向口等，为逻辑电路设计提供了极大的灵活性。

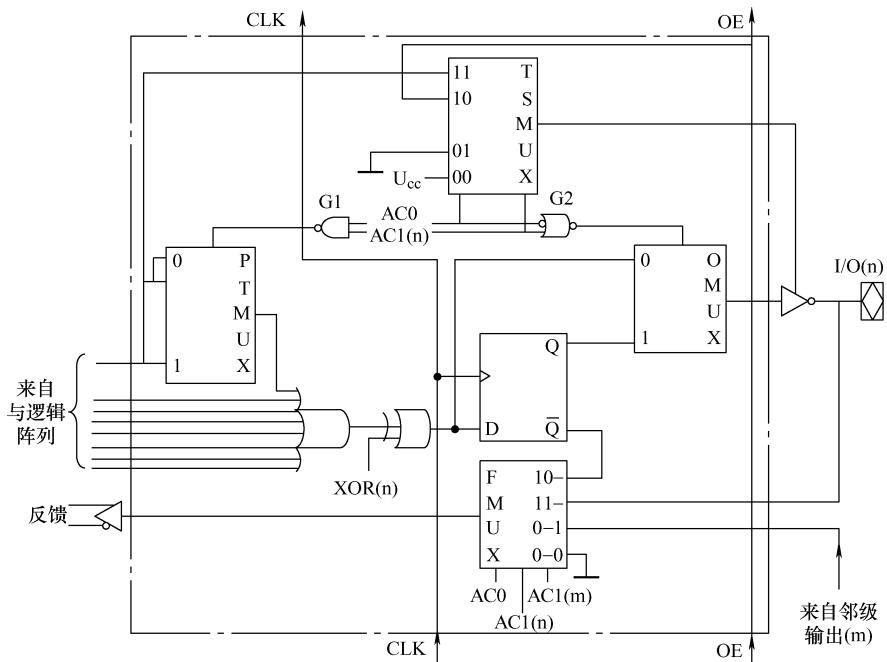

OLMC 作为一种灵活的、可编程的输出结构主要由 1 个或门、1 个异或门，1 个 D 触发器和 4 个数据选择器（MUX）组成。或门有 8 个输入端，可以对 8 个乘积项进行或运算；异或门可以对输出的极性进行选择；D 触发器主要用于存储输出状态和实现时序逻辑功能；数据选择器分别为乘积项选择器（PTMUX）、三态缓冲器使能信号选择器（TSMUX）、输出类型选择器（OMUX）和反馈源选择器（FMUX）。因此，OLMC 可以通过不同的选择方式产生不同类型的输出结构。

### 1. GAL 的基本结构

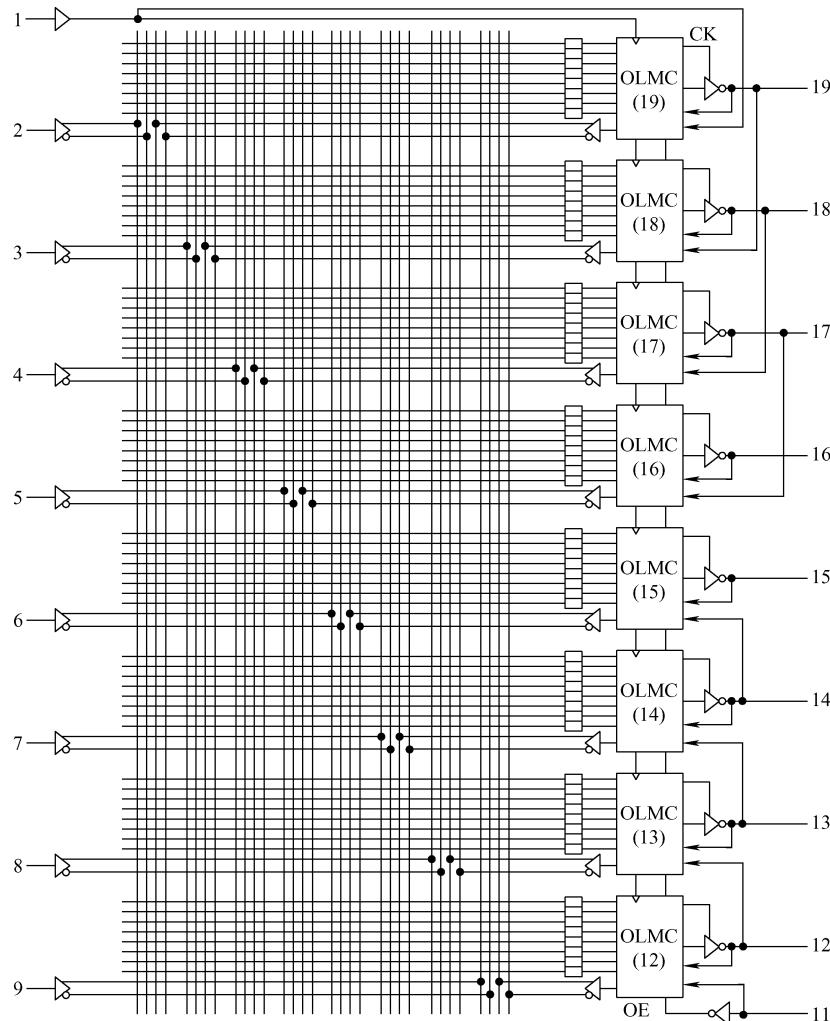

GAL 器件具有基本相同的电路结构，图 2.18 所示为型号为 GAL16V8 器件的结构图。此器件包含了可编程的与阵列、输入三态缓冲器、输出三态缓冲器、输出逻辑宏单元 OLMC、输出反馈/输入缓冲器。其中，与阵列由 8×8 个与门构成，每个与门有 32 个输入端；一个与门对应一个乘积项，共可形成 64 个乘积项；输入三态缓冲器和输出三态缓冲器都有 8 个缓冲器；输出反馈/输入缓冲器也有 8 个缓冲器，分别与 8 个输出逻辑宏单元 OLMC 相连。其中，在此结构中，还包括系统时钟和三态输出选通信号 OE 的输入缓冲器。

在 GAL16V8 中，除了 8 个引脚（2~9）固定作为输入外，它还可能有其他 8 个引脚（1、11、12、13、14、17、18、19）配置成输入模式，此时只能有两个引脚（15、16）作为输出。因此，这类芯片最多可有 16 个引脚作为输入引脚，而输出引脚最多为 8 个（12~19），这就是 GAL16V8 中 16 和 8 这两个数字的含义。

由于 GAL 是在 PAL 基础上设计的，与很多 PAL 器件保持兼容性，一个 GAL 器件能替代多片 PAL 器件，大大方便了应用厂商对现有的产品进行升级，因此，GAL 器件目前仍然被使用。

图 2.18 GAL16V8 器件的结构图

## 2. 输出逻辑宏单元

具有输出逻辑宏单元（OLMC）是 GAL 器件的一大特点。分析和讨论 OLMC 如何配置将有助于更加深刻地理解 GAL 器件。应当指出的是，OLMC 配置的具体实现是由开发工具和软件完成的，并对用户是完全透明的。OLMC 的内部结构如图 2.19 所示。

每个 OLMC 包含“或”门阵列中的 1 个“或”门。1 个“或”门有 8 个输入端，和来自“与”阵列的 8 个乘积项（PT）相对应。其中 7 个直接相连，第一个乘积项与 PTMUX 相连，“或”门输出为有关乘积项之和。“异或”门用于控制输出函数的极性。当结构控制字中 XOR (n) 字段为 1 时，“异或”门的输出和“或”门的输出相反。XOR (n) 是控制字的一位，n 为引脚号。D 触发器（寄存器）对“异或”门的输出状态起记忆（存储）作用，使 GAL 适用于时序逻辑电路。4 个多路开关（MUX）在结构控制字段作用下设定输出逻辑宏单元的组态。其作用分别为：

- (1) 乘积项数据选择器（PTMUX）也是一个二选一数据选择器。它根据结果控制字中的 AC0 和 AC1 (n) 字段的状态决定来自“与”逻辑阵列的第一个乘积项是否作为“或”

图 2.19 OLMC 的内部结构

门的第一个输入。当  $AC0AC1(n) = 00, 01$  或  $10$  时,  $G1$  门输出为 '1', 第一个乘积项作为“或”门的第一个输入; 当  $AC0AC1(n) = 11$  时,  $G1$  门输出为 '0', 第一个乘积项不作为“或”门的第一个输入。

(2) 输出数据选择器 (OMUX) 是一个二选一数据选择器。它根据结构控制字中的  $AC0$  和  $AC1(n)$  字段的状态决定 OLMC 是组合输出模式还是寄存器输出模式。当  $AC0AC1(n) = 00, 01$  或  $11$  时,  $G2$  门输出为 '0', “异或”门输出的“与-或”逻辑函数经输出数据选择器的 '0' 输入端, 直接送到输出三态缓冲寄存器; 当  $AC0AC1(n) = 10$  时,  $G2$  门输出为 '1', “异或”门输出的“与-或”逻辑函数寄存在  $D$  触发器中, 其  $Q$  端输出的寄存器结果送到输出数据选择器 (OMUX) 的 '1' 输入端后, 再送到输出三态缓冲器。

(3) 三态数据选择器 (TSMUX) 是一个四选一数据选择器。它的输出是输出三态缓冲器的控制信号。换言之, 输出数据选择器 (OMUX) 的结果能否出现在 OLMC 的输出端, 是由 TSMUX 的输出来决定的。从图中可以看出。 $AC0, AC1(n)$  是 TSMUX 的地址输入信号,  $Ucc$ 、地、 $OE$  和来自“与”逻辑阵列的第一个乘积项是 TSMUX 的数据输入信号。它们之间的关系见表 2.2。

表 2.2 TSMUX 的控制功能表

| $AC0$ | $AC1(n)$ | TSMUX 输出 | 输出三态缓冲器的工作状态                             |

|-------|----------|----------|------------------------------------------|

| 0     | 0        | $U_{cc}$ | 工作态                                      |

| 0     | 1        | 地        | 高阻态                                      |

| 1     | 0        | $OE$     | $OE = 1$ 时, 为工作态<br>$OE = 0$ 时, 为高阻态     |

| 1     | 1        | 第一个乘积项   | 第一个乘积项 = 1 时, 为工作态<br>第一个乘积项 = 0 时, 为高阻态 |

(4) 反馈数据选择器 (FMUX) 是一个八选一数据选择器。它的地址输入信号是 AC0、AC1 (n)、AC1 (m) (n 表示本级 OLMC 编号, m 表示邻级 OLMC 编号); 它的数据输入信号只有 4 个, 分别是: 地、邻级 OLMC 输出、本级 OLMC 输出和 D 触发器的输出  $\bar{Q}$  端。显然, 它的作用是根据 AC0、AC1 (n)、AC1 (m) 的状态, 在 4 个数据输入信号中选择其中一个作为反馈信号接回到“与”逻辑阵列中。FMUX 的控制功能见表 2.3。

表 2.3 FMUX 的控制功能表

| AC0 | AC1 (n) | AC1 (m) | 反馈信号                 |

|-----|---------|---------|----------------------|

| 1   | 0       | ×       | 本级 D 触发器 $\bar{Q}$ 端 |

| 1   | 1       | ×       | 本级 OLMC 输出           |

| 0   | ×       | 1       | 邻级 OLMC 输出           |

| 0   | ×       | 0       | 地                    |

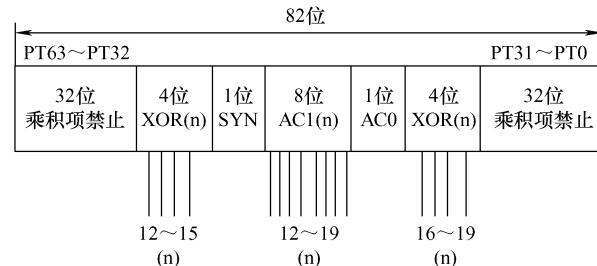

### 3. 结构控制字

GAL16V8 器件的各种配置是由结构控制字来控制的。GAL 的结构控制字共 82 位, 每位取值为‘1’或‘0’, 如图 2.20 所示。图中 XOR (n) 和 AC1 (n) 字段下的数字对应各个 OLMC 的引脚号。

结构控制字各位功能如下:

(1) 同步位 SYN 决定 GAL 器件是具有寄存器型(时序型)输出能力( $SYN=0$ ), 还是纯粹组合型输出能力( $SYN=1$ )。在 GAL 开始编程时首先确定 SYN 的状态。

(2) 结构控制位 AC0 只有 1 位, 8 个 OLMC 共用此位, AC0 和每个 OLMC

(n) 中的 AC1 (n) 配合在一起控制 OLMC (n) 中的 4 个数据选择器。

(3) 结构控制位 AC1(n) 共有 8 位, 每个 OLMC (n) 有各自的 AC1 (n), 这里, n 代表 OLMC 的输出端编号。例如, 对于 GAL16V8 来说, n 取 12~19。

(4) 极性控制位 XOR (n) 有 8 位, 每个 OLMC (n) 有各自的 XOR (n)。它通过 OLMC 里的“异或”门来控制每个 OLMC 的输出极性。 $XOR (n)=0$ ; 输出信号  $O(n)$  低电平有效;  $XOR (n)=1$ , 输出信号  $O(n)$  高电平有效。

(5) 乘积项 (PT) 禁止位共有 64 位, 分别屏蔽“与”阵列 64 个乘积项 (PT0~PT63) 中某些不用的乘积项。在 SYN、AC0、AC1 (n) 组合的控制下, OLMC (n) 可组态配置成 5 种工作模式, 表中列出了各种模式下对控制位的配置和选择。

从以上分析可以发现 GAL 器件由于采用了 OLMC, 所以使用更加灵活, 只要写入不同的结构控制字, 就可以得到不同类型的输出电路结构。这些电路结构完全可以取代 PAL 器件各种输出电路结构。

### 4. GAL 器件的行地址映射图

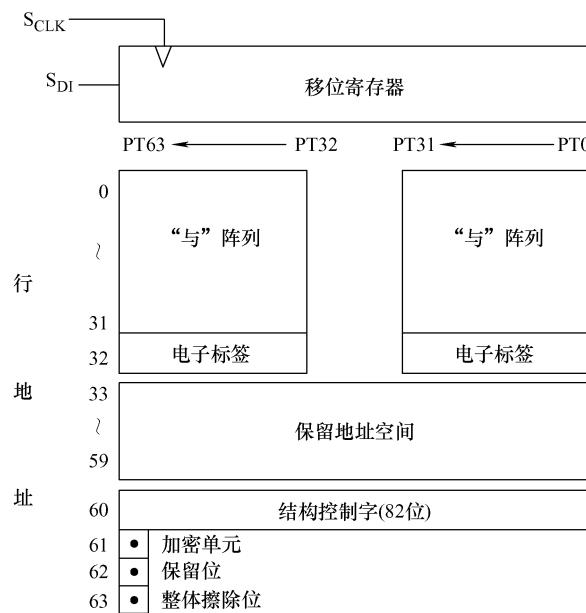

当用户对 GAL 器件编程时, 除了对“与”阵列编程外, 还要对各个 OLMC 中的结构控制

图 2.20 GAL16V8 的结构控制字

字、电子标签、加密、擦除方式等进行编程，所以有必要了解编程单元的地址分配情况。GAL16V8 编程单元的地址分配如图 2.21 所示。因为它并不是变成单元实际的空间分布图，所以又把它称为行地址映射图。

用户可用行地址共有 63 个，它们各自的含义如下：

(1) 行地址 0~31 对应“与”阵列的 32 个输入。而每个行地址单元有 64 位，对应“与”阵列的 64 个积项。

(2) 行地址 32 是器件的电子标签字，也有 64 位，供用户存放各种备查信息，如用户或厂家代码、器件编程数据、编程器识别码和模式识别码等信息。用户可以在任何时间读出标签数据，与下述保密单元的状态无关。

(3) 行地址 33~59 是保留给制造厂家使用的地址空间，用户不能使用。

(4) 行地址 60 是结构控制字，共有 82 位，用于设定 8 个 OLMC 的工作模式和 64 个乘积项的禁止。

(5) 行地址 61 是加密单元，只有 1 位。该位一旦被编程，对“与”阵列的任何访问都无效，它可以防止对“与”阵列的再次编程和检验，从而实现对电路设计结果的保密。这个单元只能在整体擦除时和阵列一起擦除，当然它不影响电子标签单元的读出。

(6) 行地址 63 是整体擦除位，只有 1 位。在器件编程器件访问该行地址，意味着执行整体擦除操作，使器件恢复到未使用前的原始状态。

图 2.21 GAL16V8 编程单元的地址分配

## 2.3 CPLD 的结构原理

### 2.3.1 CPLD 的基本结构

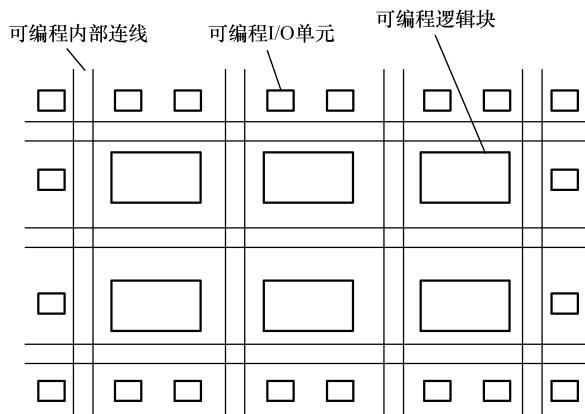

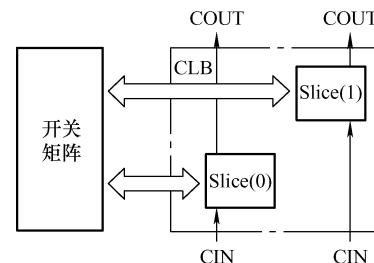

CPLD 是复杂可编程逻辑器件能够实现复杂的数字系统功能。由 GAL 发展起来的 CPLD 的主体仍然是与或阵列，其中与阵列可编程，或阵列固定，称为可编程逻辑宏单元；在器件中心有一个时延固定的可编程连线阵列，逻辑单元之间的互连是由固定长度的金属线来实现的；CPLD 还增加了 I/O 控制模块的数量和功能。CPLD 的基本结构主要由可编程逻辑块 FB (Function Block)、可编程 I/O 单元和可编程内部连线资源 3 部分组成，如图 2.22 所示。

#### 1. 可编程逻辑块

可编程逻辑块被称为可编程逻辑宏单元，它是 CPLD 器件的逻辑组成核心。宏单元内部主要包括与阵列、或阵列、可编程触发器和多路选择器等电路，能够独立地配置为时序逻辑或组合逻辑工作方式。

与 GAL 器件对比来看, CPLD 不但集成度很高, 而且逻辑宏单元也做了很大的改进, 使器件功能得到了极大地增强。

首先, 与 GAL 不同的是, GAL 每个输出逻辑宏单元 OLMC 中只有一个触发器, 而 CPLD 器件的逻辑宏单元内通常含两个或两个以上的触发器, 其中只有一个触发器与输出端相连, 其余的触发器不与输出端链接, 但可以通过相应的缓冲电路反馈到与阵列, 从而与其他触发器一起构成较为复杂的时序逻辑电路, 这些不与输出端连接的触发器叫作“隐埋”触发器, 正是由于这些“隐埋”触发器, CPLD 可以在不增加引脚数目的情况下增加了内部资源。由此可见, 这种多触发器结构和“隐埋”触发器结构使得器件实现时序逻辑功能的能力得以增强。

其次, 在 PAL 和 GAL 的与或阵列中, 每个或门的输入乘积项最多为 8 个, 当要实现多于 8 个乘积项的与或逻辑函数时, 必须将与或函数表达式进行逻辑变换。与之不同, 在 CPLD 的宏单元中, 如果输出表达式的与项较多, 对应的或门输入端不够用时, 可以编程将其他编辑宏单元中的或门与之联合起来使用, 即并联扩展项; 也可以借助编程开关将其他宏单元中未使用的乘积项拿来共享, 即乘积扩展项。可以看出, 这种乘积项共享结构提高了资源利用率, 从而实现了快速复杂的逻辑函数。

除此之外, CPLD 器件中的触发器时钟, 除了可以采用同步时钟外, 还可以采用异步时钟, 这些触发器的时钟可以通过数据选择器或时钟网络进行选择。此外, 各触发器的异步清零和异步置位也可以用乘积项进行控制, 从而使得使用更加灵活。

## 2. 可编程 I/O 单元

CPLD 的可编程 I/O 单元是内部信号到 I/O 引脚的接口部分, 是器件的输入输出单元, 简称 I/O 单元 (或 IOC)。不同器件的 I/O 单元结构有所不同。由于阵列型 HDPLD 通常只有少数几个专用输入端, 如全局清零信号输入、时钟信号输入等, 其余大部分均为 I/O 端, 而且系统的输入信号常常需要锁存, 因此 I/O 常作为一个独立的单元来进行处理。

## 3. 可编程内部连线

CPLD 器件内部具有丰富的可编程内部连线资源, 其可编程内部连线在各逻辑宏单元以及逻辑宏单元与 I/O 单元之间提供了互连网络。各个逻辑宏单元通过可编程内部连线接收来自专用输入端和通用输入端的信号, 并将宏单元的信号反馈到其需要到达的目的地。这种互连机制具有极大的灵活性, 它可以在不影响引脚分配的情况下改变内部的设计。

### 2.3.2 基于乘积项的可编程逻辑器件

Altera 公司的 CPLD 主要有 MAX 系列产品, 包括 MAX3000、MAX7000、MAX II 等产品, 都是非易失性和瞬时接通的器件。MAX3000 和 MAX7000 采用基于乘积项的宏单元体系结构, 下面以 MAX7000 产品为例介绍 Altera 公司基于乘积项的可编程逻辑器件。

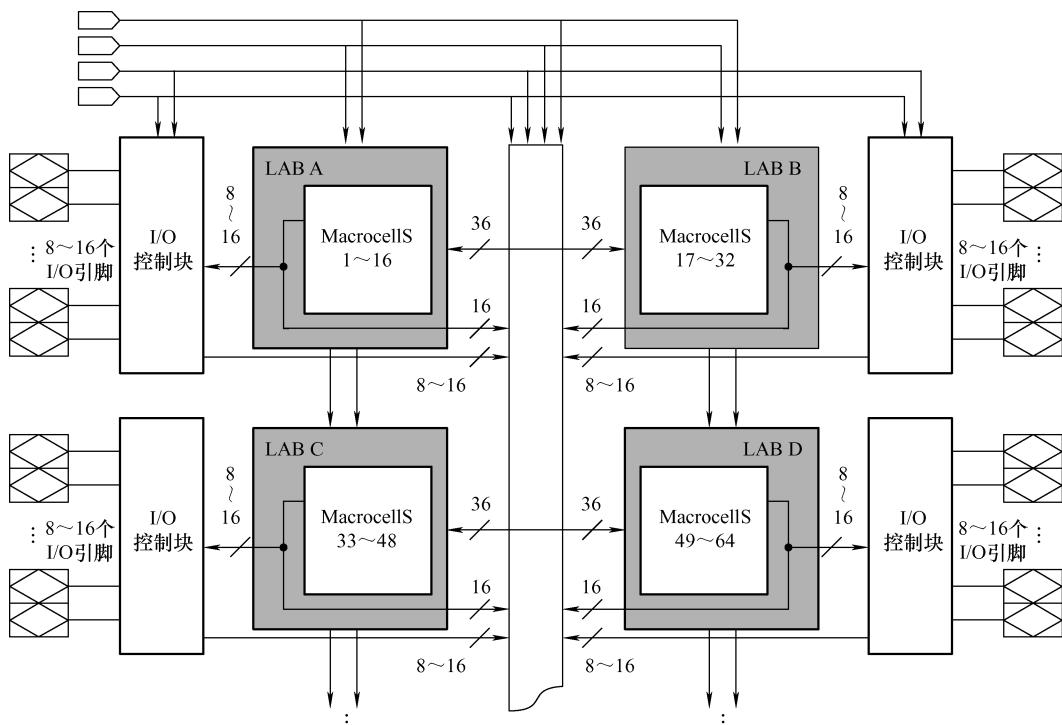

图 2.22 CPLD 的基本结构

MAX7000 由逻辑阵列块 (Logic Array Block, LAB)、可编程连线和 I/O 控制块，每个 LAB 中包含 16 个逻辑宏单元 Macrocell，此外还有 4 个专用输入信号，分别是全局时钟信号  $GLCK_1$ 、全局清零信号  $GCLR_n$  和两个输出使能信号  $OE_1$  和  $OE_2$ ，有专用连线将它们与 CPLD 中的每个宏单元相连，这些信号到每个宏单元的延时相同并且延时最短。

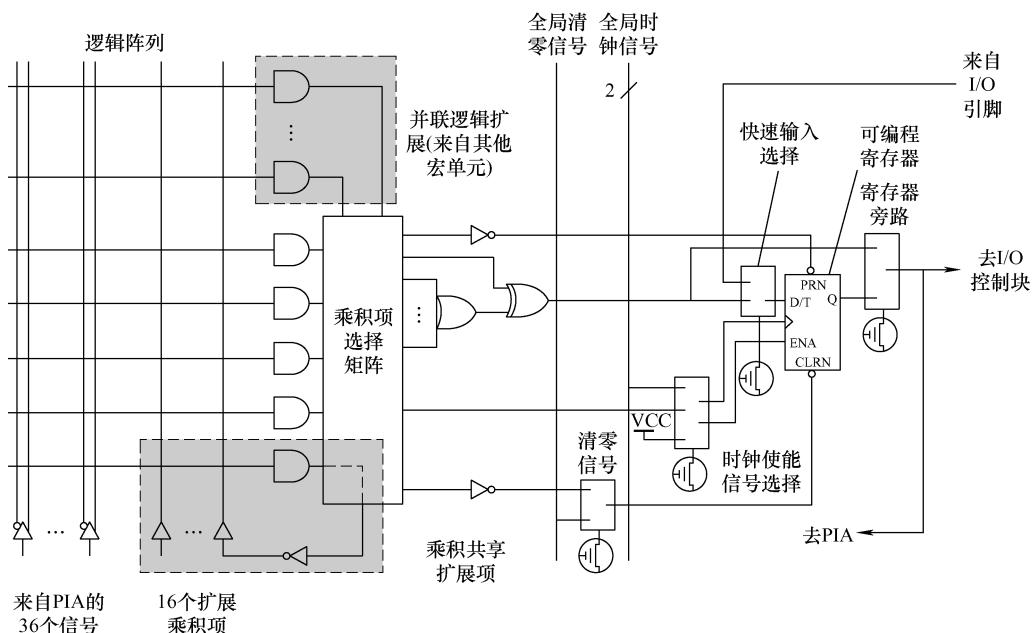

### 1. 逻辑宏单元

逻辑宏单元是 CPLD 的基本结构，由它来实现基本的逻辑功能。每个逻辑阵列块 LAB 包含 16 个逻辑宏单元，接收的信号有来自可编程连线阵列 (Programmable Interconnect Array, PIA) 的 36 个通用逻辑输入信号、用于辅助寄存器功能的全局控制信号、I/O 引脚到寄存器的直接输入信号。

CPLD 的宏单元结构如图 2.23 所示。左侧是乘积项阵列，也就是与或阵列，每一个交叉点都是一个可编程熔丝，如果导通就是实现与逻辑。乘积项选择矩阵对乘积项进行选择让其参加或运算，输出到或阵列，完成组合逻辑。宏单元中有一个可编程 D 触发器，时钟和清零信号输入都可以编程选择，既可以使用专用的全局清零和全局时钟，又可以使用内部逻辑 (乘积项阵列) 产生的时钟和清零。如果不需要触发器，也可以将此触发器旁路，组合逻辑信号直接输给 PIA 或输出到 I/O 引脚。

图 2.23 CPLD 的宏单元结构

乘积项共享扩展项由每个宏单元提供一个未投入使用的乘积项，将其反相后反馈到逻辑阵列中，以便于集中使用，每个共享扩展项可以被所在 LAB 内任意宏单元使用和共享，以实现复杂的逻辑功能，每个 LAB 有 16 个共享扩展项。并联扩展允许最多 20 个乘积项直接送到宏单元的或阵列中，其中 5 个由宏单元本身提供，其余 15 个并联扩展项由该 LAB 中邻近的宏单元提供。采用共享扩展项和并联扩展项都会增加一个时延。

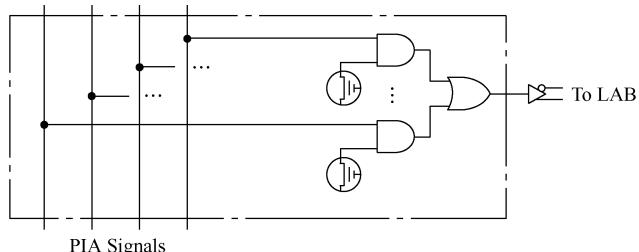

## 2. 可编程连线

可编程连线阵列（PIA）负责信号传递，连接所有宏单元和I/O控制块的全局总线，使得在器件全部范围内获得信号。专用输入信号、I/O单元和逻辑宏单元的输出均送到可编程连线阵列，PIA把各个LAB相互连接构成所需的逻辑，再把这些信号送到器件内的各个地方。MAX7000器件的PIA具有固定的时延，因此消除了信号之间的延迟偏移，容易预测系统的时间性能。可编程的E<sup>2</sup>PROM单元控制2输入与门，从而选择来自PIA的信号送入LAB。可编程连线阵列如图2.24所示。

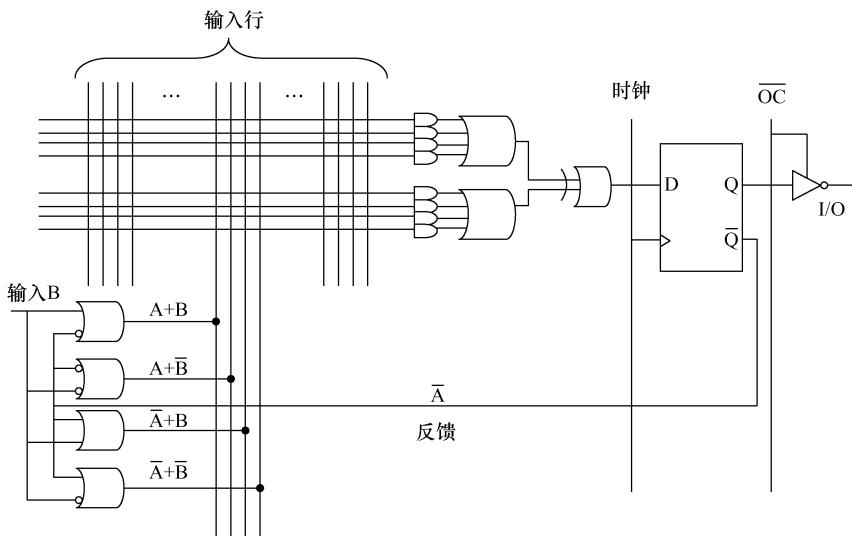

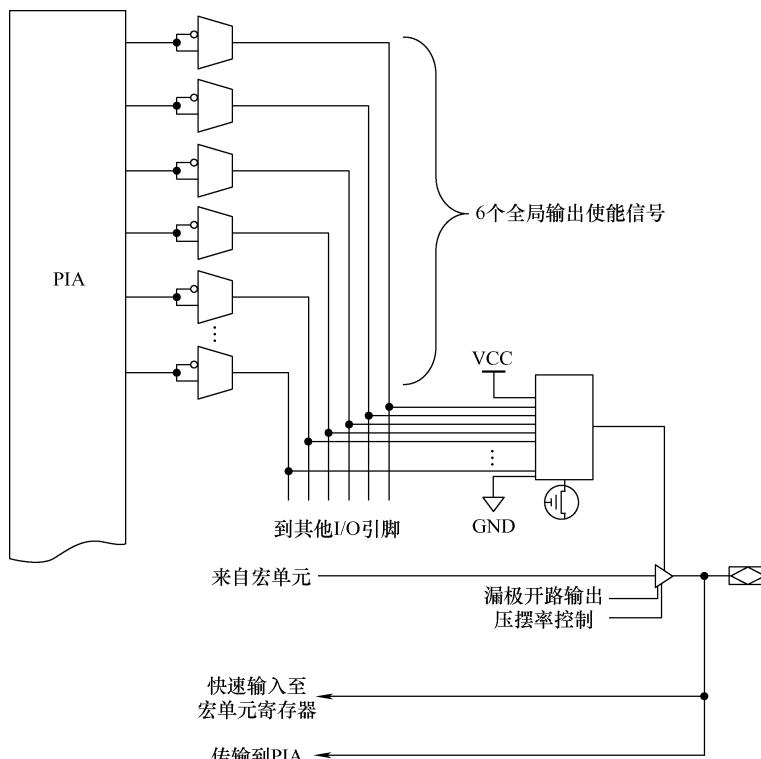

### 3. I/O控制块

I/O控制块允许每个引脚独立配置成输入、输出或双向工作方式。所有的I/O引脚都有一个三态缓冲器。三态缓冲器既能用全局输出使能控制，又能够用高低电平直接控制。当三态缓冲器控制端接地时，输出成高阻态，引脚被设置成输入，信号可以快速输入到宏单元的寄存器，也可以输入到PIA。当三态缓冲器控制端接到高电平时，引脚输出使能，可以控制其漏极开路输出，也可以对信号的压摆率进行控制。压摆率越大，信号的转换速度越快，但功耗也就越大，若用户将器件设置为低功耗模式，只需要少部分重要的逻辑门工作在高频率上即可。MAX7000的I/O控制单元如图2.25所示。

图2.24 可编程连线阵列

图2.25 MAX7000的I/O控制单元

## 2.4 FPGA 的结构原理

FPGA 是 20 世纪 80 年代中期出现的高密度 PLD。在 1985 年，Xilinx 公司首家推出 FPGA 器件之后，FPGA 不断向集成度更高、速度更快、价格更低、功耗更小的方向发展。FPGA 与 CPLD 都是可编程逻辑器件，虽然它们都是在 PAL、GAL 等逻辑器件的基础上发展起来的，但是与 PAL、GAL 等相比较，FPGA 和 CPLD 的规模比较大，可以替代几十甚至上千块通用的 IC 芯片。这类 FPGA 和 CPLD 实际上就是一个子系统部件，深受电子工程设计人员的广泛关注和普遍欢迎。

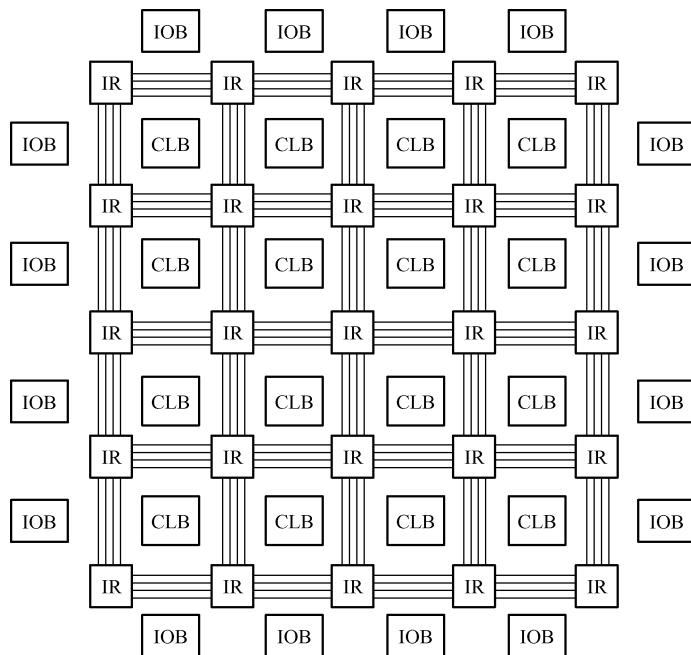

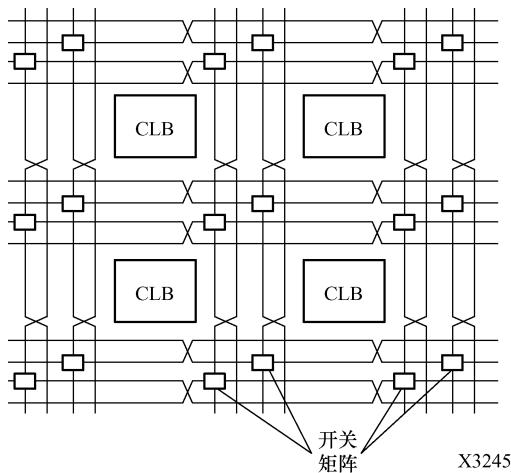

FPGA 具有掩膜可编程门阵列的通用结构，它由逻辑功能块排成阵列，并由可编程的互连资源连接这些逻辑功能块实现不同的设计。下面以 Xilinx 公司的 FPGA 为例，分析其结构特点。典型的 FPGA 结构主要由可编程逻辑块（Configurable Logic Block, CLB）、可编程输入/输出模块（Input/Output Block, IOB）、可编程内部连线资源（Interconnect Resource, IR）组成。如图 2.26 所示。

图 2.26 FPGA 的基本结构

### 1. 可编程逻辑块（CLB）

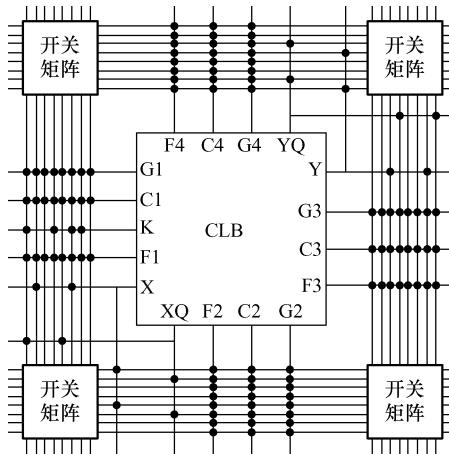

可编程逻辑块（CLB）是实现逻辑功能的基本逻辑单元，它们通常规则地排列成一个阵列，散布于整个芯片中；可编程输入输出模块 IOB 主要完成芯片上的逻辑与外部封装引脚的接口，通常排列在芯片的四周，允许通过编程配置为输入、输出或双向工作 3 种方式；可编程互连资源 IR 包括各种长度的连线线段和一些可编程连接开关，它们将各个 CLB 之间或 CLB、IOB 之间以及 IOB 之间连接起来，从而可以构成各种特定功能的电路。由此可见，如果希望改变芯片的功能只需要改变 CLB 的设置或 CLB 与 IOB 之间的连接就可以了。FPGA 的功能由逻

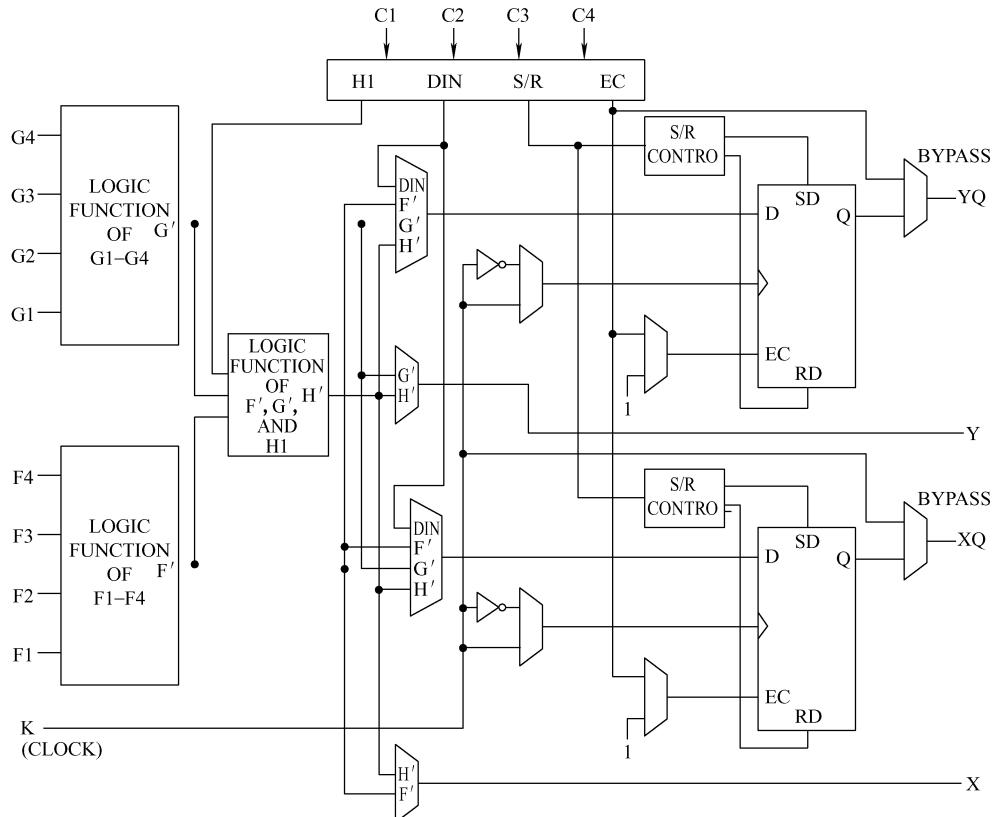

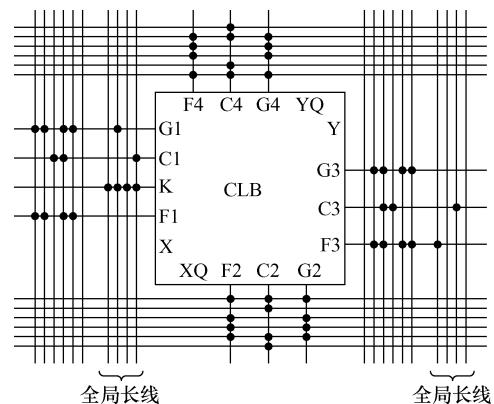

辑结构的配置数据决定。工作时，一般配置数据存放在芯片内部的 SRAM 之中，一旦系统掉电后信息就会丢失，因此，大部分的 FPGA 一定需要外加一片专用配置芯片，如 EPROM、E<sup>2</sup>PROM 等。FPGA 器件在工作前需要从芯片外部加载配置数据，然后 FPGA 就可以正常工作了，由于配置时间很短，不会影响系统正常工作。此外，也存在少数的 FPGA 采用反熔丝或 Flash 工艺，对这种 FPGA 就不需要外加专用的配置芯片。CLB 的基本结构如图 2.27 所示。

图 2.27 CLB 的基本结构

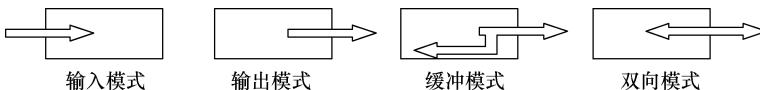

## 2. 可编程输入/输出模块 (IOB)

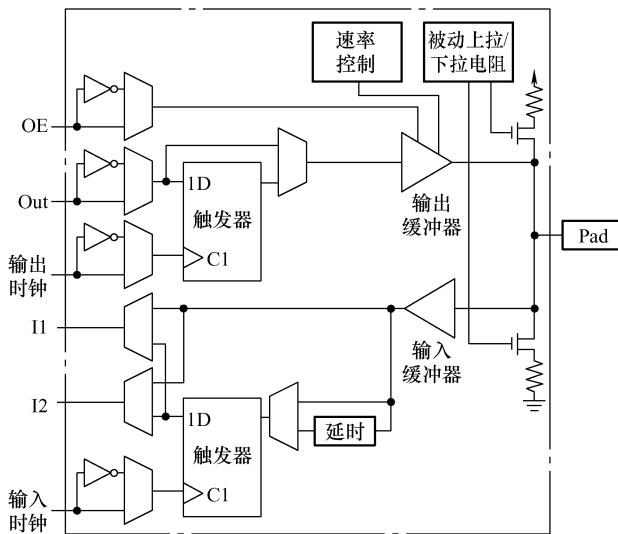

可编程输入输出模块分布于 FPGA 器件的四周，提供了器件引脚与内部逻辑阵列之间的连接，可以通过编程灵活地实现不同的功能。IOB 主要由输入触发器、输入缓冲器和输出触发器/锁存器、输出缓冲器组成，每个 IOB 控制一个引脚，它们可以被配置为输入/输出或双向 I/O 功能。如图 2.28 所示为 IOB 的基本结构。

## 3. 可编程内部连线资源 (IR)

可编程内部连线资源将 CLB 的输入、输出之间，CLB 与 CLB 之间，CLB 和 IOB 之间连接起来，从而使 FPGA 能够形成各种功能复杂的系统。IR 主要由许多金属线段构成，这些金属线段带有可编程开关，通过自动布线实现各种电路的连接。布线时，我们可以选择单长线或双长线连接，单长线是贯穿于 CLB 之间的垂直和水平金属线段，长度分别等于相邻 CLB 的行距和列距，提供了相邻 CLB 之间的快速互连和复杂互连的灵活性，任意两点间的连接都要通过开关矩阵。单长线结构如图 2.29 所示。

图 2.28 IOB 的基本结构

图 2.29 单长线结构

双长线用于将两个不相邻的 CLB 连接起来，长度是单长线的两倍，需要经过两个 CLB 之后，才通过开关矩阵。双长线结构如图 2.30 所示。

无论是单长线还是双长线，信号的传输都要经过开关矩阵，这使得信号的传输存在延时，所以对于某些重要的信号，我们可以通过专用长线进行传输，专用长线并不经过开关矩阵，其长度可以跨越整个芯片。由此可见，FPGA 器件的内部时延与器件结构以及逻辑布线等存在很大的联系，信号传输时延是不可以确定的。长线结构如图 2.31 所示。

图 2.30 双长线结构

图 2.31 长线结构

## 2.4.1 查找表型 FPGA 的逻辑结构

基于查找表（Look – Up Table，LUT）结构的 PLD 芯片也可以称为 FPGA，LUT 本质上就是一个 RAM。目前 FPGA 中多使用 4 输入的 LUT，所以每一个 LUT 可以看成一个有 4 位地址

线的  $16 \times 1$  的 RAM。当用户通过原理图或 HDL 语言描述了一个逻辑电路以后，PLD/FPGA 开发软件会自动计算逻辑电路的所有可能的结果，并把结果事先写入 RAM。这样，每输入一个信号进行逻辑运算就等于输入一个地址进行查表，找出地址对应的内容，然后输出即可。

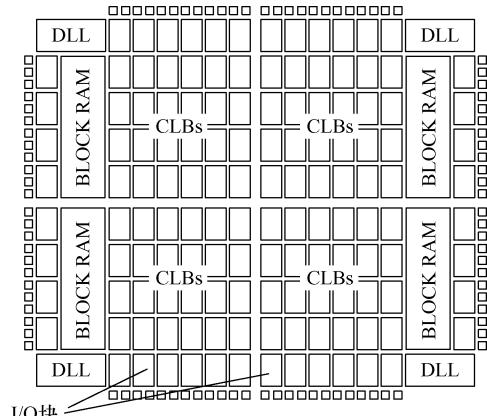

Xilinx 公司的 Spartan - II 主要包括 CLBs、I/O 块、RAM 块和可编程连线（未表示出）。在 Spartan - II 中，一个 CLB 包括两个 Slices，每个 Slices 包括两个 LUT，两个触发器和相关逻辑。Slices 可以看成是 Spartan - II 实现逻辑的最基本结构（Xilinx 其他系列，如 SpartanXL、Virtex 的结构与此稍有不同，具体请参阅数据手册）。图 2.32 所示是 Spartan II 芯片的内部结构。

Altera 公司的 FLEX/ACEX 的结构主要包括 LAB、I/O 块、RAM 块（未表示出）和可编程行/列连线。在 FLEX/ACEX 中，1 个 LAB 包括 8 个逻辑单元（LE），每个 LE 包括 1 个 LUT、1 个触发器和相关逻辑。LE 是 FLEX/ACEX 芯片实现逻辑的最基本结构（Altera 其他系列，如 APEX 的结构与此基本相同，具体请参阅数据手册），因此，LE 的个数也是衡量 PLD 集成度的参数，1 个 LE 主要由 4 个查找表（LUT）和 1 个可编程触发器，再加上一些辅助电路组成。如图 2.33 所示为 Altera 公司的 FLEX/ACEX 等芯片的结构。

图 2.32 Xilinx 公司 Spartan II 芯片的内部结构

实现逻辑的最基本结构（Altera 其他系列，如 APEX 的结构与此基本相同，具体请参阅数据手册），因此，LE 的个数也是衡量 PLD 集成度的参数，1 个 LE 主要由 4 个查找表（LUT）和 1 个可编程触发器，再加上一些辅助电路组成。如图 2.33 所示为 Altera 公司的 FLEX/ACEX 等芯片的结构。

图 2.33 Altera 公司的 FLEX/ACEX 等芯片的结构

由于 FPGA 内部存在着丰富的可编程互连资源，这使得 FPGA 的可编程具有很大的灵活性，如果互连线资源缺乏将会导致设计无法布线，从而降低 FPGA 的可用性。随着 FPGA 工艺的不断改进，设计中的布线延时往往超过逻辑延时，因此，FPGA 内部互连线的长短和快慢，对整个设计的性能起着决定性的作用。

## 2.4.2 Xilinx 公司 7 系列 FPGA 简介

Xilinx 公司有两大类 FPGA 产品：Spartan 类和 Virtex 类，前者主要面向低成本的中低端应用，是目前业界成本最低的一类 FPGA；后者主要面向高端应用，属于业界的顶级产品。但是这两个系列芯片内部的布局布线、时钟管理以及其他模块有着很大的区别，开发人员在不同平台切换的时候，往往要对代码进行修改。这就降低了开发的速度，因此 Xilinx 公司在 7 系列芯片中采用统一的架构，帮助开发人员快速地完成设计在不同平台的切换。下面介绍 Xilinx 公司 7 系列芯片的结构特点及工作原理。

该系列芯片应用了全新的高级硅模组块（Advanced Silicon Modular Block，ASMBL）架构。该架构将功能模块分布成可互换的列，而不是以前的栅格平面。为了尽量满足各种应用的需要，7 系列芯片又分为 3 个子系列：Artix - 7 系列具有低成本低功耗的特点，主要面向大批量的小型化设计；Kintex - 7 系列对性价比做了优化，在提高性能的同时兼顾了成本；Virtex - 7 系列拥有最高的系统性能，是一款高容量的芯片，适用于高端设计。用户可以根据自己的需要选择适合自己应用的 FPGA。

### 1. 可配置逻辑模块

7 系列芯片根据型号的不同 CLB 的资源也是不同的，但是它们都有着共通的结构可以实现设计的转移。一个 CLB 模块包括两个 Slice，每个 Slice 中都含有 4 个 LUT、8 个寄存器以及其他多路选择器和进位逻辑等电路，CLB 的结构如图 2.34 所示。

FPGA 芯片中有很多 CLB，CLB 之间的关系如图 2.34 所示。多个 CLB 可以组合完成复杂的任务。在 CLB 中有两种 Slice 分别是 SLICEM 和 SLICEL。每个 LUT 都可以配置成 6 输入的 LUT 或者 2 个 5 输入的 LUT，每个 LUT 的输出都可以存储在寄存器中。只有 SLICEM 可以配置成 64 位的分布式 RAM、32 位的移位寄存器或者是 16 位移位寄存器。在应用设计的过程中，FPGA 的综合工具会自动地使用 CLB 的资源而不需要开发人员对 FPGA 进行特殊的编程，使用基本的 HDL 的编程语言就可以完成高效的设计。

只有 CLB 中的 SLICEM 中的 LUT 可以配置为分布式 RAM，以 LUT 作为分布式 RAM 的存储单元。分布式 RAM 又分为单端口分布式 RAM、双端口分布式 RAM 以及四端口分布式 RAM。单端口 RAM 指读和写共享相同的地址线；双端口 RAM 又可以配置成两种，一种是一个端口负责同步的读和写，另一个端口负责异步的读入操作；另一种是一个端口负责同步写操作，另一个端口负责异步读操作；四端口只一个端口负责同步写操作和异步读操作，另外 3 个端口负责异步读操作。除此之外，SLICEM 也可以用来配置成移位寄存器，该寄存器

图 2.34 Xilinx 公司的 7 系列 CLB 的结构

不需要使用 SLICEM 中的寄存器单元。SLICEM 中的每个 LUT 都可以配置成 32 位的移位寄存器，因此一个 SLICEM 最多可以配置成 128 位的移位寄存器。

CLB 中的 SLICEM 和 SLICEL 都可以用来配置成 ROM，使用 1 个 LUT 可以实现  $64 \times 1$  的 ROM，使用 4 个 LUT 组合则可以实现  $256 \times 1$  的 ROM。CLB 中的 SLICEM 和 SLICEL 也可以用来实现多路选择器。每一个 LUT 都可以配置成 4 : 1 多路选择器（MUX），因此每个 Slice 可以实现 4 个 4 : 1 多路选择器、2 个 8 : 1 多路选择器或者 1 个 16 : 1 多路选择器。为了进行快速的数学加减运算，CLB 中有专门的快速进位逻辑。每个 Slice 中有 1 条进位链，Slice 中的进位链使用超前进位逻辑结构，每个进位链有 10 个独立的输入以及 8 个独立的输出。

## 2. 存储器资源

该系列芯片根据型号的不同内含 25 ~ 1880 个 36KB 双向 RAM 块。这些 RAM 块可以被组合配置成  $32K \times 1$ 、 $16K \times 2$ 、 $8K \times 4$ 、 $4K \times 9$ （或 8）、 $2K \times 18$ （或 16）、 $1K \times 36$ （或者 32）以及  $512 \times 72$ （或者 64）等不同模式的 RAM 块。32KB 的 RAM 块也可以分成两个完全独立的 18K RAM 块来使用。两个端口是相互独立的，可以被配置成可配置的宽度，也就是说两个端口的宽度可以是不同的。通过内置的 FIFO 控制器，每一个 RAM 块也可以被配置成 18KB 或者是 36KB 的 FIFO。在读入过程中，每 64 位宽的 RAM 块可以生成、存储以及利用 8 位额外的汉明码来生成 1 位或者 2 位的错误检测码（ECC），ECC 可以在 64 位到 72 位宽 RAM 的写入过程或者读出过程中使用。

除了分布式 RAM 和高速 SelectIO™ 存储接口以外，7 系列芯片也有很多 36KB 的块 RAM。每个 36KB 的块 RAM 由 2 个独立的 18KB 的块 RAM 组成。这些 36KB 的块 RAM 可以级联构成更大宽度和深度的块 RAM。

利用块 RAM 也可以用来配置成同步时钟 FIFO 以及双时钟的 FIFO。FIFO 可以配制成 18KB 模式和 36KB 模式。在 18KB 模式下可以配置成  $4K \times 4$ 、 $2K \times 9$ 、 $1K \times 18$  和  $512 \times 36$  等模式；在 36KB 模式下可以配置成  $8K \times 4$ 、 $4K \times 9$ 、 $2K \times 18$ 、 $1K \times 36$  以及  $512 \times 72$  等模式。FIFO 可以有不同的读写时钟，比如读操作可以在读时钟的上升沿进行，写操作可以在写时钟的上升沿进行，在没有额外 CLB 模块逻辑的支持下，FIFO 是不支持不同的读写位宽的。

ECC 是错误纠正模块，可以用来检测 RAM 数据中的 1 位或者是 2 位的错误，同时在读出数据的时候可以纠正 1 位错误。块 RAM 以及块 RAM 配置成的 FIFO 都支持 64 位的 ECC（Error Correction Code）。在写入的过程中，校验位就可以自动生成，在读出过程中，这些校验位就被送到 ECC 译码器中进行校验，可以去纠正 1 位错误或者是检测 2 位错误。当检测出 1 位错误并且改正后，并不会去修改 RAM 中的数据，只是将修改后的结果存储到输出寄存器中。ECC 的标准模式是编码器和译码器都使用，在写入数据的时候生成校验码，在读出数据的时候在译码器里进行校验、检测和纠正错误。同时编码器和译码器也可以单独使用。

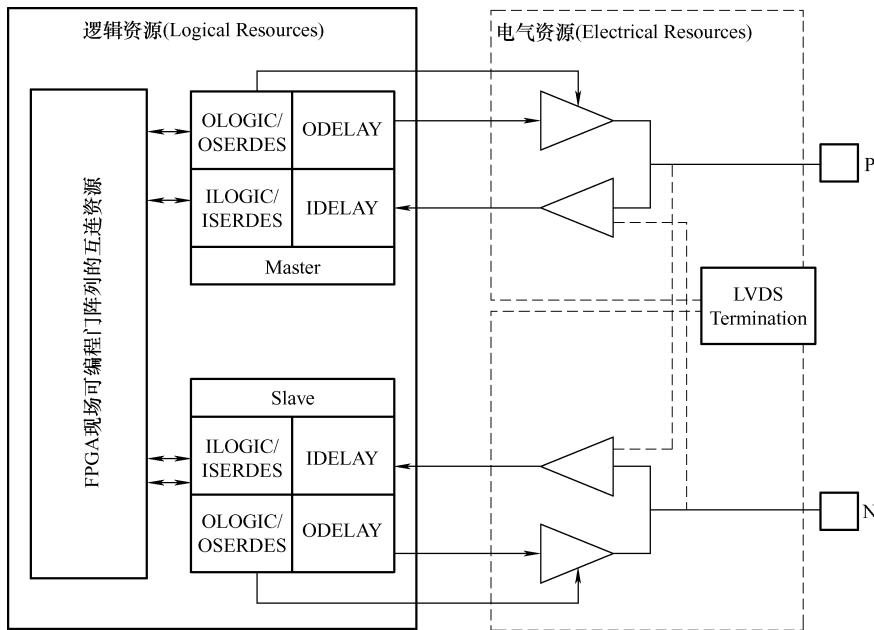

## 3. I/O 模块

7 系列 I/O 主要由逻辑资源和电气资源两部分组成，支持 1.2 ~ 3.3V 的电压范围，并且支持 40 多种点评标准。可配置成单端、差分或三态模式。最高性能在 LVDS 模式下可达 1600Mbit/s，在单端模式下用于 DDR3 可达 1866Mbit/s。同时在 IOB 内部还集成了 DCI 功能，在引脚提供特定的阻抗匹配，简化单板设计，增加设计的集成度。7 系列的 IOB 结构如图 2.35 所示。

图 2.35 7 系列的 IOB 结构

7 系列 FPGA 内部，I/O 模块是按列分布的，分为高范围（High Range, HR）和高性能（High Performance, HP）两种类型。HR 类型的 I/O 支持 3.3V 电平，而 HP 类型的 I/O 最高只支持 1.8V 电平。不同系列的 FPGA，每种类型的 I/O 所占的比例对于不同的 7 系列器件不大一样。I/O 模块在器件内部以 Bank 形式划分，每个 Bank 有 50 个 I/O。在同一个 Bank 中的所有 I/O 电平都必须一致，是由 Vcco 所控制。并且在同一个 Bank 中只有一个 Vref（参考电压），只有一对 Vrn/Vrp（用于 DCI 阻抗匹配）。

IOB 逻辑资源包含 Master 和 Slave 两个模块。每个模块包括 ILOGIC/ISERDES、OLOGIC/IDELAY 和 ODELAY 组件。

**ILOGIC:** HP Bank 中命名 ILOGIC2，HR Bank 中命名 ILOGIC3，可直接输入或通过 IDELAY 模块输入，直接输出或通过 IDDR 模块输出。

**OLOGIC:** HP Bank 中命名为 OLOGIC2，HR bank 中命名为 OLOGIC3，可直接输出或通过 ODELAY 模块输出。

**ISERDES:** 输入串并转换器，可实现 2, 3, 4, 5, 6, 7, 8 位 SDR 数据转化或 4, 6, 8 位 DDR 数据的转化，如需实现更宽的数据位转换，可将 Master 和 Slave 级联，最高实现 14 位的数据转化。

**OSERDES:** 输出并串转换器，可实现 2, 3, 4, 5, 6, 7, 8 位 SDR 数据转化或 4, 6, 8 位 DDR 数据的转化，如需实现更宽的数据位转换，可将 Master 和 Slave 级联，最高实现 14 位的数据转化。当使用 3 态模式的数据转换，数据和 3 态数据位宽必须为 4，此时时钟是共享的。

**IDELAY:** 在 HR 和 HP Bank 中都有。

**ODELAY:** 只存在于 HP Bank 中。

IOB 的延迟是通过 IDELAYCTRL 模块来控制实现，共分为 32tap 的延迟是 78ps (200MHz) 或 52ps (300MHz)，用户可以设定延迟 tap 参数。

#### 4. DSP 模块

7 系列 FPGA 的 DSP 模块由很多专用的、充分定制的低功耗 DSP Slice 构成，突出功能包括： $25 \times 18$  的补码乘法器，高分辨率 48 位累加器，用于对称滤波器应用的低功耗预加器以及一些高级功能（可选流水线、可选 ALU 和级联专用线）。

每一个 DSP Slice 都有一个专用的  $25 \times 18$  的补码乘法器、一个 48 位累加器、48 位的模式检测器（Pattern Detector）以及一个用于对称滤波器应用的预加器，乘法器和累加器最高可支持 741MHz 的时钟频率。DSP Slice 可以完成多种操作，乘法、乘累加、乘加、三输入加法、桶型移位、按位逻辑功能、计数功能、量值比较、模式选择等。

根据型号的不同，7 系列 FPGA 有 60 ~ 3600 个 DSP Slice，它们也可以级联，应对更复杂的数字信号处理应用。

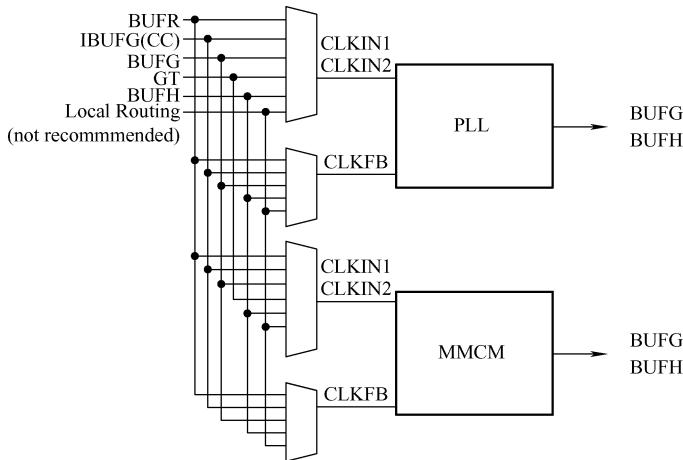

#### 5. 时钟资源和时钟管理模块

Xilinx7 系列芯片的时钟资源分为全局时钟资源和区域时钟资源。全局时钟资源是一种专用的互联网络，可以实现芯片内部的时钟同步。全局时钟有着降低时钟歪斜、占空比失真和功耗，提升抖动容限等特点，并且全局时钟资源有着专用的时钟缓冲和驱动结构，可以是全局时钟到达 CLB、IOB 和 BRAM 的时间延迟最小，但是在芯片内部只有 32 条全局时钟线。区域时钟资源是独立于全局时钟网络的，7 系列芯片将内部分割成若干时钟区域，根据芯片的大小，时钟区域的数目从最小 4 个时钟区域到最大 24 个时钟区域。在每个时钟区域内部可以完成各自的时钟同步。一个时钟区域只能通过 12 条全局时钟线，因为区域内只有 12 条水平时钟线可以使用。一般来说，每个时钟区域有 50 个 CLB、10 个 36KB 块 RAM、20 个 DSP Slice 和 12 个 BUFG，但是有些时钟区域还有一个时钟管理模块（CMT）、一个 I/O 模块（50 个 IO）、一个 GT 条（其中包括 4 个串行收发器）和一个 PCIe（PCIe 会占用 5 个 36KB 块 RAM 的位置）。

在整个芯片中有一条垂直时钟线，将整个芯片分成左右两个区域，相当于树干。水平时钟中线将芯片分割成上下两个相邻的部分，每个时钟区域的水平时钟脊梁（HROW）将各自的区域分割成上下两个部分，每个水平时钟脊梁内包含 12 条水平时钟线，它们则相当于枝干，共同构成复杂的时钟网络。

每个 I/O 模块都有时钟输入引脚，配合专用的时钟缓存器，可以将用户时钟引入到 FPGA 芯片的时钟网络中来。比如，全局时钟缓冲（Global Clock Buffer）驱动着全局时钟线，水平时钟缓冲（Horizontal Clock Buffer）可以使全局时钟线连接到区域时钟资源的水平时钟线上等。芯片内的时钟路由资源可以帮助完成芯片内各种各样的时钟调度，比如高扇出的、低传播延迟的、低歪斜的等。为了更有效率地完成时钟调度，我们必须要充分了解芯片内部的时钟资源，比如缓冲器类型、时钟输入引脚、时钟连通性等内容。选择合适的时钟资源不仅可以节约资源而且可以提高性能。

时钟管理模块（Clock Management Tile，CMT）由一个混合模式时钟管理器（Mixed – Mode Clock Manager，MMCM）和一个锁相环（Phase – Locked Loop，PLL）构成，在功能上，PLL 是 MMCM 的一个子集，CMT 的结构如图 2.36 所示，图中左侧是多种时钟输入资源。

在 7 系列芯片中有 24 个时钟管理模块，MMCM 和 PLL 可以作为宽范围的频率合成器，也可以作为抖动滤波器和抗扭斜时钟。当 MMCM 和 PLL 作为单独的频率合成器时，分频因子可以是整数也可以是小数，通过对对应的可编程分频因子配置来实现。MMCM 和 PLL

图 2.36 CMT 的结构图