# ARM处理器开发详解

基于ARM Cortex-A8处理器的开发设计

清华大学出版社 刘洪涛 邹南 编著

## 本书特色

关注理论知识和实践操作，重视实践的综合性强

内容基于流行的Cortex-A8 ARM处理器

丰富的实训项目并提供源码

所有的实验源码都通过FS-JTAG板验证

IFS\_SOPC1000验证平台验证

电子工业出版社

高等院校嵌入式人才培养规划教材

# ARM处理器开发详解

基于ARM Cortex-A8处理器的开发设计

■ 华清远见嵌入式学院 刘洪涛 邹南 编著

电子工业出版社

Publishing House of Electronics Industry

北京•BEIJING

## 内 容 简 介

作为一种 32 位高性能、低成本的嵌入式 RISC 微处理器，ARM 目前已经成为应用最广泛的嵌入式处理器。目前 Cortex-A 系列处理器已经占据了大部分中高端产品市场。

本书在全面介绍 Cortex-A8 处理器的体系结构、编程模型、指令系统及开发环境的同时，以基于 Cortex-A8 的应用处理器——S5PC100 为核心，详细介绍了系统的设计及相关接口技术。接口技术涵盖了 I/O、中断、串口、存储器、PWM、A/D、DMA、IIC、SPI、Camera、LCD 等，并提供了大量的实验例程。

本书可以作为高等院校电子、通信、自动化、计算机等专业的 ARM 体系结构、接口技术课程的教材，也可作为嵌入式开发人员的参考书。

未经许可，不得以任何方式复制或抄袭本书之部分或全部内容。

版权所有，侵权必究。

### 图书在版编目（CIP）数据

ARM 处理器开发详解：基于 ARM Cortex-A8 处理器的开发设计 / 刘洪涛，邹南编著.—北京：电子工业出版社，2012.9

ISBN 978-7-121-17714-9

I . ①A… II . ①刘… ②邹… III. ①微处理器—系统设计 IV. ①TP332

中国版本图书馆 CIP 数据核字（2012）第 168402 号

策划编辑：胡辛征

责任编辑：许 艳

特约编辑：赵树刚

印 刷：北京中新伟业印刷有限公司

装 订：

出版发行：电子工业出版社

北京市海淀区万寿路 173 信箱 邮编 100036

开 本：787×1092 1/16 印张：18 字数：460 千字

印 次：2012 年 9 月第 1 次印刷

印 数：4000 册 定价：49.00 元

凡所购买电子工业出版社图书有缺损问题，请向购买书店调换。若书店售缺，请与本社发行部联系，联系及邮购电话：(010) 88254888。

质量投诉请发邮件至 [zlts@phei.com.cn](mailto:zlts@phei.com.cn)，盗版侵权举报请发邮件至 [dbqq@phei.com.cn](mailto:dbqq@phei.com.cn)。

服务热线：(010) 88258888。

# 前　　言

随着消费群体对产品要求的日益提高，嵌入式技术在机械器具制造业、电子产品制造业、信息通信业、信息服务业等领域得到了大显身手的机会，并被越来越广泛地应用。ARM 作为一种 32 位的高性能、低成本的嵌入式 RISC 微处理器，已得到最广泛的应用。目前，Cortex-A 系列处理器已经占据了嵌入式处理器大部分的中高端产品市场，尤其是在移动设备市场上，几乎占据了绝对垄断的地位。

伴随着 Android 系统的发展，ARM 也越来越被大家所了解和接受，企业对 ARM 技术人才的需求也越来越大。各高校也已经认识到了这一点，并设置了相关课程。但建立一套完整的嵌入式教学课程，是一项非常复杂的工作，尤其是如何和企业需求相结合，更是高校所需要面临的重大问题。目前市场上的嵌入式开发相关书籍大多是针对研发人员编写的，并不太适合高校教学使用。北京华清远见科技信息有限公司长期以来致力于嵌入式培训，为市场输送了大量的嵌入式人才。为了普及嵌入式技术，公司计划着手针对高职院校的特点编写一套嵌入式教材。教材的内容涵盖 ARM 体系结构、接口技术、Linux 操作系统、Linux C 语言及 Linux 应用开发实训。本书重点讲解 ARM 体系结构及接口技术部分。

在学习本书之前，读者需要具有数字电路、C 语言等基础知识。通过本书的学习，读者可以掌握 ARM 体系结构和基于 Cortex-A8 核心的 S5PC100 处理器常见硬件接口的开发方法。

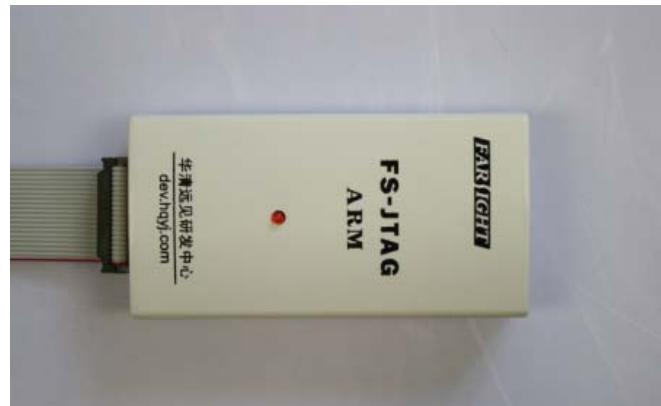

本书以 S5PC100 处理器为平台，介绍了嵌入式系统开发的各个主要环节。本书侧重实践，辅以代码加以讲解，从分析的角度来学习嵌入式开发的各种技术。本书使用的工具是 FS-JTAG 仿真器。FS-JTAG 是华清远见研发中心为了推进 Cortex-A8 ARM 处理器的教学，提高合作企业及合作院校广大技术爱好者和培训学员的学习效率，研发出的低价的可以支持 Cortex-A8 的 ARM 仿真器。

本书将嵌入式软/硬件理论讲解和嵌入式实验实践融合在一起，全书共 16 章。其中，第 1 章为嵌入式系统基础知识，介绍了嵌入式系统的组成及嵌入式开发概述。第 2 章为 ARM 技术概述，讲解了 ARM 体系结构、应用选型及编程模型等。第 3 章为 ARM 微处理器的指令系统，重点介绍了 ARM 指令集。第 4 章为 ARM 汇编语言程序设计，主要介绍了 GUN ARM 汇编伪操作、GNU ARM 汇编支持的伪指令、汇编语言与 C 语言的混合编程。第 5 章为 ARM 开发环境搭建，包括 Eclipse 环境介绍、FS-JTAG 仿真器使用等。第 6 章为 GPIO 编程，介绍了 GPIO 的概念及 S5PC100 的 GPIO 操作方法。第 7 章为 ARM 异常及中断处理，介绍了 ARM 处理器的异常处理及 S5PC100 的中断控制器工作原理。第 8 章为串行通信接口，介绍了串行通信的概念及 S5PC100 串口的操作方法。第 9 章为存储器接口，介绍了 NOR Flash、NAND Flash 存储器的操作方法。第 10 章为定时器与 RTC，介绍了定时器的工作原理及 S5PC100 定时器接口的操作方法。第 11 章为 A/D 转换器，介绍了 A/D 转换器的工作原理及 S5PC100 A/D 控制器的操作方法。

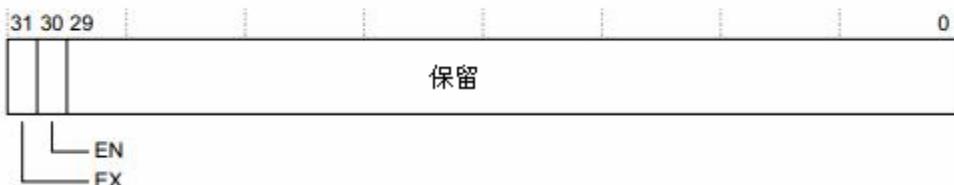

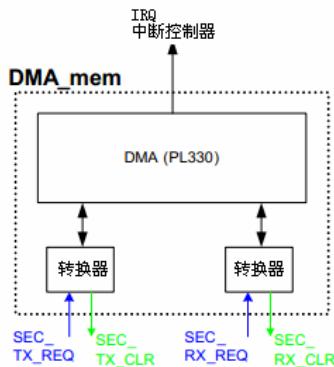

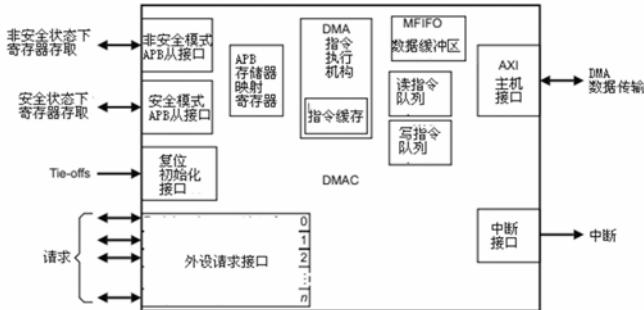

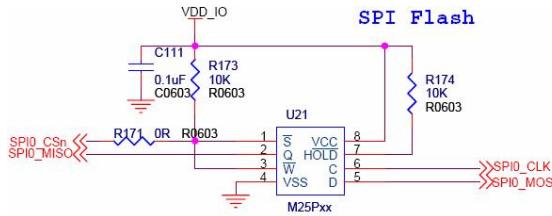

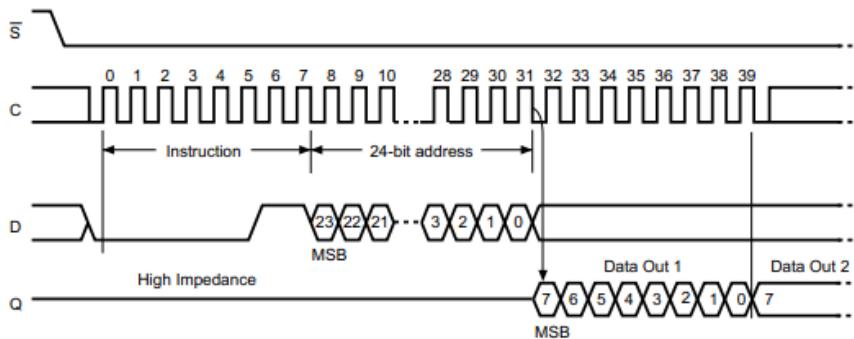

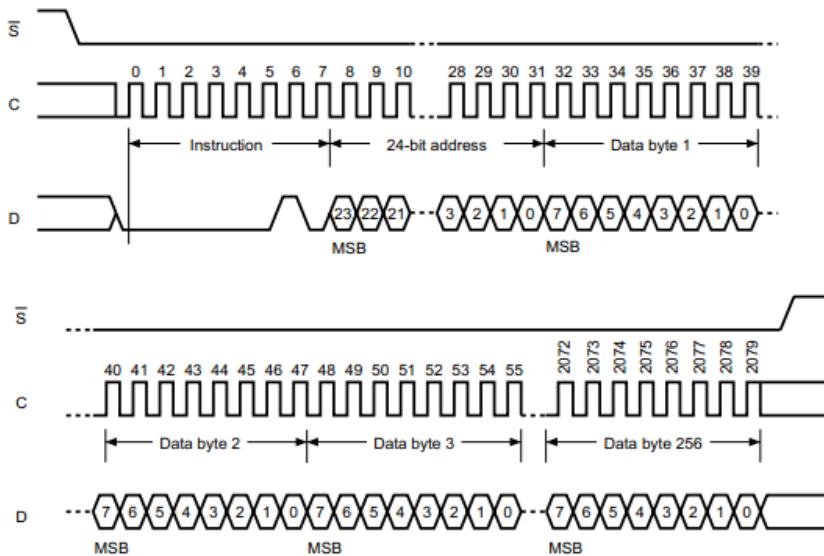

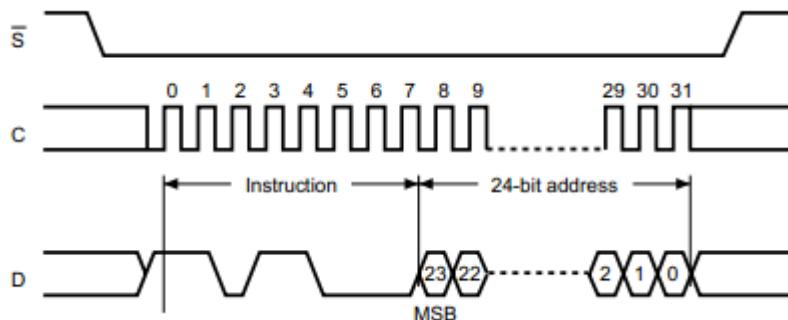

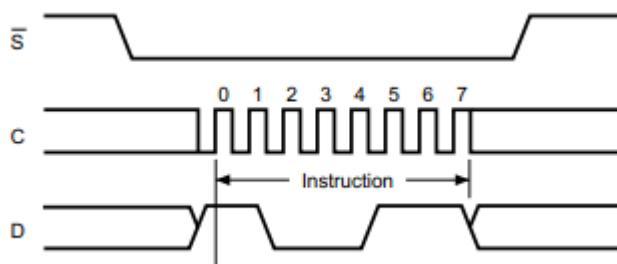

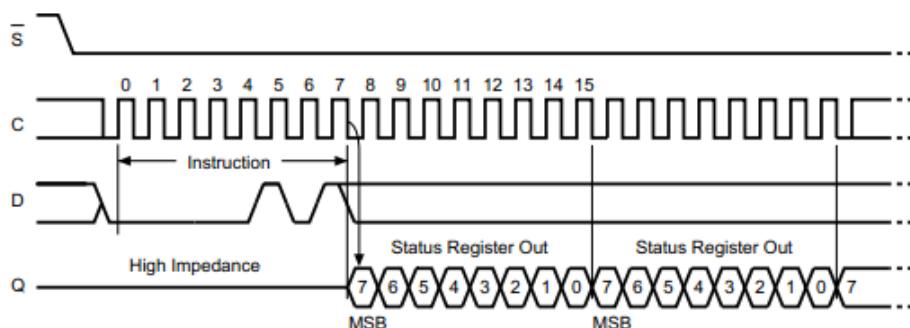

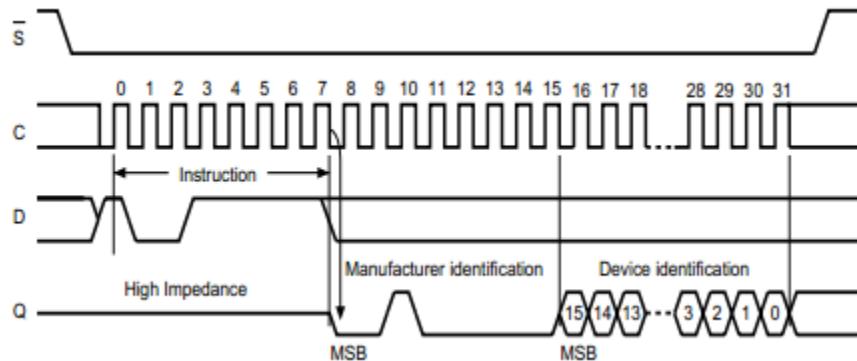

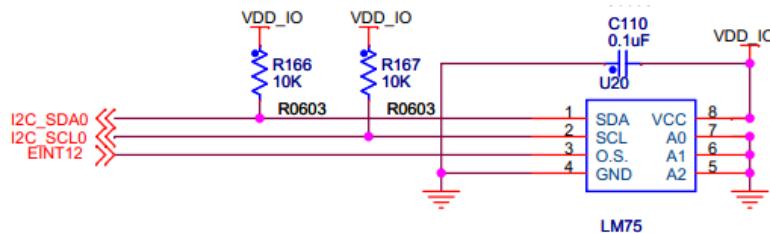

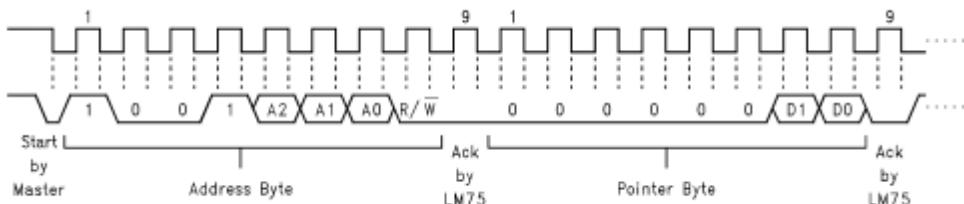

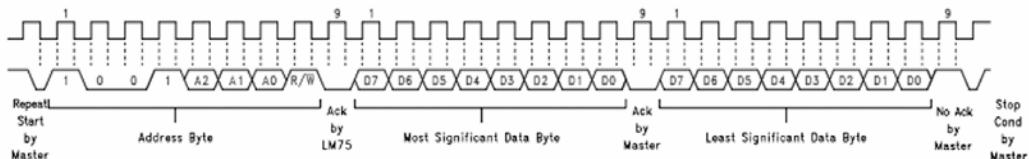

第 12 章为 DMA (PL330) 控制器，介绍了 ARM 公司最新的 PL330 DMA 控制器的开发方法和 PL330 指令。第 13 章为 LCD 接口设计，介绍了 S5PC100 的 LCD 控制器的工作原理。第 14 章为 CAMIF 接口技术，结合 OV9650 摄像头，介绍了 S5PC100 CAMIF 控制器的开发方法。第 15 章为 SPI 接口，结合 M24PXX SPI Flash，介绍了 SPI 总线协议和 S5PC100 SPI 控制器开发方法。第 16 章为 I2C 接口，结合 LM75 温度传感器，讲解了 I2C 协议和 S5PC100 的 IIC 控制器开发方法。

本书的出版要感谢华清远见嵌入式培训中心的无私帮助。本书的前期组织和后期审校工作都凝聚了培训中心几位老师的心血，他们认真阅读了书稿，提出了大量中肯的建议，并帮助纠正了书稿中的很多错误。

全书由刘洪涛、邹南承担了书稿的编写及全书的统稿工作。书稿的完成需要感谢赵孝强、温尚书、杨胜利、周志强、谭翠君、曾宏安、曹忠明等老师的帮助。

由于作者水平所限，书中不妥之处在所难免，恳请读者批评指正。对于本书的批评和建议，可以发表到 [www.farsight.com.cn](http://www.farsight.com.cn) 技术论坛。

编 者

2012 年 6 月

# 目 录

|                                      |    |

|--------------------------------------|----|

| 第 1 章 嵌入式系统基础知识 .....                | 1  |

| 1.1 嵌入式系统概述 .....                    | 1  |

| 1.1.1 嵌入式系统简介 .....                  | 1  |

| 1.1.2 嵌入式系统的观点 .....                 | 2  |

| 1.1.3 嵌入式系统的发展 .....                 | 3  |

| 1.2 嵌入式系统的组成 .....                   | 5  |

| 1.2.1 嵌入式系统硬件组成 .....                | 5  |

| 1.2.2 嵌入式系统软件组成 .....                | 6  |

| 1.3 嵌入式操作系统举例 .....                  | 6  |

| 1.3.1 商业版嵌入式操作系统 .....               | 7  |

| 1.3.2 开源版嵌入式操作系统 .....               | 7  |

| 1.4 嵌入式系统开发概述 .....                  | 8  |

| 1.5 学好微处理器在嵌入式学习中的重要性 .....          | 14 |

| 1.6 本章小结 .....                       | 16 |

| 1.7 思考题 .....                        | 16 |

| 第 2 章 ARM 技术概述 .....                 | 17 |

| 2.1 ARM 体系结构的技术特征及发展 .....           | 17 |

| 2.1.1 ARM 公司简介 .....                 | 17 |

| 2.1.2 ARM 技术特征 .....                 | 18 |

| 2.1.3 ARM 体系架构的发展 .....              | 19 |

| 2.2 ARM 微处理器简介 .....                 | 20 |

| 2.2.1 ARM9 处理器系列 .....               | 21 |

| 2.2.2 ARM9E 处理器系列 .....              | 22 |

| 2.2.3 ARM11 处理器系列 .....              | 22 |

| 2.2.4 SecurCore 处理器系列 .....          | 23 |

| 2.2.5 StrongARM 和 Xscale 处理器系列 ..... | 23 |

| 2.2.6 MPCore 处理器系列 .....             | 23 |

| 2.2.7 Cortex 处理器系列 .....             | 24 |

| 2.2.8 最新 ARM 应用处理器发展现状 .....         | 26 |

| 2.3 ARM 微处理器结构 .....                 | 27 |

| 2.4 ARM 微处理器的应用选型 .....              | 27 |

|                                  |           |

|----------------------------------|-----------|

| 2.4.1 ARM 芯片选择的一般原则.....         | 28        |

| 2.4.2 选择一款适合 ARM 教学的 CPU .....   | 28        |

| 2.5 CORTEX-A8 内部功能及特点.....       | 31        |

| 2.6 数据类型 .....                   | 32        |

| 2.6.1 ARM 的基本数据类型.....           | 32        |

| 2.6.2 浮点数据类型 .....               | 33        |

| 2.6.3 存储器大/小端 .....              | 33        |

| 2.7 CORTEX-A8 内核工作模式.....        | 34        |

| 2.8 CORTEX-A8 存储系统.....          | 35        |

| 2.8.1 协处理器（CP15） .....           | 36        |

| 2.8.2 存储管理单元（MMU） .....          | 37        |

| 2.8.3 高速缓冲存储器（Cache） .....       | 37        |

| 2.9 流水线 .....                    | 37        |

| 2.9.1 流水线的概念与原理.....             | 37        |

| 2.9.2 流水线的分类 .....               | 38        |

| 2.9.3 影响流水线性能的因素.....            | 40        |

| 2.10 寄存器组织.....                  | 40        |

| 2.11 程序状态寄存器 .....               | 43        |

| 2.12 三星 S5PC100 处理器介绍 .....      | 46        |

| 2.13 FS_S5PC100 开发平台介绍 .....     | 47        |

| 2.14 本章小结 .....                  | 49        |

| 2.15 练习题 .....                   | 50        |

| <b>第 3 章 ARM 微处理器的指令系统 .....</b> | <b>51</b> |

| 3.1 ARM 处理器的寻址方式.....            | 51        |

| 3.1.1 数据处理指令寻址方式.....            | 51        |

| 3.1.2 内存访问指令寻址方式.....            | 53        |

| 3.2 ARM 处理器的指令集.....             | 55        |

| 3.2.1 数据操作指令 .....               | 55        |

| 3.2.2 乘法指令 .....                 | 62        |

| 3.2.3 Load/Store 指令 .....        | 65        |

| 3.2.4 跳转指令 .....                 | 71        |

| 3.2.5 状态操作指令 .....               | 74        |

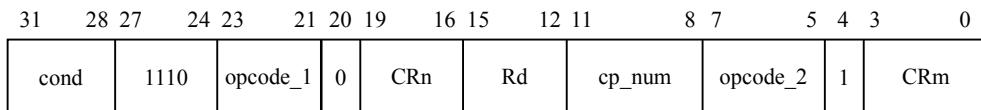

| 3.2.6 协处理器指令 .....               | 76        |

| 3.2.7 异常产生指令 .....               | 80        |

| 3.2.8 其他指令介绍 .....               | 81        |

| 3.3 本章小结 .....                   | 83        |

| 3.4 思考题 .....                    | 83        |

|                                        |     |

|----------------------------------------|-----|

| 第 4 章 ARM 汇编语言程序设计 .....               | 85  |

| 4.1 GNU ARM 汇编器支持的伪操作 .....            | 85  |

| 4.1.1 伪操作概述 .....                      | 85  |

| 4.1.2 数据定义 (Data Definition) 伪操作 ..... | 85  |

| 4.1.3 汇编控制伪操作 .....                    | 87  |

| 4.1.4 杂项伪操作 .....                      | 89  |

| 4.2 ARM 汇编器支持的伪指令 .....                | 89  |

| 4.2.1 ADR 伪指令 .....                    | 89  |

| 4.2.2 ADRL 伪指令 .....                   | 90  |

| 4.2.3 LDR 伪指令 .....                    | 91  |

| 4.3 GNU ARM 汇编语言的语句格式 .....            | 92  |

| 4.4 ARM 汇编语言的程序结构 .....                | 94  |

| 4.4.1 汇编语言的程序格式 .....                  | 94  |

| 4.4.2 汇编语言子程序调用 .....                  | 95  |

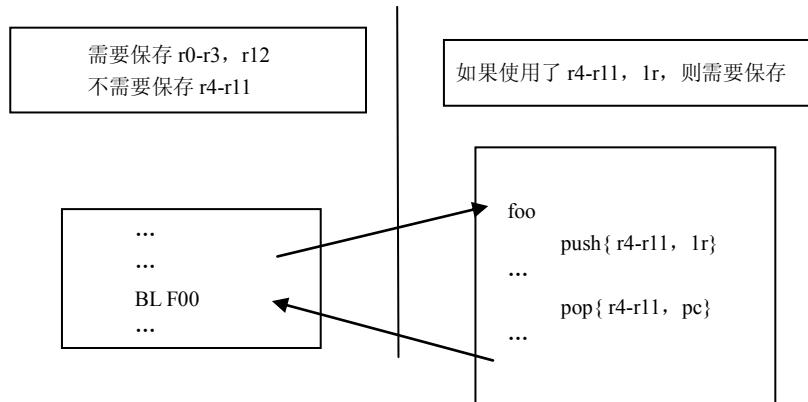

| 4.4.3 过程调用标准 AAPCS .....               | 95  |

| 4.4.4 汇编语言程序设计举例 .....                 | 97  |

| 4.5 汇编语言与 C 语言的混合编程 .....              | 98  |

| 4.5.1 GNU ARM 内联汇编 .....               | 98  |

| 4.5.2 混合编程调用举例 .....                   | 100 |

| 4.6 本章小结 .....                         | 102 |

| 4.7 思考题 .....                          | 102 |

| 第 5 章 ARM 开发及环境搭建 .....                | 103 |

| 5.1 仿真器简介 .....                        | 103 |

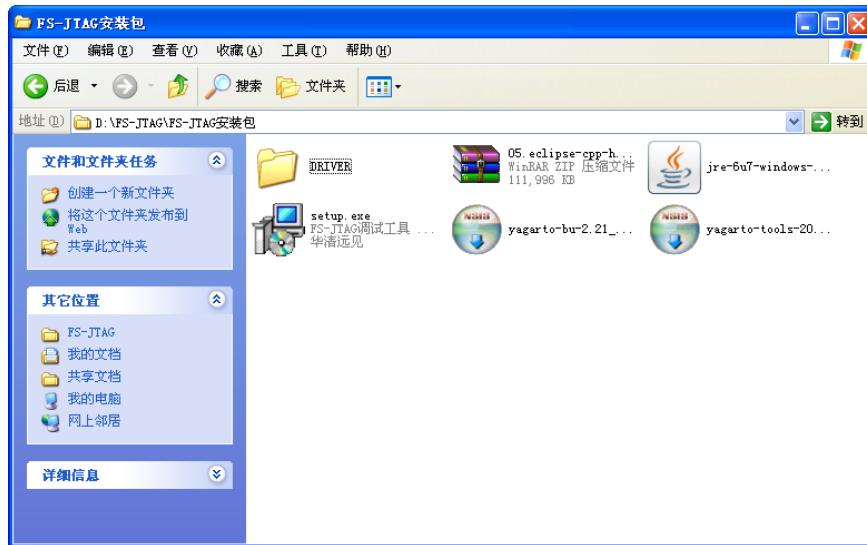

| 5.1.1 FS-JTAG 仿真器介绍 .....              | 103 |

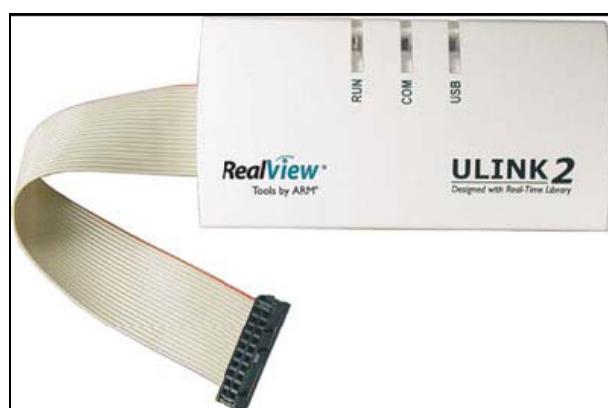

| 5.1.2 ULINK 介绍 .....                   | 104 |

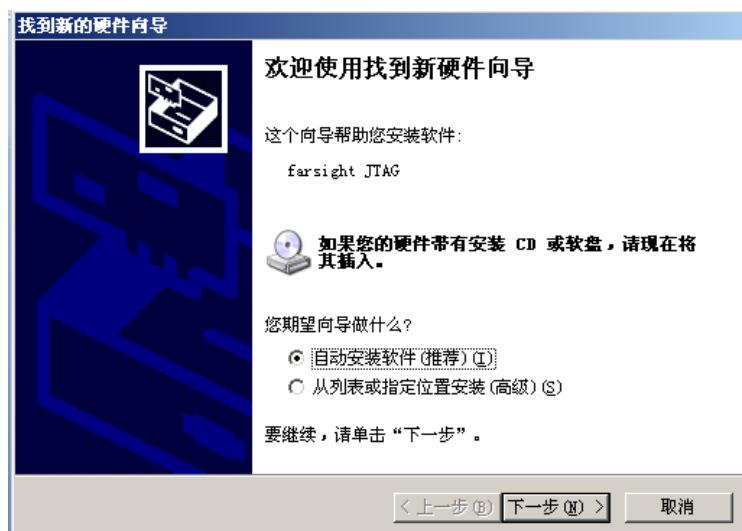

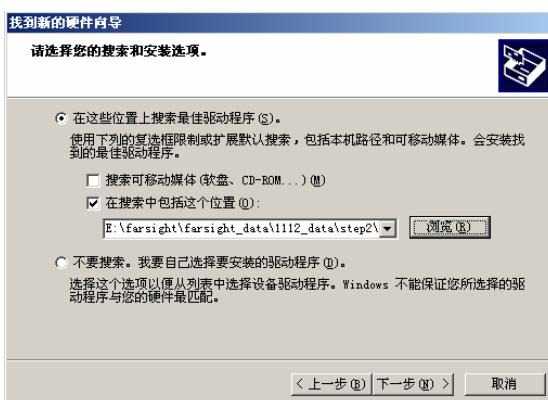

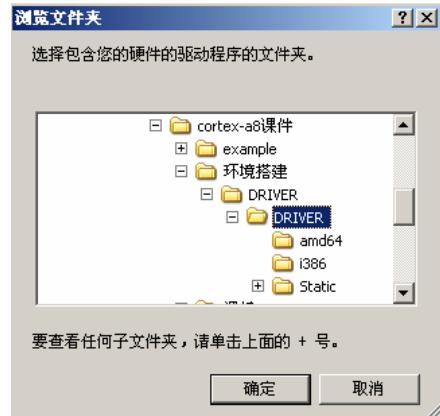

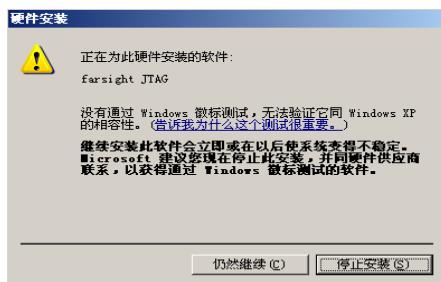

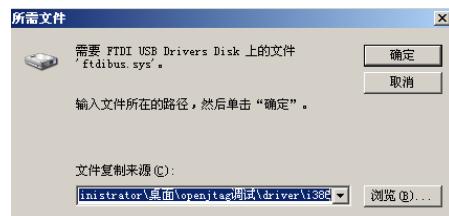

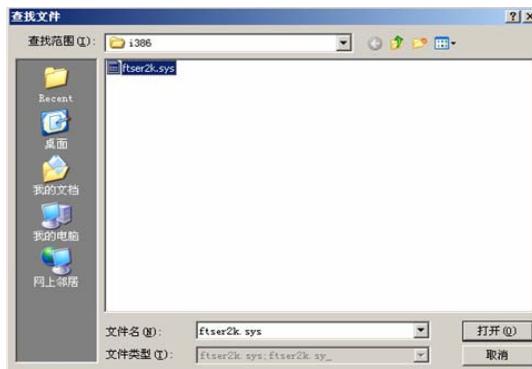

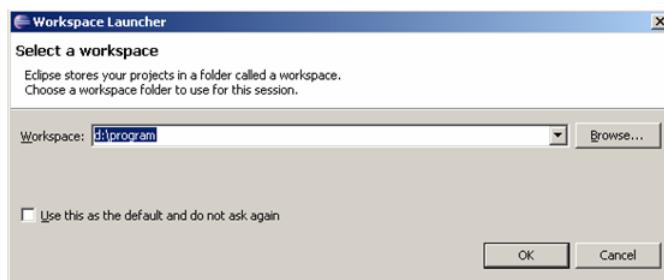

| 5.2 开发环境搭建 .....                       | 105 |

| 5.3 ECLIPSE FOR ARM 使用 .....           | 108 |

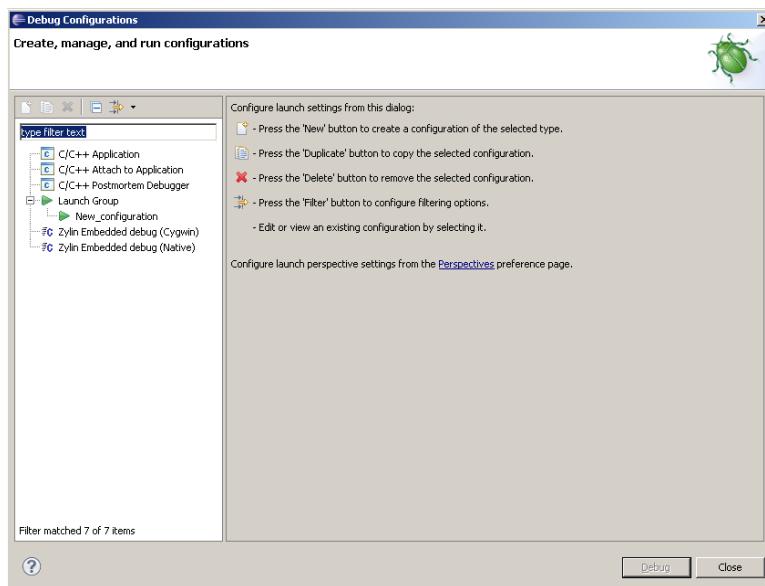

| 5.4 编译工程 .....                         | 109 |

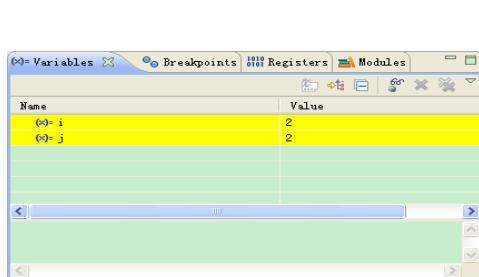

| 5.5 调试工程 .....                         | 110 |

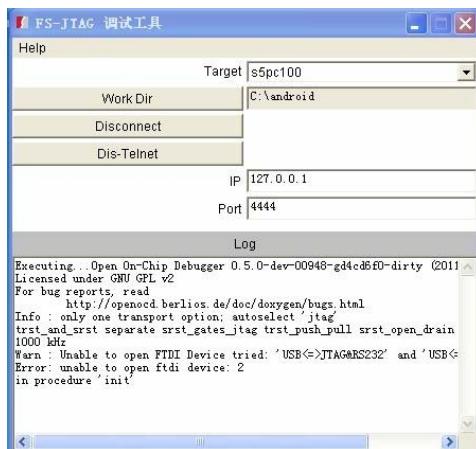

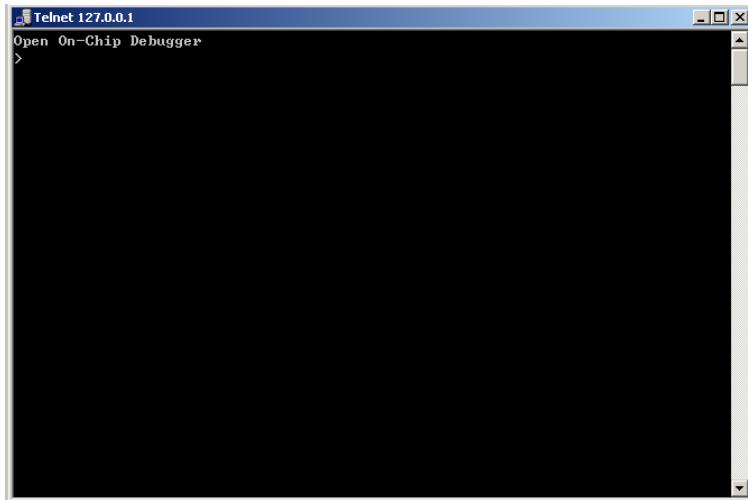

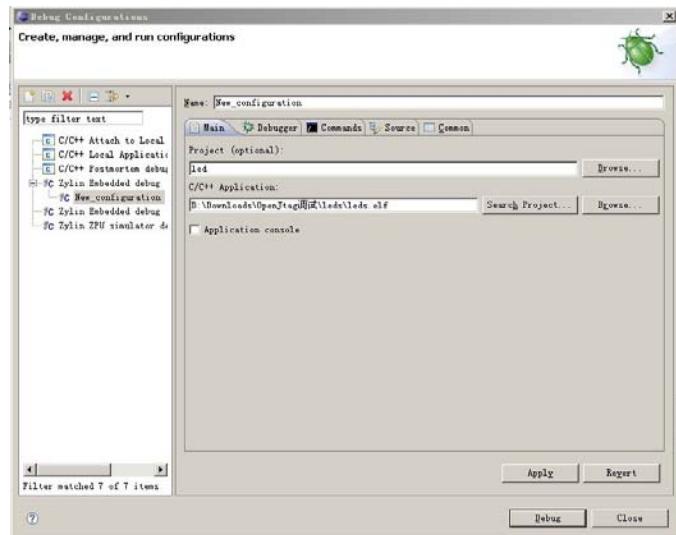

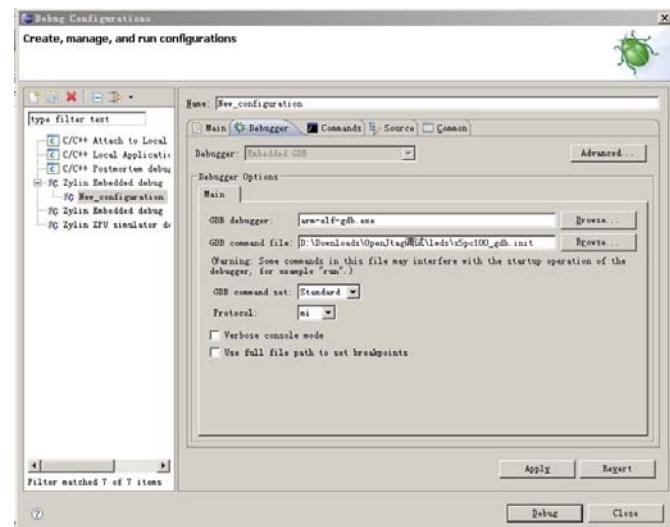

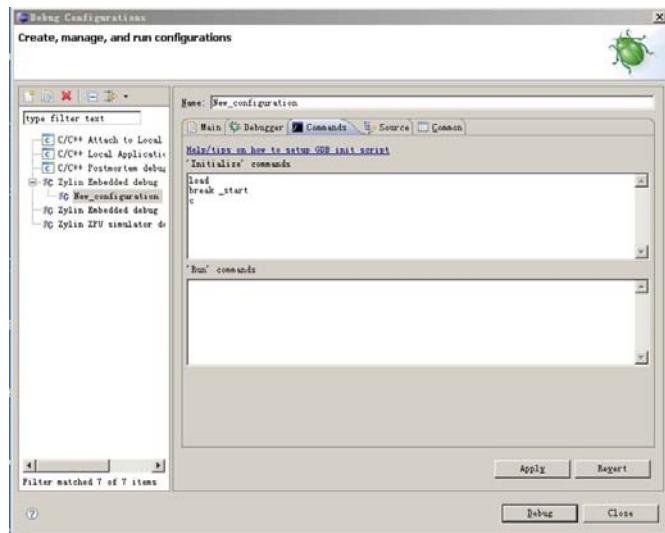

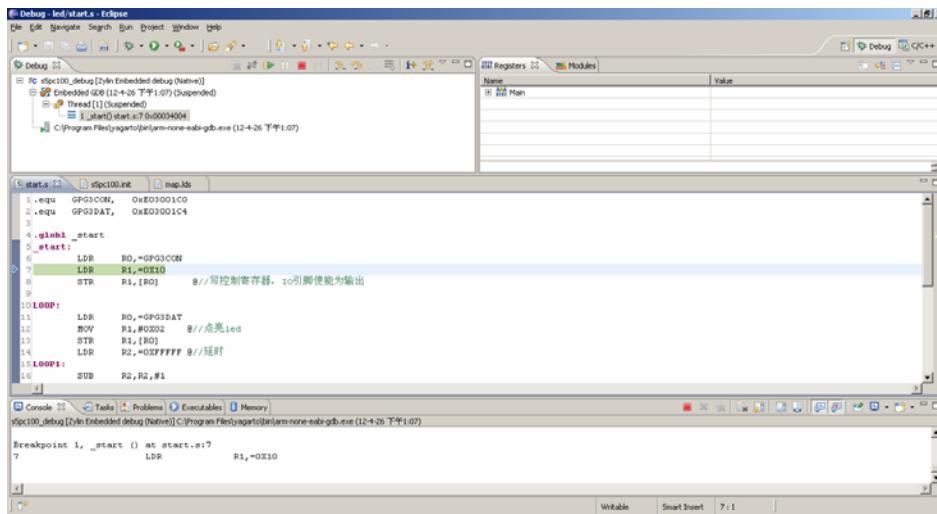

| 5.5.1 配置 FS-JTAG 调试工具 .....            | 110 |

| 5.5.2 配置调试工具 .....                     | 111 |

| 5.6 本章小结 .....                         | 114 |

| 5.7 练习题 .....                          | 114 |

| 第 6 章 GPIO 编程 .....                    | 115 |

| 6.1 GPIO 功能介绍 .....                    | 115 |

| 6.2 S5PC100 芯片的 GPIO 控制器详解 .....       | 115 |

|                                    |            |

|------------------------------------|------------|

| 6.2.1 特性 .....                     | 115        |

| 6.2.2 GPIO 分组预览 .....              | 116        |

| 6.2.3 S5PC100 的 GPIO 常用寄存器分类 ..... | 116        |

| 6.2.4 GPIO 功能描述 .....              | 116        |

| 6.2.5 S5PC100 I/O 接口常用寄存器詳解 .....  | 117        |

| 6.2.6 GPIO 数据寄存器 .....             | 118        |

| 6.3 S5PC100 GPIO 的应用 .....         | 118        |

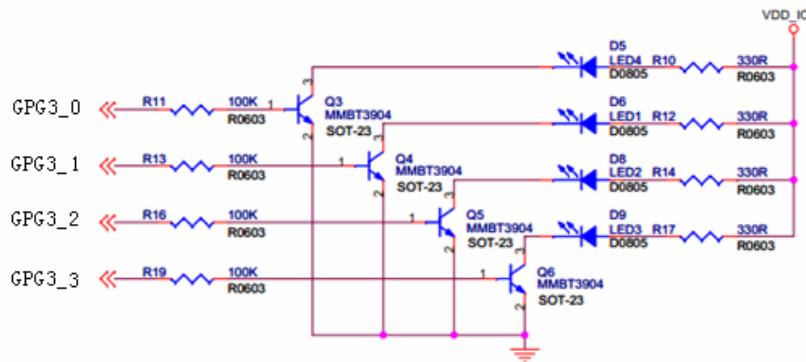

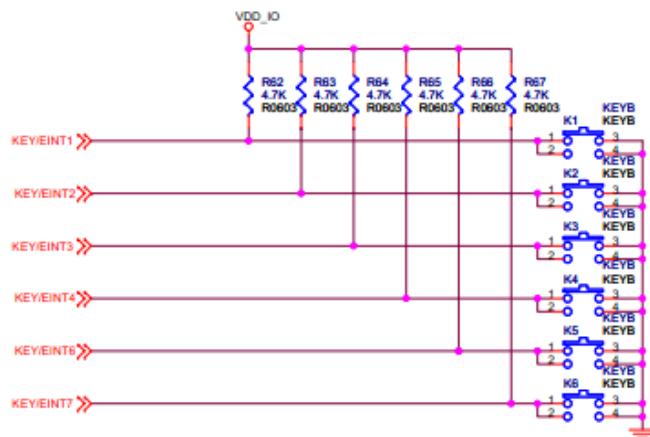

| 6.3.1 电路连接 .....                   | 119        |

| 6.3.2 寄存器设置 .....                  | 119        |

| 6.3.3 程序编写 .....                   | 119        |

| 6.4 本章小结 .....                     | 120        |

| 6.5 练习题 .....                      | 120        |

| <b>第 7 章 ARM 异常及中断处理 .....</b>     | <b>121</b> |

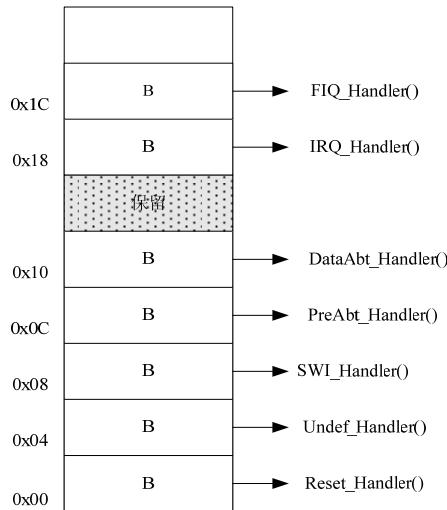

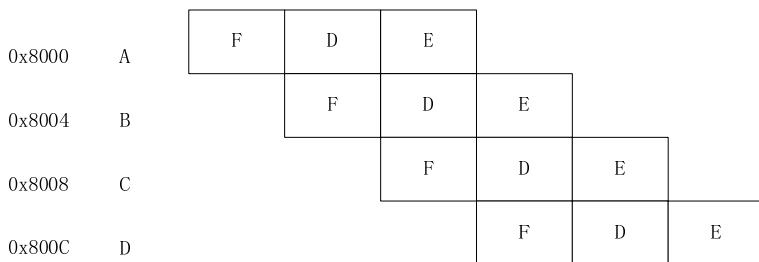

| 7.1 ARM 异常中断处理概述 .....             | 121        |

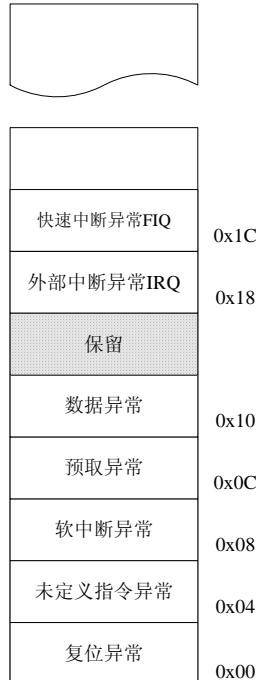

| 7.2 ARM 体系异常种类 .....               | 122        |

| 7.3 ARM 异常的优先级 .....               | 127        |

| 7.4 ARM 处理器模式和异常 .....             | 127        |

| 7.5 ARM 异常响应和处理程序返回 .....          | 128        |

| 7.5.1 中断响应的概念 .....                | 128        |

| 7.5.2 ARM 异常响应流程 .....             | 128        |

| 7.5.3 从异常处理程序中返回 .....             | 129        |

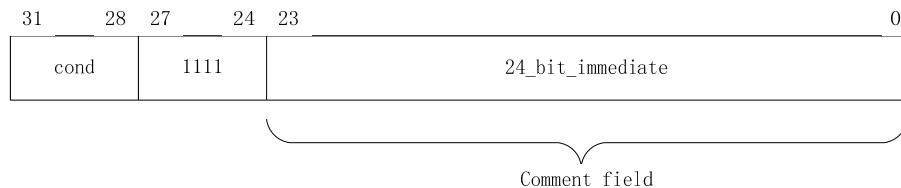

| 7.6 ARM 的 SWI 异常中断处理程序设计 .....     | 131        |

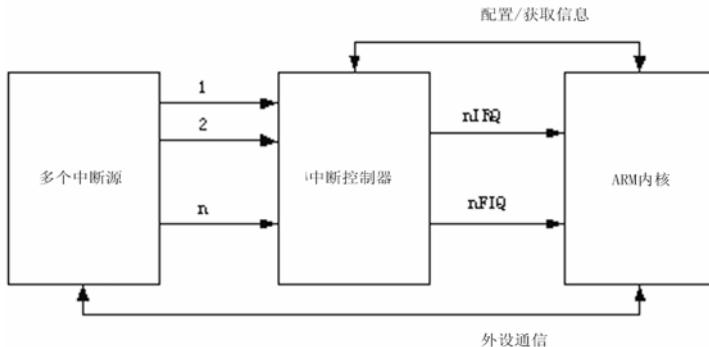

| 7.7 FIQ 和 IRQ 中断 .....             | 133        |

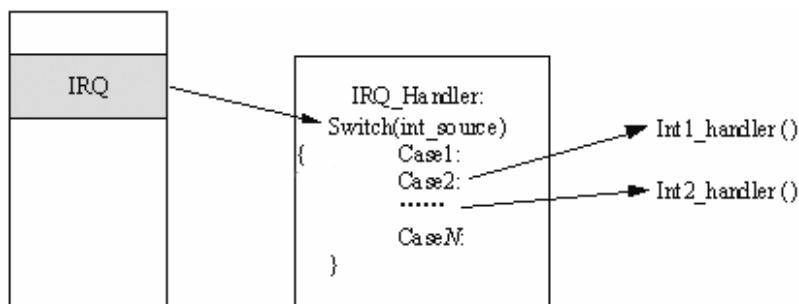

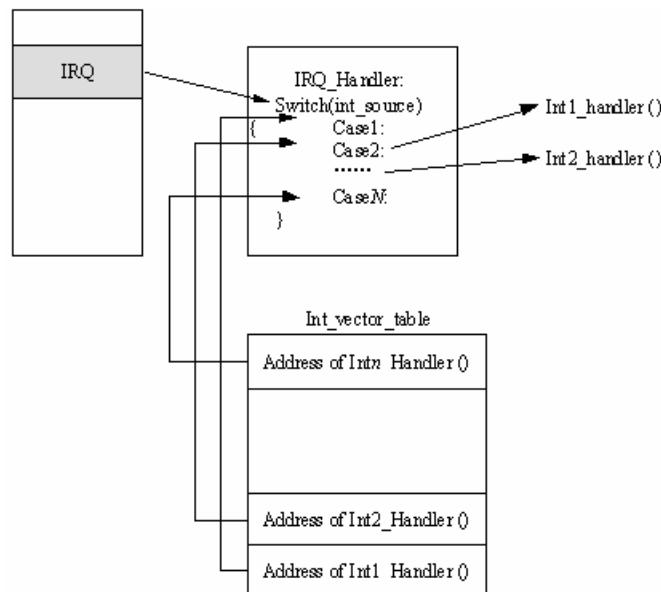

| 7.7.1 中断分支 .....                   | 133        |

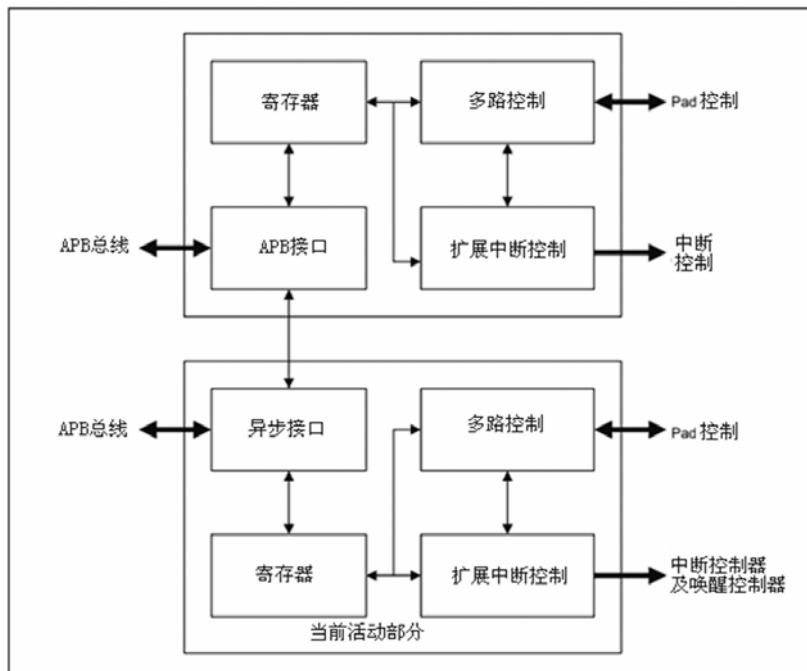

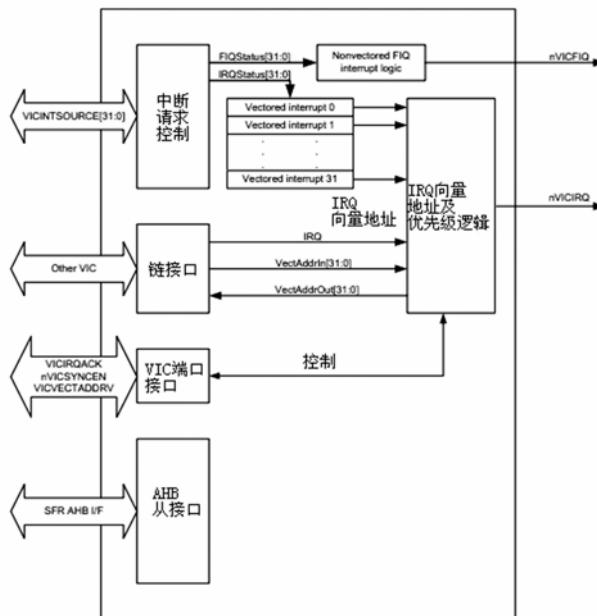

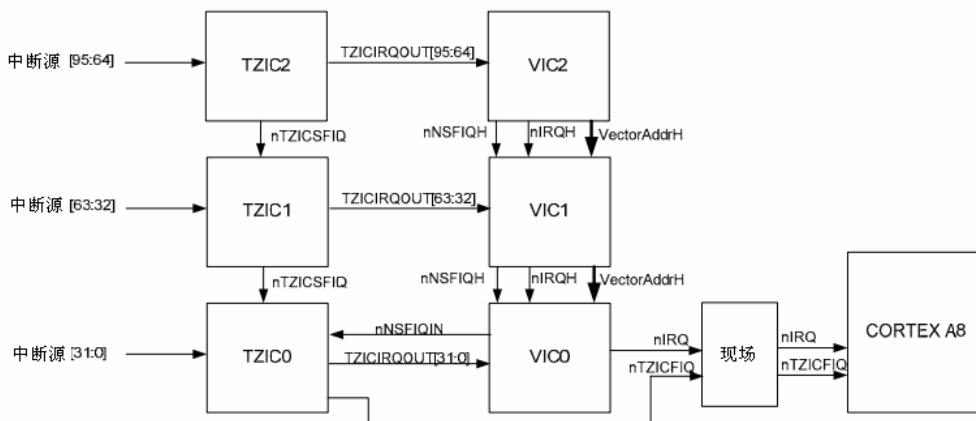

| 7.7.2 S5PC100 中断机制分析 .....         | 134        |

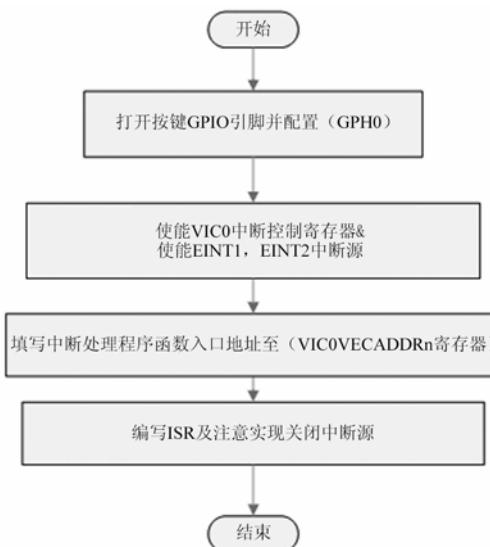

| 7.7.3 S5PC100 中断处理程序实例 .....       | 138        |

| 7.8 本章小结 .....                     | 140        |

| 7.9 练习题 .....                      | 140        |

| <b>第 8 章 串行通信接口 .....</b>          | <b>141</b> |

| 8.1 串行通信概述 .....                   | 141        |

| 8.1.1 串行通信与并行通信概念 .....            | 141        |

| 8.1.2 异步串行方式的特点 .....              | 141        |

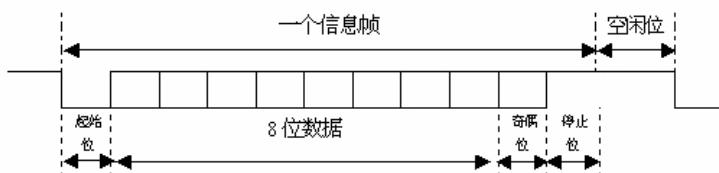

| 8.1.3 异步串行方式的数据格式 .....            | 142        |

| 8.1.4 同步串行方式的特点 .....              | 142        |

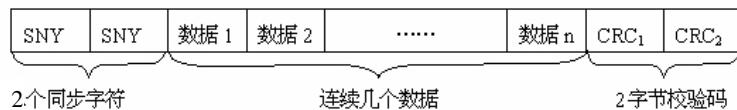

| 8.1.5 同步串行方式的数据格式 .....            | 142        |

| 8.1.6 比特率、比特率因子与位周期 .....          | 143        |

|                                        |            |

|----------------------------------------|------------|

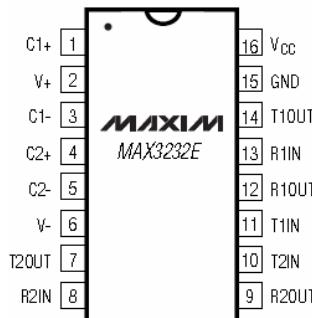

| 8.1.7 RS-232C 串口规范.....                | 143        |

| 8.1.8 RS-232C 接线方式.....                | 145        |

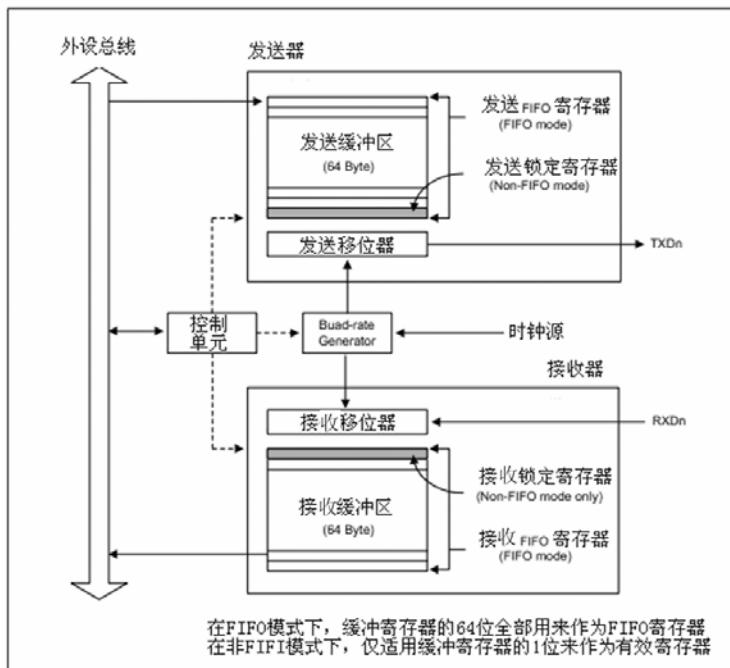

| 8.2 S5PC100 异步串行通信.....                | 145        |

| 8.2.1 S5PC100 串口控制器概述.....             | 145        |

| 8.2.2 UART 寄存器详解.....                  | 147        |

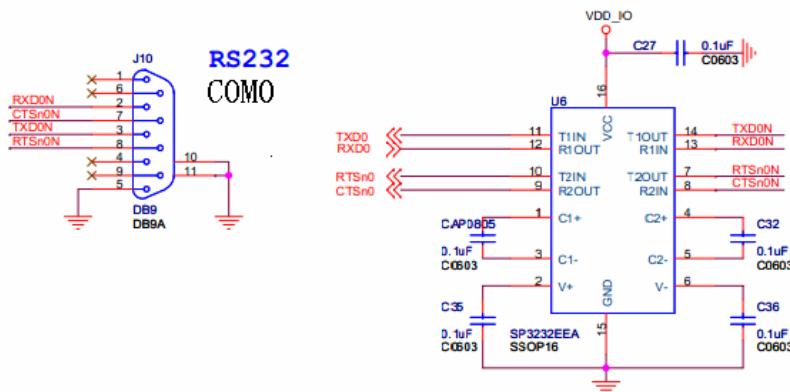

| 8.3 接口电路与程序设计.....                     | 150        |

| 8.3.1 电路连接 .....                       | 150        |

| 8.3.2 程序编写 .....                       | 150        |

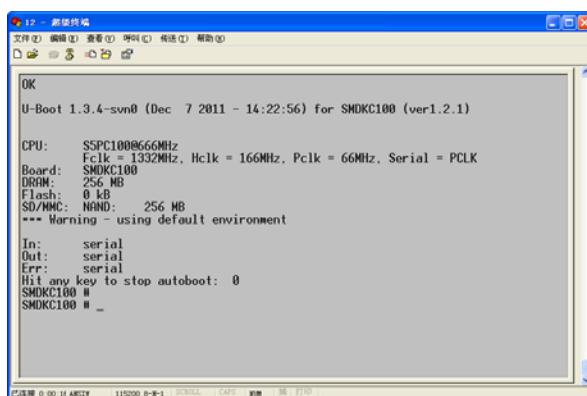

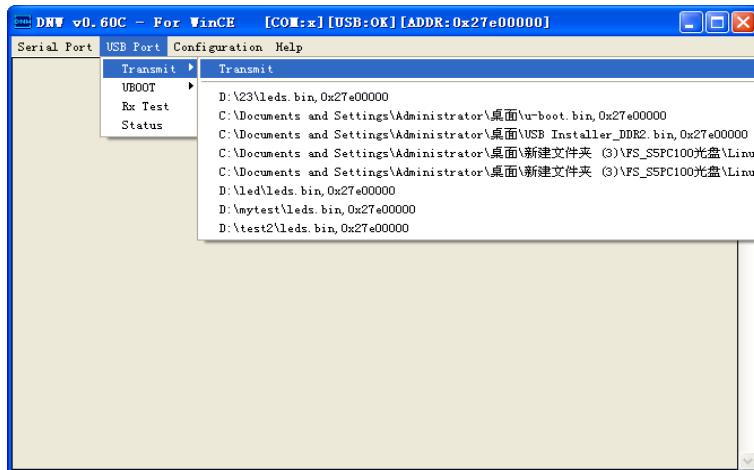

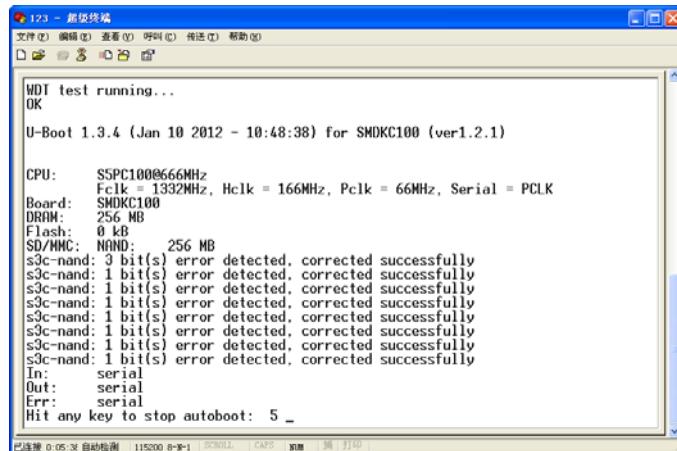

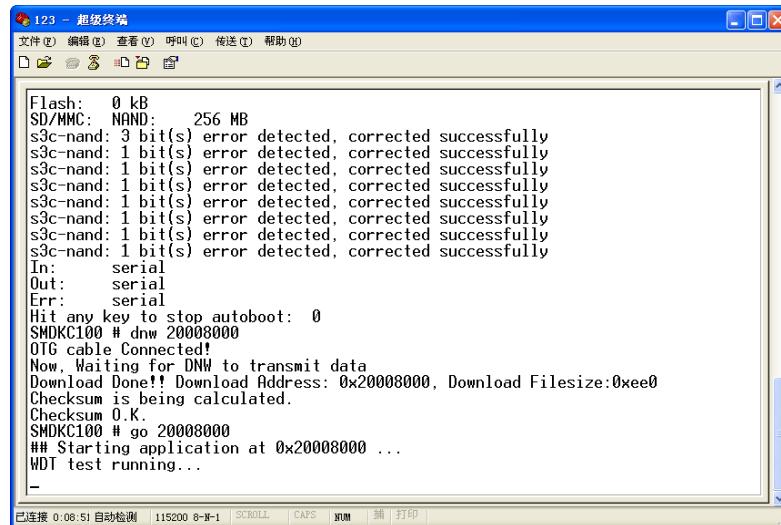

| 8.3.3 调试与运行结果.....                     | 152        |

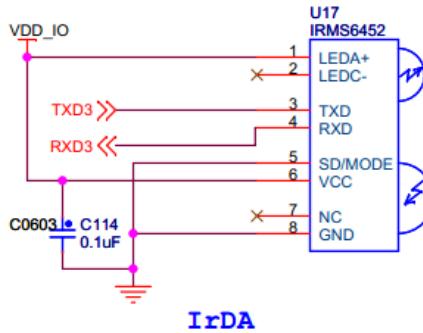

| 8.3.4 红外收发程序 .....                     | 154        |

| 8.4 本章小结 .....                         | 157        |

| 8.5 练习题.....                           | 157        |

| <b>第 9 章 存储器接口.....</b>                | <b>158</b> |

| 9.1 FLASH ROM 介绍 .....                 | 158        |

| 9.2 NOR Flash 操作 .....                 | 160        |

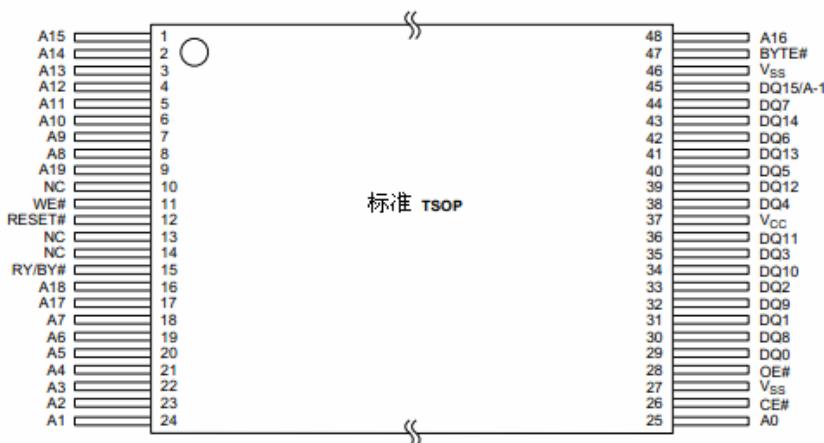

| 9.2.1 AM29LV160D 芯片介绍 .....            | 160        |

| 9.2.2 AM29LV160D 字编程操作 .....           | 161        |

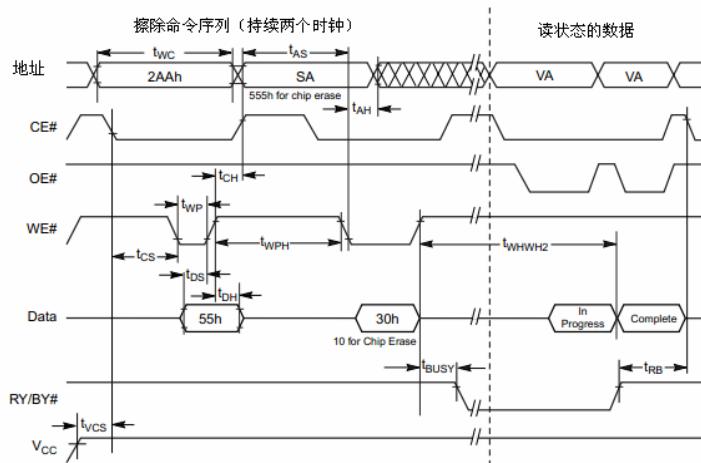

| 9.2.3 AM29LV160D 扇区/块擦除操作 .....        | 162        |

| 9.2.4 AM29LV160D 芯片擦除操作 .....          | 163        |

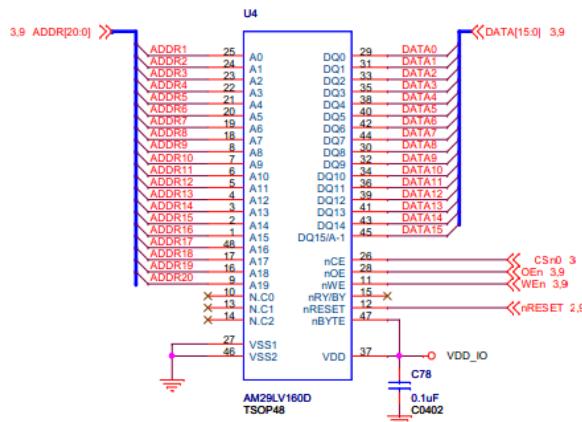

| 9.2.5 AM29LV160D 与 S5PC100 的接口电路.....  | 163        |

| 9.2.6 AM29LV160D 存储器的程序设计.....         | 164        |

| 9.3 NAND Flash 操作 .....                | 166        |

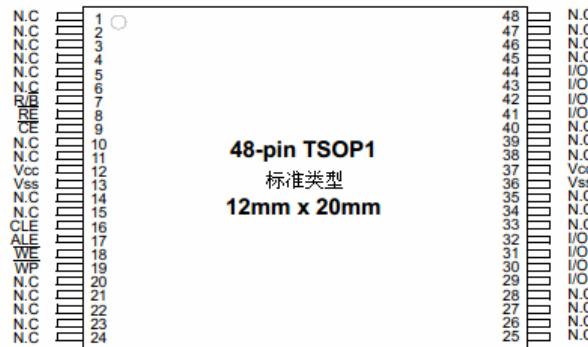

| 9.3.1 芯片介绍 .....                       | 166        |

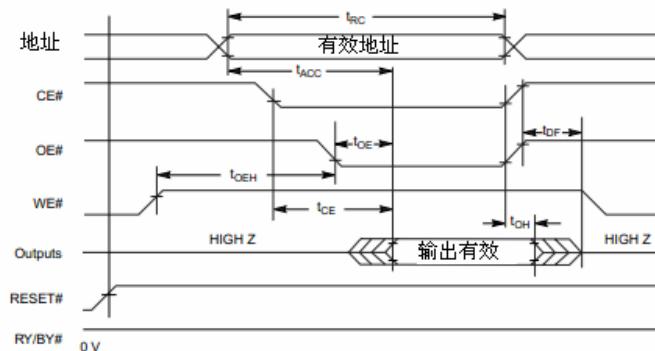

| 9.3.2 读操作过程 .....                      | 167        |

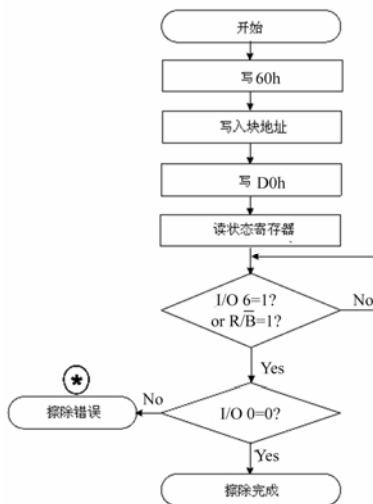

| 9.3.3 擦除操作过程 .....                     | 168        |

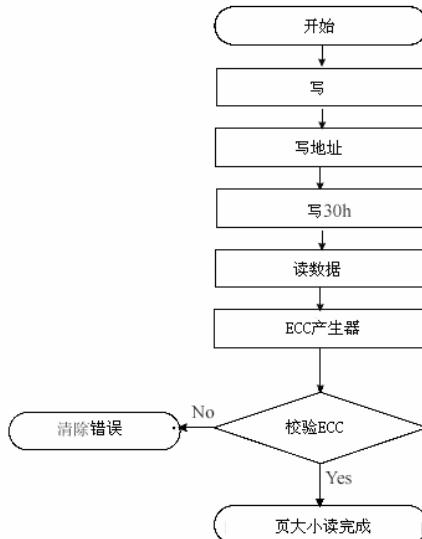

| 9.3.4 写操作过程 .....                      | 169        |

| 9.4 S5PC100 中 NAND Flash 控制器的操作 .....  | 170        |

| 9.4.1 S5PC100 NAND Flash 控制器概述.....    | 170        |

| 9.4.2 S5PC100 NAND Flash 控制器寄存器详解..... | 170        |

| 9.5 S5PC100 NAND Flash 接口电路与程序设计 ..... | 172        |

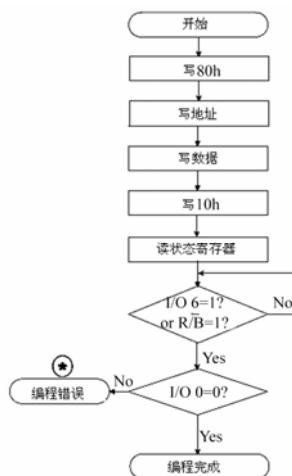

| 9.5.1 K9F2G080U 和 S5PC100 的接口电路 .....  | 172        |

| 9.5.2 S5PC100 控制 K9F2G080U 的程序设计 ..... | 173        |

| 9.6 本章小结 .....                         | 176        |

| 9.7 练习题.....                           | 176        |

| <b>第 10 章 定时器与 RTC .....</b>           | <b>177</b> |

| 10.1 S5PC100 PWM 定时器 .....             | 177        |

|        |                          |     |

|--------|--------------------------|-----|

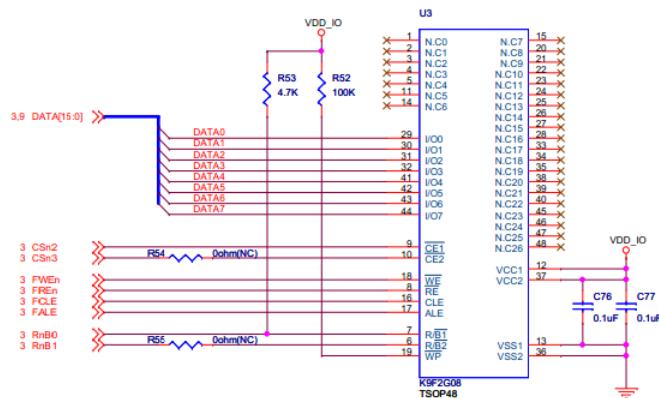

| 10.1.1 | PWM 定时器概述 .....          | 177 |

| 10.1.2 | PWM 定时器特点 .....          | 178 |

| 10.1.3 | PWM 定时器的寄存器 .....        | 179 |

| 10.1.4 | PWM 定时器操作示例 .....        | 184 |

| 10.2   | S5PC100 看门狗定时器 .....     | 185 |

| 10.2.1 | S5PC100 看门狗定时器概述 .....   | 185 |

| 10.2.2 | 看门狗定时器寄存器 .....          | 186 |

| 10.2.3 | 看门狗定时器程序编写 .....         | 187 |

| 10.3   | RTC .....                | 190 |

| 10.3.1 | RTC 介绍 .....             | 190 |

| 10.3.2 | RTC 控制器 .....            | 190 |

| 10.3.3 | RTC 控制器寄存器详解 .....       | 191 |

| 10.3.4 | RTC 测试例子 .....           | 192 |

| 10.4   | 本章小结 .....               | 193 |

| 10.5   | 练习题 .....                | 193 |

| 第 11 章 | A/D 转换器 .....            | 194 |

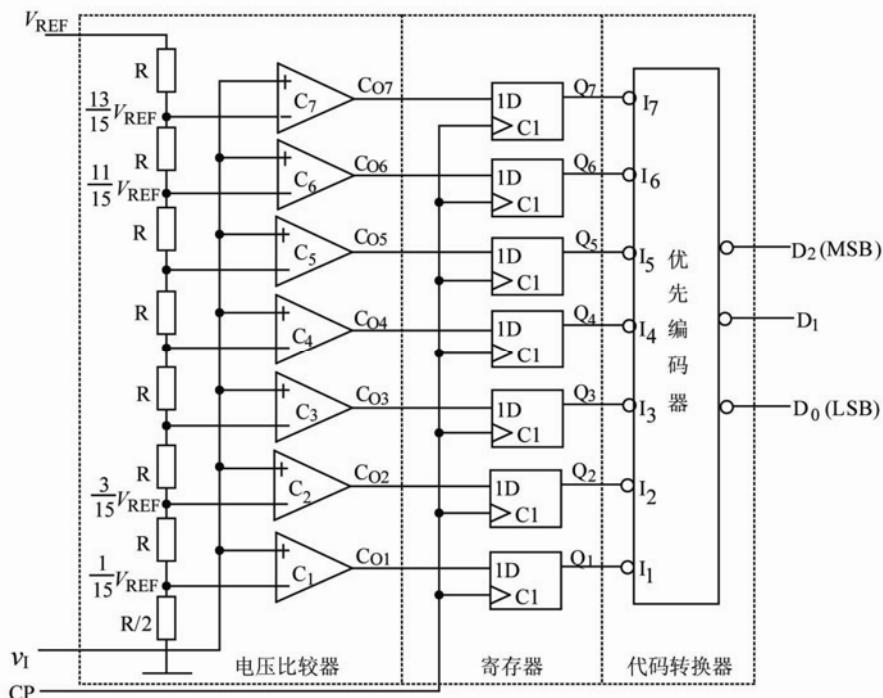

| 11.1   | A/D 转换器原理 .....          | 194 |

| 11.1.1 | A/D 转换基础 .....           | 194 |

| 11.1.2 | A/D 转换的技术指标 .....        | 195 |

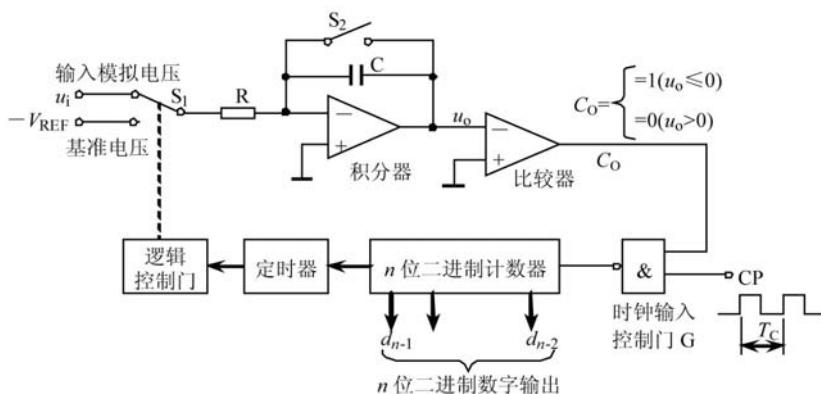

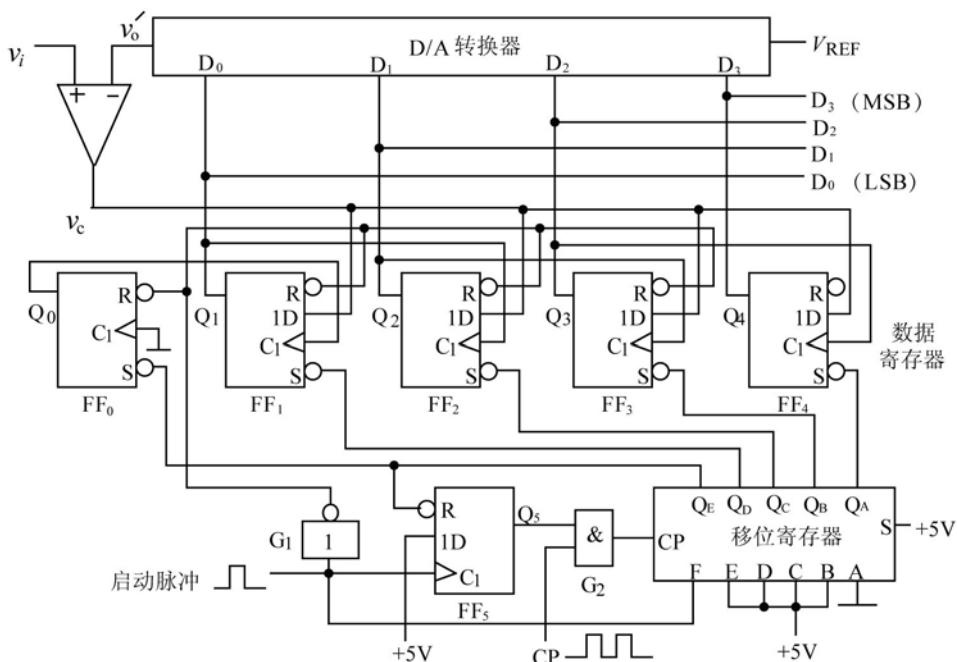

| 11.1.3 | A/D 转换器类型 .....          | 196 |

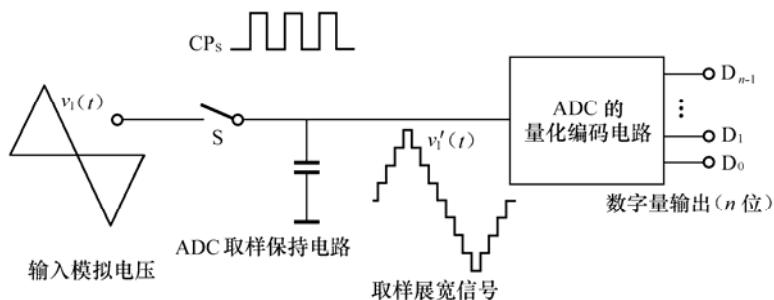

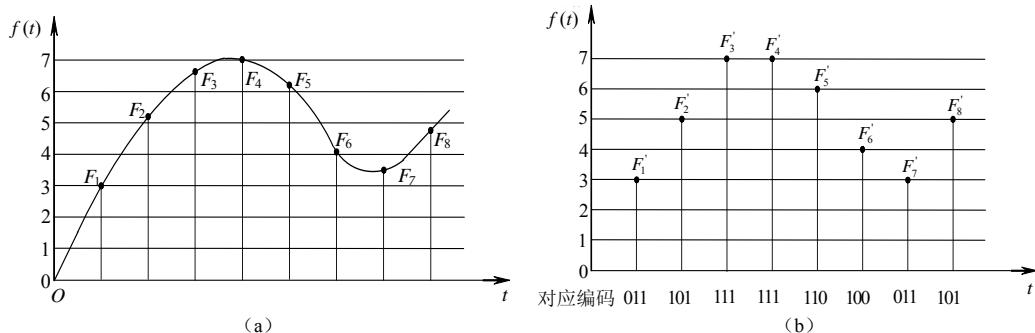

| 11.1.4 | A/D 转换的一般步骤 .....        | 200 |

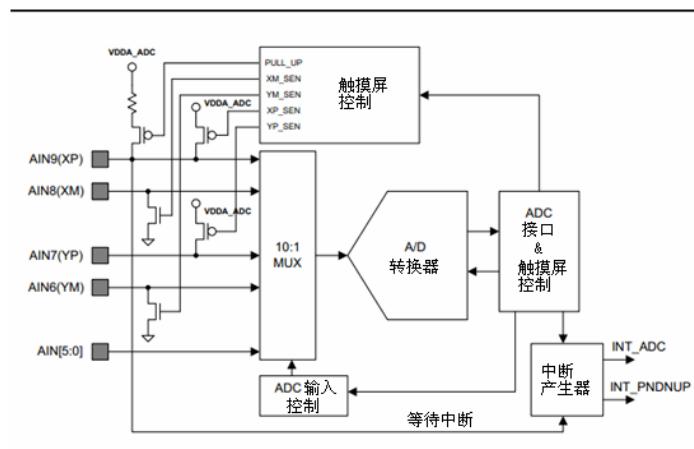

| 11.2   | S5PC100 A/D 转换器 .....    | 200 |

| 11.2.1 | S5PC100 A/D 转换器概述 .....  | 200 |

| 11.2.2 | S5PC100 A/D 控制器寄存器 ..... | 201 |

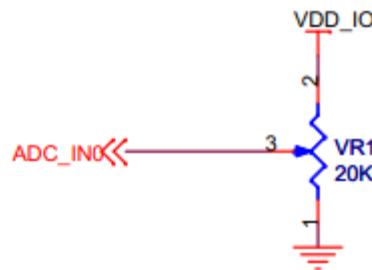

| 11.3   | A/D 转换器应用举例 .....        | 203 |

| 11.3.1 | 电路连接 .....               | 203 |

| 11.3.2 | 程序编写 .....               | 203 |

| 11.3.3 | 调试与运行结果 .....            | 204 |

| 11.4   | 本章小结 .....               | 205 |

| 11.5   | 练习题 .....                | 205 |

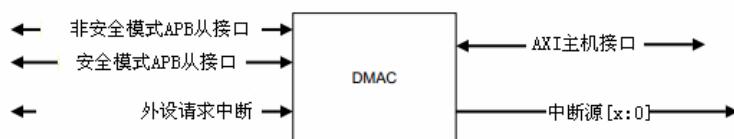

| 第 12 章 | DMA (PL330) 控制器 .....    | 206 |

| 12.1   | PL330 原理概述 .....         | 206 |

| 12.1.1 | DMAC 简述 .....            | 206 |

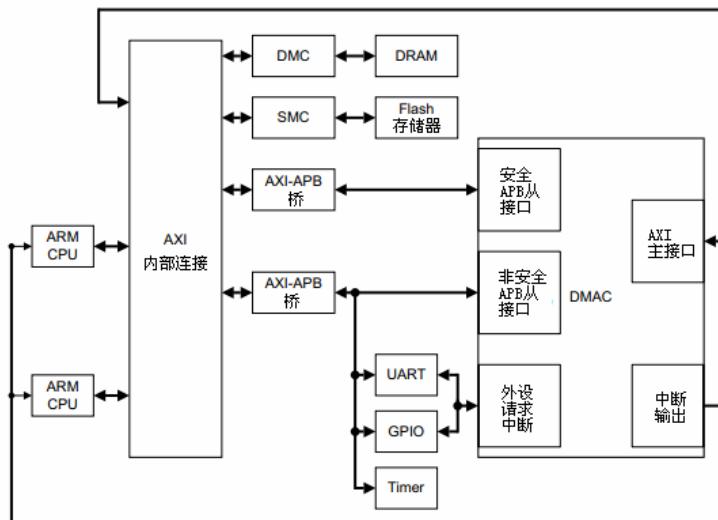

| 12.1.2 | S5PC100 下的 DMAC 模型 ..... | 207 |

| 12.1.3 | PL330 简述 .....           | 208 |

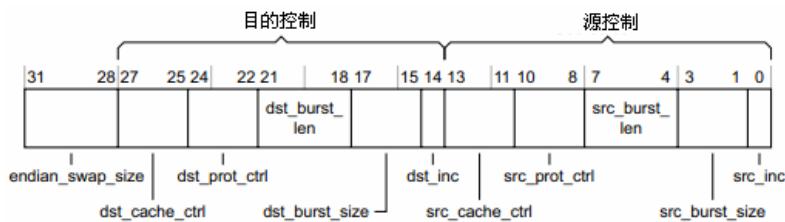

| 12.2   | PL330 详解 .....           | 209 |

|                                      |            |

|--------------------------------------|------------|

| 12.2.1 PL330 指令集.....                | 209        |

| 12.2.2 相关寄存器详解.....                  | 215        |

| 12.3 S5PC100 PL330 测试例子 .....        | 217        |

| 12.4 本章小结 .....                      | 221        |

| 12.5 练习题.....                        | 221        |

| <b>第 13 章 LCD 接口设计 .....</b>         | <b>222</b> |

| 13.1 LCD 控制器.....                    | 222        |

| 13.1.1 LCD 控制器介绍.....                | 222        |

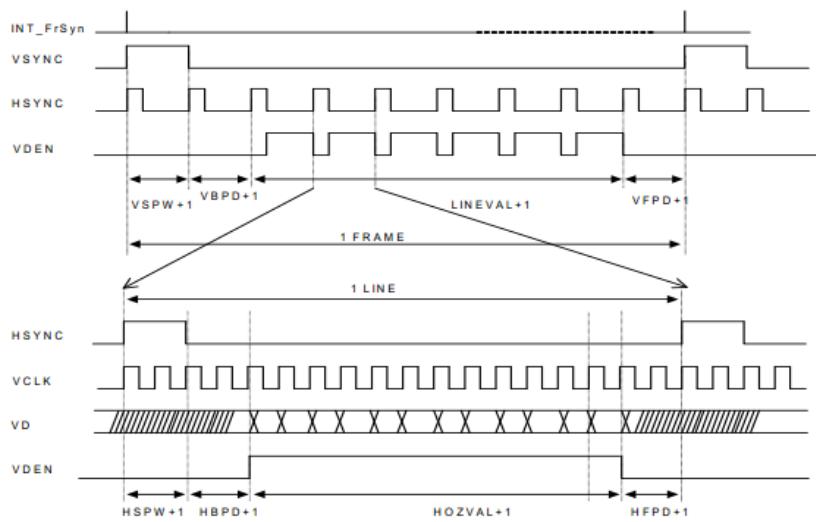

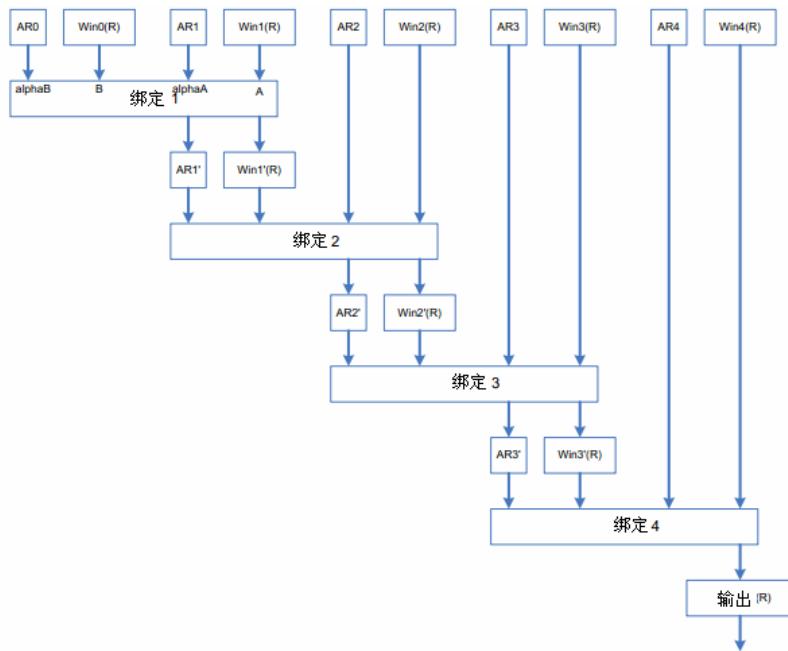

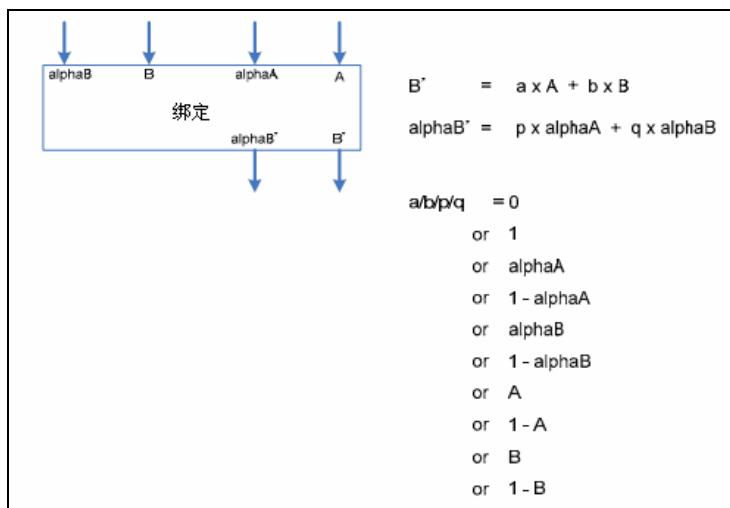

| 13.1.2 S5PC100 的 LCD 控制器介绍.....      | 223        |

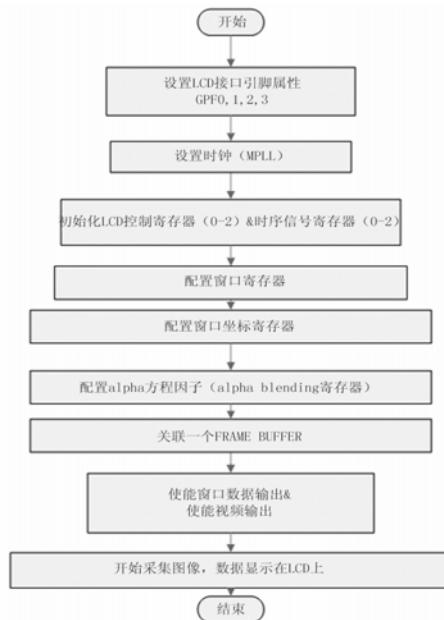

| 13.1.3 S5PC100 的 LCD 控制器操作.....      | 224        |

| 13.1.4 LCD 控制器寄存器.....               | 226        |

| 13.2 LCD 控制器实例 .....                 | 231        |

| 13.3 本章小结 .....                      | 235        |

| 13.4 练习题.....                        | 235        |

| <b>第 14 章 CAMIF 接口技术 .....</b>       | <b>236</b> |

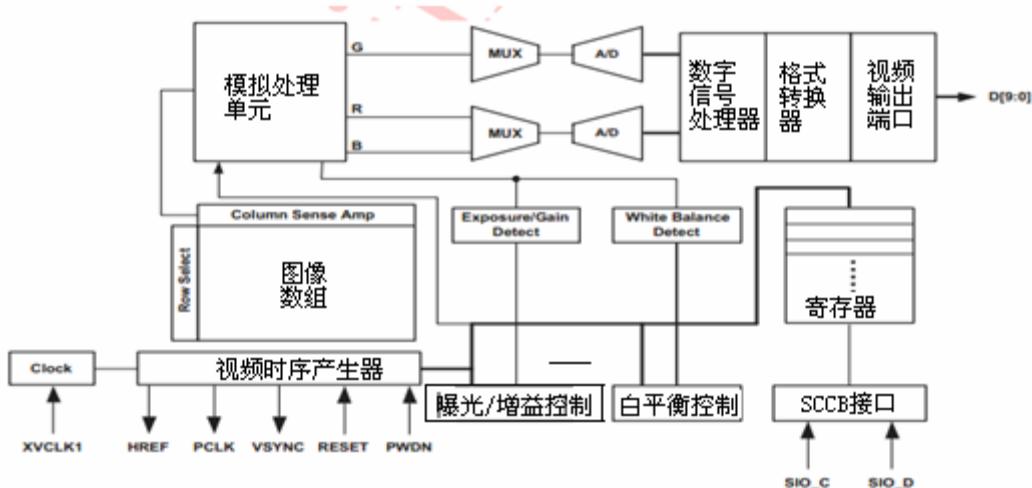

| 14.1 OV9650 介绍 .....                 | 236        |

| 14.1.1 芯片功能描述 .....                  | 236        |

| 14.1.2 OV9650 物理参数.....              | 237        |

| 14.1.3 OV9650 寄存器详解.....             | 238        |

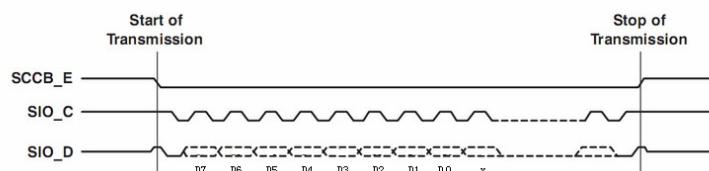

| 14.2 SCCB 总线.....                    | 240        |

| 14.2.1 SCCB 协议介绍 .....               | 240        |

| 14.2.2 SCCB 的总线编程 .....              | 241        |

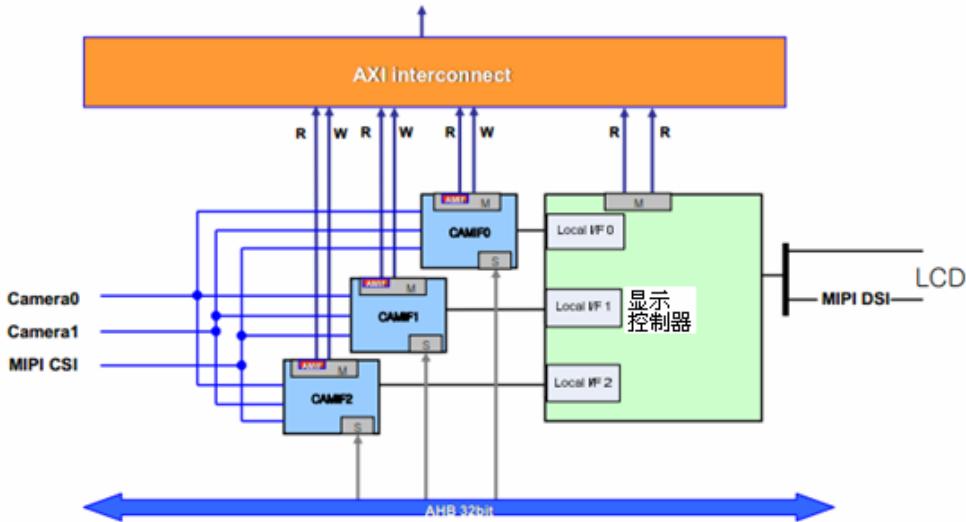

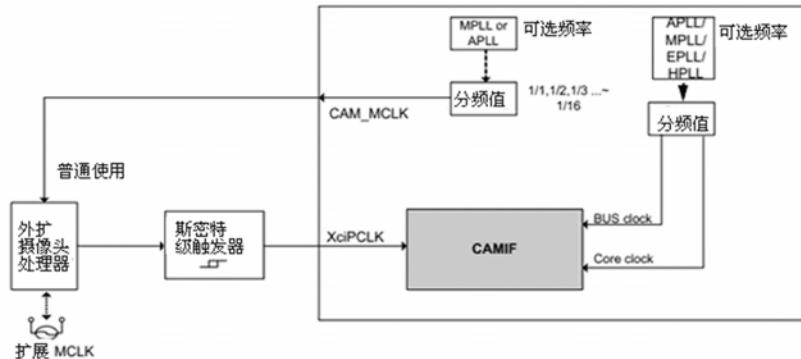

| 14.3 CAMIF 接口详解 .....                | 242        |

| 14.3.1 基于 S5PC100 的 CAMIF 接口介绍 ..... | 242        |

| 14.3.2 S5PC100 CAMIF 寄存器详解 .....     | 244        |

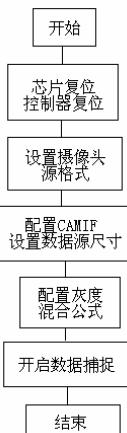

| 14.3.3 CAMIF 操作案例.....               | 247        |

| 14.4 本章小结 .....                      | 251        |

| 14.5 练习题.....                        | 251        |

| <b>第 15 章 SPI 接口.....</b>            | <b>252</b> |

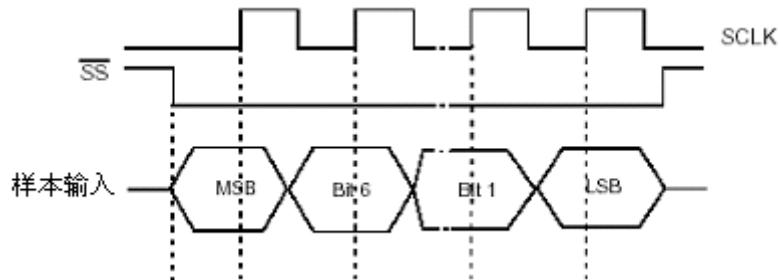

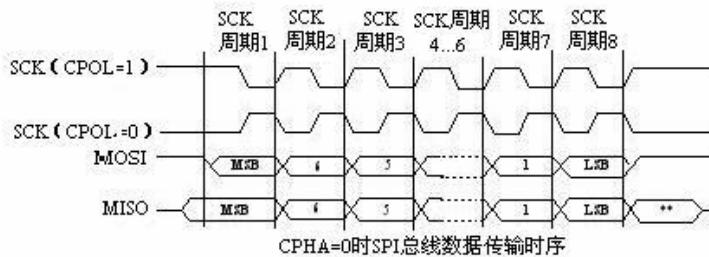

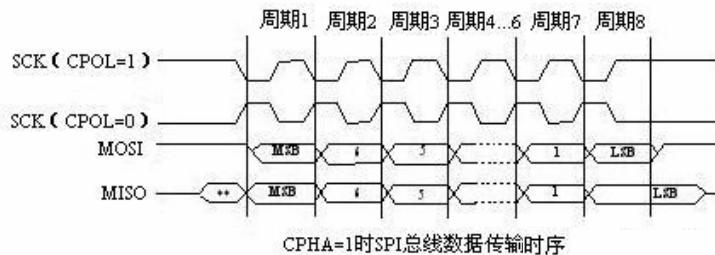

| 15.1 SPI 总线协议理论 .....                | 252        |

| 15.1.1 协议简介 .....                    | 252        |

| 15.1.2 协议内容 .....                    | 252        |

| 15.2 SPI 控制器详解 .....                 | 254        |

| 15.2.1 S5PC100 的 SPI 控制器简介 .....     | 254        |

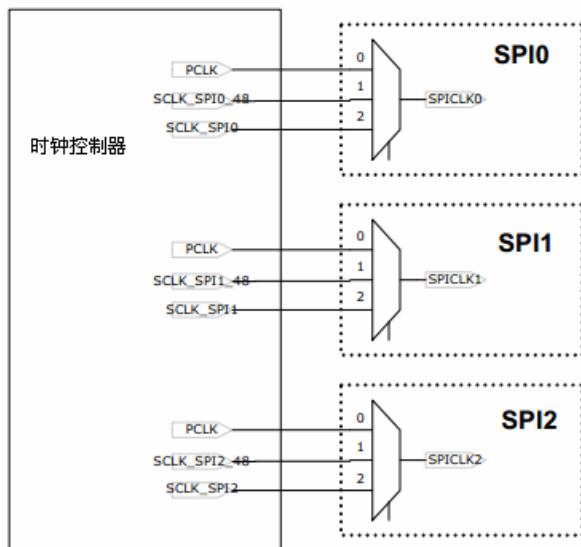

| 15.2.2 时钟源控制 .....                   | 255        |

| 15.2.3 寄存器详解 .....                   | 255        |

|                                   |            |

|-----------------------------------|------------|

| 15.3 SPI 开发例子 .....               | 257        |

| 15.4 本章小结 .....                   | 264        |

| 15.5 练习题 .....                    | 264        |

| <b>第 16 章 I2C 接口 .....</b>        | <b>265</b> |

| 16.1 I2C 总线 .....                 | 265        |

| 16.1.1 I2C 总线介绍 .....             | 265        |

| 16.1.2 I2C 总线术语 .....             | 265        |

| 16.1.3 I2C 总线位传输 .....            | 266        |

| 16.1.4 I2C 总线数据传输 .....           | 266        |

| 16.1.5 I2C 总线寻址方式 .....           | 267        |

| 16.1.6 快速和高速模式 .....              | 268        |

| 16.2 I2C 总线控制器 .....              | 269        |

| 16.2.1 S5PC100 下的 I2C 控制器介绍 ..... | 269        |

| 16.2.2 I2C 总线控制寄存器詳解 .....        | 269        |

| 16.3 I2C 总线的实际应用 .....            | 270        |

| 16.3.1 应用分析 .....                 | 270        |

| 16.3.2 代码实现 .....                 | 272        |

| 16.4 本章小结 .....                   | 274        |

| 16.5 练习题 .....                    | 274        |

| <b>参考文献 .....</b>                 | <b>275</b> |

# 第1章 嵌入式系统基础知识

嵌入式系统已成为当前最为热门的领域之一，它无处不在，受到了社会各方面的广泛关注，更有越来越多的人开始学习嵌入式系统开发。本章将向读者介绍嵌入式系统的基本知识，主要内容如下：

- 嵌入式系统的概述。

- 嵌入式系统的组成。

- 嵌入式系统开发举例。

- 嵌入式系统开发概述。

## 1.1 嵌入式系统概述

### 1.1.1 嵌入式系统简介

嵌入式系统已经广泛地渗透到人们的生产、生活、学习中，我们可以看到，嵌入式系统已经应用在科学研究、工程设计、军事技术、各类产业、商业文化艺术、娱乐业及人们的日常生活等方方面面。表 1-1 列举了嵌入式系统应用的部分领域。

表 1-1 嵌入式系统应用领域举例

| 领 域   | 应 用                      |

|-------|--------------------------|

| 消费电子  | 信息家电、智能玩具、通信设备、移动存储、视频监控 |

| 工业控制  | 工控设备、智能仪表、汽车电子、电子农业      |

| 网 络   | 网络设备、电子商务、无线传感器          |

| 医务医疗  | 医疗电子                     |

| 军事国防  | 军事电子                     |

| 航空航天  | 各类飞行设备、卫星等               |

| 物 联 网 | 追溯系统、仓库存储                |

随着数字信息技术和网络技术的飞速发展，计算机、通信、消费电子的一体化趋势日益明显，这必将培育出一个庞大的嵌入式应用市场。嵌入式系统技术也成了当前关注、学习研究的热点。大家可能会问究竟什么是嵌入式系统呢？嵌入式系统本身是一个相对模糊的定义，不同的组织对其定义也略有不同，但大意是相同的，我们来看一下嵌入式系统的相关定义。

按照电器工程协会（IEEE）的定义，嵌入式系统是用来控制、监控，或者辅助操作机器、装置、工厂等大规模系统的设备（devices used to control, monitor, or assist the operation of equipment, machinery or plants）。这个定义主要是从嵌入式系统的用途方面来进行定义的。

更具一般性且在多数书籍资料中使用较多的关于嵌入式系统的定义如下：嵌入式系统是指以应用为中心，以计算机技术为基础，软件硬件可剪裁，适应应用系统对功能、可靠性、成本、体积、功耗严格要求的专用计算机系统。

根据以上嵌入式系统的定义，我们可以看出，嵌入式系统是由硬件和软件相结合组成的具有特定功能、用于特定场合的独立系统。其硬件主要由嵌入式微处理器、外围硬件设备组成；其软件主要包括底层系统软件和用户应用软件。

### 1.1.2 嵌入式系统的特点

#### 1. 专用、软/硬件可剪裁可配置

从嵌入式系统定义可以看出，嵌入式系统是面向应用的，和通用系统最大的区别在于嵌入式系统功能专一。根据这个特性，嵌入式系统的软、硬件可以根据需要进行精心设计、量体裁衣、去除冗余，以实现低成本、高性能。也正因如此，嵌入式系统采用的微处理器和外围设备种类繁多，系统不具通用性。

#### 2. 低功耗、高可靠性、高稳定性

嵌入式系统大多用在特定场合，要么是环境条件恶劣，要么要求其长时间连续运转，因此嵌入式系统应具有高可靠性、高稳定性、低功耗等特点。

#### 3. 软件代码短小精悍

由于成本和应用场合的特殊性，通常嵌入式系统的硬件资源（如内存等）都比较少，因此对嵌入式系统设计也提出了较高的要求。嵌入式系统的软件设计尤其要求高质量，要在有限的资源上实现高可靠性、高性能的系统。虽然随着硬件技术的发展和成本的降低，在高端嵌入式产品上也开始采用嵌入式操作系统，但其和 PC 资源比起来还是少得可怜，所以嵌入式系统的软件代码依然要在保证性能的情况下，占用尽量少的资源，保证产品的高性价比，使其具有更强的竞争力。

#### 4. 代码可固化

为了提高执行速度和系统可靠性，嵌入式系统中的软件一般都固化在存储器芯片或单片机本身中，而不是存储于磁盘中。

#### 5. 实时性

很多采用嵌入式系统的应用具有实时性要求，所以大多嵌入式系统采用实时性系统。但需要注意的是嵌入式系统不等于实时系统。

#### 6. 弱交互性

嵌入式系统不仅功能强大，而且要求使用灵活方便，一般不需要键盘、鼠标等。人机交互以简单方便为主。

## 7. 嵌入式系统软件开发通常需要专门的开发工具和开发环境

在开发一个嵌入式系统时，需要事先搭建开发环境及开发系统，如进行 ARM 编程时，需要安装特定的 IDE，如 MDK、IAR 等，如果需要交叉编译时，除了特定的宿主系统外，还要有目标交叉工具链，之所以这样是因为嵌入式系统不具有通用系统那样的单一性，嵌入式系统具有多样性，因此，不同的目标就要为其准备不同的开发环境。

## 8. 要求开发、设计人员有较高的技能

嵌入式系统是将先进的计算机技术、半导体技术和电子技术与各个行业的具体应用相结合后的产物。这一点就决定了它必然是一个技术密集、资金密集、高度分散、不断创新的知识集成系统，从事嵌入式系统开发的人才也必须是复合型人才。

### 1.1.3 嵌入式系统的发展

#### 1. 嵌入式系统主要经历的 4 个阶段

第 1 阶段是以单芯片为核心的可编程控制器形式的系统。这类系统大部分应用于一些专业性强的工业控制系统中，一般没有操作系统的支持，软件通过汇编语言编写。这一阶段系统的主要特点是：系统结构和功能相对单一，处理效率较低，存储容量较小，几乎没有用户接口。由于这种嵌入式系统使用简单、价格低，因此以前在国内工业领域应用较为普遍，但是现在已经远不能适应高效的、需要大容量存储的现代工业控制和新兴信息家电等领域的需求。

第 2 阶段是以嵌入式 CPU 为基础、以简单操作系统为核心的嵌入式系统。其主要特点是：CPU 种类繁多，通用性比较弱；系统开销小，效率高；操作系统达到一定的兼容性和扩展性；应用软件较专业化，用户界面不够友好。

第 3 阶段是以嵌入式操作系统为标志的嵌入式系统。其主要特点是：嵌入式操作系统能运行于各种不同类型的微处理器上，兼容性好；操作系统内核小、效率高，并且具有高度的模块化和扩展性；具备文件和目录管理，支持多任务，支持网络应用，具备图形窗口和用户界面；具有大量的应用程序接口 API，开发应用程序较简单；嵌入式应用软件丰富。

第 4 阶段是以物联网为标志的嵌入式系统。这是一个正在迅速发展的技术。物联网拥有业界最完整的专业物联产品系列，覆盖从传感器、控制器到云计算的各种应用。物联网一方面可以提高经济效益，大大节约成本；另一方面可以为全球经济的复苏提供技术动力。目前，美国、欧盟等都在投入巨资深入研究探索物联网。我国也正在高度关注、重视物联网的研究，工业和信息化部会同有关部门，在新一代信息技术方面正在开展研究，以形成支持新一代信息技术发展的政策措施。

#### 2. 未来嵌入式系统的发展趋势

##### 1) 小型化、智能化、网络化、可视化

随着技术水平的提高和人们生活的需要，嵌入式设备正朝着小型化便携式和智能化的方向发展。如果携带笔记本电脑外出办事，你肯定希望它轻薄小巧，甚至可能希望有一种更便携的设备来替代它，目前的 PAD、智能手机，便携投影仪等都是因类似的需求而出现

的。对嵌入式而言，可以说是已经进入了嵌入式互联网时代（有线网、无线网、广域网、局域网的组合），嵌入式设备和互联网的紧密结合，更为我们的日常生活带来了极大的方便和无限的想象空间。除此之外，人工智能、模式识别技术也将在嵌入式系统中得到应用，使得嵌入式系统更具人性化、智能化。

### 2) 多核技术的应用

人们需要处理的信息越来越多，这就要求嵌入式设备运算能力更强，因此需要设计出更强大的嵌入式处理器，多核技术处理器在嵌入式中的应用将更为普遍。

### 3) 低功耗（节能）、绿色环保

嵌入式系统的硬件和软件设计都在追求更低的功耗，以求嵌入式系统能获得更长的可靠工作时间。例如：手机的通话和待机时间，mp3 听音乐的时间等。同时，绿色环保型嵌入式产品将更受人们青睐，在嵌入式系统设计中也会更多地考虑如辐射和静电等问题。

### 4) 云计算、可重构、虚拟化等技术被进一步应用到嵌入式系统中

简单讲，云计算是将计算分布在大量的分布式计算机上，这样我们只需要一个终端，就可以通过网络服务来实现我们需要的计算任务，甚至是超级计算任务。云计算（Cloud Computing）是分布式处理（Distributed Computing）、并行处理（Parallel Computing）和网格计算（Grid Computing）的发展，或者说是这些计算机科学概念的商业实现。在未来几年里，云计算将得到进一步发展与应用。

可重构性是指在一个系统中，其硬件模块或（和）软件模块均能根据变化的数据流或控制流对系统结构和算法进行重新配置（或重新设置）。可重构系统最突出的优点就是能够根据不同的应用需求，改变自身的体系结构，以便与具体的应用需求相匹配。

虚拟化是指计算机软件在一个虚拟的平台上而不是真实的硬件上运行。虚拟化技术可以简化软件的重新配置过程，易于实现软件的标准。其中 CPU 的虚拟化可以单 CPU 模拟多 CPU 并行运行，允许一个平台同时运行多个操作系统，并且都可以在相互独立的空间内运行而互不影响，从而提高工作效率和安全性，虚拟化技术是降低多内核处理器系统开发成本的关键。虚拟化技术是未来几年最值得期待和关注的关键技术之一。

随着各种技术的成熟与在嵌入式系统中的应用，将不断为嵌入式系统增添新的魅力和发展空间。

### 5) 嵌入式软件开发平台化、标准化、系统可升级，代码可复用将更受重视

嵌入式操作系统将进一步走向开放、开源、标准化、组件化。嵌入式软件开发平台化也将是今后的一个趋势，越来越多的嵌入式软/硬件行业标准将出现，最终的目标是使嵌入式软件开发简单化，这也是一个必然规律。同时随着系统复杂度的提高，系统可升级和代码复用技术在嵌入式系统中得到更多的应用。

### 6) 嵌入式系统软件将逐渐 PC 化

需求和网络技术的发展是嵌入式系统发展的一个源动力，随着移动互联网的发展，将进一步促进嵌入式系统软件 PC 化。如前所述，结合跨平台开发语言的广泛应用，未来嵌入式软件开发的概念将被逐渐淡化，也就是嵌入式软件开发和非嵌入式软件开发的区别将逐渐减小。

### 7) 融合趋势

嵌入式系统软/硬件融合、产品功能融合、嵌入式设备和互联网的融合趋势加剧。嵌入式系统设计中软/硬件结合将更加紧密，软件将是其核心。消费类产品将在运算能力和便携方面进一步融合。传感器网络将迅速发展，其将极大地促进嵌入式技术和互联网技术的融合。

### 8) 安全性

随着嵌入式技术和互联网技术的结合发展，嵌入式系统的信息安全问题日益凸显，保证信息安全也成为了嵌入式系统开发的重点和难点。

## 1.2 嵌入式系统的组成

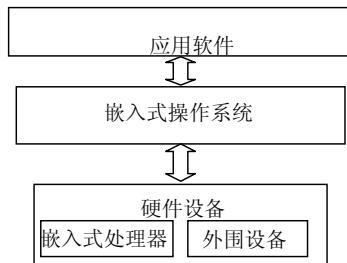

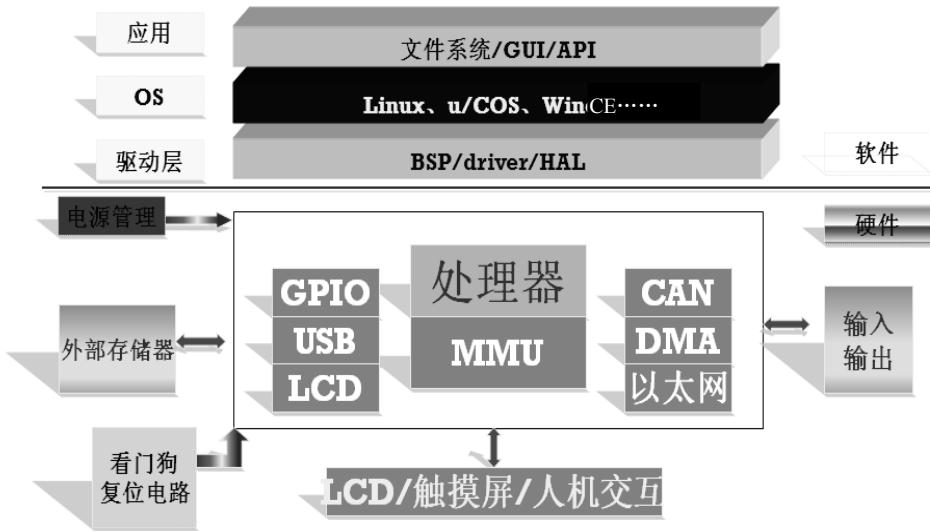

从前面的介绍我们可以知道，嵌入式系统总体上是由硬件和软件组成的，硬件是其基础，软件是其核心与灵魂。它们之间的关系如图 1-1 所示。

图 1-1 嵌入式系统结构简图

### 1.2.1 嵌入式系统硬件组成

嵌入式系统硬件设备包括嵌入式处理器和外围设备。其中的嵌入式处理器（CPU）是嵌入式系统的核心部分，它与通用处理器最大的区别在于，嵌入式处理器大多工作在为特定用户群所专门设计的系统中，它将通用处理器中许多由板卡完成的任务集成到芯片内部，从而有利于嵌入式系统在设计时趋于小型化，同时还具有很高的效率和可靠性。如今，全世界嵌入式处理器已经超过 1000 多种，流行的体系结构有 30 多个系列，其中以 ARM、PowerPC、MC 68000、MIPS 等使用得最为广泛。

外围设备是嵌入式系统中用于完成存储、通信、调试、显示等辅助功能的其他部件。目前常用的嵌入式外围设备按功能可以分为存储设备（如 RAM、SRAM、Flash 等）、通信设备（如 RS-232 接口、SPI 接口、以太网接口等）和显示设备（如显示屏等）3 类。

常见存储器概念包括：RAM、ROM、SRAM、DRAM、SDRAM、EPROM、EEPROM、Flash。

存储器可以分为很多种类，其中根据掉电数据是否丢失可以分为 RAM（随机存取存储器）和 ROM（只读存储器），其中 RAM 的访问速度比较快，但掉电后数据会丢失，而 ROM 掉电后数据不会丢失。人们通常所说的内存即指系统中的 RAM。

RAM 又可分为 SRAM（静态存储器）和 DRAM（动态存储器）。SRAM 是利用双稳态触发器来保存信息的，只要不掉电，信息是不会丢失的。DRAM 是利用 MOS（金属氧化物半导体）电容存储电荷来存储信息，因此必须通过不停地给电容充电来维持信息，所以 DRAM 的成本、集成度、功耗等明显优于 SRAM。

而通常人们所说的 SDRAM 是 DRAM 的一种，它是同步动态存储器，利用一个单一的系统时钟同步所有的地址数据和控制信号。使用 SDRAM 不但能提高系统表现，还能简化设计、提供高速的数据传输。在嵌入式系统中经常使用。

EPROM、EEPROM 都是 ROM 的一种，分别为可擦除可编程 ROM 和电可擦除 ROM，但使用不是很方便。

Flash 也是一种非易失性存储器（掉电不会丢失），它擦写方便，访问速度快，已在很大程度上取代了传统的 EPROM 的地位。由于它具有和 ROM 一样掉电不会丢失的特性，因此很多人称其为 Flash ROM。

## 1.2.2 嵌入式系统软件组成

图 1-2 嵌入式系统软件组成图

在嵌入式系统不同的应用领域和不同的发展阶段，嵌入式系统软件组成也不完全相同。其大致如图 1-2 所示。

图 1-2 左侧显示，在某些特殊领域中，嵌入式系统软件没有使用通用计算机系统。嵌入式操作系统从嵌入式发展的第 3 阶段起开始引入。嵌入式操作系统不仅具有通用操作系统的一般功能，如向上提供对用户的接口（如图形界面、库函数 API 等），向下提供与硬件设备交互的接口（硬件驱动程序等），管理复杂的系统资源，同时，它还在系统实时性、硬件依赖性、软件固化性及应用专用性等方面，具有更加鲜明的特点。

应用软件是针对特定应用领域，基于某一固定的硬件平台，用来达到用户预期目标的计算机软件。由于嵌入式系统自身的特点，决定了嵌入式应用软件不仅要求做到准确性、安全性和稳定性等方面需要，而且还要尽可能地进行代码优化，以减少对系统资源的消耗，降低硬件成本。

## 1.3 嵌入式操作系统举例

嵌入式操作系统主要有商业版和开源版两大阵营，从长远看，嵌入式系统开源、开放将是其发展趋势。

### 1.3.1 商业版嵌入式操作系统

VxWorks 作为商业版嵌入式操作系统的典型代表，这里有必要简要介绍一下。

VxWorks 操作系统是美国 WindRiver 公司于 1983 年设计开发的一种嵌入式实时操作系统（RTOS），它是在当前市场占有率最高的嵌入式实时操作系统。VxWorks 的实时性做得非常好，其系统本身的开销很小，进程调度、进程间通信、中断处理等系统公用程序精练而有效，使得它们造成的延迟很短。另外 VxWorks 提供的多任务机制，对任务的控制采用了优先级抢占（Linux 2.6 内核也采用了优先级抢占的机制）和轮转调度机制，这充分保证了可靠的实时性，并使同样的硬件配置能满足更强的实时性要求。另外 VxWorks 具有高度的可靠性，从而保证了用户工作环境的稳定。同时，VxWorks 还有很完备强大的集成开发环境，这也大大方便了用户的使用。

但是，由于 VxWorks 的开发和使用都需要交高额的专利费，因此大大增加了用户的开发成本。同时，由于 VxWorks 的源码不公开，造成它部分功能的更新（如网络功能模块）滞后。

### 1.3.2 开源版嵌入式操作系统

嵌入式 Linux（Embedded Linux）作为开源版嵌入式操作系统的典型，这里也简单介绍一下它的特性。

嵌入式 Linux 是指对标准 Linux 经过小型化裁剪处理之后，能够固化在容量只有几 KB 或者几 MB 的存储器芯片或者单片机中，是适合于特定嵌入式应用场合的专用 Linux 操作系统。在目前已经开发成功的嵌入式系统中，大约有一半使用的是 Linux。这与它自身的优良特性是分不开的。

嵌入式 Linux 同 Linux 一样，具有低成本、多种硬件平台支持、优异的性能和良好的网络支持等优点。另外，为了更好地适应嵌入式领域的开发，嵌入式 Linux 还在 Linux 基础上做了部分改进。

#### 1. 改善的内核结构

Linux 内核采用的是整体式结构（Monolithic），整个内核是一个单独的、非常大的程序，这样虽然能够使系统的各个部分直接沟通，提高系统响应速度，但与嵌入式系统存储容量小、资源有限的特点不相符。因此，在嵌入式系统经常采用的是另一种称为微内核（Microkernel）的体系结构，即内核本身只提供一些最基本的操作系统功能，如任务调度、内存管理、中断处理等，而类似于文件系统和网络协议等附加功能则运行在用户空间中，并且可以根据实际需要进行取舍。这样就大大减小了内核的体积，便于维护和移植。

#### 2. 提高的系统实时性

由于现有的 Linux 是一个通用的操作系统，虽然它也采用了许多技术来加快系统的运行和响应速度，但从本质上来说并不是一个嵌入式实时操作系统。因此，人们利用 Linux 作为底层操作系统，在其上进行实时化改造，从而构建出一个具有实时处理能力的嵌入式

系统，如 RT-Linux 已经成功地应用于航天飞机的空间数据采集、科学仪器测控和电影特技图像处理等各种领域。

## 1.4 嵌入式系统开发概述

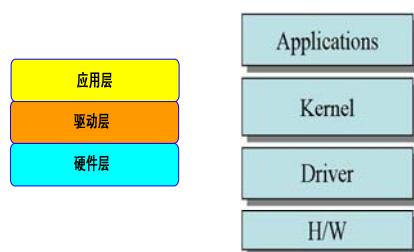

由于受嵌入式系统本身的特性所影响，嵌入式系统开发与通用系统的开发有很大的区别。嵌入式系统的开发主要分为系统总体开发、嵌入式硬件开发和嵌入式软件开发 3 大部分，其总体流程图如图 1-3 所示。

图 1-3 嵌入式系统开发流程图

在系统总体开发中，由于嵌入式系统与硬件依赖程序非常紧密，往往某些需求只能通过特定的硬件才能实现，因此需要进行处理器选型，以更好地满足产品的需求。另外，对于有些硬件和软件都可以实现的功能，就需要在成本和性能上做出选择。通过硬件实现往往增加产品的成本，但能大大提高产品的性能和可靠性。

再次，开发环境的选择对于嵌入式系统的开发也有很大的影响。这里的开发环境包括嵌入式操作系统的选择及开发工具的选择等。本书在 1.3 节对各种不同的嵌入式操作系统进行了比较，读者可以以此为依据进行相关的选择。比如，对开发成本和进度限制较大的产品可以选择嵌入式 Linux，对实时性要求非常高的产品可以选择 VxWorks 等。

嵌入式软件开发总体流程为图 1-3 中“软件设计实现”部分所示，它同通用计算机软件开发一样，分为需求分析、软件概要设计、软件详细设计、软件实现和软件测试。其中嵌入式软件需求分析与硬件的需求分析合二为一，故没有分开画出。

由于在嵌入式软件开发的工具非常多，为了更好地帮助读者选择开发工具，下面首先对嵌入式软件开发过程中所使用的工具进行简单归纳。

嵌入式软件的开发工具根据不同的开发过程而划分，比如在需求分析阶段，可以选择 IBM 的 Rational Rose 等软件，而在程序开发阶段可以采用 CodeWarrior 等，在调试阶段可以采用 Multi-ICE 等。同时，不同的嵌入式操作系统往往会有配套的开发工具，比如 VxWorks 有集成开发环境 Tornado，WinCE 的集成开发环境 WinCE Platform 等。此外，不同的处理器可能还有针对的开发工具，比如 ARM 的常用集成开发工具 ADS 等。在这里，大多数软件都有比较高的使用费用，但也可以大大加快产品的开发进度，用户可以根据需求自行选择。

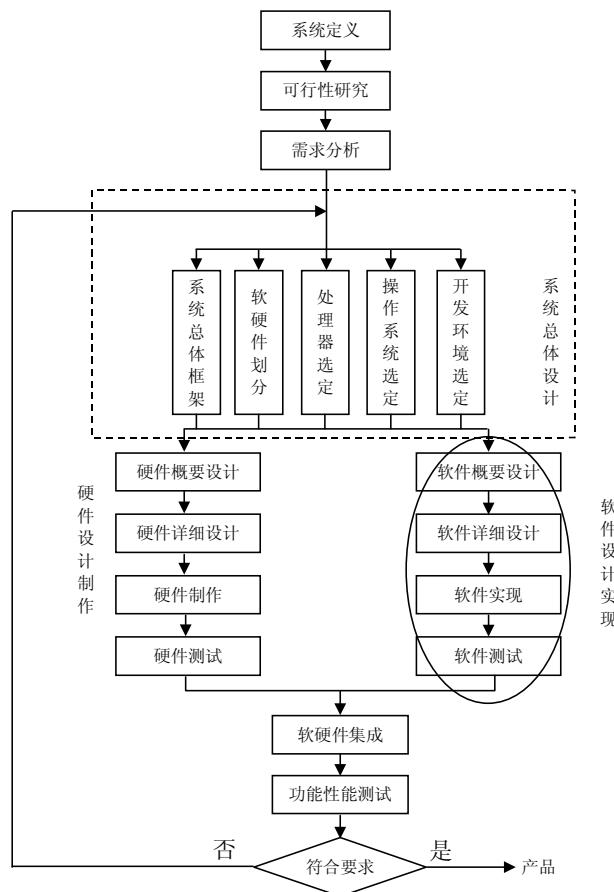

嵌入式系统的软件开发与通常软件开发的区别主要在于软件实现部分，其中又可以分为交叉编译和交叉调试两部分，下面分别对这两部分进行讲解。

### 1. 交叉编译

嵌入式软件开发所采用的编译为交叉编译。所谓交叉编译就是在在一个平台上生成可以在另一个平台上执行的代码。因此，不同的 CPU 需要有相应的编译器，而交叉编译就如同翻译一样，把相同的程序代码翻译成不同的 CPU 对应语言。要注意的是，编译器本身也是程序，也要在与之对应的某一个 CPU 平台上运行。

这里一般把进行交叉编译的主机称为宿主机，也就是普通的通用计算机，而把程序实际的运行环境称为目标机，也就是嵌入式系统环境。由于一般通用计算机拥有非常丰富的系统资源、使用方便的集成开发环境和调试工具等，而嵌入式系统的系统资源非常紧缺，没有相关的编译工具，因此，嵌入式系统的开发需要借助宿主机来编译出目标机的可执行代码。

由于编译的过程包括编译、链接等几个阶段，因此，嵌入式的交叉编译也包括交叉编译、交叉链接等过程，通常 ARM 的交叉编译器为 arm-elf-gcc，交叉链接器为 arm-elf-ld，交叉编译过程如图 1-4 所示。

图 1-4 嵌入式交叉编译过程

## 2. 交叉调试

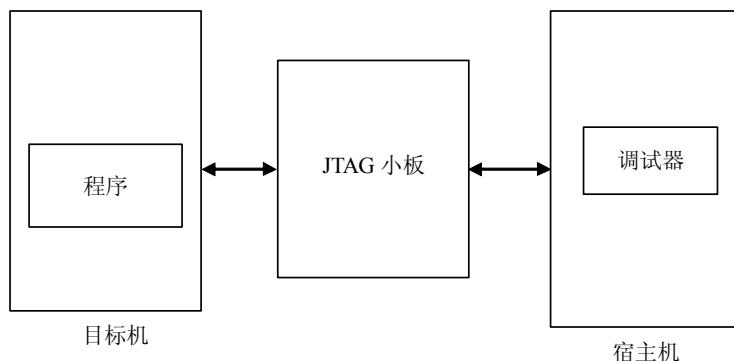

嵌入式软件经过编译和链接后即进入调试阶段，调试是软件开发过程中必不可少的一个环节，嵌入式软件开发过程中的交叉调试与通用软件开发过程中的调试方式有很大的差别。在常见软件开发中，调试器与被调试的程序往往运行在同一台计算机上，调试器是一个单独运行的进程，它通过操作系统提供的调试接口来控制被调试的进程。而在嵌入式软件开发中，调试时采用的是在宿主机和目标机之间进行的交叉调试，调试器仍然运行在宿主机的通用操作系统之上，但被调试的进程却是运行在基于特定硬件平台的嵌入式操作系统中，调试器和被调试进程通过串口或者网络进行通信，调试器可以控制、访问被调试进程，读取被调试进程的当前状态，并能够改变被调试进程的运行状态。

嵌入式系统的交叉调试有多种方法，主要可分为软件方式和硬件方式两种。它们一般都具有如下一些典型特点。

- 调试器和被调试进程运行在不同的机器上，调试器运行在 PC 或者工作站上（宿主机），而被调试的进程则运行在各种专业调试板上（目标机）。

- 调试器通过某种通信方式（串口、并口、网络、JTAG 等）控制被调试进程。

- 在目标机上一般会具备某种形式的调试代理，它负责与调试器共同配合完成对目标机上运行的进程进行调试。这种调试代理可能是某些支持调试功能的硬件设备，也可能是某些专门的调试软件（如 GdbServer）。

- 目标机可能是某种形式的系统仿真器，通过在宿主机上运行目标机的仿真软件，整个调试过程可以在一台计算机上运行。此时物理上虽然只有一台计算机，但逻辑上仍然存在着宿主机和目标机的区别。

下面分别就软件调试和硬件调试两种方式进行详细介绍。

### 1) 软件调试

软件方式调试主要是通过插入调试桩的方式来进行的。用调试桩方式进行调试是通过目标操作系统和调试器内分别加入某些功能模块，二者互通信息来进行调试。该方式的典型调试器有 Gdb 调试器。

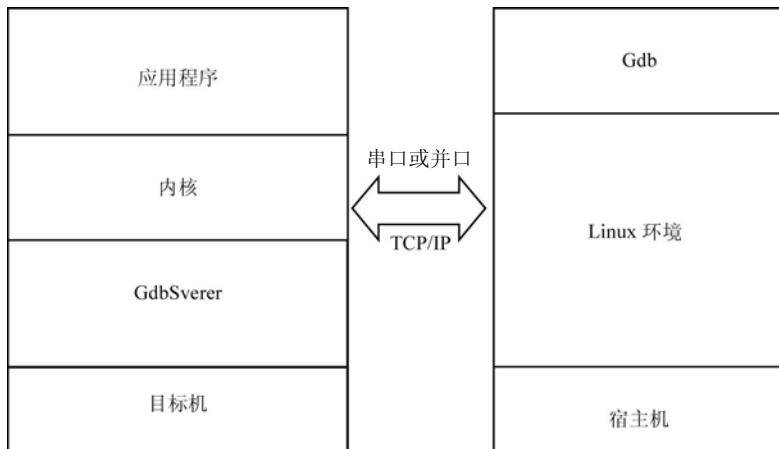

Gdb 的交叉调试器分为 GdbServer 和 GdbClient，其中的 GdbServer 作为调试桩安装在目标板上，GdbClient 是驻于本地的 Gdb 调试器。它们的调试原理如图 1-5 所示。

图 1-5 Gdb 远程调试原理图

Gdb 调试桩的工作流程如下。

- (1) 建立调试器（本地 Gdb）与目标操作系统的通信连接，可通过串口、网卡、并口等多种方式。

- (2) 在目标机上开启 GdbServer 进程，并监听对应端口。

- (3) 在宿主机上运行调试器 Gdb，这时，Gdb 就会自动寻找远端的通信进程，也就是 Gdbserver 的所在进程。

- (4) 在宿主机上的 Gdb 通过 GdbServer 请求对目标机上的程序发出控制命令。这时，Gdbserver 将请求转化为程序的地址空间或目标平台的某些寄存器的访问，这对于没有虚拟存储器的简单的嵌入式操作系统而言，是十分容易的。

- (5) GdbServer 把目标操作系统的所有异常处理转向通信模块，并告知宿主机上 Gdb 当前异常。

- (6) 宿主机上的 Gdb 向用户显示被调试程序产生了哪一类异常。

这样就完成了调试的整个过程。这个方案的实质是用软件接管目标机的全部异常处理及部分中断处理，并在其中插入调试端口通信模块，与主机的调试器进行交互。但是它只能在目标机系统初始化完毕、调试通信端口初始化完成后才能起作用，因此，一般只能用于调试运行于目标操作系统之上的应用程序，而不宜用来调试目标操作系统的内核代码及启动代码。而且，它必须改变目标操作系统，因此，也就多了一个不用于正式发布的调试版。

## 2) 硬件调试

相对于软件调试而言，使用硬件调试器可以获得更强大的调试功能和更优秀的调试性能。硬件调试器的基本原理是通过仿真硬件的执行过程，让开发者在调试时可以随时了解

到系统的当前执行情况。目前嵌入式系统开发中最常用到的硬件调试器是 ROMMonitor、ROMEEmulator、In-CircuitEmulator 和 In-CircuitDebugger。

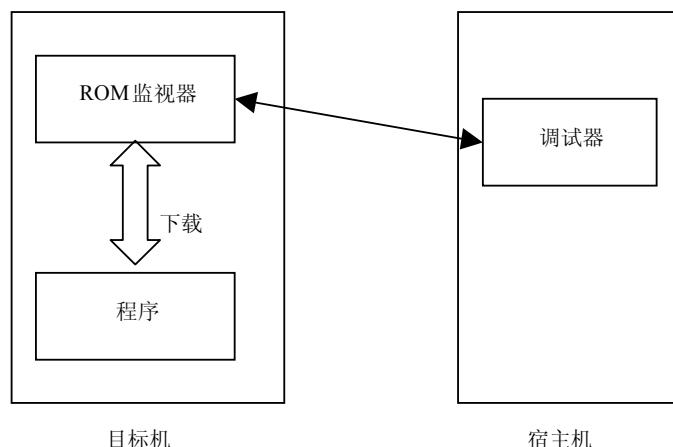

(1) 采用 ROMMonitor 方式进行交叉调试需要在宿主机上运行调试器，在目标机上运行 ROM 监视器 (ROMMonitor) 和被调试程序，宿主机通过调试器与目标机上的 ROM 监视器遵循远程调试协议建立通信连接。ROM 监视器可以是一段运行在目标机 ROM 上的可执行程序，也可以是一个专门的硬件调试设备，它负责监控目标机上被调试程序的运行情况，能够与宿主机端的调试器一同完成对应用程序的调试。

在使用这种调试方式时，被调试程序首先通过 ROM 监视器下载到目标机，然后在 ROM 监视器的监控下完成调试。

优点：ROM 监视器功能强大，能够完成设置断点、单步执行、查看寄存器、修改内存空间等各项调试功能。

缺点：同软件调试一样，使用 ROM 监视器目标机和宿主机必须建立通信连接。

其原理图如图 1-6 所示。

图 1-6 ROMMonitor 调试方式

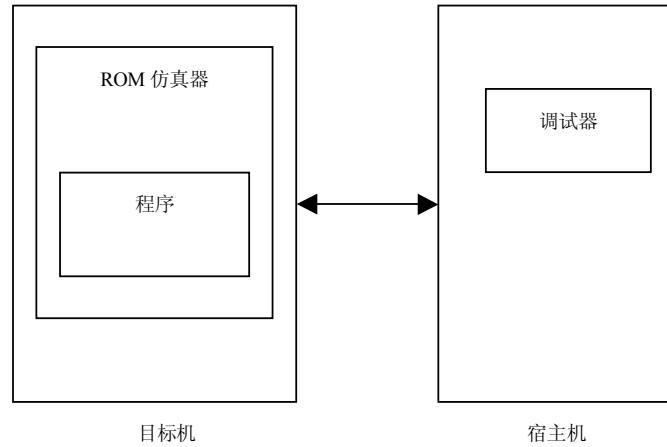

(2) 采用 ROMEEmulator 方式进行交叉调试时需要使用 ROM 仿真器，并且它通常被插入到目标机上的 ROM 插槽中，专门用于仿真目标机上的 ROM 芯片。

在使用这种调试方式时，被调试程序首先下载到 ROM 仿真器中，因此等效于下载到目标机的 ROM 芯片上，然后在 ROM 仿真器中完成对目标程序的调试。

优点：避免了每次修改程序后都必须重新烧写到目标机的 ROM 中。

缺点：ROM 仿真器本身比较昂贵，功能相对来讲又比较单一，只适应于某些特定场合。

其原理图如图 1-7 所示。

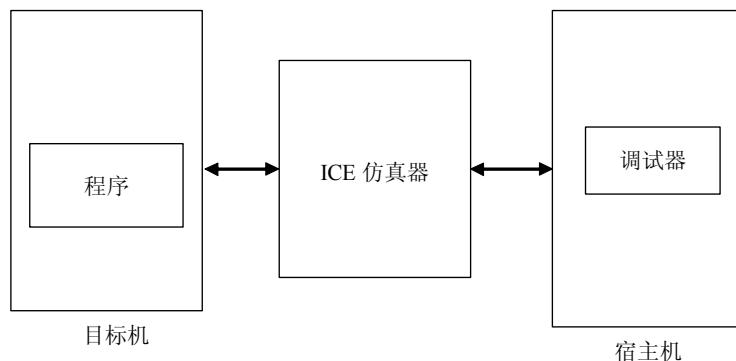

(3) 采用 In-Circuit Emulator (ICE) 方式进行交叉调试时需要使用在线仿真器，它是目前最为有效的嵌入式系统的调试手段。它是仿照目标机上的 CPU 而专门设计的硬件，可以完全仿真处理器芯片的行为。仿真器与目标板可以通过仿真头连接，与宿主机可以通过串口、并口、网线或 USB 口等连接方式。由于仿真器自成体系，所以调试时既可以连接目

标板，也可以不连接目标板。在线仿真器提供了非常丰富的调试功能。在使用在线仿真器进行调试的过程中，可以按顺序单步执行，也可以倒退执行，还可以实时查看所有需要的数据，从而给调试过程带来很多的便利。嵌入式系统应用的一个显著特点是与现实世界中的硬件直接相关，并存在各种异变和事先未知的变化，从而给微处理器的指令执行带来各种不确定因素，这种不确定性在目前情况下只有通过在线仿真器才有可能发现。

图 1-7 ROMEmulator 调试方式

优点：功能强大，软/硬件都可做到完全实时在线调试。

缺点：价格昂贵。

其原理图如图 1-8 所示。

图 1-8 ICE 调试方式

(4) 采用 In-Circuit Debugger (ICD) 方式进行交叉调试时需要使用在线调试器。由于 ICE 的价格非常昂贵，并且每种 CPU 都需要一种与之对应的 ICE，使得开发成本非常高。一个比较好的解决办法是让 CPU 直接在其内部实现调试功能，并通过在开发板上引出的调试端口发送调试命令和接收调试信息，完成调试过程。应用非常广泛的 ARM 处理器的 JTAG 端口技术就是由此而诞生的。

JTAG 是 1985 年指定的检测 PCB 和 IC 芯片的一个标准。1990 年被修改成为 IEEE 的一个标准，即 IEEE1149.1。JTAG 标准所采用的主要技术为边界扫描技术，它的基本思想就是在靠近芯片的输入/输出引脚上增加一个移位寄存器单元。因为这些移位寄存器单元都分布在芯片的边界上（周围），所以被称为边界扫描寄存器（Boundary-Scan Register Cell）。

当芯片处于调试状态时候，这些边界扫描寄存器可以将芯片和外围的输入/输出隔离开来。通过这些边界扫描寄存器单元，可以实现对芯片输入/输出信号的观察和控制。对于芯片的输入引脚，可通过与之相连的边界扫描寄存器单元把信号（数据）加载到该引脚中去；对于芯片的输出引脚，可以通过与之相连的边界扫描寄存器单元“捕获”（Capture）该引脚的输出信号。这样，边界扫描寄存器提供了一个便捷的方式用于观测和控制所需要调试的芯片。

现在较为高档的微处理器都带有 JTAG 接口，包括 ARM 经典系列、Cortex 系列、DSP 等，通过 JTAG 接口可以方便地对目标系统进行测试，同时，还可以实现 Flash 的编程，是非常受人欢迎的。

优点：连接简单，成本低。

缺点：特性受制于芯片厂商。

其原理图如图 1-9 所示。

图 1-9 JTAG 调试方式

## 1.5 学好微处理器在嵌入式学习中的重要性

处理器在嵌入式开发中非常重要，如图 1-10 所示。

图 1-10 处理器在嵌入式开发中的重要性

### 1. 处理器的角色

在嵌入式开发中，各种外设的控制器操作都要靠处理器来进行，包括初始化、数据存取等，常见的外设控制器如 LCD 控制器、USB 控制器、GPIO、电源管理器、I2C 控制器、SPI 控制器、摄像头控制器等，这些控制器的共有特征都是不仅要对处理器的体系特征有所了解，还要掌握处理器指令以便能够初始化这些控制器，使其能正常操作外设工作。

### 2. 底层的重要性

开发中，作为前期计划之一，就是硬件平台的选择，以及各个外设的选择，其中，嵌入式系统的核心部件是各种类型的嵌入式处理器。目前全世界嵌入式处理器的品种总量已经超过 1000 多种，流行体系结构有三十几个系列。但与全球 PC 市场不同的是，没有一种微处理器和微处理器公司可以主导嵌入式系统，仅以 32 位的 CPU 而言，就有 100 种以上嵌入式微处理器。由于嵌入式系统设计的差异性极大，因此选择是多样化的，这样对于嵌入式处理器的学习就显得很重要了。

### 3. 对于嵌入式理解的深度

在学习中，对于嵌入式的底层来说，除了硬件工程师，那么最底层的则是驱动开发工程师，这种工程师不仅要看得懂芯片手册，更要看懂原理图和硬件紧密相关的资料，在这些基础上才可以做好开发工作，因此，对于处理器的学习来说，不仅是对底层环境的认知加深，更是对一名嵌入式工程师的底层知识的提炼。

在学习时，学习一套嵌入式处理器架构即可，因为大部分的体系架构其实思想是相通的，只要掌握了一种处理器架构，那么其他的只要根据所占部分不大的差异而学习，就能很快掌握新的处理器。

#### 4. 行业需求

嵌入式行业是一个新兴而发展迅速的行业，随着网络等云计算技术的推广和应用，智能终端设备遍布于我们的身边，2011 年嵌入式芯片厂商 ARM 曾宣布，基于 ARM 的芯片处理器出货量已接近 80 亿个，这个数量还将以每年至少 30% 的速度增长。可见其相关联的产业之巨大，同时巨大的产业变革带来的是新型劳动力的需求和经济利益的扩大，最终，嵌入式行业对芯片型人才的紧缺是相当严重的，因此从长远考虑，学习处理器对于一位即将从事嵌入式开发的工程师来说都是势在必行的事情。

### 1.6 本章小结

本章向读者简单介绍了嵌入式系统的概念、特点、发展及开发等问题，希望通过阅读本章读者能对嵌入式系统和嵌入式系统开发有一个基本了解，以便为后面章节的学习打下基础。

### 1.7 思考题

1. 什么是嵌入式系统？列举出几个你身边熟悉的嵌入式系统的产品。

2. 嵌入式系统由哪几部分组成？

3. 列举出 3 种你知道的嵌入式操作系统。

4. 简述嵌入式系统的优点。

# 第2章 ARM技术概述

ARM体系结构的处理器在嵌入式中的应用是非常广泛的，本章将向读者介绍ARM处理器的基本知识。通过阅读本章，读者将了解以下主要内容：

- ARM体系结构的技术特征及发展。

- ARM微处理器简介。

- ARM微处理器结构。

- ARM微处理器的应用选型。

- Cortex-A8内部功能及特点。

- 数据类型。

- Cortex-A8存储系统。

- 流水线。

- 寄存器组织S。

- 程序状态寄存器。

- SAMSUNG S5PC100处理器介绍。

## 2.1 ARM体系结构的技术特征及发展

---

ARM(Advanced RISC Machines)有3种含义，它是一个公司的名称，是一类微处理器的通称，还是一种技术的名称。

### 2.1.1 ARM公司简介

1991年ARM公司(Advanced RISC Machine Limited)成立于英国剑桥，最早由Arcon、Apple和VLSI合资成立，主要出售芯片设计技术的授权，1985年4月26日，第一个ARM原型在英国剑桥的Acorn计算机有限公司诞生(在美国VLSI公司制造)。目前，ARM架构处理器已在高性能、低功耗、低成本的嵌入式应用领域中占据了领先地位。

ARM公司最初只有12人，经过多年的发展，ARM公司已拥有近千名员工，在许多国家都设立了分公司，包括在中国上海的分公司。目前，采用ARM技术知识产权(IP)核的微处理器，即我们通常所说的ARM微处理器，已遍及工业控制、消费类电子产品、通信系统、网络系统、无线系统等各类产品市场，基于ARM技术的微处理器应用约占据了32位RISC微处理器80%以上的市场份额，其中，在手机市场，ARM占有绝对的垄断地位。可以说，ARM技术正在逐步渗入到人们生活中的各个方面，而且随着32位CPU价格的不断下降和开发环境的不断成熟，ARM技术会应用得越来越广泛。

ARM 公司是专门从事基于 RISC 技术芯片设计开发的公司，作为嵌入式 RISC 处理器的知识产权 IP 供应商，公司本身并不直接从事芯片生产，而是靠转让设计许可由合作公司生产各具特色的芯片，世界各大半导体生产商从 ARM 公司购买其设计的 ARM 微处理器核，根据各自不同的应用领域，加入适当的外围电路，从而形成自己的 ARM 微处理器芯片进入市场，利用这种合伙关系，ARM 很快成为许多全球性 RISC 标准的缔造者。目前，全世界有几十家大的半导体公司都使用 ARM 公司的授权，其中包括 Intel、IBM、SAMSUNG、LG 半导体、NEC、SONY、PHILIP 等公司，这也使得 ARM 技术获得更多的第三方工具、制造厂商、软件的支持，又使整个系统成本降低，使产品更容易进入市场并被消费者所接受，更具有竞争力。

### 2.1.2 ARM 技术特征

ARM 的成功，一方面得益于它独特的公司运作模式，另一方面，当然来自于 ARM 处理器自身的优良性能。作为一种先进的 RISC 处理器，ARM 处理器有如下特点。

- 体积小、低功耗、低成本、高性能。

- 支持 Thumb（16 位）/ARM（32 位）双指令集，能很好地兼容 8 位/16 位器件。

- 大量使用寄存器，指令执行速度更快。

- 大多数数据操作都在寄存器中完成。

- 寻址方式灵活简单，执行效率高。

- 指令长度固定。

此处有必要解释一下 RISC 处理器的概念及其与 CISC 微处理器的区别。

#### 1. 嵌入式 RISC 微处理器

RISC (Reduced Instruction Set Computer) 是精简指令集计算机，RISC 把着眼点放在如何使计算机的结构更加简单和如何使计算机的处理速度更加快速上。RISC 选取了使用频率最高的简单指令，抛弃复杂指令，固定指令长度，减少指令格式和寻址方式，不用或少用微码控制。这些特点使得 RISC 非常适合嵌入式处理器。

#### 2. 嵌入式 CISC 微处理器

传统的复杂指令级计算机 (CISC) 则更侧重于硬件执行指令的功能性，使 CISC 指令及处理器的硬件结构变得更复杂。这些会导致成本、芯片体积的增加，影响其在嵌入式产品的应用。如表 2-1 所示描述了 RISC 和 CISC 之间的主要区别。

表 2-1 RISC 和 CISC 之间主要的区别

| 指 标           | RISC                                   | CISC               |

|---------------|----------------------------------------|--------------------|

| 指令集           | 一个周期执行一条指令，通过简单指令的组合实现复杂操作；指令长度固定      | 指令长度不固定，执行需要多个周期   |

| 流水线           | 流水线每周期前进一步                             | 指令的执行需要调用微代码的一个微程序 |

| 寄存器           | 更多通用寄存器                                | 用于特定目的的专用寄存器       |

| Load/Store 结构 | 独立的 Load 和 Store 指令完成数据在寄存器和外部存储器之间的传输 | 处理器能够直接处理存储器中的数据   |

### 2.1.3 ARM 体系架构的发展

在讨论 ARM 体系结构前，先解释一下体系结构的定义。

体系架构定义了指令集 (ISA) 和基于这一体系结构下处理器的编程模型。基于同种体系结构可以有多种处理器，每个处理器性能不同，所面向的应用不同，每个处理器的实现都要遵循这一体系结构。ARM 体系结构为嵌入系统发展商提供很高的系统性能，同时保持优异的功耗和面积效率。

ARM 体系结构为满足 ARM 合作者及设计领域的一般需求正稳步发展。目前，ARM 体系结构共定义了 7 个版本，从版本 1 到版本 7，ARM 体系的指令集功能不断扩大，不同系列的 ARM 处理器，性能差别很大，应用范围和对象也不尽相同，但是，如果是相同的 ARM 体系结构，那么基于它们的应用软件是兼容的。

#### 1. v1 架构

V1 版本的 ARM 处理器并没有实现商品化，采用的地址空间是 26 位，寻址空间是 64MB，在目前的版本中已不再使用这种结构。

#### 2. v2 架构

与 v1 结构的 ARM 处理器相比，v2 架构的 ARM 处理器的指令结构要有所完善，比如增加了乘法指令并且支持协处理器指令，该版本的处理器仍然采用 26 位的地址空间。

#### 3. v3 架构

从 v3 结构开始，ARM 处理器的体系结构有了很大的改变，实现了 32 位的地址空间，指令结构相对前面的两种结构也所完善。

#### 4. v4 架构

v4 结构的 ARM 处理器增加了半字指令的读取和写入操作，增加了处理器系统模式，并且有了 T 变种——v4T，在 Thumb 状态下支持的是 16 位的 Thumb 指令集。属于 v4T (支持 Thumb 指令) 体系结构的处理器 (核) 有 ARM7TDMI、ARM7TDMI-S (ARM7TDMI 综合版本)、ARM710T (ARM7TDMI 核的处理器)、ARM720T (ARM7TDMI 核的处理器)、ARM740T (ARM7TDMI 核的处理器)、ARM9TDMI、ARM910T (ARM9TDMI 核的处理器)、ARM920T (ARM9TDMI 核的处理器)、ARM940T (ARM9TDMI 核的处理器) 和 StrongARM (Intel 公司的产品)。

#### 5. v5 架构

v5 架构的 ARM 处理器提升了 ARM 和 Thumb 两种指令的交互工作能力，同时有了 DSP 指令 (-v5E 架构)、Java 指令 (-v5J 架构) 的支持。属于 v5T (支持 Thumb 指令) 体系结构的处理器 (核) 有 ARM10TDMI 和 ARM1020T (ARM10TDMI 核处理器)。

属于 v5TE (支持 Thumb、DSP 指令) 体系结构的处理器 (核) 有 ARM9E、ARM9E-S (ARM9E 可综合版本)、ARM946 (ARM9E 核的处理器)、ARM966 (ARM9E 核的处理器)、

ARM10E、ARM1020E (ARM10E 核处理器)、ARM1022E (ARM10E 核的处理器) 和 Xscale (Intel 公司产品)。

属于 v5TEJ (支持 Thumb、DSP 指令、Java) 体系结构的处理器 (核) 有 ARM9EJ、ARM9EJ-S (ARM9EJ 可综合版本)、ARM926EJ (ARM9EJ 核的处理器) 和 ARM10EJ。

### 6. v6 架构

v6 架构是在 2001 年发布的，在该版本中增加了媒体指令，属于 v6 体系结构的处理器核有 ARM11 (2002 年发布)。v6 体系结构包含 ARM 体系结构中所有的 4 种特殊指令集：Thumb 指令 (T)、DSP 指令 (E)、Java 指令 (J) 和 Media 指令。

### 7. v7 架构

ARMv7 架构是在 ARMv6 架构的基础上诞生的。该架构采用了 Thumb-2 技术，它是在 ARM 的 Thumb 代码压缩技术的基础上发展起来的，并且保持了对现存 ARM 解决方案的完整的代码兼容性。Thumb-2 技术比纯 32 位代码少使用 31% 的内存，减小了系统开销，同时能够提供比已有的基于 Thumb 技术的解决方案高出 38% 的性能。ARMv7 架构还采用了 NEON 技术，将 DSP 和媒体处理能力提高了近 4 倍。并支持改良的浮点运算，满足下一代 3D 图形、游戏物理应用及传统嵌入式控制应用的需求。

Cortex 系列处理器是基于 ARMv7 架构的，分为 Cortex-M3、Cortex-R 和 Cortex-A3 类。本章的 2.28 节将会例举一些 Cortex 的特性。

### 8. v8 架构

ARMv8 是在 32 位 ARM 架构上进行开发的，将被首先用于对扩展虚拟地址和 64 位数据处理技术有更高要求的产品领域，如企业应用、高档消费电子产品。ARMv8 架构包含两个执行状态：AArch64 和 AArch32。AArch64 执行状态针对 64 位处理技术，引入了一个全新指令集 A64，可以存取大虚拟地址空间；而 AArch32 执行状态将支持现有的 ARM 指令集。目前的 ARMv7 架构的主要特性都将在 ARMv8 架构中得以保留或进一步拓展，如 TrustZone 技术、虚拟化技术及 NEON advanced SIMD 技术等。

## 2.2 ARM 微处理器简介

ARM 处理器的产品系列非常广，包括 ARM7、ARM9、ARM9E、ARM10E、ARM11 和 SecurCore、Cortex 等。每个系列提供一套特定的性能来满足设计者对功耗、性能、体积的要求。SecurCore 是单独一个产品系列，是专门为安全设备而设计的。

表 2-2 总结了 ARM 各系列处理器所包含的不同类型。

表 2-2 ARM 各系列处理器所包含的不同类型

| ARM 系列                            | 包 含 类 型                                                                            |

|-----------------------------------|------------------------------------------------------------------------------------|

| ARM9/9E 系列                        | ARM920T<br>ARM922T<br>ARM926EJ-S<br>ARM940T<br>ARM946E-S<br>ARM966E-S<br>ARM968E-S |

| 向量浮点运算 (Vector Floating Point) 系列 | VFP9-S<br>VFP10                                                                    |

| ARM10E 系列                         | ARM1020E<br>ARM1022E<br>ARM1026EJ-S                                                |

| ARM11 系列                          | ARM1136J-S<br>ARM1136JF-S<br>ARM1156T2(F)-S<br>ARM1176JZ(F)-S<br>ARM11 MPCore      |

| Cortex 系列                         | Cortex-A<br>Cortex-R<br>Cortex-M                                                   |

| SecurCore 系列                      | SC100<br>SC110<br>SC200<br>SC210                                                   |

| 其他合作伙伴产品                          | StrongARM<br>XScale<br>MBX                                                         |

本节简要介绍 ARM 各个系列处理器的特点。

### 2.2.1 ARM9 处理器系列

ARM9 系列于 1997 年问世。由于采用了 5 级指令流水线, ARM9 处理器能够运行在比 ARM7 更高的时钟频率上, 改善了处理器的整体性能; 存储器系统根据哈佛体系结构(程序和数据空间独立的体系结构)重新设计, 区分了数据总线和指令总线。

ARM9 系列的第一个处理器是 ARM920T，它包含独立的数据指令 Cache 和 MMU (Memory Management Unit, 存储器管理单元)。此处理器能够用在要求有虚拟存储器支持的操作系统上。该系列中的 ARM922T 是 ARM920T 的变种，只有一半大小的数据指令 Cache。

ARM940T 包含一个更小的数据指令 Cache 和一个 MPU (Micro Processor Unit, 微处理器)。它是针对不要求运行操作系统的应用而设计的。ARM920T、ARM940T 都执行 v4T 架构指令。

ARM9 系列处理器主要应用于下面一些场合：

- (1) 下一代无线设备，包括视频电话和 PDA 等。

- (2) 数字消费品，包括机顶盒、家庭网关、MP3 播放器和 MPEG-4 播放器。

- (3) 成像设备，包括打印机、数码照相机和数码摄像机。

- (4) 汽车、通信和信息系统。

### 2.2.2 ARM9E 处理器系列

ARM9 系列的下一代处理器基于 ARM9E-S 内核，这个内核是 ARM9 内核带有 E 扩展的一个可综合版本，包括 ARM946E-S 和 ARM966E-S 两个变种。两者都执行 v5TE 架构指令。它们也支持可选的嵌入式跟踪宏单元，支持开发者实时跟踪处理器指令和数据的执行。当调试对时间敏感的程序段时，这种方法非常重要。

ARM946E-S 包括 TCM (Tightly Coupled Memory, 紧耦合存储器)、Cache 和一个 MPU。TCM 和 Cache 的大小可配置。该处理器是针对要求有确定的实时响应的嵌入式控制而设计的。ARM966E-S 有可配置的 TCM，但没有 MPU 和 Cache 扩展。

ARM9 系列的 ARM926EJ-S 内核为可综合的处理器内核，发布于 2000 年。它是针对小型便携式 Java 设备，如 3G 手机和 PDA 应用而设计的。ARM926EJ-S 是第一个包含 Jazelle 技术，可加速 Java 字节码执行的 ARM 处理器内核。它还有一个 MMU、可配置的 TCM 及具有零或非零等待存储器的数据/指令 Cache。

ARM9E 系列处理器主要应用于下面一些场合：

- (1) 下一代无线设备，包括视频电话和 PDA 等。

- (2) 数字消费品，包括机顶盒、家庭网关、MP3 播放器和 MPEG-4 播放器。

- (3) 成像设备，包括打印机、数码照相机和数码摄像机。

- (4) 存储设备，包括 DVD 或 HDD 等。

- (5) 工业控制，包括电机控制等。

- (6) 汽车、通信和信息系统的 ABS 和车体控制。

- (7) 网络设备，包括 VoIP、WirelessLAN 等。

### 2.2.3 ARM11 处理器系列

ARM1136J-S 发布于 2003 年，是针对高性能和高能效应而设计的。ARM1136J-S 是第一个执行 ARMv6 架构指令的处理器。它集成了一条具有独立的 Load/Stroe 和算术流水线

的 8 级流水线。ARMv6 指令包含了针对媒体处理的单指令流多数据流扩展，采用特殊的设计改善视频处理能力。

#### 2.2.4 SecurCore 处理器系列

SecurCore 系列处理器提供了基于高性能的 32 位 RISC 技术的安全解决方案。SecurCore 系列处理器除了具有体积小、功耗低、代码密度高等特点外，还具有它自己的特别优势，即提供了安全解决方案支持。下面总结了 SecurCore 系列的主要特点：

- (1) 支持 ARM 指令集和 Thumb 指令集，以提高代码密度和系统性能。

- (2) 采用软内核技术以提供最大限度的灵活性，可以防止外部对其进行扫描探测。

- (3) 提供了安全特性，可以抵制攻击。

- (4) 提供面向智能卡和低成本的存储保护单元 MPU。

- (5) 可以集成用户自己的安全特性和其他的协处理器。

SecurCore 系列包含 SC100、SC110、SC200 和 SC210 四种类型。

SecurCore 系列处理器主要应用于一些安全产品及应用系统，包括电子商务、电子银行业务、网络、移动媒体和认证系统等。

#### 2.2.5 StrongARM 和 Xscale 处理器系列

StrongARM 处理器最初是 ARM 公司与 Digital Semiconductor 公司合作开发的，现在由 Intel 公司单独许可，在低功耗、高性能的产品中应用很广泛。它采用哈佛架构，具有独立的数据和指令 Cache，有 MMU。StrongARM 是第一个包含 5 级流水线的高性能 ARM 处理器，但它不支持 Thumb 指令集。

Intel 公司的 Xscale 是 StrongARM 的后续产品，在性能上有显著改善。它执行 V5TE 架构指令，也采用哈佛结构，类似于 StrongARM 也包含一个 MMU。前面说过，Xscale 已经被 Intel 卖给了 Marvell 公司。

#### 2.2.6 MPCore 处理器系列

MPCore 是在 ARM11 核心的基础上构建的，结构上仍属于 V6 指令体系。根据不同的需要，MPCore 可以被配置为 1 到 4 个处理器的组合方式，最高性能达到 2600 Dhystone MIPS，运算能力几乎与 Pentium III 1GHz 处于同一水准（Pentium III 1GHz 的指令执行性能约为 2700 Dhystone MIPS）。多核心设计的优点是在频率不变的情况下让处理器的性能获得明显提升，在多任务应用中表现尤其出色，这一点很适合未来家庭消费电子的需要。例如，机顶盒在录制多个频道电视节目的同时，还可通过互联网收看数字视频点播节目；车内导航系统在提供导航功能的同时，可以向后座乘客提供各类视频娱乐信息等。在这类应用环境下，多核心结构的嵌入式处理器将表现出极强的性能优势。

## 2.2.7 Cortex 处理器系列

### 1. ARM Cortex 处理器技术特点

ARMv7 架构是在 ARMv6 架构的基础上诞生的。该架构采用了 Thumb-2 技术，它是在 ARM 的 Thumb 代码压缩技术的基础上发展起来的，并且保持了对现存 ARM 解决方案的完整的代码兼容性。Thumb-2 技术比纯 32 位代码少使用 31% 的内存，减小了系统开销，同时能够提供比已有的基于 Thumb 技术的解决方案高出 38% 的性能。ARMv7 架构还采用了 NEON 技术，将 DSP 和媒体处理能力提高了近 4 倍。并支持改良的浮点运算，满足下一代 3D 图形、游戏物理应用及传统嵌入式控制应用的需求。此外，ARMv7 还支持改良的运行环境，以迎合不断增加的 JIT (Just In Time) 和 DAC (Dynamic Adaptive Compilation) 技术的使用。

在与早期的 ARM 处理器软件兼容性方面，ARMv7 架构在设计时充分考虑到了。ARM Cortex-M 系列支持 Thumb-2 指令集 (Thumb 指令集的扩展集)，可以执行所有已存的为早期处理器编写的代码。通过一个前向的转换方式，为 ARM Cortex-M 系列处理器所写的用户代码可以与 ARM Cortex-R 系列微处理器完全兼容。ARM Cortex-M 系列系统代码 (如实时时操作系统) 可以很容易地移植到基于 ARM Cortex-R 系列的系统上。ARM Cortex-A 和 Cortex-R 系列处理器还支持 ARM 32 位指令集，向后完全兼容早期的 ARM 处理器，包括 1995 年发布的 ARM7TDMI 处理器，2002 年发布的 ARM11 处理器系列。由于应用领域的不同，基于 v7 架构的 Cortex 处理器系列所采用的技术也不相同。在命名方式上，基于 ARMv7 架构的 ARM 处理器已经不再延用过去的数字命名方式，而是冠以 Cortex 的代号。基于 v7A 的称为“Cortex-A 系列”，基于 v7R 的称为“Cortex-R 系列”，基于 v7M 的称为“Cortex-M3”。

### 2. ARM Cortex-M3 处理器技术特点

ARM Cortex-M3 处理器是为存储器和处理器的尺寸对产品成本影响极大的各种应用专门开发设计的。它整合了多种技术，减少了内存使用，并在极小的 RISC 内核上提供低功耗和高性能，可实现由以往的代码向 32 位微控制器的快速移植。ARM Cortex-M3 处理器是使用最少门数的 ARM CPU，相对于过去的设计大大减小了芯片面积，可减小装置的体积或采用更低成本的工艺进行生产，仅 33000 门的内核性能可达 1.2DMIPS/MHz。此外，基本系统外设还具备高度集成化特点，集成了许多紧耦合系统外设，合理利用了芯片空间，使系统满足下一代产品的控制需求。

ARM Cortex-M3 处理器结合了执行 Thumb-2 指令的 32 位哈佛微体系结构和系统外设，包括 Nested Vectored Interrupt Controller 和 Arbiter 总线。该技术方案在测试和实例应用中表现出较高的性能：在台机电 180 nm 工艺下，芯片性能达 1.2 DMIPS/MHz，时钟频率高达 100 MHz。Cortex-M3 处理器还实现了 Tail-Chaining 中断技术。该技术是一项完全基于硬件的中断处理技术，最多可减少 12 个时钟周期数，在实际应用中可减少 70% 的中断；推出了新的单线调试技术，避免使用多引脚进行 JTAG 调试，并全面支持 RealView 编译器和 RealView 调试产品。Realview 工具向设计者提供模拟、创建虚拟模型、编译软件、调试、验证和测试基于 ARMv7 架构的系统等功能。

为微控制器应用而开发的 Cortex-M3 拥有以下性能：

- 实现单周期 Flash 应用最优化。

- 准确快速地中断处理。永不超过 12 周期，仅 6 周期 tail-chaining（末尾连锁）。

- 有低功耗时钟门控（Clock Gating）的 3 种睡眠模式。

- 单周期乘法和乘法累加指令。

- ARM Thumb-2 混合的 16/32 位固有指令集，无模式转换。

- 包括数据观察点和 Flash 补丁在内的高级调试功能。

- 原子位操作，在一个单一指令中读取/修改/编写。

- 1. 25DMIPS/MHz（与 0. 9DMIPS/MHz 的 ARM7 和 1. 1DMIPS/MHz 的 ARM9 相比）。

### 3. ARM Cortex-R4 处理器技术特点

Cortex-R4 处理器支持手机、硬盘、打印机及汽车电子设计，能协助新一代嵌入式产品快速执行各种复杂的控制算法与实时工作的运算；可通过内存保护单元（Memory Protection Unit, MPU）、高速缓存及紧密耦合内存（Tightly Coupled Memory, TCM）让处理器针对各种不同的嵌入式应用进行最佳化调整，且不影响基本的 ARM 指令集兼容性。这种设计能够在沿用原有程序代码的情况下，降低系统的成本与复杂度，同时其紧密耦合内存功能也能提供更小的规格及更高效率的整合，并带来快速的响应时间。

Cortex-R4 处理器采用 ARMv7 体系结构，让它能与现有的程序维持完全的回溯兼容性，能支持现今在全球各地数十亿的系统，并已针对 Thumb-2 指令进行最佳化设计。此项特性带来很多的利益，其中包括：更低的时钟速度所带来的省电效益；更高的性能将各种多功能特色带入移动电话与汽车产品的设计；更复杂的算法支持更高性能的数码影像与内建硬盘的系统。运用 Thumb-2 指令集，加上 RealView 开发套件，使芯片内部存储器的容量最多降低 30%，大幅降低系统成本，其速度比在 ARM9tt6E-S 处理器所使用的 Thumb 指令集高出 40%。由于存储器在芯片中的占用空间愈来愈多，因此这项设计将大幅节省芯片容量，让芯片制造商运用这款处理器开发各种 SoC（System on a Chip）器件。

相比于前几代的处理器，Cortex-R4 处理器高效率的设计方案，使其能以更低的时钟达到更高的性能；经过最佳化设计的 Artisan Metro 内存，可进一步降低嵌入式系统的体积与成本。处理器搭载一个先进的微架构，具备双指令发送功能，采用 90nm 工艺并搭配 Artisan Advantage 程序库的组件，底面积不到 1mm<sup>2</sup>，耗电最低低于 0.27mW/MHz，并能提供超过 600 DMIPS 的性能。

Cortex-R4 处理器在各种安全应用上加入容错功能和内存保护机制，支持最新版 OSEK 实时操作系统；支持 RealView Develop 系列软件开发工具、RealView Create 系列 ESL 工具与模块，以及 Core Sight 除错与追踪技术，协助设计者迅速开发各种嵌入式系统。

### 4. ARM Cortex-A8 处理器技术特点

ARM Cortex-A8 处理器是一款适用于复杂操作系统及用户应用的应用处理器，支持智能能源管理（Intelligent Energy Manager, IEM）技术的 ARM Artisan 库及先进的泄漏控制技

术，使得 Cortex-A8 处理器实现了非凡的速度和功耗效率。在 65nm 工艺下，ARM Conex-A8 处理器的功耗不到 300mW，能够提供高性能和低功耗。它第一次为低费用、高容量的产品带来了台式机级别的性能。

Conex-A8 处理器是第一款基于下一代 ARMv7 架构的应用处理器，使用了能够带来更高性能、更低功耗和更高代码密度的 Thumb-2 技术。它首次采用了强大的 NEON 信号处理扩展集，为 H.264 和 MP3 等媒体编解码提供加速。Cortex-A8 的解决方案还包括 Jazelle-RCTJava 加速技术，对实时 (JTT) 和动态调整编译 (DAC) 提供最优化，同时减少内存占用空间高达 3 倍。该处理器配置了先进的超标量体系结构流水线，能够同时执行多条指令。处理器集成了一个可调尺寸的二级高速缓冲存储器，能够同高速的 16KB 或者 32KB 一级高速缓冲存储器一起工作，从而达到最快的读取速度和最大的吞吐量。新处理器还配置了用于安全交易和数字版权管理的 Trust Zone 技术，以及实现低功耗管理的 IEM 功能。

Cortex-A8 处理器使用了先进的分支预测技术，并且具有专用的 NEON 整型和浮点型流水线进行媒体和信号处理。在使用小于  $4\text{mm}^2$  的硅片及低功耗的 65 nm 工艺的情况下，Cortex-A8 处理器的运行频率将高于 600MHz(不包括 NEON 追踪技术和二级高速缓冲存储器)。在高性能的 90nm 和 65nm 工艺下，Cortex-A8 处理器运行频率最高可达 1GHz，能够满足高性能消费产品设计的需要。

## 2.2.8 最新 ARM 应用处理器发展现状

(1) 从之前的 ARM 单核逐步向双核演变。作为对比，下面依次将近年来最尖端的芯片应用方案列举出来。

- NVIDIA (英伟达) 的 Tegra 2 双核处理器及 Tegra 3 四核处理器，已经应用在摩托罗拉双核智能手机 ME860 及 LG Optimus 2X 手机上。

- 三星 Exynos 4210，基于 CORTEX-A9 的双核处理器，目前应用在三星公司推出的 GALAXY SII 智能手机。

- TI 的 OMAP4430 及 OMAP4460 双核 ARM 处理芯片，已应用在 LG Optimus 3D 手机。

- 高通 MSM8260、MSM8660 (1.5G)、MSM8960 (1.7G) 双核处理器及 APQ8060 (2.5G) 四核心处理器。目前应用的代表有 HTC 的金字塔 (Pyramid) 双核智能手机，还有国内的小米手机。

- 苹果 A5 双核处理器，典型代表是 iPhone4S 与 iPad2。

(2) 内嵌的图形显示芯片越来越强劲。

- Mali 系列由 ARM 出品，Mali-400、Mali-T658 于 2011 年 11 月推出，支持 OpenGL ES 2.0 和 DirectX 接口，可从单核扩展到四核，可提供卓越的二维和三维加速性能。

- PowerVR SGX 系列由 Imagination Technologies 公司出品，包括 PowerVR SGX530/535/540/543MP，支持 DirectX 9、SM3.0 和 OpenGL 2.0。

- SGX535 被苹果公司的 iPhone4 和 iPad 采用，而 SGX540 性能更加强劲，在三星 Galaxy Tab 与魅族 M9 上采用。SGX543MP 作为新一代最强新品，目前已成为苹

果 iPad 2 (SGX543MP2/双核) 和索尼 NGP (SGX543MP4/四核) 的图形内核。

- Adreno 系列由高通公司出品，主要配合 Snapdragon CPU 使用。旗下典型方案有 Adreno200/205/220/300。

- 在图形处理单元上，Tegra 3 从之前 Tegra 2 的 8 核心图形单元升级到 12 核心单元，NV5DIA 官方宣布将有 3 倍的图形性能提升。这 12 个处理核心的 GeForce GPU 专门为下一代移动游戏而打造（完全兼容现有 Tegra 2 游戏），支持更好的动态光影、物理效果和高分辨率环境。典型处理器方案有 NVIDIA Tegra 2 和 NVIDIA Tegra 3。

(3) 支持大 RAM，支持大数据量的存储介质。

现在诸多处理器已支持 DDR2、DDR3、LPDDR (mDDR) 等类型的内存。这些类型的内存高速度，高精度，并且容量也很高，已属于高速硬件之一。

(4) 提升显示控制器性能。最高  $2048 \times 1536$  分辨率液晶屏显示，如 Tegra 3 处理器。

(5) 提升 Camera 性能。最高支持 3200 万像素摄像头

## 2.3 ARM 微处理器结构

ARM 内核采用 RISC 体系结构。ARM 体系结构的主要特征如下：

- (1) 采用大量的寄存器，它们都可以用于多种用途。

- (2) 采用 Load/Store 体系结构。

- (3) 每条指令都条件执行。

- (4) 采用多寄存器的 Load/Store 指令。

- (5) 能够在单时钟周期执行的单条指令内完成一项普通的移位操作和一项普通的 ALU 操作。

- (6) 通过协处理器指令集来扩展 ARM 指令集，包括在编程模式中增加了新的寄存器和数据类型。

- (7) 如果把 Thumb 指令集也当做 ARM 体系结构的一部分，那么在 Thumb 体系结构中还可以高密度 16 位压缩形式表示指令集。

## 2.4 ARM 微处理器的应用选型

随着国内嵌入式应用领域的发展，ARM 芯片必然会获得广泛的重视和应用。但是由于 ARM 芯片有多达十几种的芯核结构、70 多个芯片生产厂家及千变万化的内部功能配置组合，开发人员在选择方案时会有一定的困难。所以对 ARM 芯片做对比研究是十分必要的。

### 2.4.1 ARM 芯片选择的一般原则

#### 1. 功能

考虑处理器本身能够支持的功能，如 USB、网络、串口、液晶显示功能等。

#### 2. 性能

从处理器的功耗、速度、稳定可靠性等方面考虑。

#### 3. 价格

通常产品总是希望在完成功能要求的基础上，成本越低越好。在选择处理器时需要考虑处理的价格，及由处理器衍生出的开发价格。如开发板价格、处理器自身价格、外围芯片、开发工具、制版价格等。

#### 4. 熟悉程度及开发资源

通常公司对产品的开发周期都有严格的要求，选择一款自己熟悉的处理器可以大大降低开发风险。在自己熟悉的处理器都无法满足功能的情况下，可以尽量选择开发资源丰富的处理器。

#### 5. 操作系统支持

在选择嵌入式处理器时，如果最终的程序需要运行在操作系统上，那么还应该考虑处理器对操作系统的支持。

#### 6. 升级

很多产品在开发完成后都会面临升级的问题，正所谓人无远虑必有近忧。所以在选择处理器时必须要考虑升级的问题。如尽量选择具有相同封装的不同性能等级的处理器；考虑产品未来可能增加的功能。

#### 7. 供货稳定

供货稳定也是选择处理器时的一个重要参考因素，尽量选择大厂家，比较通用的芯片。

### 2.4.2 选择一款适合 ARM 教学的 CPU

在 ARM 教学中，在选择 CPU 作为学习目标时，主要从芯片功能、开发平台价格、开发资源等方面考虑。

#### 1. ARM 芯核

如果希望学习使用 Windows CE 或 Linux 等操作系统，就需要选择 ARM720T 以上带有 MMU（Memory Management Unit）功能的 ARM 芯片，ARM720T、StrongARM、Cortex-A 系列处理器都带有 MMU 功能。而 ARM7TDMI 没有 MMU，不支持 Windows CE 和大部分的 Linux。目前，uCLinux 及 Linux 2.6 内核等 Linux 系统不需要 MMU 的支持。

## 2. 系统时钟速度

系统时钟决定了 ARM 芯片的处理速度。ARM7 的处理速度为 0.97MIPS/MHz, 常见的 ARM7 芯片系统主时钟为 20~133MHz, ARM9 的处理速度为 1.1MIPS/MHz, 常见的 ARM9 的系统主时钟为 100~233MHz。Cortex-A 系列的主时钟频率也越来越快, 如 Cortex-A8 主频率可以达到 1.2GHz, 如果希望学习可以支持较为复杂的操作系统的芯片时, 可以选择 ARM9 及 ARM9 以上的芯片。

## 3. 支持内存访问的类型

支持内存访问的类型如表 2-3 所示。

表 2-3 支持内存访问的类型

| 芯片名     | 是否有 SDRAM | 是否有 DDR2 | 是否有 mDDR | 是否有 DDR3 |

|---------|-----------|----------|----------|----------|

| S3C2410 | 是         | 否        | 否        | 否        |

| S3C2440 | 是         | 否        | 否        | 否        |

| S5PC100 | 否         | 是        | 否        | 否        |

| S5PV310 | 否         | 否        | 否        | 是        |

## 4. USB 接口

USB 接口产品的使用越来越广泛, 许多 ARM 芯片内置 USB 控制器, 有些芯片甚至同时有 USB Host 和 USB Slave 控制器。表 2-4 显示了内置 USB 控制器的 ARM 芯片。

表 2-4 内置 USB 控制器的 ARM 芯片

| 芯 片 型 号 | ARM 内核    | 供 应 商   | USB (otg) | USB Host |

|---------|-----------|---------|-----------|----------|

| S3C2410 | ARM920T   | SAMSUNG | 1         | 2        |

| S3C2440 | ARM920T   | SAMSUNG | 1         | 2        |

| S5PC100 | CORTEX-A8 | SAMSUNG | 1         | 1        |

| S5PV310 | CORTEX-A9 | SAMSUNG | 1         | 1        |

## 5. GPIO 数量

在某些芯片供应商提供的说明书中, 往往申明的是最大可能的 GPIO 数量, 但是有许多引脚是和地址线、数据线、串口线等引脚复用的。这样在系统设计时需要计算实际可以使用的 GPIO 数量。

## 6. 中断控制器

ARM 内核只提供快速中断 (FIQ) 和标准中断 (IRQ) 两个中断向量。但各个半导体厂家在设计芯片时加入了自己定义的中断控制器, 以便支持诸如串行口、外部中断、时钟中断等硬件中断。外部中断控制是选择芯片时必须考虑的重要因素, 合理的外部中断设计可以很大程度地减少任务调度工作量。例如 PHILIPS 公司的 SAA7750, 所有 GPIO 都可以设置成 FIQ 或 IRQ, 并且可以选择上升沿、下降沿、高电平和低电平 4 种中断方式。这使

得红外线遥控接收、指轮盘和键盘等任务都可以作为背景程序运行。而 Cirrus Logic 公司的 EP7312 芯片只有 4 个外部中断源，并且每个中断源都只能是低电平或高电平中断，这样接收红外线信号的场合必须用查询方式，浪费大量 CPU 时间。

## 7. IIS (Integrate Interface of Sound) 接口

IIS 接口即集成音频接口。如果设计音频应用产品，IIS 接口是必需的。

## 8. nWAIT 信号

这是一个外部总线速度控制信号。不是每个 ARM 芯片都提供这个信号引脚，利用这个信号与廉价的 GAL 芯片就可以实现符合 PCMCIA 标准的 WLAN 卡和 BlueTooth 卡的接口，而不需要外加高成本的 PCMCIA 专用控制芯片。另外，当需要扩展外部 DSP 协处理器时，此信号也是必需的。

## 9. RTC (Real Time Clock)

很多 ARM 芯片都提供 RTC (实时时钟) 功能，但方式不同。如 Cirrus Logic 公司的 EP7312 的 RTC 只是一个 32 位计数器，需要通过软件计算出年月日时分秒；而 SAA7750 和 S3C2410 等芯片的 RTC 直接提供年月日时分秒格式。

## 10. LCD 控制器

有些 ARM 芯片内置 LCD 控制器，有的甚至内置 64KB 彩色 TFT LCD 控制器。在设计 PDA 和手持式显示记录设备时，选用内置 LCD 控制器的 ARM 芯片（如 S3C2410）较为适宜。

## 11. PWM 输出

有些 ARM 芯片有 2~8 路 PWM 输出，可以用于电机控制或语音输出等场合。

## 12. ADC 和 DAC

有些 ARM 芯片内置 2~8 通道 8~12 位通用 ADC，可以用于电池检测、触摸屏和温度监测等。PHILIPS 的 SAA7750 更是内置了一个 16 位立体声音频 ADC 和 DAC，并且带耳机驱动。

## 13. 扩展总线

大部分 ARM 芯片具有外部 SDRAM 和 SRAM 扩展接口，不同的 ARM 芯片可以扩展的芯片数量即片选线数量不同，外部数据总线有 8 位、16 位或 32 位。为某些特殊应用设计的 ARM 芯片（如德国 Micronas 的 PUC3030A）没有外部扩展功能。

## 14. UART 和 IrDA

几乎所有的 ARM 芯片都具有 1~2 个 UART 接口，可以用于和 PC 通信或用 Angel 进行调试。一般的 ARM 芯片通信波特率为 115200bit/s，少数专为蓝牙技术应用设计的 ARM 芯片的 UART 通信波特率可以达到 920kbit/s，如 Linkup 公司 L7205。

### 15. 时钟计数器和看门狗

一般 ARM 芯片都具有 2~4 个 16 位或 32 位时钟计数器和一个看门狗计数器。

### 16. 电源管理功能

ARM 芯片的耗电量与工作频率成正比，一般 ARM 芯片都有低功耗模式、睡眠模式和关闭模式。

### 17. DMA 控制器

有些 ARM 芯片内部集成 DMA (Direct Memory Access) 接口，可以和硬盘等外部设备高速交换数据，同时减少数据交换时对 CPU 资源的占用。

另外，可以选择的内部功能部件还有 HDLC、SDLC、CD-ROM Decoder、Ethernet MAC、VGA controller 和 DC-DC。可以选择的内置接口有：IIC、SPDIF、CAN、SPI、PCI 和 PCMCIA。

### 18. 封装类型

最后需说明的是封装问题。ARM 芯片现在主要的封装有 QFP、TQFP、PQFP、LQFP、BGA、LBGA 等形式，BGA 封装具有芯片面积小的特点，可以减少 PCB 的面积，但是需要专用的焊接设备，无法手工焊接。另外，一般 BGA 封装的 ARM 芯片无法用双面板完成 PCB 布线，需要多层 PCB 板布线。

最后，根据大专、高职院校的实际情况结合当前及未来一段时间的市场人才需求，经过综合考虑，本书教学选取的是三星公司的 S5PC100 芯片。S5PC100 是一款基于 Cortex-A8 核心的微处理器芯片。本章的后面部分章节将对 Cortex-A8 的一些特性及 S5PC100 进行详细介绍。

## 2.5 Cortex-A8 内部功能及特点

Cortex-A8 处理器是一款高性能、低功耗的处理器核心，并支持 Cache、虚拟存取，它的特性如下：

- 完全执行 v7-A 体系指令集。

- 可配置 64 位或 128 位 AMBA 高速总线接口 AXI。

- 具有一个集成的整形流水线。

- 具有一个 NEON 技术下执行 SIMD/VFP 的流水线。

- 支持动态分支预取，全局历史缓存，8 入口返回栈。

- 具有独立的数据/指令 MMU。

- 16KB/32KB 可配置 1 级 Cache。

- 具有带奇偶校验及 ECC 校验的 2 级 Cache。

- 支持 ETM 的非侵入式调试。

- 具有静态/动态电源管理功能。

ARMv7 体系指令集方面表现如下特点：

- 支持 ARM Thumb-2 高密度指令集。

- 使用 ThumbEE，执行环境加速。

- 安全扩展体系加强了安全应用的可靠性。

- 先进的 SIMD 体系技术用于加速多媒体应用。

- 支持 VFP 第三代向量浮点运算。

## 2.6 数据类型

### 2.6.1 ARM 的基本数据类型

ARM 采用的是 32 位架构，ARM 的基本数据类型有以下 3 种。

- **Byte**: 字节，8bit。

- **Halfword**: 半字，16bit（半字必须与 2 字节边界对齐）。

- **Word**: 字，32bit（字必须与 4 字节边界对齐）。

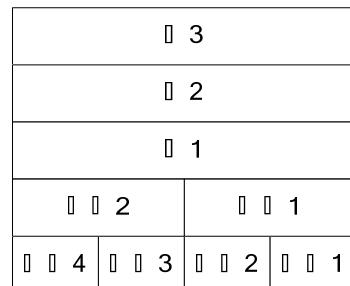

存储器可以看做是序号为  $0 \sim 2^{32}-1$  的线性字节阵列。如图 2-1 所示为 ARM 存储器的组织结构。其中每一个字节都有唯一的地址。字节可以占用任一位置，图中给出了几个例子。长度为 1 个字的数据项占用一组 4 字节的位置，该位置

开始于 4 的倍数的字节地址（地址最末两位为 00）。半字占有两个字节的位置，该位置开始于偶数字节地址（地址最末一位为 0）。

图 2-1 ARM 存储器组织结构

#### 注意

- (1) ARM 系统结构 v4 以上版本支持以上 3 种数据类型，v4 以前版本仅支持字节和字。

- (2) 当将这些数据类型中的任意一种声明成 unsigned 类型时， $n$  位数据值表示范围为  $0 \sim 2^n-1$  的非负数，通常使用二进制格式。

- (3) 当将这些数据类型的任意一种声明成 signed 类型时， $n$  位数据值表示范围为  $-2^{n-1} \sim 2^{n-1}-1$  的整数，使用二进制的补码格式。

- (4) 所有数据类型指令的操作数都是字类型的，如“ADD r1, r0, #0x1”中的操作数“0x1”就是以字类型数据处理的。

- (5) Load/Store 数据传输指令可以从存储器存取传输数据，这些数据可以是字节、半字、字。加载时自动进行字节或半字的零扩展或符号扩展。对应的指令分别为 LDR/BSTRB(字节操作) LDRH/STRH(半字操作) LDR/STR(字操作)。详见后面的指令参考。

- (6) ARM 指令编译后是 4 个字节(与字边界对齐)。Thumb 指令编译后是 2 个字节(与半字边界对齐)。

## 2.6.2 浮点数据类型

浮点运算使用在 ARM 硬件指令集中未定义的数据类型。尽管如此，但 ARM 公司在协处理器指令空间定义了一系列浮点指令。通常这些指令全部可以通过未定义指令异常（此异常收集所有硬件协处理器不接受的协处理器指令）在软件中实现，但是其中的一小部分也可以由浮点运算协处理器 FPA10 以硬件方式实现。另外，ARM 公司还提供了用 C 语言编写的浮点库作为 ARM 浮点指令集的替代方法（Thumb 代码只能使用浮点指令集）。该库支持 IEEE 标准的单精度和双精度格式。C 编译器有一个关键字标志来选择这个历程。它产生的代码与软件仿真（通过避免中断、译码和浮点指令仿真）相比既快又紧凑。

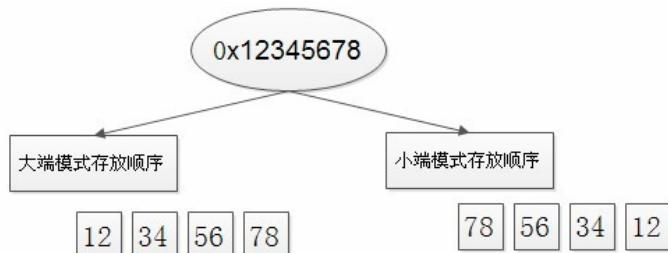

## 2.6.3 存储器大/小端

从软件角度看，内存相对于一个大的字节数组，其中每个数组元素（字节）都是可寻址的。

ARM 支持大端模式（big-endian）和小端模式（little-endian）两种内存模式。

如图 2-2 所示显示了大端模式和小端模式数据存放特点。

图 2-2 大小端模式存放数据的特点

下面的例子显示了使用内存大/小端（big/little endian）的存取格式。

程序执行前：

```

r0=0x11223344

```

执行指令：

```

r1=0x100

STR r0, [r1]

LDRB r2, [r1]

```

执行后：

```

小端模式下：r2=0x44

大端模式下：r2=0x11

```

上面的例子向我们提示了一个潜在的编程隐患。在大端模式下，一个字的高地址放的是数据的低位，而在小端模式下，数据的低位放在内存中的低地址。要小心对待存储器中一个字内字节的顺序。

## 2.7 Cortex-A8 内核工作模式

Cortex-A8 基于 ARMv7-A 架构，共有 8 种工作模式，如表 2-5 所示。

表 2-5 S5PC100 处理器的工作模式

| 处理器工作模式           | 简写  | 描述                                           |

|-------------------|-----|----------------------------------------------|

| 用户模式 (User)       | usr | 正常程序执行模式，大部分任务执行在这种模式下                       |

| 快速中断模式 (FIQ)      | fiq | 当一个高优先级 (fast) 中断产生时将会进入这种模式，一般用于高速数据传输和通道处理 |

| 外部中断模式 (IRQ)      | irq | 当一个低优先级 (normal) 中断产生时将会进入这种模式，一般用于通常的中断处理   |

| 特权模式 (Supervisor) | svc | 当复位或软中断指令执行时进入这种模式，是一种供操作系统使用的保护模式           |

| 数据访问中止模式 (Abort)  | abt | 当存取异常时将会进入这种模式，用于虚拟存储或存储保护                   |

| 未定义指令中止模式 (Undef) | und | 当执行未定义指令时进入这种模式，有时用于通过软件仿真协处理器硬件的工作方式        |

| 系统模式 (System)     | sys | 使用和 User 模式相同寄存器集的模式，用于运行特权级操作系统任务           |

| 监控模式 (Monitor)    | mon | 可以在安全模式与非安全模式之间进行转换                          |

除用户模式外的其他 7 种处理器模式称为特权模式 (Privileged Modes)。在特权模式下，程序可以访问所有的系统资源，也可以任意地进行处理器模式切换。其中以下 6 种又称为异常模式：

- (1) 快速中断模式 (FIQ)。

- (2) 外部中断模式 (IRQ)。

- (3) 特权模式 (Supervisor)。

- (4) 数据访问中止模式 (Abort)。

- (5) 未定义指令中止模式 (Undef)。

- (6) 监控模式 (Monitor)。

处理器模式可以通过软件控制进行切换，也可以通过外部中断或异常处理过程进行切换。

大多数的用户程序运行在用户模式下。当处理器工作在用户模式时，应用程序不能够访问受操作系统保护的一些系统资源，应用程序也不能直接进行处理器模式切换。当需要进行处理器模式切换时，应用程序可以产生异常处理，在异常处理过程中进行处理器模式切换。这种体系结构可以使操作系统控制整个系统资源的使用。

当应用程序发生异常中断时，处理器进入相应的异常模式。在每一种异常模式中都有一组专用寄存器以供相应的异常处理程序使用，这样就可以保证在进入异常模式时用户模式下的寄存器（保存程序运行状态）不被破坏。

## 2.8 Cortex-A8 存储系统

ARM存储系统有非常灵活的体系结构,可以适应不同的嵌入式应用系统的需要。ARM存储器系统可以使用简单的平板式地址映射机制(就像一些简单的单片机一样,地址空间的分配方式是固定的,系统中各部分都使用物理地址),也可以使用其他技术提供功能更为强大的存储系统。例如:

- (1) 系统可能提供多种类型的存储器件,如Flash、ROM、SRAM等。

- (2) Cache技术。

- (3) 写缓存技术(Write Buffers)。

- (4) 虚拟内存和I/O地址映射技术。

大多数的系统通过下面的方法之一可实现对复杂存储系统的管理。

- (1) 使用Cache,缩小处理器和存储系统速度差别,从而提高系统的整体性能。

- (2) 使用内存映射技术实现虚拟空间到物理空间的映射。这种映射机制对嵌入式系统非常重要。通常嵌入式系统程序存放在ROM/Flash中,这样系统断电后程序能够得到保存。但是,通常ROM/Flash与SDRAM相比,速度慢很多,而且基于ARM的嵌入式系统中通常把异常中断向量表放在RAM中。利用内存映射机制可以满足这种需要。在系统加电时,将ROM/Flash映射为地址0,这样可以进行一些初始化处理;当这些初始化处理完成后将SDRAM映射为地址0,并把系统程序加载到SDRAM中运行,这样可很好地满足嵌入式系统的需求。

- (3) 引入存储保护机制,增强系统的安全性。

- (4) 引入一些机制保证将I/O操作映射成内存操作后,各种I/O操作能够得到正确的结果。在简单存储系统中,不存在这样的问题。而当系统引入了Cache和write buffer后,就需要一些特别的措施。

在ARM系统中,要实现对存储系统的管理通常使用协处理器CP15,它通常也被称为系统控制协处理器(System Control Coprocessor)。

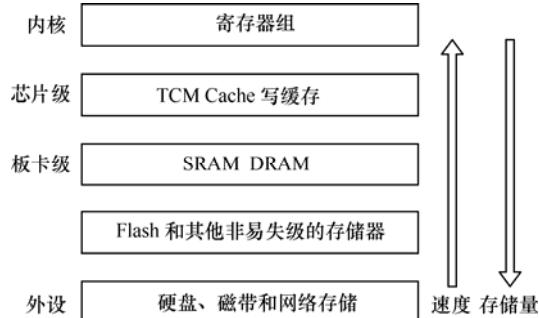

ARM的存储器系统是由多级构成的,可以分为内核级、芯片级、板卡级、外设级。如图2-3所示为存储器的层次结构。

图2-3 存储器的层次结构

每级都有特定的存储介质，下面对比各级系统中特定存储介质的存储性能。

(1) 内核级的寄存器。处理器寄存器组可看做是存储器层次的顶层。这些寄存器被集成在处理器内核中，在系统中提供最快的存储器访问。典型的 ARM 处理器有多个 32 位寄存器，其访问时间为 ns 量级。

(2) 芯片级的紧耦合存储器 (TCM) 是为弥补 Cache 访问的不确定性增加的存储器。TCM 是一种快速 SDRAM，它紧挨内核，并且保证取指和数据操作的时钟周期数，这一点对一些要求确定行为的实时算法是很重要的。TCM 位于存储器地址映射中，可作为快速存储器来访问。

(3) 芯片级的片上 Cache 存储器的容量在 8KB~32KB 之间，访问时间大约为 10ns。高性能的 ARM 结构中，可能存在第二级片外 Cache，容量为几百 KB，访问时间为几十 ns。

(4) 板卡级的 DRAM。主存储器可能是几 MB 到几十 MB 的动态存储器，访问时间大约为 100ns。

(5) 外设级的后援存储器，通常是硬盘，可能从几百 MB 到几个 GB，访问时间为几十 ms。

### 2.8.1 协处理器 (CP15)

ARM 处理器支持 16 个协处理器。在程序执行过程中，每个协处理器忽略属于 ARM 处理器和其他协处理器的指令。当一个协处理器硬件不能执行属于它的协处理器指令时，将产生一个未定义指令异常中断，在该异常中断处理程序中，可以通过软件模拟该硬件操作。例如，如果系统不包含向量浮点运算器，则可以选择浮点运算软件模拟包来支持向量浮点运算。CP15 即通常所说的系统控制协处理器 (System Control Coprocessor)，它负责完成大部分的存储系统管理。除了 CP15 外，在具体的各种存储管理机制中可能还会用到其他一些技术，如在 MMU 中除了 CP15 外，还使用了页表技术等。

在一些没有标准存储管理的系统中，CP15 是不存在的。在这种情况下，针对 CP15 的操作指令将被视为未定义指令，指令的执行结果不可预知。

CP15 包含 16 个 32 位寄存器，其编号为 0~15。实际上对于某些编号的寄存器可能对应多个物理寄存器，在指令中指定特定的标志位来区分这些物理寄存器。这种机制有些类似于 ARM 中的寄存器，当处于不同的处理器模式时，某些相同编号的寄存器对应于不同的物理寄存器。

CP15 中的寄存器可能是只读的，也可能是只写的，还有一些是可读/可写的。在对协处理器寄存器进行操作时，需要注意以下几个问题：

- (1) 寄存器的访问类型 (只读/只写/可读可写)。

- (2) 不同的访问引发不同的功能。

- (3) 相同编号的寄存器是否对应不同的物理寄存器。

- (4) 寄存器的具体作用。

### 2.8.2 存储管理单元（MMU）

在创建多任务嵌入式系统时，最好用一个简单的方式来编写、装载及运行各自独立的任务。目前大多数的嵌入式系统不再使用自己定制的控制系统，而使用操作系统来简化这个过程。较高级的操作系统采用基于硬件的存储管理单元（MMU）来实现上述操作。

MMU 提供的一个关键服务是使各个任务作为各自独立的程序在自己的私有存储空间中运行。在带 MMU 的操作系统控制下，运行的任务无须知道其他与之无关的任务的存储需求情况，这就简化了各个任务的设计。

MMU 提供了一些资源以允许使用虚拟存储器（将系统物理存储器重新编址，可将其看成一个独立于系统物理存储器的存储空间）。MMU 作为转换器，将程序和数据的虚拟地址（编译时的连接地址）转换成实际的物理地址，即在物理主存中的地址。这个转换过程允许运行的多个程序使用相同的虚拟地址，而各自存储在物理存储器的不同位置。

这样存储器就有两种类型的地址：虚拟地址和物理地址。虚拟地址由编译器和连接器在定位程序时分配；物理地址用来访问实际的主存硬件模块（物理上程序存在的区域）。

### 2.8.3 高速缓冲存储器（Cache）

Cache 是一个容量小但存取速度非常快的存储器，它保存最近用到的存储器数据副本。对于程序员来说，Cache 是透明的。它自动决定保存哪些数据、覆盖哪些数据。现在 Cache 通常与处理器在同一芯片上实现。Cache 能够发挥作用是因为程序具有局部性。所谓局部性就是指在任何特定的时间，处理器趋于对相同区域的数据（如堆栈）多次执行相同的指令（如循环）。

Cache 经常与写缓存器（write buffer）一起使用。写缓存器是一个非常小的先进先出（FIFO）存储器，位于处理器核与主存之间。使用写缓存的目的是，将处理器核和 Cache 从较慢的主存写操作中解脱出来。当 CPU 向主存储器做写入操作时，它先将数据写入到写缓存区中，由于写缓存器的速度很高，这种写入操作的速度也将很高。写缓存区在 CPU 空闲时，以较低的速度将数据写入到主存储器中相应的位置。

通过引入 Cache 和写缓存区，存储系统的性能得到了很大的提高，但同时也带来了一些问题。例如，由于数据将存在于系统中不同的物理位置，可能造成数据的不一致性；由于写缓存区的优化作用，可能有些写操作的执行顺序不是用户期望的顺序，从而造成操作错误。

## 2.9 流水线

### 2.9.1 流水线的概念与原理

处理器按照一系列步骤来执行每一条指令，典型的步骤如下：

- (1) 从存储器读取指令 (fetch)。

- (2) 译码以鉴别它属于哪一条指令 (decode)。

- (3) 从指令中提取指令的操作数 (这些操作数往往存在于寄存器 reg 中)。

- (4) 将操作数进行组合以得到结果或存储器地址 (ALU)。

- (5) 如果需要，则访问存储器以存储数据 (mem)。

- (6) 将结果写回到寄存器堆 (res)。

并不是所有的指令都需要上述每一个步骤，但是，多数指令需要其中的多个步骤。这些步骤往往使用不同的硬件功能，如 ALU 可能只在第 4 步中用到。因此，如果一条指令不是在前一条指令结束之前就开始，那么在每一步骤内处理器只有少部分的硬件在使用。

有一种方法可以明显改善硬件资源的使用率和处理器的吞吐量，这就是在当前一条指令结束之前就开始执行下一条指令，即通常所说的流水线 (Pipeline) 技术。流水线是 RISC 处理器执行指令时采用的机制。使用流水线，可在取下一条指令的同时译码和执行其他指令，从而加快执行的速度。可以把流水线看做是汽车生产线，每个阶段只完成专门的处理器任务。

采用上述操作顺序，处理器可以这样来组织：当一条指令刚刚执行完步骤 (1) 并转向步骤 (2) 时，下一条指令就开始执行步骤 (1)。从原理上说，这样的流水线应该比没有重叠的指令执行快 6 倍，但由于硬件结构本身的一些限制，实际情况会比理想状态差一些。

### 2.9.2 流水线的分类

#### 1. 3 级流水线 ARM 组织

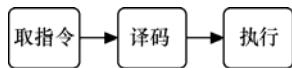

到 ARM7 为止的 ARM 处理器使用简单的 3 级流水线，它包括下列流水线级。

- (1) 取指令 (fetch)：从寄存器装载一条指令。

- (2) 译码 (decode)：识别被执行的指令，并为下一个周期准备数据通路的控制信号。在这一级，指令占有译码逻辑，不占用数据通路。

- (3) 执行 (execute)：处理指令并将结果写回寄存器。

如图 2-4 所示为 3 级流水线指令的执行过程。

图 2-4 3 级流水线

当处理器执行简单的数据处理指令时，流水线使得平均每个时钟周期能完成 1 条指令。但 1 条指令需要 3 个时钟周期来完成，因此，有 3 个时钟周期的延时 (latency)，但吞吐率 (throughput) 是每个周期 1 条指令。

## 2. 5 级流水线 ARM 组织

所有的处理器都要满足对高性能的要求，直到 ARM7 为止，在 ARM 核中使用的 3 级流水线的性价比是很高的。但是，为了得到更高的性能，需要重新考虑处理器的组织结构。有两种方法来提高性能。

(1) 提高时钟频率。时钟频率的提高，必然引起指令执行周期的缩短，所以要求简化流水线每一级的逻辑，流水线的级数就要增加。

(2) 减少每条指令的平均指令周期数 CPI。这就要求重新考虑 3 级流水线 ARM 中多于 1 个流水线周期的实现方法，以便使其占有较少的周期，或者减少因指令相关造成的流水线停顿，也可以将两者结合起来。

3 级流水线 ARM 核在每一个时钟周期都访问存储器，或者取指令，或者传输数据。只是抓紧存储器不用的几个周期来改善系统性能，效果并不明显。为了改善 CPI，存储器系统必须在每个时钟周期中给出多于一个的数据。方法是在每个时钟周期从单个存储器中给出多于 32 位数据，或者为指令或数据分别设置存储器。

基于以上原因，较高性能的 ARM 核使用了 5 级流水线，而且具有分开的指令和数据存储器。把指令的执行分割为 5 部分而不是 3 部分，进而可以使用更高的时钟频率，分开的指令和数据存储器使核的 CPI 明显减少。

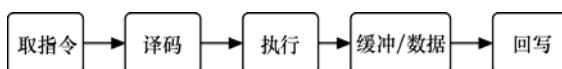

在 ARM9TDMI 中使用了典型的 5 级流水线，5 级流水线包括下面的流水线级。

(1) 取指令 (fetch): 从存储器中取出指令，并将其放入指令流水线。

(2) 译码 (decode): 指令被译码，从寄存器堆中读取寄存器操作数。在寄存器堆中有 3 个操作数读端口，因此，大多数 ARM 指令能在 1 个周期内读取其操作数。

(3) 执行 (execute): 将其中 1 个操作数移位，并在 ALU 中产生结果。如果指令是 Load 或 Store 指令，则在 ALU 中计算存储器的地址。

(4) 缓冲/数据 (buffer/data): 如果需要则访问数据存储器，否则 ALU 只是简单地缓冲 1 个时钟周期。

(5) 回写 (write-back): 将指令的结果回写到寄存器堆，包括任何从寄存器读出的数据。

如图 2-5 所示列出了 5 级流水线指令的执行过程。

图 2-5 5 级流水线

在程序执行过程中，PC 值是基于 3 级流水线操作特性的。5 级流水线中提前 1 级来读取指令操作数，得到的值是不同的 (PC + 4 而不是 PC + 8)。这里产生代码不兼容是不容许的。但 5 级流水线 ARM 完全仿真 3 级流水线的行为。在取指级增加的 PC 值被直接送到译码级的寄存器，穿过两级之间的流水线寄存器。下一条指令的 PC + 4 等于当前指令的 PC + 8，因此，未使用额外的硬件便得到了正确的 R15。

### 3. 13 级流水线

在 Cortex-A8 中有一条 13 级的流水线，但是由于 ARM 公司没有对其中的技术公开任何相关的细节，这里只能简单介绍一下，从经典 ARM 系列到现在的 Cortex 系列，ARM 处理器的结构在向复杂的阶段发展，但没改变的是 CPU 的取指指令和地址关系，不管是几级流水线，都可以按照最初的 3 级流水线的操作特性来判断其当前的 PC 位置。这样做主要还是为了软件兼容性上的考虑，由此可以判断的是，后面 ARM 所推出的处理核心都想满足这一特点，感兴趣的读者可以自行查阅相关资料。

#### 2.9.3 影响流水线性能的因素

##### 1. 互锁

在典型的程序处理过程中，经常会遇到这样的情形，即一条指令的结果被用做下一条指令的操作数。例如，有如下指令序列：

```

LDR R0,[R0,#0]

ADD R0,R0,R1 ; 在 5 级流水线上产生互锁

```

从例子可以看出，流水线的操作产生中断，因为第 1 条指令的结果在第 2 条指令取数时还没有产生。第 2 条指令必须停止，直到结果产生为止。

##### 2. 跳转指令

跳转指令也会破坏流水线的行为，因为后续指令的取指步骤受到跳转目标计算的影响，因而必须推迟。但是，当跳转指令被译码时，在它被确认是跳转指令之前，后续的取指操作已经发生。这样一来，已经被预取进入流水线的指令不得不被丢弃。如果跳转目标的计算是在 ALU 阶段完成的，那么在得到跳转目标之前已经有两条指令按原有指令流读取。

显然，只有当所有指令都依照相似的步骤执行时，流水线的效率达到最高。如果处理器的指令非常复杂，每一条指令的行为都与下一条指令不同，那么就很难用流水线实现。

## 2.10 寄存器组织

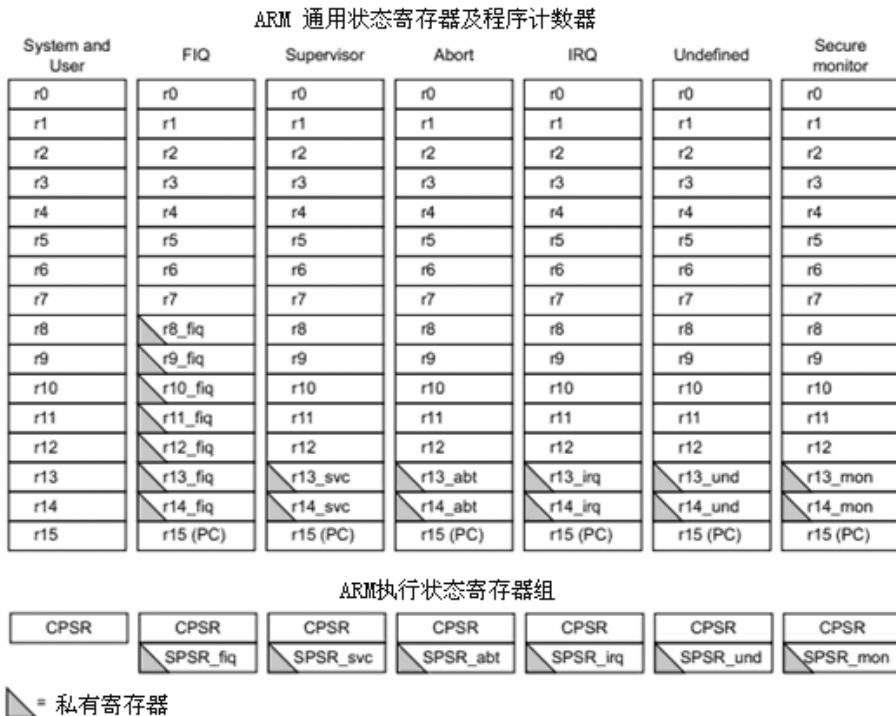

ARM 处理器有如下 40 个 32 位长的寄存器。

- (1) 33 个通用寄存器。

- (2) 6 个状态寄存器：1 个 CPSR (Current Program Status Register，当前程序状态寄存器)，6 个 SPSR (Saved Program Status Register，备份程序状态寄存器)。

- (3) 1 个 PC (Program Counter，程序计数器)。

ARM 处理器共有 7 种不同的处理器模式，在每一种处理器模式中都有一组相应的寄存器组，如图 2-6 所示列出了 ARM 处理器的寄存器组织概要。

图 2-6 寄存器列表

当前处理器的模式决定着哪组寄存器可操作，任何模式都可以存取下列寄存器。

- (1) 相应的 R0~R12。

- (2) 相应的 R13 (Stack Pointer, SP, 栈指向) 和 R14 (the Link Register, LR, 链路寄存器)。

- (3) 相应的 R15 (PC)。

- (4) 相应的 CPSR。

特权模式（除 System 模式外）还可以存取相应的 SPSR。

通用寄存器根据其分组与否可分为以下两类。

- (1) 未分组寄存器 (Unbanked Register)，包括 R0~R7。

- (2) 分组寄存器 (Banked Register)，包括 R8~R14。

### 1. 未分组寄存器

未分组寄存器包括 R0~R7。顾名思义，在所有处理器模式下对于每一个未分组寄存器来说，指的都是同一个物理寄存器。未分组寄存器没有被系统用于特殊的用途，任何可采用通用寄存器的应用场合都可以使用未分组寄存器。但由于其通用性，在异常中断所引起的处理器模式切换时，其使用的是相同的物理寄存器，所以也就很容易使寄存器中的数据被破坏。

## 2. 分组寄存器

R8~R14 是分组寄存器，它们每一个访问的物理寄存器取决于当前的处理器模式。

对于分组寄存器 R8~R12 来说，每个寄存器对应两个不同的物理寄存器。一组用于除 FIQ 模式外的所有处理器模式，而另一组则专门用于 FIQ 模式。这样的结构设计有利于加快 FIQ 的处理速度。不同模式下寄存器的使用，要使用寄存器名后缀加以区分。例如，当使用 FIQ 模式下的寄存器时，寄存器 R8 和寄存器 R9 分别记为 R8\_fiq、R9\_fiq；当使用用户模式下的寄存器时，寄存器 R8 和 R9 分别记为 R8\_usr、R9\_usr 等。在 ARM 体系结构中，R8~R12 没有任何指定的其他的用途，所以当 FIQ 中断到达时，不用保存这些通用寄存器，也就是说，FIQ 处理程序可以不必执行保存和恢复中断现场的指令，从而使中断处理过程非常迅速。所以 FIQ 模式常被用来处理一些时间紧急的任务，如 DMA 处理。

对于分组寄存器 R13 和 R14 来说，每个寄存器对应 6 个不同的物理寄存器。其中的一个是用户模式和系统模式公用的，而另外 5 个分别用于 5 种异常模式。访问时需要指定它们的模式。名字形式如下：

- (1) R13\_<mode>

- (2) R14\_<mode>

其中，<mode>可以是以下几种模式之一：usr、svc、abt、und、irp、fiq 及 mon。

R13 寄存器在 ARM 处理器中常用做堆栈指针，称为 SP。当然，这只是一个习惯用法，并没有任何指令强制性的使用 R13 作为堆栈指针，用户完全可以使用其他寄存器作为堆栈指针。而在 Thumb 指令集中，有一些指令强制性地将 R13 作为堆栈指针，如堆栈操作指令。

每一种异常模式拥有自己的 R13。异常处理程序负责初始化自己的 R13，使其指向该异常模式专用的栈地址。在异常处理程序入口处，将用到的其他寄存器的值保存在堆栈中，返回时，重新将这些值加载到寄存器。通过这种保护程序现场的方法，异常不会破坏被其中断的程序现场。

寄存器 R14 又被称为连接寄存器（Link Register，LR），在 ARM 体系结构中具有下面两种特殊的作用。

(1) 每一种处理器模式用自己的 R14 存放当前子程序的返回地址。当通过 BL 或 BLX 指令调用子程序时，R14 被设置成该子程序的返回地址。在子程序返回时，把 R14 的值复制到程序计数器（PC）。典型的做法是使用下列两种方法之一。

- ① 执行下面任何一条指令。

```

MOV PC, LR

BX LR

```

- ② 在子程序入口处使用下面的指令将 PC 保存到堆栈中。

```

STMFD SP!, {<register>,LR}

```

在子程序返回时，使用如下相应的配套指令返回。

```

LDMFD SP!, {<register>,PC}

```

(2) 当异常中断发生时, 该异常模式特定的物理寄存器 R14 被设置成该异常模式的返回地址, 对于有些模式 R14 的值可能与返回地址有一个常数的偏移量 (如数据异常使用 SUB PC, LR, #8 返回)。具体的返回方式与上面的子程序返回方式基本相同, 但使用的指令稍微有些不同, 以保证当异常出现时正在执行的程序的状态被完整保存。

R14 也可以被用做通用寄存器使用。

## 2.11 程序状态寄存器

当前程序状态寄存器 (Current Program Status Register, CPSR) 可以在任何处理器模式下被访问, 它包含下列内容:

- (1) ALU (Arithmetic Logic Unit, 算术逻辑单元) 状态标志的备份。

- (2) 当前的处理器模式。

- (3) 中断使能标志。

- (4) 设置处理器的状态。

每一种处理器模式下都有一个专用的物理寄存器做备份程序状态寄存器 (Saved Program Status Register, SPSR)。当特定的异常中断发生时, 这个物理寄存器负责存放当前程序状态寄存器的内容。当异常处理程序返回时, 再将其内容恢复到当前程序状态寄存器。

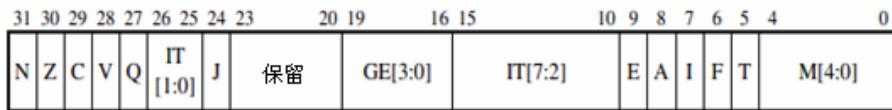

CPSR 寄存器 (和保存它的 SPSR 寄存器) 中的位分配如图 2-7 所示。

图 2-7 程序状态寄存器格式

下面给出各个状态位的定义。

### 1. 标志位

N (Negative)、Z (Zero)、C (Carry) 和 V (oVerflow) 通称为条件标志位。这些条件标志位会根据程序中的算术指令或逻辑指令的执行结果进行修改, 而且这些条件标志位可由大多数指令检测以决定指令是否执行。

在 ARM 4T 架构中, 所有的 ARM 指令都可以条件执行, 而 Thumb 指令却不能。

各条件标志位的具体含义如下。

#### 1) N

本位设置成当前指令运行结果的 bit[31]的值。当两个由补码表示的有符号整数运算时,  $N = 1$  表示运算的结果为负数,  $N = 0$  表示结果为正数或零。

## 2) Z

$Z = 1$  表示运算的结果为零,  $Z = 0$  表示运算的结果不为零。

## 3) C

下面分 4 种情况讨论 C 的设置方法。

(1) 在加法指令中 (包括比较指令 CMN), 当结果产生了进位, 则  $C = 1$ , 表示无符号数运算发生上溢出; 其他情况下  $C = 0$ 。

(2) 在减法指令中 (包括比较指令 CMP), 当运算中发生错位 (即无符号数运算发生下溢出), 则  $C = 0$ ; 其他情况下  $C = 1$ 。

(3) 对于在操作数中包含移位操作的运算指令 (非加/减法指令), C 被设置成被移位寄存器最后移出去的位。

(4) 对于其他非加/减法运算指令, C 的值通常不受影响。

## 4) V

下面分两种情况讨论 V 的设置方法。

(1) 对于加/减运算指令, 当操作数和运算结果都是以二进制的补码表示的带符号的数时, 且运算结果超出了有符号运算的范围是溢出。 $V = 1$  表示符号位溢出。

(2) 对于非加/减法指令, 通常不改变标志位 V 的值 (具体可参照 ARM 指令手册)。

尽管以上 C 和 V 的定义看起来颇为复杂, 但使用时在大多数情况下用一个简单的条件测试指令即可, 不需要程序员计算出条件码的精确值即可得到需要的结果。

## 2. Q 标志位

在带 DSP 指令扩展的 ARM v5 及更高版本中, bit[27] 被指定用于指示增强的 DAP 指令是否发生了溢出, 因此也就被称为 Q 标志位。同样, 在 SPSR 中 bit[27] 也被称为 Q 标志位, 用于在异常中断发生时保存和恢复 CPSR 中的 Q 标志位。

在 ARM v5 以前的版本及 ARM v5 的非 E 系列处理器中, Q 标志位没有被定义, 属于待扩展的位。

## 3. 控制位

CPSR 的低 8 位 (I、F、T 及 M[4:0]) 统称为控制位。当异常发生时, 这些位的值将发生相应的变化。另外, 如果在特权模式下, 也可以通过软件编程来修改这些位的值。

### 1) 中断禁止位

$I = 1$ , IRQ 被禁止。

$F = 1$ , FIQ 被禁止。

### 2) 状态控制位

T 位是处理器的状态控制位。

$T = 0$ , 处理器处于 ARM 状态 (即正在执行 32 位的 ARM 指令)。

$T = 1$ , 处理器处于 Thumb 状态 (即正在执行 16 位的 Thumb 指令)。

当然, T 位只有在 T 系列的 ARM 处理器上才有效, 在非 T 系列的 ARM 版本中, T 位将始终为 0。

### 3) 模式控制位

M[4:0]作为位模式控制位，这些位的组合确定了处理器处于哪种状态。如表 2-6 所示列出了其具体含义。

只有表中列出的组合是有效的，其他组合无效。

表 2-6 状态控制位 M[4:0]

| M[4 : 0] | 处理器模式          | 可以访问的寄存器                                    |

|----------|----------------|---------------------------------------------|

| 0b10000  | User           | PC, R14~R0, CPSR                            |

| 0b10001  | FIQ            | PC, R14_fiq~R8_fiq, R7~R0, CPSR, SPSR_fiq   |

| 0b10010  | IRQ            | PC, R14_irq~R13_irq, R12~R0, CPSR, SPSR_irq |

| 0b10011  | Supervisor     | PC, R14_svc~R13_svc, R12~R0, CPSR, SPSR_svc |

| 0b10111  | Abort          | PC, R14_abt~R13_abt, R12~R0, CPSR, SPSR_abt |

| 0b11011  | Undefined      | PC, R14_und~R13_und, R12~R0, CPSR, SPSR_und |

| 0b11111  | System         | PC, R14~R0, CPSR (ARM v4 及更高版本)             |

| 0b10110  | Secure monitor | PC,R0-R12, CPSR,SPSR_mon,r13_mon,r14_mon    |

### 4. IF-THEN 标志位

CPSR 中的 bits[15:10,26:25]称为 if-then 标志位，它用于对 thumb 指令集中 if-then-else 这一类语句块的控制。

其中 IT[7:5]定义为基本条件，如图 2-8 所示。

IT[4:0]被定义为 IF-THEN 语句块的长度。

| [7:5] | [4] | [3] | [2] | [1] | [0] |                  |

|-------|-----|-----|-----|-----|-----|------------------|

| 控制基础  | P1  | P2  | P3  | P4  | 1   | 4 指令 IT 块入口点     |

| 控制基础  | P1  | P2  | P3  | 1   | 0   | 3 指令 IT 块入口点     |

| 控制基础  | P1  | P2  | 1   | 0   | 0   | 2 指令 IT 块入口点     |

| 控制基础  | P1  | 1   | 0   | 0   | 0   | 1 指令 IT 块入口点     |

| 000   | 0   | 0   | 0   | 0   | 0   | 普通执行状态，无 IT 块入口点 |

图 2-8 IF-THEN 标志位[7:5]的定义

### 5. E 位/A 位/GE[19-16]位的定义

A 表示异步异常禁止位。

E 表示大小端控制位，0 表示小端操作，1 表示大端操作。注意，该位在预取阶段是被忽略的。

GE[19-16]用于表示在 SIMD 指令集中的大于、等于标志。在任何模式下该位可读可写。

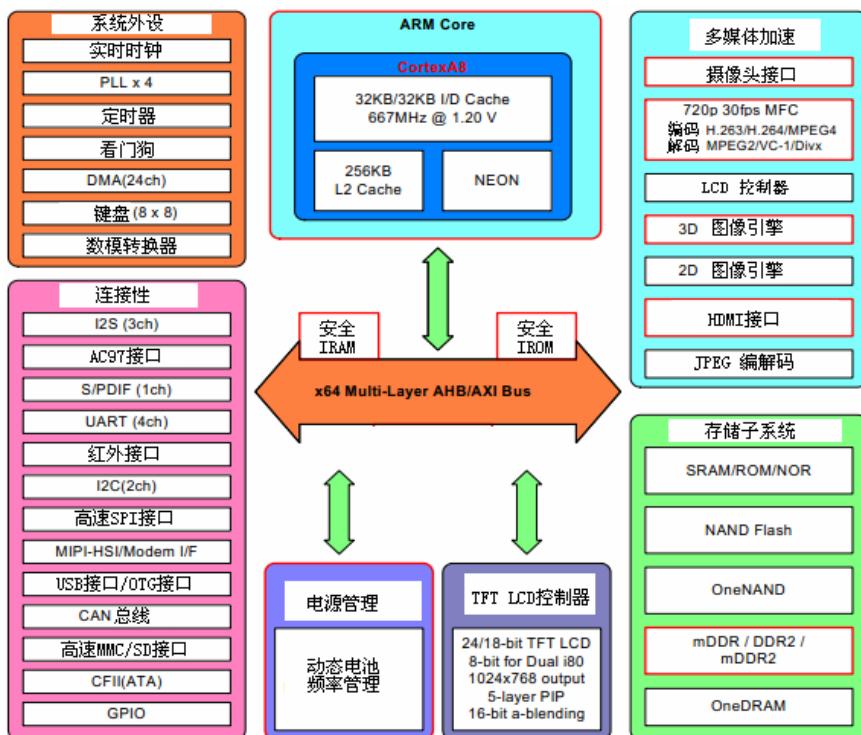

## 2.12 三星 S5PC100 处理器介绍

S5PC100 是著名的半导体公司 SAMSUNG 推出的一款 32 位 RISC 处理器，它为手持设备和一般类型的应用提供了低价格、低功耗、高性能微控制器的解决方案。S5PC100 的内核基于 Cortex-A8，带有 MMU（Memory Management Unit）功能，采用  $0.18\mu\text{m}$  工艺，其主频可达 203MHz，适合于对成本和功耗敏感的需求。同时它还采用了 AMBA（Advanced Microcontroller Bus Architecture）的新型总线结构，实现了 MMU、AMBA BUS、Harvard 的高速缓冲体系结构，同时支持 Thumb16 位压缩指令集，从而能以较小的存储空间需求，获得 32 位的系统性能。

S5PC100 是一款低功耗、低成本、高性能的移动领域及普通应用的微处理解决方案，集成的 Cortex-A8 使用 v7 架构，以及支持众多的外设。

S5PC100 还采取了 64 位的内部总线架构，并包括许多性能强大的加速硬件，例如针对于图形图像加速、显示、伸缩裁剪、集成的多媒体格式编码（MFC），硬件加速还支持实时会议、模拟电视输出、高清视频、PAL 等。

S5PC100 还支持一个可扩展高端内存的接口，其中 DRAM 接口可配置支持 DDR、DDR2、LPDDR2。

其片上功能如下：

- 先进的电源管理系统。

- 用于安全启动的片内 ROM/片内 RAM。

- 8 位 ITU 601/656 摄像头接口，最大支持 8M 像素裁剪图像，以及 64M 像素的未裁剪图像。

- 多格式编解码单元支持 MPEG-4/H.263/H.264 的编解码，可支持 720p/30 帧每秒。以及对 MPEG2/VC1/DIVx video 的解码，最大支持 720p/30 帧每秒。

- 支持 3D/2D 多媒体加速技术。

- 支持模拟电视信号输出及高清晰度多媒体接口。

- AC97 音频编解码接口，PCM 串行音频接口。

- 3 通道的 24 位 IIS 接口。

- 一个 2 通道的 IIC 总线控制器。

- 一个 3 通道的 SPI 总线控制器。

- 4 通道 UART 接口，包括一个 4M 波特率的蓝牙 2.0 接口。

- 一个红外传感器端口。

- 一个 USB 2.0 OTG 控制器。

- 一个 USB 1.1 HOST。

- SD/MMC 高速数字信号卡接口。

- 24 通道的 DMA 控制器。

- 8×8 矩阵键盘。

- 10通道的12位混合ADC接口。

- 可配置的GPIO资源。

- 实时时钟/PLL/看门狗等片上外设。

S5PC100处理器支持大/小端模式存储字数据，其寻址空间可达4GB，对于外部I/O设备的数据宽度，可以是8/16/32位，所有的存储器Bank（共有15个）都具有可编程的操作周期，而且支持各种ROM引导方式（NOR/Nand Flash、EEPROM/SD/USB/ONENAND等），其结构框图如图2-9所示。

图2-9 S5PC100结构框图

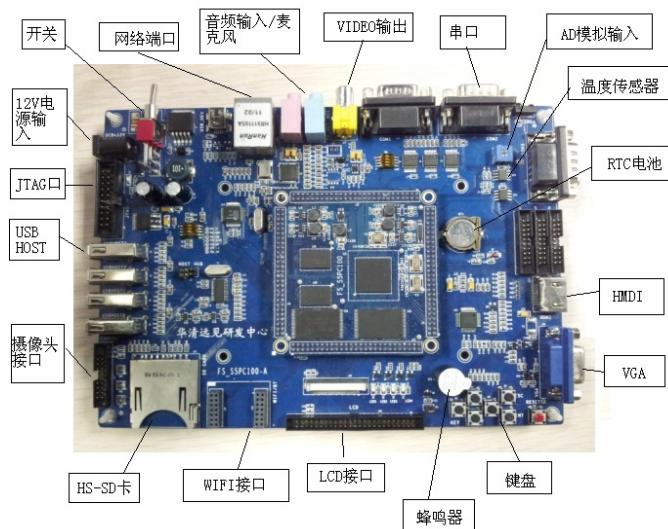

## 2.13 FS\_S5PC100 开发平台介绍

FS\_S5PC100是由华清远见研发部自主研发的一款基于Cortex-A8核心的嵌入式系统学习开发平台，以适应Android、Linux、Wince等智能操作系统的发展及市场需求。华清远见研发中心及教师团队将不断完善推广平台资料，帮助大家快速掌握高端嵌入式技术。

FS\_S5PC100核心实验板如图2-10所示。

图 2-10 FS\_S5PC100 核心实验板

(1) FS\_S5PC100 拥有如下丰富的硬件资源。

- 存储器: 256MB 的 NAND Flash, 256MB 的 DDR2 内存, 2MB 的 NOR Flash。

- 显示输出接口: LCD 接口、VGA 接口、TVout 接口、HDMI 接口。

- 视频输入接口: Camera 接口。

- 串口: 2 路 5 线串口、1 路 3 线串口。

- 红外通信接口: 1 路红外收发。

- 存储卡接口: SD 卡接口。

- SPI: SPI 的 E2PROM (用于 SPI 实验)。

- I2C: I2C 的温度传感器 (用于 I2C 实验)。

- A/D: 变阻器 (用于 A/D 实验)。

- USB: USB2.0-OTG 接口、4 路 USB Host 接口。

- PWM: 蜂鸣器 (用于 PWM 实验)。

- 网络接口: DM9000AE 以太网控制器, 实现 10M/100M 自适应以太网通信。

- 外扩接口: 蓝牙、WiFi 等。

- 音频接口: WM9714。

(2) FS\_S5PC100 软件资源。其中包括下列资源信息。

① 裸机代码资源。

GPIO 测试代码, I2C 总线测试温度传感器, SPI 总线对 EEPROM 的读/写, ADC 模拟数字转换例子, 红外传感器收发实例, LCD 裸机驱动, 摄像头裸机驱动, NAND/NOR FLASH 的读/写驱动, 触摸屏裸机驱动, DMA 控制器例子 (内存至内存, 串口至内存), RTC 实时时钟驱动, 蜂鸣器驱动。

丰富的裸机代码，可以让初学者迅速掌握基于 Cortex-A8 的 FS\_S5PC100 开发平台的各项功能，在裸机驱动的帮助下，读者对寄存器操作的认识和各个接口的操作特性有深刻体会。

② 系统移植资源

uboot-1.1.6 源码及 uboot-2011.09 源码，在两种不同版本的 uboot 对比下，可以让读者迅速掌握新旧 uboot 的结构差异，注意，新旧版本 uboot 变化很大。

Android 源码，当前最流行的手机操作系统之一，Google 的 Android 操作系统，读者使用该源代码，可以对 Android 系统架构、开发及移植有很深刻的理解，对有望从事该职业的读者有很大的帮助。

Linux 2.6.29 源代码及 Linux 2.6.35 源代码，同样已经移植到 FS\_S5PC100 开发平台的 Linux 内核，其中包含了基于 Linux 架构的驱动模块，让读者从裸机驱动层次过渡到 Linux 驱动架构的层次。其中，Linux 2.6.29 是 Android 的配套 Linux 内核，而 Linux 2.6.35 为原始版的内核。

③ Linux 内核驱动资源。

包括 ADC 驱动、IO 控制蜂鸣器驱动、PWM 控制蜂鸣器驱动、内核 irq 测试、LED 驱动、平台设备驱动、EEPROM 读/写驱动、温度传感器测试驱动等。

④ 综合案例资源。

基于该平台，华清远见研发中心研发了多项典型教学案例，涵盖嵌入式系统开发课程及物联网开发课程，其中有：

《智能感应家居》，该案例的前端使用了 Android 操作系统，并通过多级 ZigBee 节点实现了一个覆盖家居的网络，在该 zigbee 网络中，通过主控端控制各个节点端，从而实现家居控制。

《仓储物联网系统》，该案例实现了从一个 Web 端来对一个由 ZigBee 节点组成的监控网络的操控，其中 FS\_S5PC100 作为一级网关，FS11C14 作为数据采集节点，在 zigbee 的网络传输下，将数据汇集到一级网关，最终上报给 Web 服务端。

《3G 机器人》通过 Android 平台和 3G 网络远程控制机器人的行为。

综合案例的学习，不仅巩固了对所用的软件与硬件的知识，并且积累了一定的开发经验，更是让学员自己去尝试项目的开发流程，以及系统架构、编程、调试等步骤。

(3) 本书所有源代码均在 FS\_S5PC100 开发平台上测试通过。

## 2.14 本章小结

本章介绍了 ARM 处理器的一些关键技术，如 ARM 核的工作模式、存储系统、流水线、寄存器组织等。并且列举了一款基于 Cortex-A8 核的处理器芯片 A5PC100。通过本章的学习，学员可以对 ARM 核的一些关键技术有所认识。

## 2.15 练习题

---

1. 简述 ARM 可以工作的几种模式。

2. ARM 核有多少个寄存器？

3. 什么寄存器用于存储 PC 和 LR 寄存器？

4. R13 通常用来存储什么？

5. 哪种模式使用的寄存器最少？

6. CPSR 的哪一位反映了处理器的状态？

# 第3章 ARM微处理器的指令系统

ARM指令集可以分为跳转指令、数据处理指令、程序状态寄存器传输指令、Load/Store指令、协处理器指令和异常中断产生指令。根据使用的指令类型不同，指令的寻址方式分为数据处理指令寻址方式和内存访问指令寻址方式。

本章主要介绍ARM汇编语言。主要内容如下：

- ARM处理器的寻址方式。

- ARM处理器的指令集。

## 3.1 ARM处理器的寻址方式

ARM指令的寻址方式分为数据处理指令寻址方式和内存访问指令寻址方式。

### 3.1.1 数据处理指令寻址方式

数据处理指令的基本语法格式如下：

```

<opcode> {<cond>} {S} <Rd>, <Rn>, <shifter_operand>

```

其中，**<shifter\_operand>**有11种形式，如表3-1所示。

表3-1 **<shifter\_operand>**的寻址方式

|    | 语 法                    | 寻 址 方 式   |

|----|------------------------|-----------|

| 1  | #<immediate>           | 立即数寻址     |

| 2  | <Rm>                   | 寄存器寻址     |

| 3  | <Rm>, LSL #<shift_imm> | 立即数逻辑左移   |

| 4  | <Rm>, LSL <Rs>         | 寄存器逻辑左移   |

| 5  | <Rm>, LSR #<shift_imm> | 立即数逻辑右移   |

| 6  | <Rm>, LSR <Rs>         | 寄存器逻辑右移   |

| 7  | <Rm>, ASR #<shift_imm> | 立即数算术右移   |

| 8  | <Rm>, ASR <Rs>         | 寄存器算术右移   |

| 9  | <Rm>, ROR #<shift_imm> | 立即数循环右移   |

| 10 | <Rm>, ROR <Rs>         | 寄存器循环右移   |

| 11 | <Rm>, RRX              | 寄存器扩展循环右移 |

数据处理指令寻址方式可以分为以下几种。

- (1) 立即数寻址方式。

- (2) 寄存器寻址方式。

- (3) 寄存器移位寻址方式。

### 1. 立即数寻址方式

指令中的立即数是由一个 8bit 的常数移动 4bit 偶数位 ( $0, 2, 4, \dots, 26, 28, 30$ ) 得到的。所以，每一条指令都包含一个 8bit 的常数 X 和移位值 Y，得到的立即数 = X 循环右移 ( $2 \times Y$ )，如图 3-1 所示。

图 3-1 立即数表示方法

下面列举了一些有效的立即数：

0xFF、0x104、0xFF0、0xFF00、0xFF000、0xFF00000、0xF00000F

下面是一些无效的立即数：

0x101、0x102、0xFF1、0xFF04、0xFF003、0xFFFFFFFF、0xF000001F

下面是一些应用立即数的指令：

```

MOV R0,#0          ;送 0 到 R0

ADD R3,R3,#1      ;R3 的值加 1

CMP R7,#1000      ;将 R7 的值和 1000 比较

BIC R9,R8,#0xFF00 ;将 R8 中 8~15 位清零，结果保存在 R9 中

```

### 2. 寄存器寻址方式

寄存器的值可以被直接用于数据操作指令，这种寻址方式是各类处理器经常采用的一种方式，也是一种执行效率较高的寻址方式，如：

```

MOV R2,R0          ;R0 的值送 R2

ADD R4,R3,R2      ;R2 加 R3，结果送 R4

CMP R7,R8          ;比较 R7 和 R8 的值

```

### 3. 寄存器移位寻址方式

寄存器的值在被送到 ALU 之前，可以事先经过桶形移位寄存器的处理。预处理和移位发生在同一周期内，所以有效地使用移位寄存器，可以增加代码的执行效率。

下面是一些在指令中使用了移位操作的例子：

```

ADD R2,R0,R1,LSR #5

MOV R1,R0,LSL #2

RSB R9,R5,R5,LSL #1

SUB R1,R2,R0,LSR #4

MOV R2,R4,ROR R0

```

### 3.1.2 内存访问指令寻址方式

内存访问指令的寻址方式可以分为以下几种。

- (1) 字及无符号字节的 Load/Store 指令的寻址方式。

- (2) 杂类 Load/Store 指令的寻址方式。

- (3) 批量 Load/Store 指令的寻址方式。

- (4) 协处理器 Load/Store 指令的寻址方式。

#### 1. 字及无符号字节的 Load/Store 指令的寻址方式

字及无符号字节的 Load/Store 指令语法格式如下：

```

LDR | STR {<cond>} {B} {T} <Rd>, <addressing_mode>

```

其中，<addressing\_mode>共有 9 种寻址方式，如表 3-2 所示。

表 3-2 字及无符号字节的 Load/Store 指令的寻址方式

|   | 格 式                              | 模 式                                            |

|---|----------------------------------|------------------------------------------------|

| 1 | [Rn, #±<offset_12>]              | 立即数偏移寻址<br>(Immediate offset)                  |

| 2 | [Rn, ±Rm]                        | 寄存器偏移寻址<br>(Register offset)                   |

| 3 | [Rn, Rm, <shift>#<offset_12>]    | 带移位的寄存器偏移寻址<br>(Scaled register offset)        |

| 4 | [Rn, #±<offset_12>]!             | 立即数前索引寻址<br>(Immediate pre-indexed)            |

| 5 | [Rn, ±Rm]!                       | 寄存器前索引寻址<br>(Register post-indexed)            |

| 6 | [Rn, Rm, <shift>#<offset_12>]!   | 带移位的寄存器前索引寻址<br>(Scaled register pre-indexed)  |

| 7 | [Rn], #±<offset_12>              | 立即数后索引寻址<br>(Immediate post-indeted)           |

| 8 | [Rn], ±<Rm>                      | 寄存器后索引寻址<br>(Register post-indexed)            |

| 9 | [Rn], ±<Rm>, <shift>#<offset_12> | 带移位的寄存器后索引寻址<br>(Scaled register post-indexed) |

上表中，“!”表示完成数据传输后要更新基址寄存器。

#### 2. 杂类 Load/Store 指令的寻址方式

使用该类寻址方式的指令的语法格式如下：

```

LDR | STR {<cond>} H | SH | SB | D <Rd>, <addressing_mode>

```

使用该类寻址方式的指令包括（有符号/无符号）半字 Load/Store 指令、有符号字节 Load/Store 指令和双字 Load/Store 指令。

该类寻址方式分为 6 种类型，如表 3-3 所示。

表 3-3 杂类 Load/Store 指令的寻址方式

|   | 格 式                 | 模 式                                  |

|---|---------------------|--------------------------------------|

| 1 | [Rn, #±<offset_8>]  | 立即数偏移寻址<br>(Immediate offset)        |

| 2 | [Rn, ±Rm]           | 寄存器偏移寻址<br>(Register offset)         |

| 3 | [Rn, #±<offset_8>]! | 立即数前索引寻址<br>(Immediate pre-indexed)  |

| 4 | [Rn, ±Rm]!          | 寄存器前索引寻址<br>(Register post-indexed)  |

| 5 | [Rn], #±<offset_8>  | 立即数后索引寻址<br>(Immediate post-indexed) |

| 6 | [Rn], ±<Rm>         | 寄存器后索引寻址<br>(Register post-indexed)  |

### 3. 批量 Load/Store 指令寻址方式

批量 Load/Store 指令将一片连续内存单元的数据加载到通用寄存器组中或将一组通用寄存器的数据存储到内存单元中。

批量 Load/Store 指令的寻址模式产生一个内存单元的地址范围，指令寄存器和内存单元的对应关系满足这样的规则，即编号低的寄存器对应于内存中低地址单元，编号高的寄存器对应于内存中的高地址单元。

该类指令的语法格式如下：

```

LDM | STM{ <cond>} <addressing_mode> <Rn>{ ! }, <registers><^>

```

该类指令的寻址方式如表 3-4 所示。

表 3-4 批量 Load/Store 指令的寻址方式

|   | 格 式                   | 模 式   |

|---|-----------------------|-------|

| 1 | IA (Increment After)  | 后递增方式 |

| 2 | IB (Increment Before) | 先递增方式 |

| 3 | DA (Decrement After)  | 后递减方式 |

| 4 | DB (Decrement Before) | 先递减方式 |

### 4. 堆栈操作寻址方式

堆栈操作寻址方式和批量 Load/Store 指令寻址方式十分类似。但对于堆栈的操作，数据写入内存和从内存中读出要使用不同的寻址模式，因为进栈操作 (pop) 和出栈操作 (push) 要在不同的方向上调整堆栈。

下面详细讨论如何使用合适的寻址方式实现数据的堆栈操作。

根据不同的寻址方式，将堆栈分为以下4种。

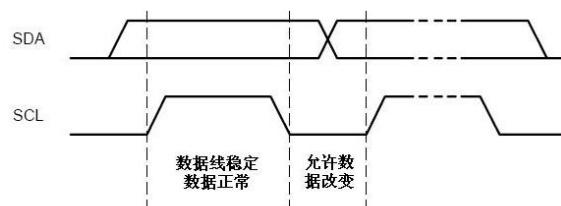

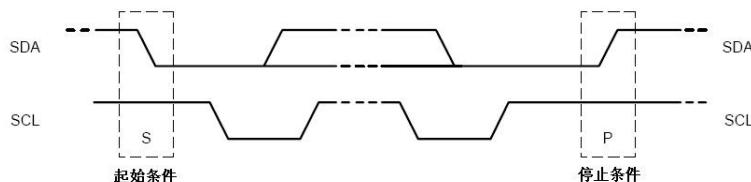

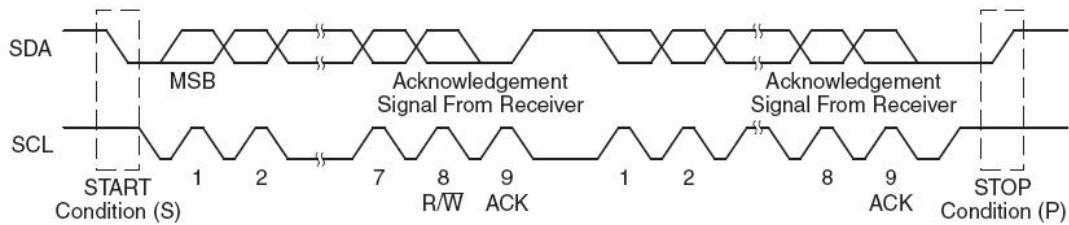

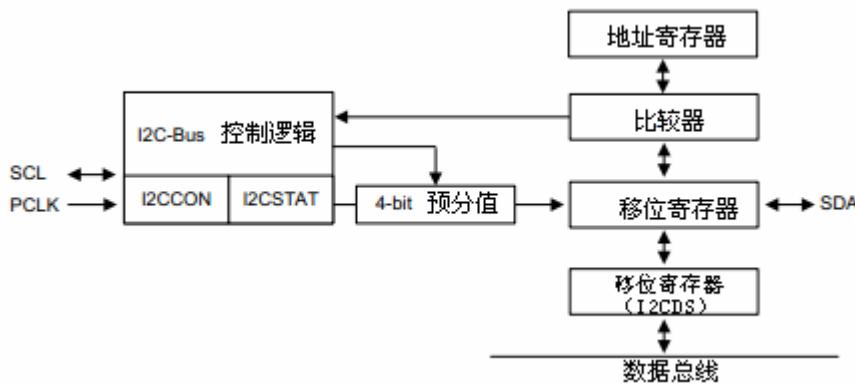

- (1) Full 栈：堆栈指针指向栈顶元素 (last used location)。