电子信息类综合创新实践系列教材

# DSP 原理及应用

## ——TMS320VC5509A 基础教程

张玉玺 王俊康 骊 编著

张有光 审校

电子工业出版社

**Publishing House of Electronics Industry**

北京 · BEIJING

## 内 容 简 介

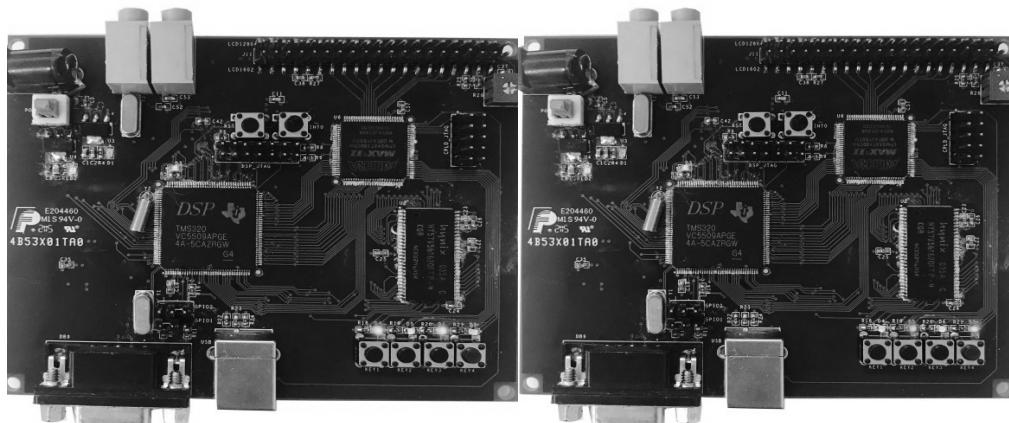

本书以 TI 公司的 DSP 芯片为例，系统地介绍了 DSP 的原理和应用方法。首先介绍了 DSP 的发展过程，引入 TI 公司的 C5000 系列 TMS320VC5509A 芯片，对其硬件设计方法进行了详细介绍；然后介绍了 TI 公司的 CCS 集成开发环境及其使用方法，并以 TMS320VC5509A 为例介绍了如何在 CCS 环境中进行 DSP 的软件开发调试方法；最后用一个完整的实例讲解如何进行 DSP 系统的开发调试。

本书语言浅显易懂，实例丰富，并在网站 <http://eelab.buaa.edu.cn/> 的“创新园地”栏目中给出了开源电路图与源程序。本书可作为高等院校电子信息工程类、通信工程类及计算机、自动控制类相关专业学生的教材，也可作为 DSP 芯片开发技术人员的初级培训教材。

未经许可，不得以任何方式复制或抄袭本书之部分或全部内容。

版权所有，侵权必究。

## 图书在版编目 (CIP) 数据

DSP 原理及应用：TMS320VC5509A 基础教程/张玉玺，王俊，康骊编著. —北京：电子工业出版社，2017.9

ISBN 978-7-121-32595-3

I . ①D… II . ①张… ②王… ③康… III . ①数字信号处理—高等学校—教材 IV . ①TN911.72

中国版本图书馆 CIP 数据核字 (2017) 第 212777 号

策划编辑：竺南直

责任编辑：桑 岚

印 刷：

装 订：

出版发行：电子工业出版社

北京市海淀区万寿路 173 信箱 邮编 100036

开 本：787×1 092 1/16 印张：13.5 字数：346 千字

版 次：2017 年 9 月第 1 版

印 次：2017 年 9 月第 1 次印刷

定 价：35.00 元

凡所购买电子工业出版社图书有缺损问题，请向购买书店调换。若书店售缺，请与本社发行部联系，联系及邮购电话：(010) 88254888, 88258888。

质量投诉请发邮件至 [zlts@phei.com.cn](mailto:zlts@phei.com.cn)，盗版侵权举报请发邮件至 [dbqq@phei.com.cn](mailto:dbqq@phei.com.cn)。

本书咨询联系方式：[davidzhu@phei.com.cn](mailto:davidzhu@phei.com.cn)。

# 丛书序言

当前世界范围内新一轮科技革命和产业变革加速进行，综合国力竞争越加激烈。而高等教育发展水平是一个国家发展水平和发展潜力的重要标志。习近平总书记指出，“我们对高等教育的需要比以往任何时候都更加迫切，对科学知识和卓越人才的渴求比以往任何时候都更加强烈”。

世界高等工程教育面临新机遇、新挑战，我国高等工程教育改革发展已经站在新的历史起点。国家正在实施“创新驱动发展”“中国制造 2025”“互联网+”“网络强国”“一带一路”等重大战略，为响应国家战略需求，支撑服务以新技术、新业态、新产业、新模式为特点的新经济蓬勃发展。面对这一机遇与挑战，高等院校电子信息工程专业需要以“新工科”建设思想为指导，在教学理念与模式、知识结构、培养质量与体系等方面深化改革，注重学科交叉和产教融合深度实践，推进教材内容与结构的完善和更新，从而培养具有创新能力、工程实践能力和多元知识结构的新型工科人才。

我国大多数工科类高等院校都设置有电子信息专业，这是一个涉及数学、物理电学、电路分析、电工基础、电子技术、信号与系统、计算机控制原理、通信原理等多门课程的专业体系。其内容涵盖了社会的诸多层面，为国家发展提供了无可替代的强大助力。电子信息专业不仅要求学生具有扎实的理论与宽广的知识面，更要求学生具备一定的工程实践能力。作为一门应用型学科，其着眼于培养学生科技创新、应用创新的能力，使学生成为推进国家科技发展的高素质技术人才。

北京航空航天大学于 1958 年 10 月 29 日成立了新中国第一个航空无线电系，经过几十年的建设，已拥有信息与通信工程、电子科学与技术、光学工程、交通工程等一级学科，并于 2002 年成立电子信息工程学院。学院依托国家/省部级重点实验室、国家集成电路人才培养基地和北京市电工电子实验教学示范中心，于 2012 年获批空天电子信息国家级实验教学示范中心。示范中心坚持“强化基础、重视实践、突出特色、面向创新”的空天信融合人才培养总体思路，以“战略牵引、科教相融、产学互动、虚实结合、能实不虚”的设计理念，建设虚实结合实验平台，于 2014 年获批空天电子信息国家级虚拟仿真实验教学中心。

中心建立了信息基础支撑类实验课程群、卫星通信导航类实验课程群、信息获取处理类实验课程群、通用航空类实验课程群、无线网络安全类实验课程群、电磁环境效应类实验课程群等 6 大类实验课程群，可以满足电子信息工程、通信工程、电子科学技术、信息对抗技术、交通运输、光电通信等专业开展跨专业跨学科的实验教学需求。

中心同时作为大学生电子创新基地，承办全国/北京市/校级电子类学科竞赛，承担全校电子信息类学科竞赛赛前训练，包括全国大学生电子设计竞赛、全国挑战杯竞赛、北京市大学生电子设计竞赛、嵌入式专题邀请赛、全国大学生电子设计竞赛信息安全专题邀请赛、全国电子专业人才技能竞赛、全国信息安全竞赛、北航“冯如杯”学生科技竞赛、北航电子创新竞赛等，并在各项比赛中取得了优异的成绩。

结合“新工科”建设和工程教育专业认证的要求，中心整合理论课程实验、开设综合实验、完善科技创新实验，形成了课程实验、综合实验、创新实验的多层次实验教学体系，着

重培养学生工程实践、科技创新及解决复杂工程问题能力。并开设了综合创新实验实践课程，包括《电子设计基础训练》《单片机基础训练》《综合创新-模拟通信》《综合创新-数字通信》《综合创新-综合设计》，贯穿本科一年级到三年级。本着从简单到复杂、从基础到综合、从经典到创新，通过模拟现代复杂工程问题的研发步骤，培养学生使用现代工具认识、解决复杂工程问题的能力与创新意识。

在综合创新实践课程体系基础上，编写了本系列教材（丛书），从电子设计的基础知识，到电路系统的仿真与设计；从简单的电路模块设计，到实际工程电路系统的设计；从电子电路系统设计，到跨学科系统设计。在电子设计基础训练中，主要讲述基本的元器件识别、仪器使用以及在电路调试中常见问题的分析与解决方法；在单片机基础训练中，主要讲述 51 单片机和 Arduino 单片机的基本原理与结构，并以实际的单片机系统为例进行单片机系统设计讲解；在模拟通信和数字通信中，以从通信、导航、雷达系统中提取出的无线收发机为原型，从单元模块到整体讲述模拟/数字无线通信系统的设计与调试方法、FPGA/DSP 系统设计与实现方法等；在综合设计中，结合北航优势特色专业，以工程项目为设计目标，培养跨学科知识运用和系统设计能力。

为了让读者能够更直观地理解知识内容、更快地进行实践，本丛书采用了教学案例以及实际的工程实例，其目的并不只是形成系列的实验指导书，让学生按照步骤实现指定实验内容，而是本着“授人以渔”的理念，通过启发式的讲解，引导学生发现问题、分析问题、解决问题，培养学生重构知识及快速学习新事物的能力。该丛书的正式出版和推广，将有利于形成“新工科”背景下的综合创新实验体系，能够促进电子信息类学生工程实践能力及解决复杂工程问题能力的培养。

丛书的编写创作主要由电子信息领域内具有丰富教学经验的教授、从事一线实验教学的教师及博士硕士研究生担纲，他们既要完成繁重的科研和教学任务，又要专心认真撰写书稿，工作十分辛苦，在此，向丛书作者和审稿专家表示深深的敬意！

希望本丛书中电子系统的设计调试方法及电路系统的调试经验等，能对高等院校、大专院校电子信息类专业的本科生、研究生以及从事电子设计以及对电子设计有兴趣的工程师、研发人员等有所帮助，从而促进我国电子信息技术的发展，为国家信息化建设和国民经济建设做出贡献。

本丛书的出版，得到了北京航空航天大学电子信息工程学院、空天电子信息国家级实验教学示范中心、空天电子信息国家级虚拟仿真实验教学中心等参与单位的大力支持，得到了电子工业出版社领导和竺南直博士的积极推动，得到了参与丛书撰写、编辑和出版工作全体同志的热情帮助，在此一并表示衷心的感谢！

北京市教学名师

工业和信息化部研究型教学创新团队负责人

# 前　　言

数字信号处理器件在近几十年发展十分迅速，种类越来越多，运算速度越来越快，功能和性能都不断增强，广泛应用于语音处理、图形图像、航空航天、仪器仪表、医疗和家用电器等产品中，成为电子产品中的核心器件。

现在 DSP 芯片的集成开发环境比较完善，支持 C 语言开发，优化编译效率逐步提高，程序可移植性好，DSP 的原理与开发应用也成为电子信息类学生及技术人员的必备硬件技能。为了能够让更多的 DSP 初学者快速入门，了解 DSP 芯片的基本原理和常用 DSP 芯片的应用，熟悉 DSP 芯片开发工具及使用方法，尽快掌握 DSP 的软硬件设计和应用系统开发方法，具备从事 DSP 芯片软硬件设计和 DSP 系统开发的能力，我们编写了这本教材。

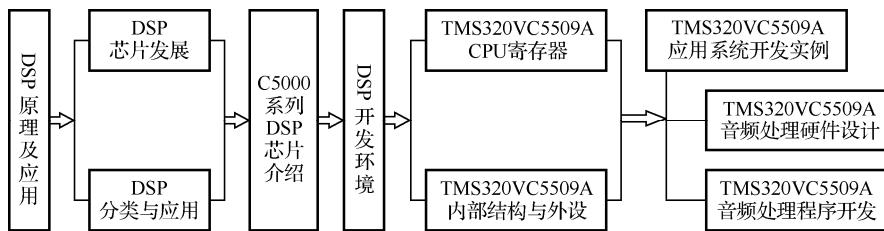

本书以 TI 的 DSP 芯片设计调试为主线，按照 DSP 常识介绍、开发环境、内部寄存器、外设、开发实例的顺序展开，如图 1 所示。

图 1 本书内容组织结构图

第 1 章主要以 TI 公司的 DSP 芯片为例介绍了 DSP 的发展过程、DSP 的分类与应用，引入 C5000 系列 DSP，对其常用的 C54x 和 C55x 系列芯片的结构、性能等进行了比较分析。

第 2 章介绍了 TI 公司 DSP 的集成开发环境 CCS，包括 CCS 的安装、建立工程以及如何调试工程等。

第 3 章详细介绍了 TMS320VC5509A 芯片的 CPU 寄存器。

第 4 章详细介绍了 TMS320VC5509A 芯片结构和片内外设，并给出以芯片支持库（CSL）编写的外设调试例程。

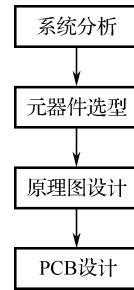

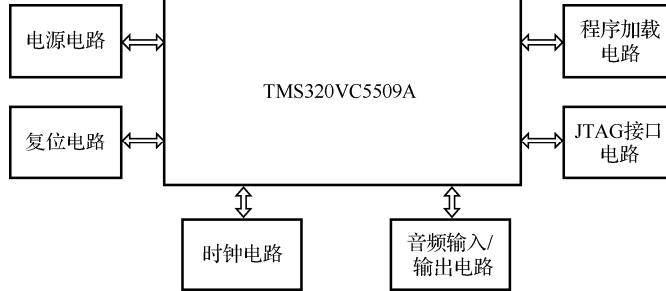

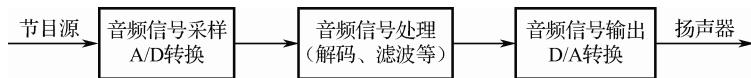

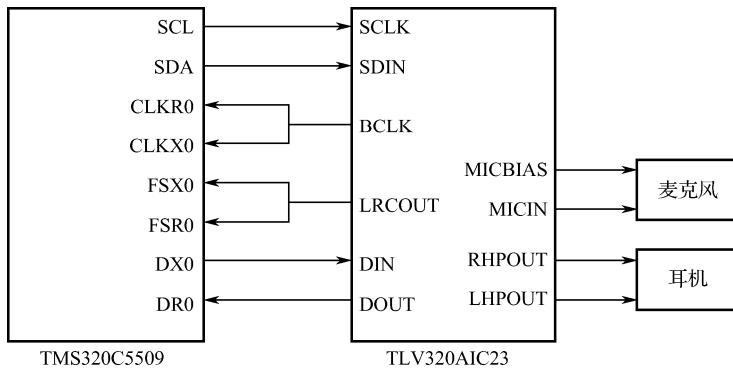

第 5 章介绍了 DSP 系统设计的一般流程，并以一个音频处理 DSP 系统为例，从原理图设计、PCB 设计以及 Boot 引导等方面详细介绍了 TMS320VC5509A 芯片的硬件电路设计过程。

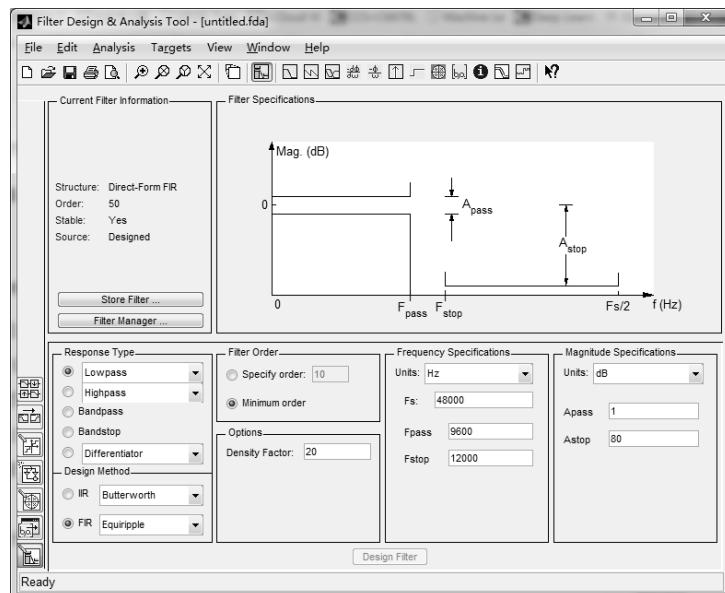

第 6 章以第 5 章的硬件电路为基础，介绍了音频滤波数字处理系统和 DTMF 识别与生成系统的程序开发过程，并在附录 C 中给出了源程序代码。

为了方便读者查询，附录 A 和附录 B 分别列出了 TMS320VC5509A 芯片引脚定义及 TMS320C55x 指令集。

本书由张玉玺、王俊、康骊编著，其中张玉玺编著了第 1、2、3 章及附录 A、B、C；王俊编著了第 4、5 章；康骊根据学生实验课的内容整理了第 6 章素材；最后由张玉玺对本书进行统稿。本书在编写过程中，北京航空航天大学电子信息工程学院的硕士生樊文贵、尹晗、陈力、张振、马抒恒等结合学位论文和项目调试经验，参与了 DSP 例程的编写与书稿的编辑工作。

本教材配有开源电路图及源程序，可登录北京航空航天大学空天电子信息实验教学中心网站（<http://eelab.buaa.edu.cn/>）免费下载。

书中如有疏漏不当之处，恳请广大读者批评指正。

编著者

# 目 录

|                                          |      |

|------------------------------------------|------|

| <b>第 1 章 概论</b> .....                    | (1)  |

| 1.1 DSP (数字信号处理器) .....                  | (1)  |

| 1.2 DSP 芯片发展 .....                       | (1)  |

| 1.3 DSP 分类与应用 .....                      | (3)  |

| 1.4 TMS320C5000 系列 DSP 概述 .....          | (4)  |

| 1.4.1 TMS320C54x 系列 DSP .....            | (5)  |

| 1.4.2 TMS320C55x 系列 DSP .....            | (5)  |

| 1.4.3 C54x 与 C55x 的比较 .....              | (6)  |

| 1.4.4 TMS320C5000 系列 DSP 外设接口 .....      | (7)  |

| 1.5 TMS320C5000 系列芯片性能分析 .....           | (7)  |

| 1.5.1 主要性能分析 .....                       | (7)  |

| 1.5.2 C54x 系列芯片性能 .....                  | (8)  |

| 1.5.3 C55x 系列芯片性能 .....                  | (9)  |

| 1.6 TMS320C5000 系列 DSP 应用 .....          | (11) |

| <b>第 2 章 CCS 集成开发环境</b> .....            | (12) |

| 2.1 CCS 概述 .....                         | (12) |

| 2.2 集成代码生成工具 .....                       | (13) |

| 2.3 CCSv5.1 的安装 .....                    | (14) |

| 2.4 利用 CCSv5.1 新建工程 .....                | (16) |

| 2.5 利用 CCSv5.1 导入已有工程 .....              | (19) |

| 2.6 利用 CCSv5.1 配置工程选项 .....              | (20) |

| 2.7 利用 CCSv5.1 调试工程 .....                | (25) |

| 2.8 CCSv5.1 资源管理器简介及应用 .....             | (28) |

| <b>第 3 章 TMS320VC5509A CPU 寄存器</b> ..... | (30) |

| 3.1 寄存器列表 .....                          | (30) |

| 3.1.1 寄存器的存储器映射 .....                    | (31) |

| 3.1.2 累加器 (AC0~AC3) .....                | (34) |

| 3.1.3 变换寄存器 (TRN0, TRN1) .....           | (35) |

| 3.1.4 临时寄存器 (T0~T3) .....                | (35) |

| 3.1.5 数据和 I/O 空间寻址寄存器 .....              | (35) |

| 3.1.6 程序流寄存器 (PC, RETA, CFCT) .....      | (40) |

| 3.1.7 中断管理寄存器 .....                      | (41) |

| 3.1.8 循环控制寄存器 .....                      | (45) |

| 3.1.9 状态寄存器 (ST0_55~ST3_55) .....        | (46) |

|              |                                    |             |

|--------------|------------------------------------|-------------|

| 3.2          | 存储器和 I/O 空间 .....                  | (47)        |

| 3.2.1        | 存储器概述 .....                        | (47)        |

| 3.2.2        | 程序空间 .....                         | (48)        |

| 3.2.3        | 数据空间 .....                         | (48)        |

| 3.2.4        | I/O 空间 .....                       | (50)        |

| 3.3          | 数据堆栈和系统堆栈 .....                    | (50)        |

| 3.3.1        | 数据堆栈和系统堆栈 .....                    | (50)        |

| 3.3.2        | 堆栈配置 .....                         | (51)        |

| 3.3.3        | 快返回与慢返回 .....                      | (51)        |

| 3.3.4        | 自动上下文切换 .....                      | (52)        |

| 3.4          | 寻址模式 .....                         | (53)        |

| 3.4.1        | 概述 .....                           | (53)        |

| 3.4.2        | 绝对寻址模式 .....                       | (54)        |

| 3.4.3        | 直接寻址模式 .....                       | (55)        |

| 3.4.4        | 间接寻址模式 .....                       | (59)        |

| 3.4.5        | 寄存器位寻址 .....                       | (69)        |

| 3.4.6        | 环形寻址 .....                         | (70)        |

| <b>第 4 章</b> | <b>TMS320VC5509A 内部结构与外设 .....</b> | <b>(72)</b> |

| 4.1          | 总体概述 .....                         | (72)        |

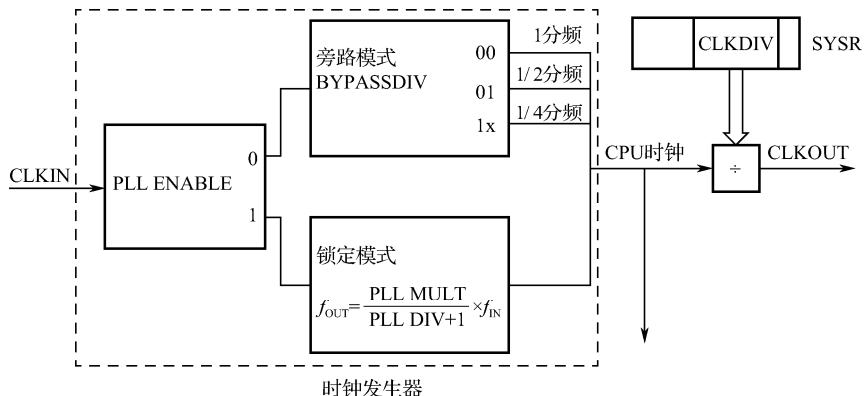

| 4.2          | 时钟发生器 .....                        | (73)        |

| 4.2.1        | 时钟发生器工作原理 .....                    | (74)        |

| 4.2.2        | 时钟发生器调试方法及结果 .....                 | (75)        |

| 4.2.3        | 时钟发生器程序示例 .....                    | (75)        |

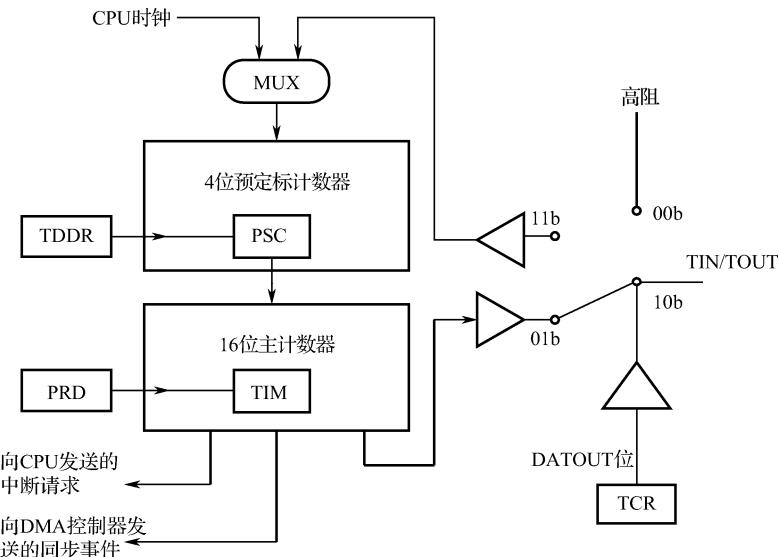

| 4.3          | 通用定时器 .....                        | (76)        |

| 4.3.1        | 通用定时器工作原理 .....                    | (77)        |

| 4.3.2        | 通用定时器调试方法及结果 .....                 | (78)        |

| 4.3.3        | 通用定时器程序示例 .....                    | (78)        |

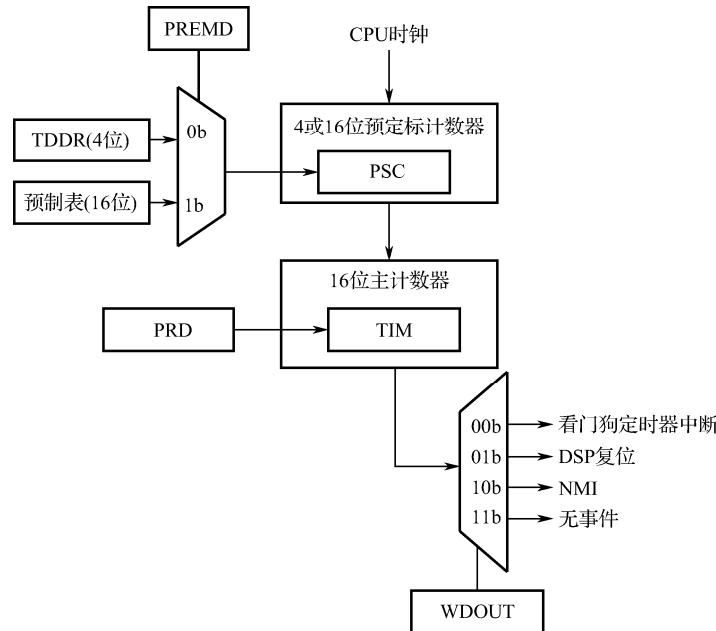

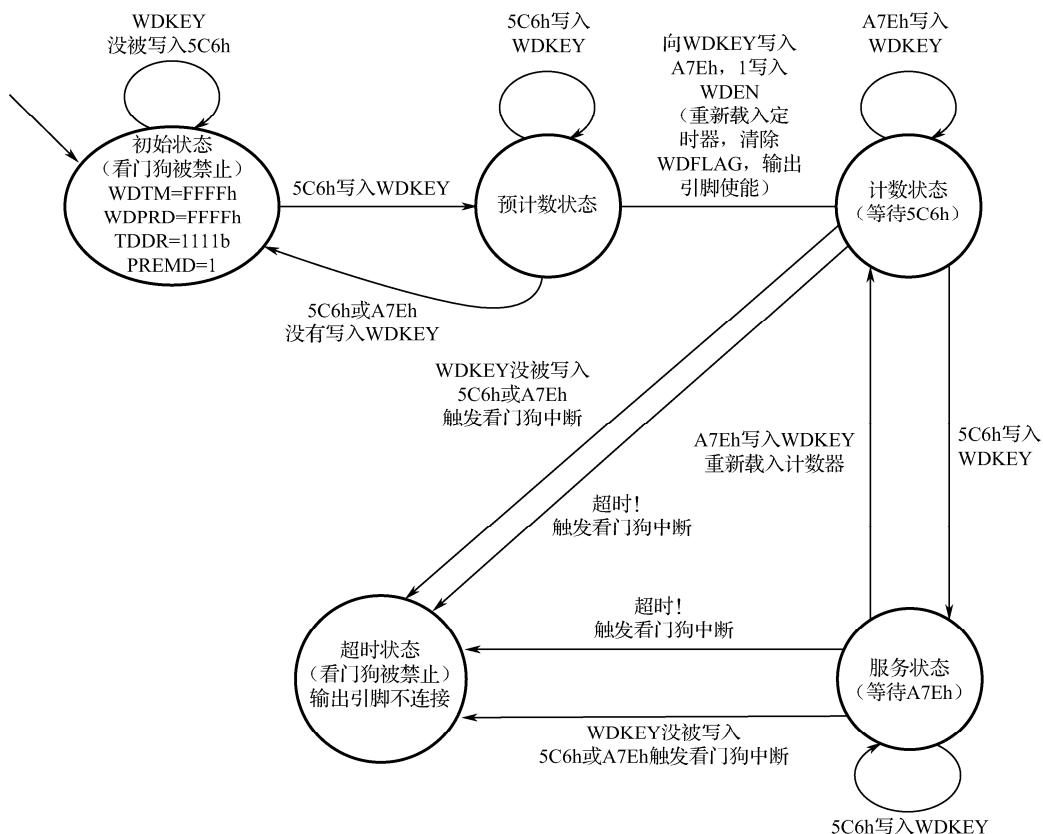

| 4.4          | 看门狗定时器 .....                       | (79)        |

| 4.4.1        | 看门狗定时器的工作原理 .....                  | (79)        |

| 4.4.2        | 看门狗定时器调试方法及结果 .....                | (81)        |

| 4.4.3        | 看门狗定时器程序示例 .....                   | (81)        |

| 4.5          | GPIO .....                         | (82)        |

| 4.5.1        | GPIO 工作模式 .....                    | (82)        |

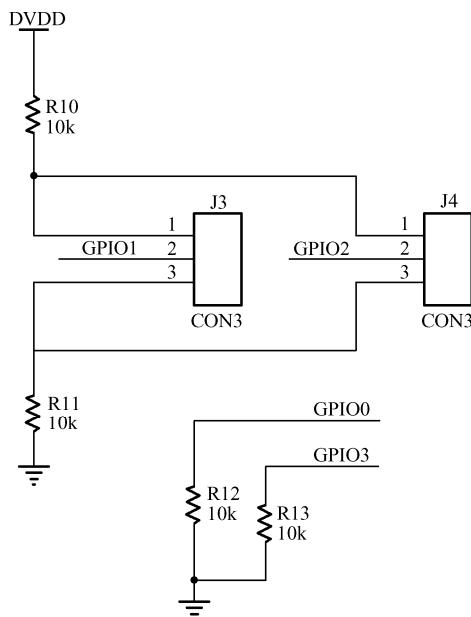

| 4.5.2        | GPIO 调试方法及结果 .....                 | (83)        |

| 4.5.3        | GPIO 程序示例 .....                    | (83)        |

| 4.6          | 中断 .....                           | (84)        |

| 4.6.1        | 中断工作原理 .....                       | (84)        |

| 4.6.2        | 中断调试方法及结果 .....                    | (85)        |

| 4.6.3        | 中断程序示例 .....                       | (86)        |

|              |                                          |       |

|--------------|------------------------------------------|-------|

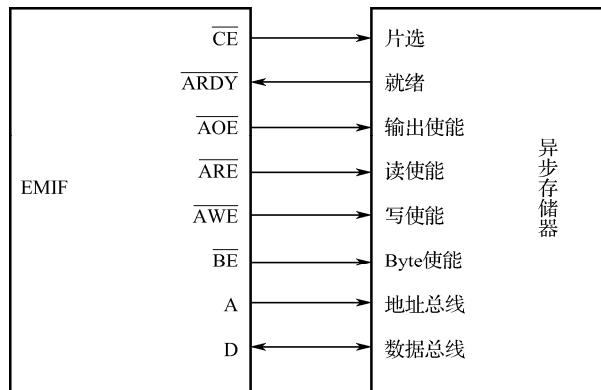

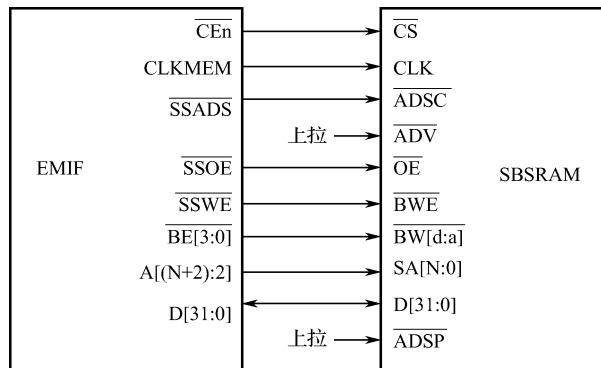

| 4.7          | EMIF                                     | (86)  |

| 4.7.1        | EMIF 工作原理                                | (86)  |

| 4.7.2        | EMIF 调试方法及结果                             | (89)  |

| 4.7.3        | 外部存储器接口程序示例                              | (89)  |

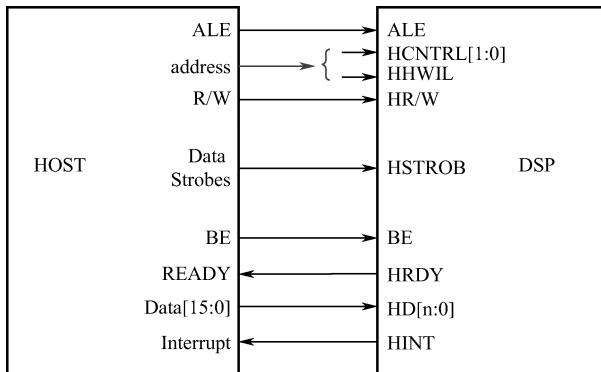

| 4.8          | HPI                                      | (90)  |

| 4.8.1        | HPI 接口工作原理                               | (90)  |

| 4.8.2        | HPI 模块调试方法及结果                            | (91)  |

| 4.8.3        | HPI 程序示例                                 | (92)  |

| 4.9          | McBSP                                    | (92)  |

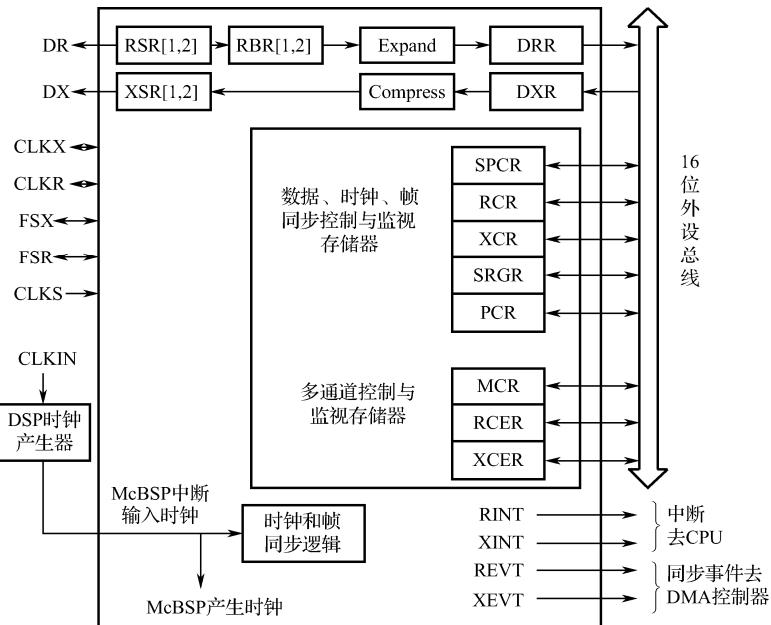

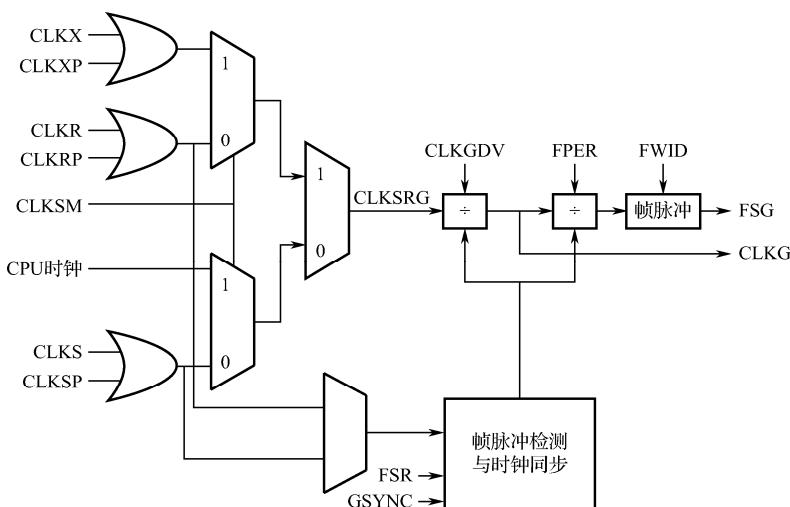

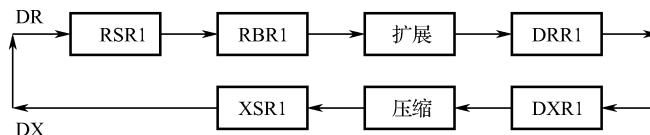

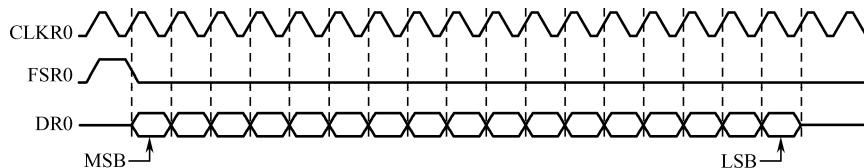

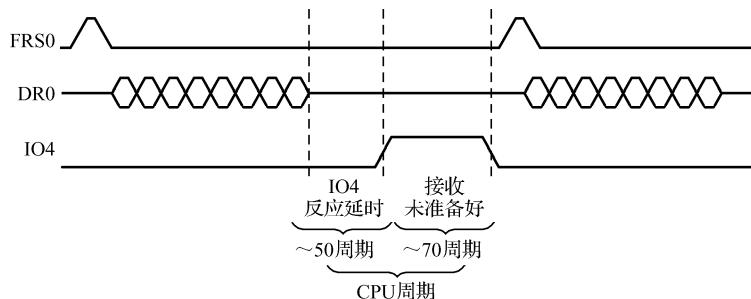

| 4.9.1        | McBSP 工作原理                               | (94)  |

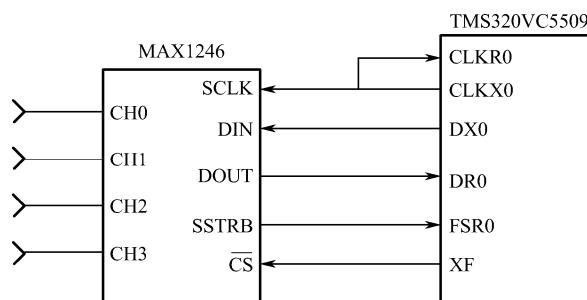

| 4.9.2        | McBSP 调试方法及结果                            | (95)  |

| 4.9.3        | McBSP 程序示例                               | (96)  |

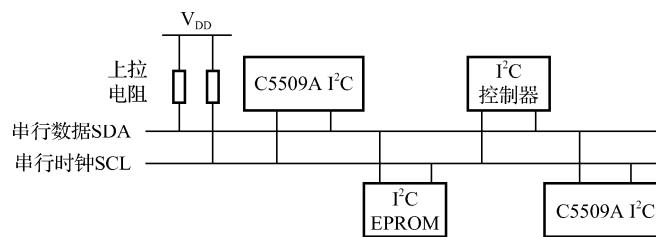

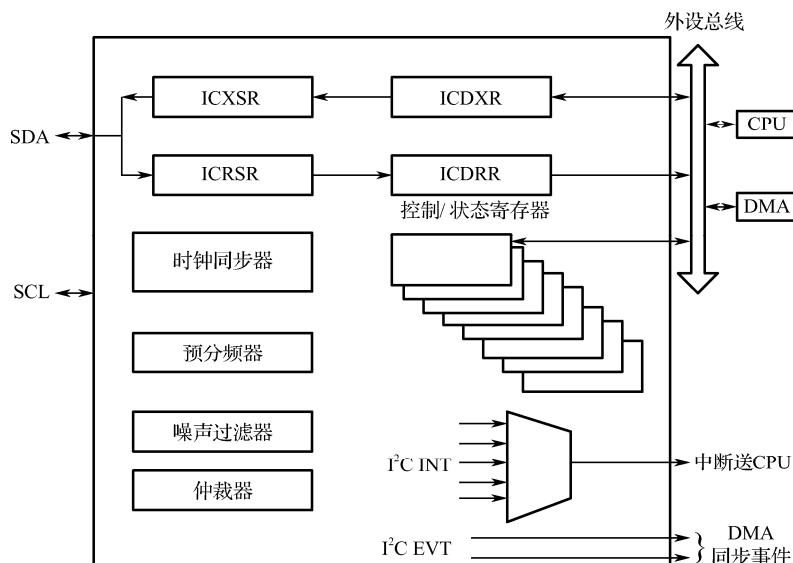

| 4.10         | I <sup>2</sup> C                         | (98)  |

| 4.10.1       | I <sup>2</sup> C 模块工作原理                  | (99)  |

| 4.10.2       | I <sup>2</sup> C 模块调试方法及结果               | (101) |

| 4.10.3       | I <sup>2</sup> C 模块程序示例                  | (102) |

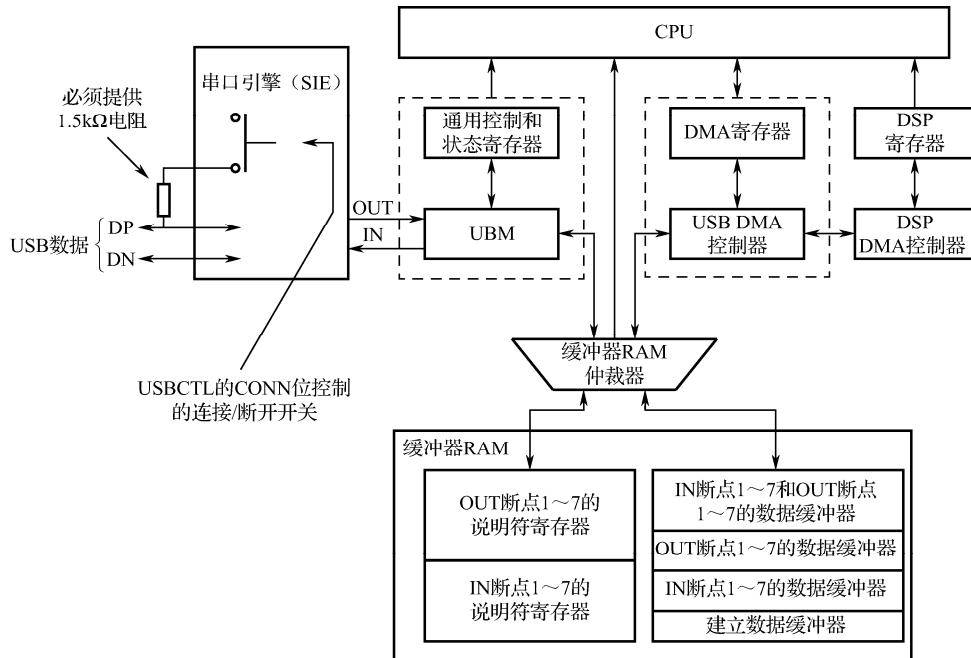

| 4.11         | USB                                      | (102) |

| 4.11.1       | USB 模块工作原理                               | (103) |

| 4.11.2       | USB 调试方法及结果                              | (104) |

| 4.11.3       | USB 模块程序示例                               | (104) |

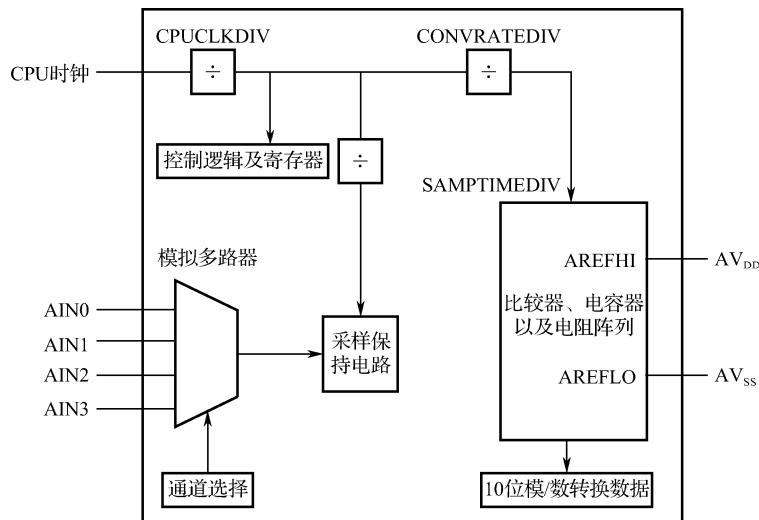

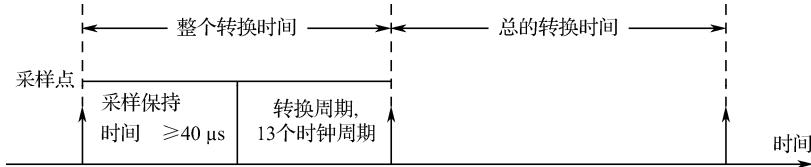

| 4.12         | ADC                                      | (105) |

| 4.12.1       | 模数转换器工作原理                                | (106) |

| 4.12.2       | ADC 调试方法及结果                              | (106) |

| 4.12.3       | 模数转换器程序示例                                | (107) |

| <b>第 5 章</b> | <b>基于 TMS320VC5509A 的音频处理 DSP 系统硬件设计</b> | (108) |

| 5.1          | 音频处理 DSP 系统硬件电路组成                        | (108) |

| 5.2          | 模块电路元器件选型及原理图设计                          | (109) |

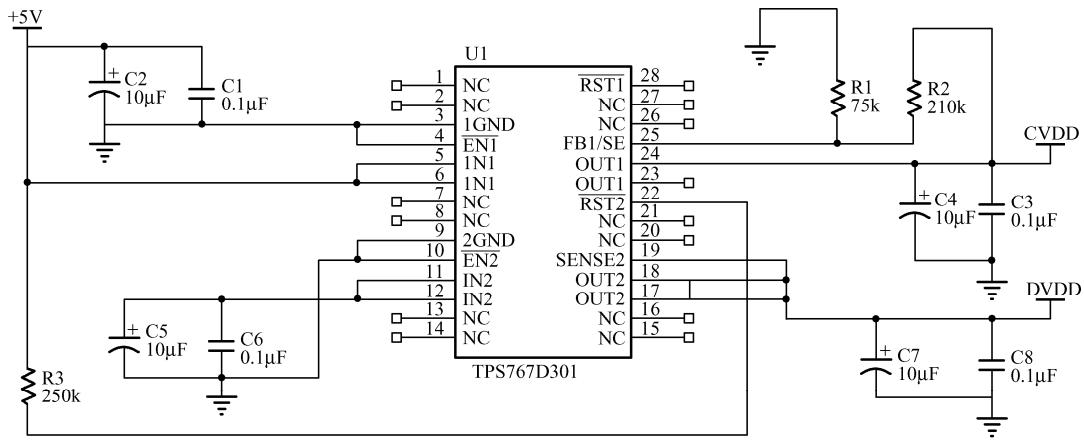

| 5.2.1        | 电源模块设计                                   | (109) |

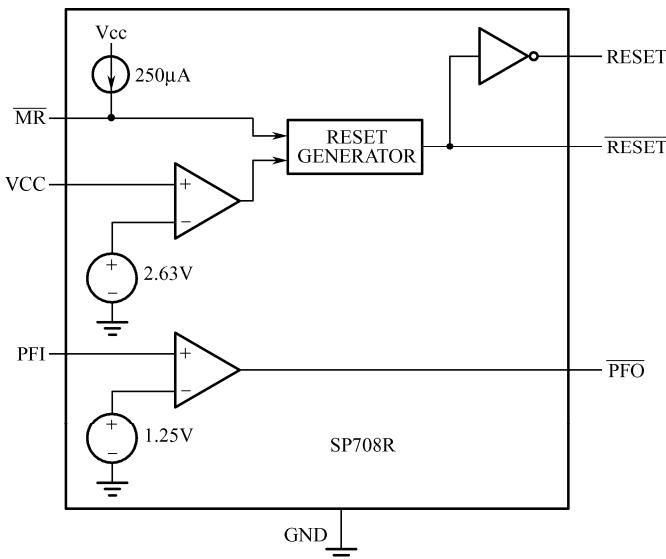

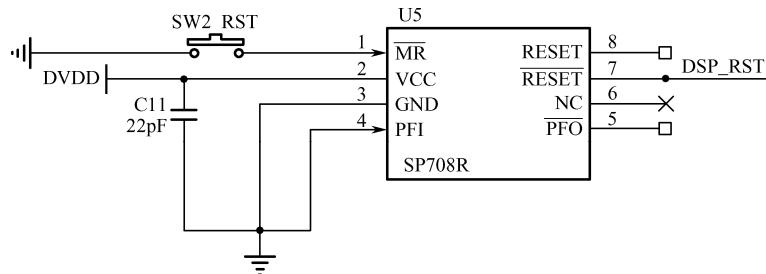

| 5.2.2        | 复位电路设计                                   | (110) |

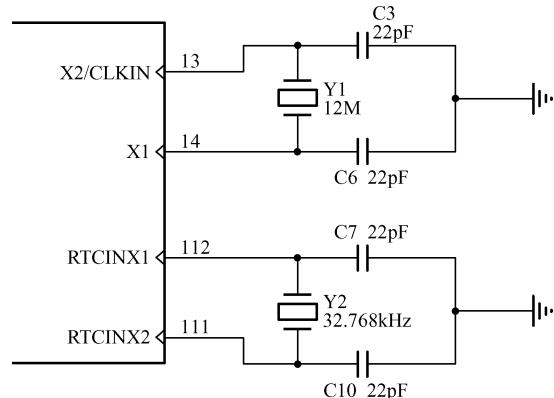

| 5.2.3        | 时钟电路设计                                   | (111) |

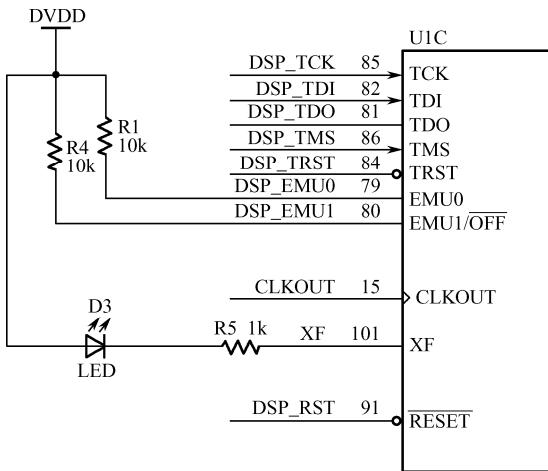

| 5.2.4        | JTAG 接口电路设计                              | (111) |

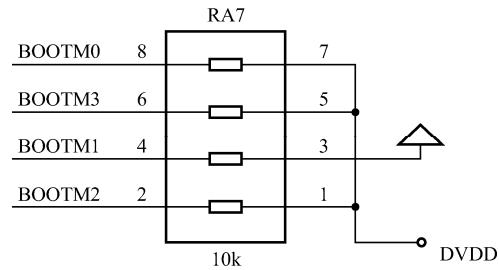

| 5.2.5        | 程序加载设计                                   | (112) |

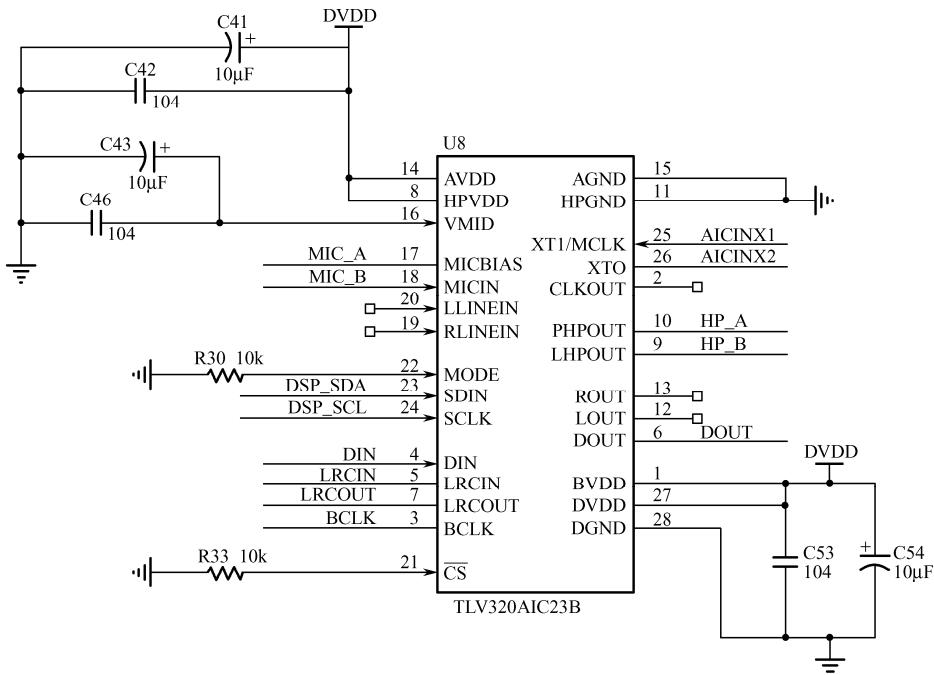

| 5.2.6        | 音频输入/输出电路设计                              | (116) |

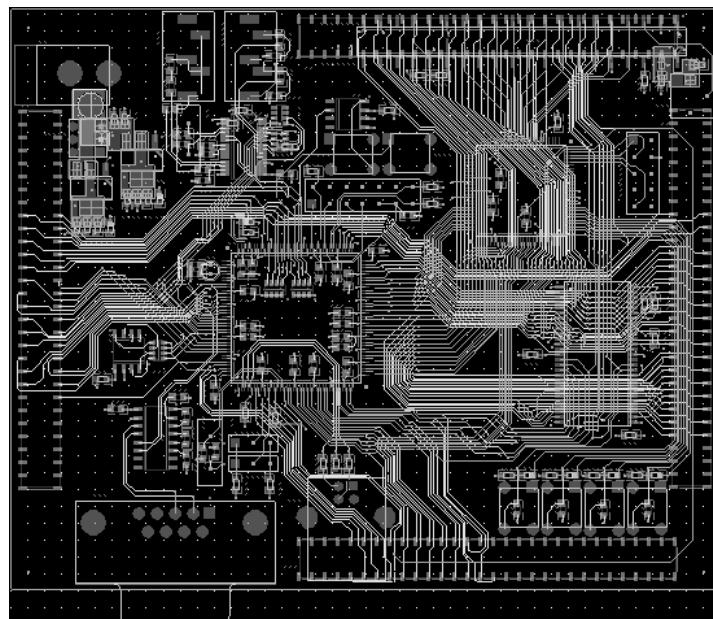

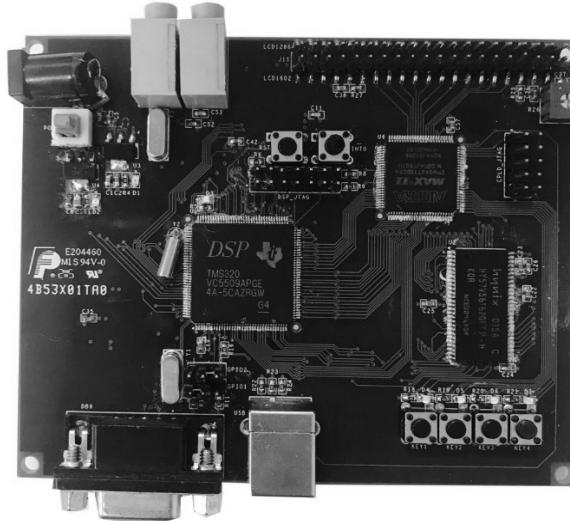

| 5.3          | PCB 设计                                   | (117) |

| 5.3.1        | 布局设计                                     | (117) |

| 5.3.2        | 布线设计                                     | (118) |

| 5.4          | 电路调试                                     | (121) |

| 5.4.1        | 硬件调试前电路板的常规检查                            | (121) |

| 5.4.2        | 调试中遇到问题的解决步骤                             | (122) |

|                                                     |              |

|-----------------------------------------------------|--------------|

| 5.4.3 JTAG 连接错误常用解决办法.....                          | (122)        |

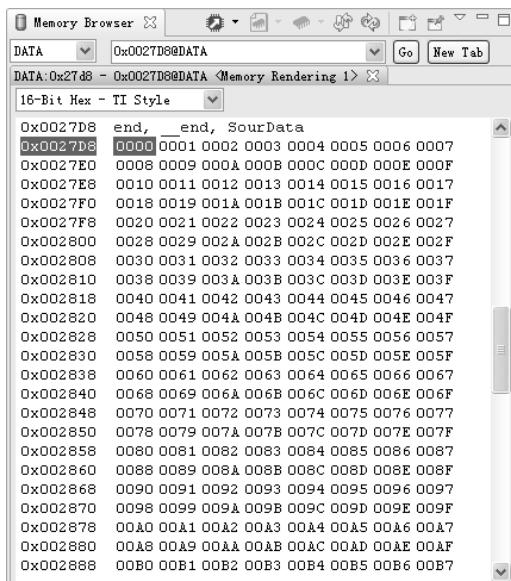

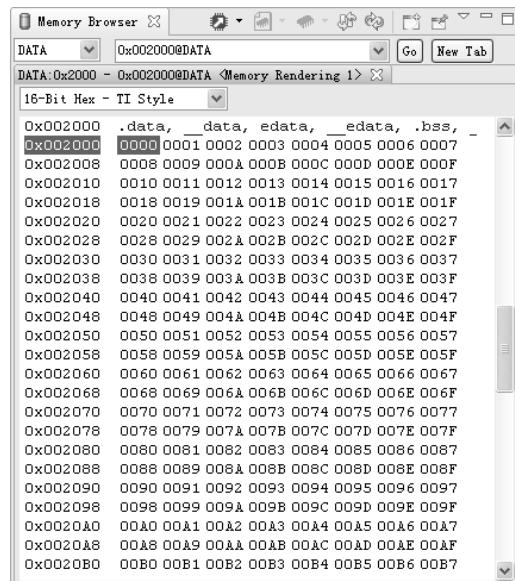

| 5.4.4 数据读/写测试 .....                                 | (123)        |

| 5.5 Boot.....                                       | (124)        |

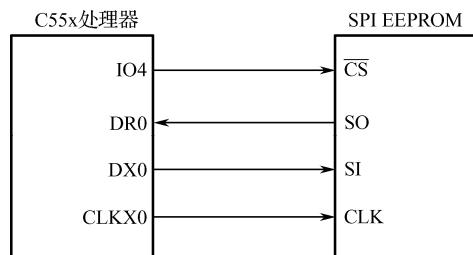

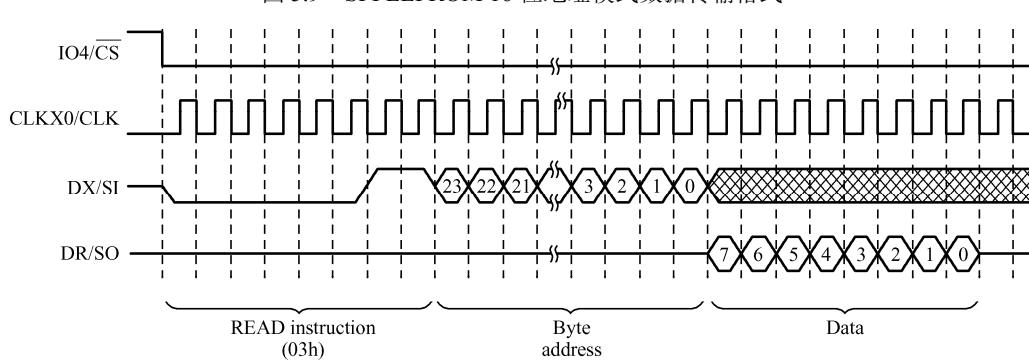

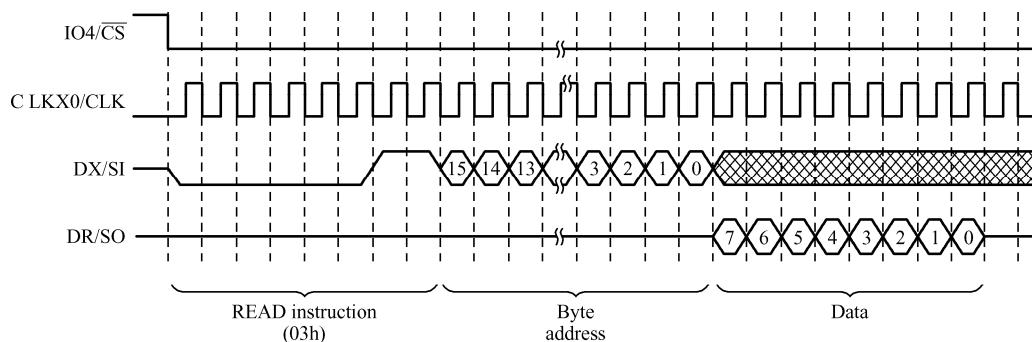

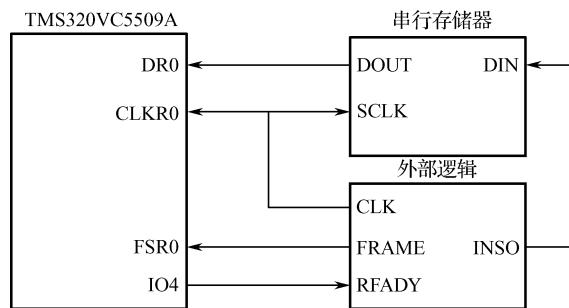

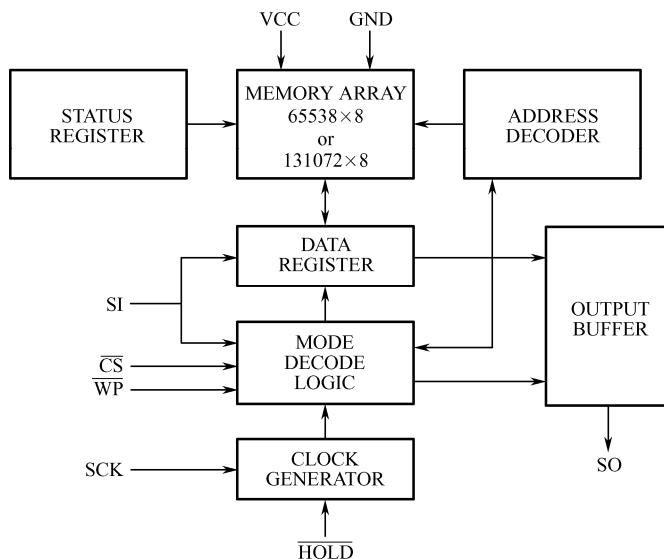

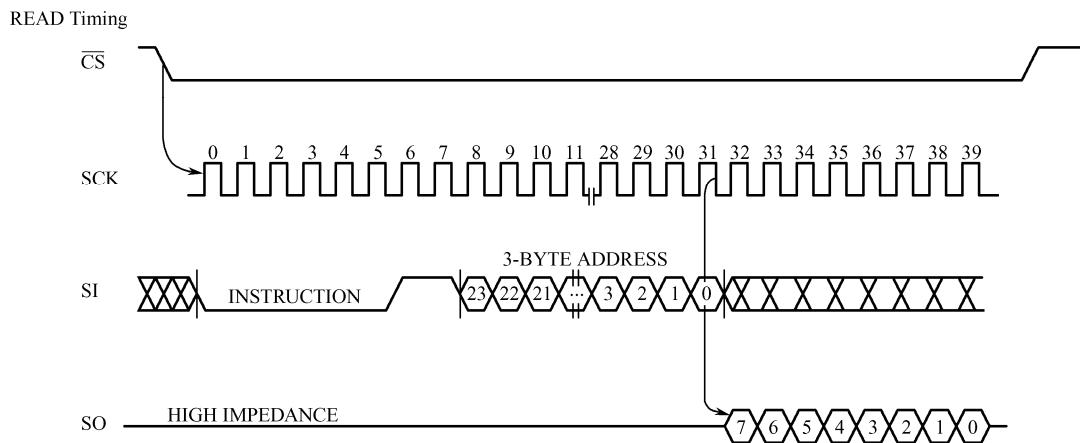

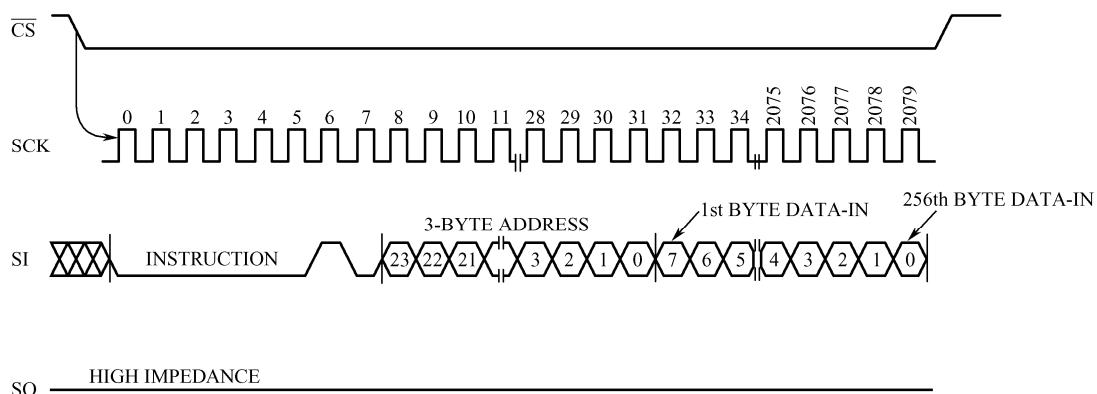

| 5.5.1 EEPROM 的读/写 .....                             | (124)        |

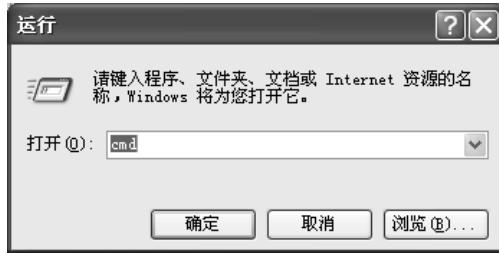

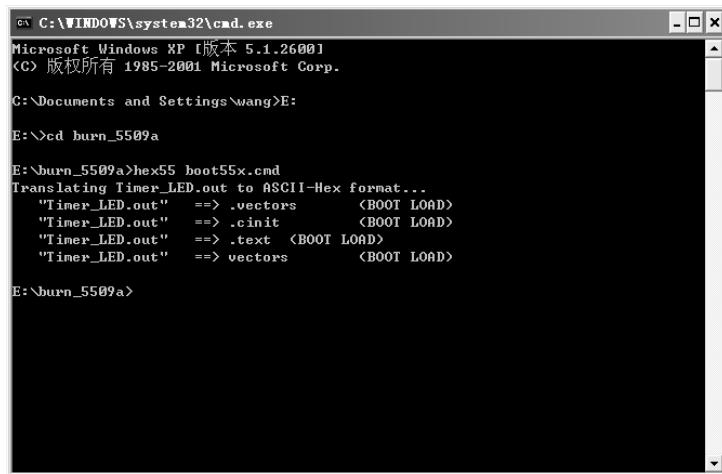

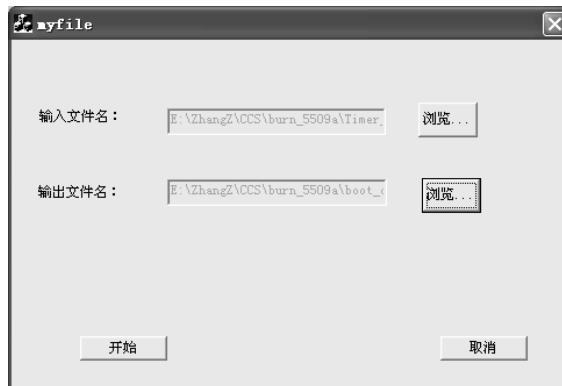

| 5.5.2 DSP bootLoader 烧写步骤 .....                     | (126)        |

| <b>第 6 章 基于 TMS320VC5509A 的音频处理 DSP 系统程序设计.....</b> | <b>(129)</b> |

| 6.1 概述.....                                         | (129)        |

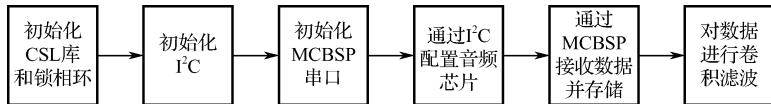

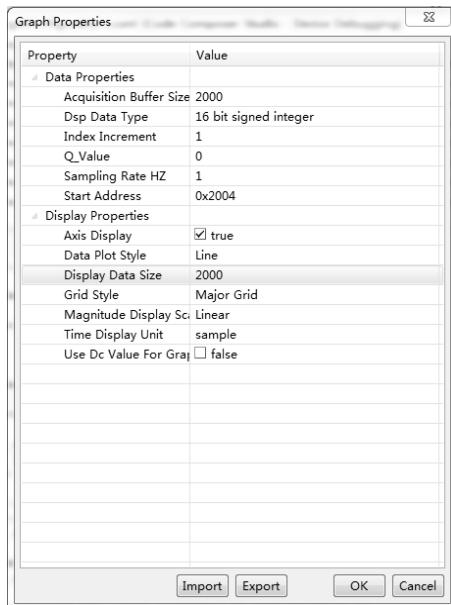

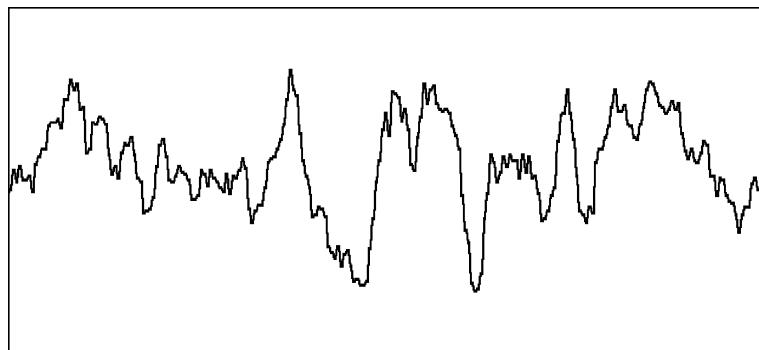

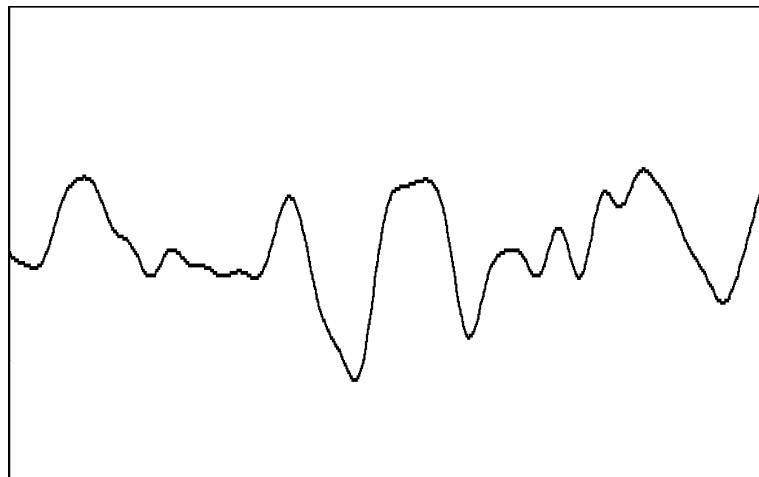

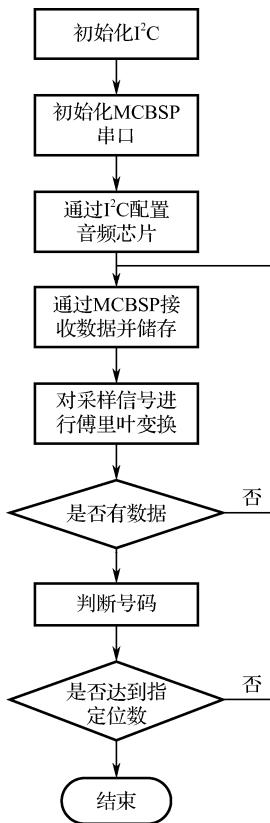

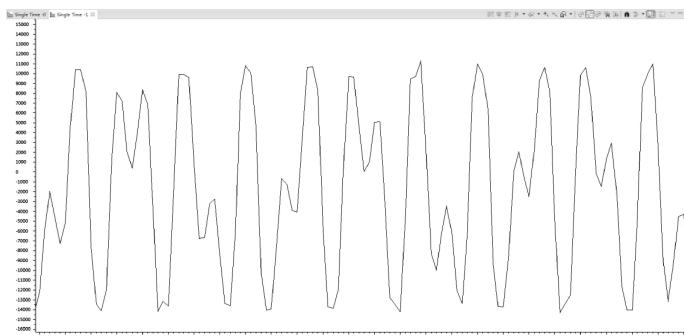

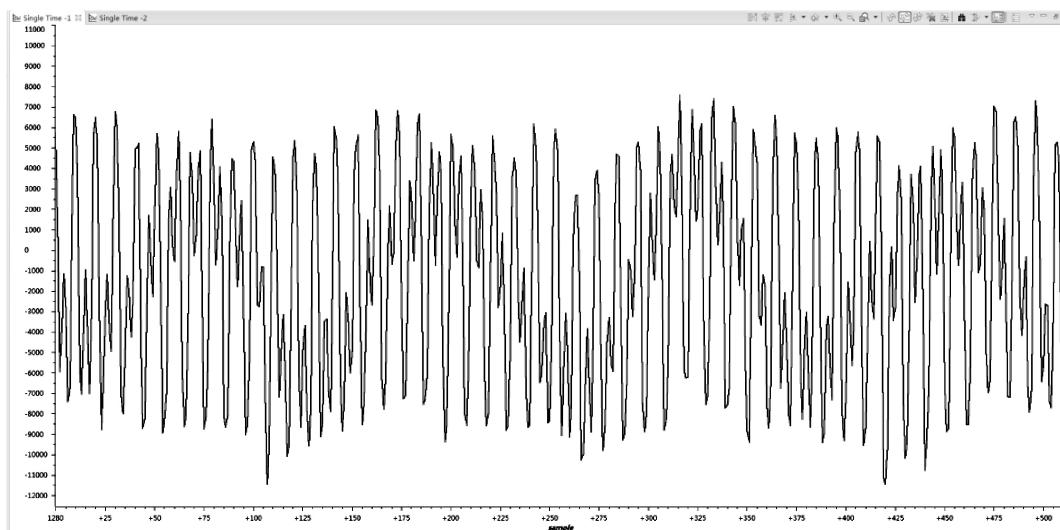

| 6.2 采集语音.....                                       | (130)        |

| 6.3 时域滤波.....                                       | (135)        |

| 6.4 频域滤波.....                                       | (141)        |

| 6.5 语音输出.....                                       | (143)        |

| 6.6 双音多频的识别与生成.....                                 | (144)        |

| 6.6.1 双音多频的识别 .....                                 | (144)        |

| 6.6.2 双音多频生成 .....                                  | (146)        |

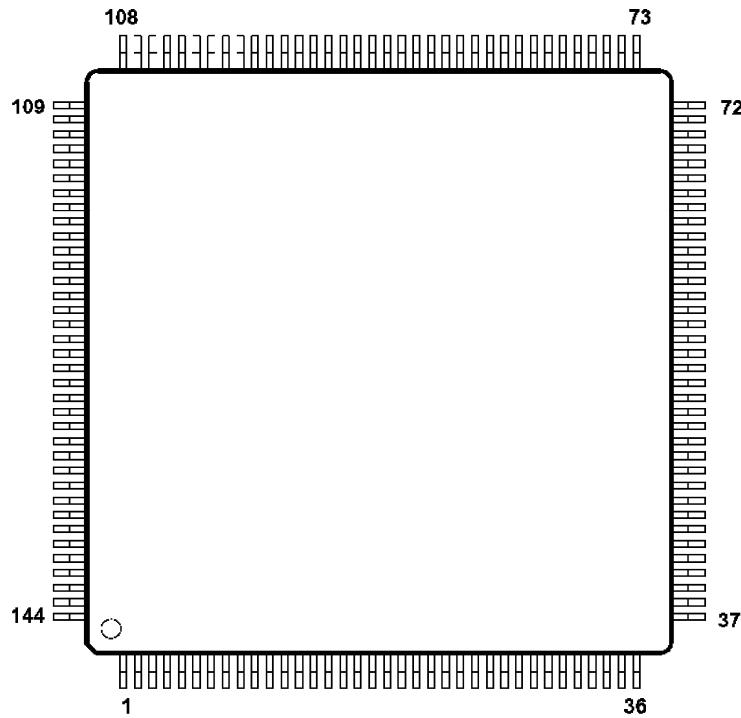

| <b>附录 A TMS320VC5509A 芯片引脚图及定义.....</b>             | <b>(150)</b> |

| <b>附录 B 指令集 .....</b>                               | <b>(157)</b> |

| <b>附录 C 代码示例 .....</b>                              | <b>(177)</b> |

| <b>参考文献 .....</b>                                   | <b>(202)</b> |

# 第1章 概论

## 1.1 DSP (数字信号处理器)

DSP 的含义主要有两种，第一，作为数字信号处理 (Digital Signal Processing) 学科，其是面向电子信息学生开放的，以数字运算方法实现信号变换、滤波、检测、估值、调制解调以及快速算法等处理的专业基础课；第二，作为数字信号处理器 (Digital Signal Processor)，其是针对数字信号或数字系统，由大规模或超大规模集成电路芯片组成的用来完成数字信号处理任务 (检测、滤波、参数估计等) 的处理器。

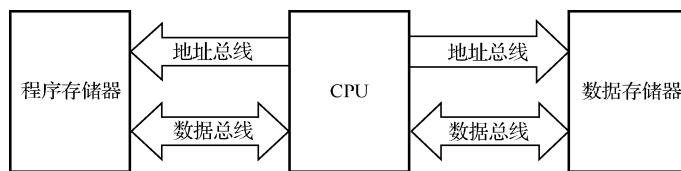

DSP (数字信号处理器) 是专门为了数字信号处理应用而设计的高速芯片，解决了原来处理器结构复杂、单片微机速度达不到实时系统要求的问题。DSP 不同于早期微处理器的冯·诺依曼结构，其内部采用了程序存储器和数据存储器分开的哈佛 (Harvard) 结构，如图 1.1 所示。这种结构允许 DSP 同时取指令 (来自程序存储器) 和取操作数 (来自数据存储器)，而且还允许在程序存储器和数据存储器之间传送数据。DSP 芯片工作于流水线模式，而且程序执行中的各种阶段是重叠执行的，即在执行本条指令的同时，还依次完成了后面三条指令的取操作数、译码和取指令的任务，将指令周期降到最小值。从某种意义上讲，DSP 芯片通过使用更多的资源换取了高速数据处理的实时性要求。

图 1.1 DSP 的哈佛结构

基于 DSP 的信号处理系统，由于 DSP 芯片具有可编程性，而且编程主要为 C 语言环境，开发相对容易。这种系统的信号处理速度快、处理能力强、具有很好的实时性能。随着 DSP 信号处理能力的不断提高，DSP 已成为数字信号处理系统中最为重要的信号处理器件之一。

## 1.2 DSP 芯片发展

世界上第一个 DSP 芯片是 1978 年 AMI 公司发布的 S2811。1979 年美国 Intel 公司发布的商用可编程器件 2920 是 DSP 芯片的一个重要里程碑。这两种芯片内部都没有现代 DSP 芯片必须有的单周期乘法器。1980 年日本 NEC 公司的 μD7720 是第一个具有乘法器的商用 DSP 芯片。1982 年日本 Hitachi 公司推出了第一款浮点 DSP 芯片。

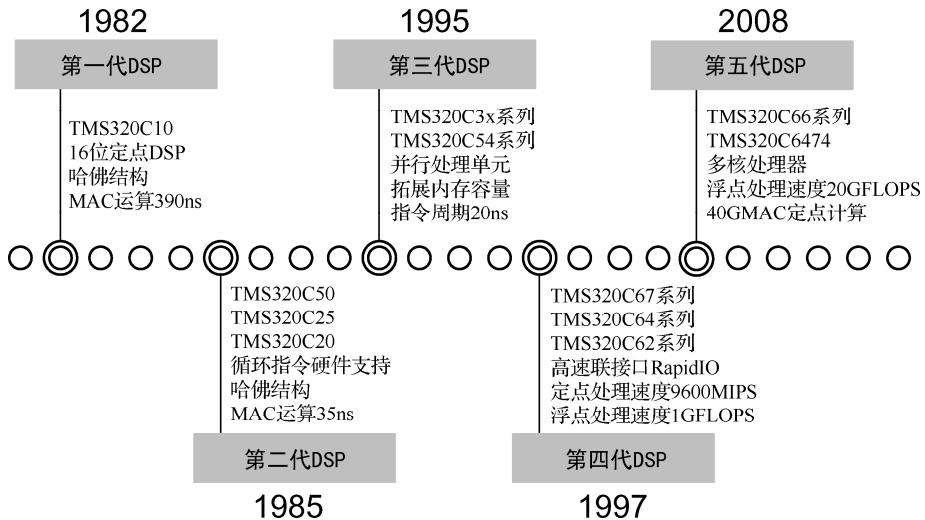

在 DSP 设计上最为成功的 DSP 芯片制造商——美国德州仪器 (TI) 公司，1982 年推出

了第一款数字信号处理器 TMS32010, 加上后续推出的 TMS32011 以及 TMS320C10 等处理器, 形成了 DSP 第一代系列产品; 此后, TI 公司又陆续推出了第二代、第三代等 DSP 系列产品, 并形成了 TMS320 系列 DSP。由于 TMS320 系列 DSP 芯片具有价格低廉、简单易用、功能强大等特点, 所以逐渐成为目前最有影响、最为成功的 DSP 系列处理器。自 DSP 芯片出现开始, 它的发展大致经历了 5 个阶段, 形成了目前 DSP 系列的五代产品。

### 1. 第一代 DSP

1982 年, TI 公司推出的 TMS320C10 是第一代 DSP 代表, 它是 16 位定点 DSP, 首次采用哈佛结构, 它完成乘累加运算的时间为 390ns, 处理速度较慢。

### 2. 第二代 DSP

1985 年, TI 公司推出的 TMS320C20 芯片是早期的第二代 DSP, 它具备单指令循环的硬件支持, 一次乘加运算时间为 200ns。随后 TI 公司又推出了 TMS320C25/C26/C28, 并在 TMS320C25 的基础上开发了 TMS320C50 芯片, 它采用了高级哈佛结构, 增加了外围电路及更多的片上存储器, 运算速度达到 35ns, 是较高性能的第二代处理器。

### 3. 第三代 DSP

1995 年, 出现了第三代定点 DSP 产品, 如 TI 公司的 TMS320C5402, TMS320C5416, TMS320C5420 等。这些产品改进了内部结构, 增加了并行处理单元, 扩展了内部存储器容量, 提高了处理速度, 指令周期大约为 20ns。同期出现了功能更强的浮点 DSP, 如 TI 公司的 TMS320C3x 系列 DSP, 增加了 32 位浮点处理器。

### 4. 第四代 DSP

1997 年初, TI 公司推出的并行处理 TMS320C6000 系列处理器是性能更高的第四代处理器, 其包含 16 位定点系列 TMS320C62xx 处理器、32 位定点系列 TMS320C64xx 处理器以及浮点系列 TMS320C67xx 处理器, 其中定点 C64xx 系列处理器的处理速度可以达到 9600MIPS (Million Instructions Per Second, 每秒钟执行的百万指令数), 浮点 C67xx 系列可达 1GFLOPS (Giga Floating-point Operations Per Second, 每秒钟执行的 10 亿次的浮点运算数)。

采用并行多处理芯片组成 DSP 阵列, 可获得更高的处理性能。但需要 DSP 提供足够高速方便的互联接口。TI 公司将 RapidIO 技术引入 TMS320C6000 系列处理器, 期望在并行多片 DSP 市场上争取更高的市场份额。

### 5. 第五代 DSP

真正意义上 DSP 性能的飞跃是多核高性能 DSP 芯片的出现, 即 2008 年 TI 的 TMS320C6474 多核处理器面世, 随后 TI 还推出了性能更高的 TMS320C66xx 系列多核处理器。多核 DSP 的出现解决了并行多 DSP 阵列芯片之间数据交换、系统功耗等问题, 是未来高性能 DSP 的发展方向。

图 1.2 以 TI 公司为例概述了 DSP 的发展和演变过程。

图 1.2 DSP 的发展和演变过程

### 1.3 DSP 分类与应用

不同应用场合对 DSP 的要求不尽相同,因此出现了 DSP 发展的多样化。依据处理数据类型, DSP 可分为定点处理器和浮点处理器; 依据处理性能要求不同, DSP 可分为低端处理器和高端处理器; 依据应用场合不同, DSP 可分为控制类处理器、计算类处理器、多功能协同类处理器, 等等。

各大 DSP 生产厂商的系列产品占据 DSP 应用的各个方面。以 TI 公司为例, 自 1982 年以来为了适应不同领域的应用已经形成了 TMS320C2000 系列、TMS320C3000 系列、TMS320C5000 系列以及 TMS320C6000 系列产品。

TMS320C2000 系列是面向电机控制、存储等数控系统的定点 DSP 芯片, 其具体包含 C20x, C24x 以及 C28x 三个系列。其中 C20x 与 C24x 为 16 位定点 DSP, 运算速度为 20MIPS。C20x 主要用在电话、数字相机和售货机当中, C24x 主要用在数字电机控制、空调、电力控制系统当中。C28x 作为第一颗针对控制进行优化的 DSP, 主要应用在工业设计方面。除了定点 DSP, 该系列还包括拥有 32 位浮点处理器的浮点 DSP, 其中应用最为广泛的是 TMS320F2407 及其后续产品 TMS320F2812。

TMS320C3000 系列是面向计算的浮点处理 DSP 芯片，配套有 32 位浮点处理器，包含 C30x、C31x、C32x 以及 C33x 四个系列。浮点处理速度可达 50MFLOPS，定点处理速度可达 25MIPS。其中 TMS320VC33 型号在通信、手机、MODEM 以及 DVD 等方面得到了广泛应用。

TMS320C5000 系列是面向网络应用的低功耗定点 DSP 芯片，主要包含 C54x 以及 C55x 两个系列。其处理速度从 80MIPS 到 400MIPS 不等，在芯片内部增加了并行处理单元以及专门的功耗控制单元。C54x 系列为 16 位定点 DSP，处理速度从 80MIPS 到 200MIPS，其中的 TMS320C5402 等应用广泛。C55x 系列与 C54x 系列相比处理速度更快，功耗更低，每个 MIPS 只需消耗 0.05mW，并且提供了 C54x 系列没有的 EMIF 外部存储器接口，主要应用在语音编

解码、调制解调、图像处理和语音合成等方面。

TMS320C6000 系列是面向计算的 VLIM 结构的高性能 DSP 芯片,其中的 TMS320C6201、TMS320C6701、TMS320C64xx 等应用广泛。C6000 系列 DSP 分为浮点和定点两类, C62xx 系列为 32 位定点 DSP, 处理速度为 1200MIPS 到 2000MIPS, 主要应用在无线基站、ADSL、网络系统与交换机等方面。C64xx 系列与 C62xx 系列相比处理性能更高, 可以达到 9600MIPS, 主要应用于 XDSL、成像处理以及高性能数据处理等方面。C67xx 系列为 32 位浮点 DSP, 处理速度为 1GFLOPS, 主要用于基站数字波束形成、医学图像处理以及语音识别等方面。

值得一提的是,在 TMS320C6000 系列中还包含了当今处理性能最高的多核处理器 C66xx 系列, 代表了 DSP 性能的飞跃。其中以 TMS320C6678 为代表, 该处理器包含 8 个核, 8 核最高处理速度可达 160GFLOPS 或者 320GMACS, 并同时集成有 RapidIO、PCIe、HyperLink 以及 SGMII 等接口。由于其拥有极高的运算, 所以在视频图像处理以及雷达数据处理等数据量大、实时性强的方面有着广泛的应用前景。

此外, TI 公司为了进入 3G 以及 4G 市场还专门开发了融合 DSP 和 ARM 架构的 OMAP 系列, 以适应无线终端多媒体处理的要求。OMAP 系列的发展已经从 OMAP1 发展到 OMAP5, 各代产品在智能手机、多媒体平台以及其他移动终端产品上得到了广泛的应用。

除了上述系列的 DSP 处理器外, TI 公司还推出过 TMS320C4000 系列及 TMS320C8000 系列处理器, 但是由于市场原因并没有得到广泛的应用, 所以上述两个系列的处理器也逐渐淡出市场。

在 TI 公司众多系列中, TMS320C5000 系列是目前中端市场上最通用、最流行的 DSP 处理器。相比于 C2000 系列及 C3000 系列, C5000 系列的处理速度有了显著提高, 并且接口丰富便于扩展; 相比于 C6000 系列及多核处理器, C5000 系列价格便宜且有着 C6000 系列难以比拟的低功耗优势。C5000 系列以其高性价比、实用节能的特点依然活跃在当今的 DSP 市场之中。

## 1.4 TMS320C5000 系列 DSP 概述

TMS320C5000 系列芯片是 TI 公司推出的高性能、低功耗、低成本的 16 位定点 DSP 处理器, 广泛应用于无线通信系统设备和远程通信等实时嵌入系统, 迄今为止已经发布了三代产品 TMS320C5x、TMS320C54x 和 TMS320C55x, 其中目前主推 TMS320C54x 和 TMS320C55x 两类系列芯片。TMS320C55x 是在 TMS320C54x 的基础上发展而来的, 其源代码也与 C54x 的兼容。300MHz 的 C55x 和 120MHz 的 C54x 相比, C55x 达到了 C54x 的 2 倍的周期效率, 性能提升了 5 倍, 并且功耗只有 C54x 的 1/6, 将低功耗提到一个新水平。C55x 在结构上做了很大的拓展, 在指令集上有很大的提高。C55x 的内核电压降到了 1.6V, 而功耗降到了 0.05mW/MIPS, 其独特的节能技术使 C55x 中未使用部分非工作期间内关闭, 各部分的开和关可以自行处理以便不同应用的功耗优化。C55x 因其优异的性能和极低的功耗在许多便携式产品中广泛应用, 成为通信和个人消费领域具有相当竞争力的主流 DSP 产品。

### 1.4.1 TMS320C54x 系列 DSP

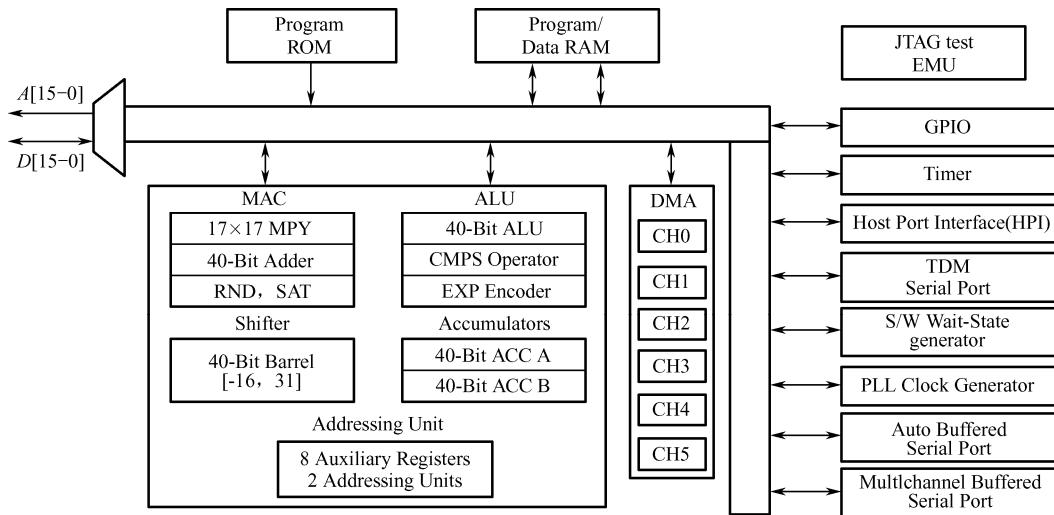

TMS320C54x 是继早期 TMS320C5x 系列发展起来的低功耗、高性能的 16 位定点 DSP，高度的集成化使其能够适应实时嵌入式应用的需要。C54x 采用改进的哈佛结构（1 组程序存储器总线，3 组数据存储器总线，4 组地址总线），独立的程序和数据总线，提供了高度的并行操作，允许同时访问程序存储器和数据存储器使处理器的性能大大提高。C54x 总体结构是由具有专用硬件逻辑的 CPU，片内存储器，片内外设以及专用的指令集所构成。C54x 系列中成员型号众多，但是不同型号芯片的体系结构基本相同，具有相同的 CPU 内核，差别主要在于存储器和外围电路配置情况有所不同。图 1.3 给出了 C54x 内部结构框图。

图 1.3 C54x 内部结构框图

按照 C54x 的功能架构和处理流程可以将其内部功能分为 4 大模块：

- (1) CPU，包括算术逻辑运算单元 (ALU)、 $17 \times 17$  位的并行乘法器、累加器、移位寄存器、各种专门用途的寄存器、双地址生成器及多条内部总线。

- (2) 存储器系统，包括片内的程序/数据 ROM、片内单寻址 RAM 和双寻址 RAM、外接存储器接口。

- (3) 片内外设与专用硬件电路，包括片内的定时器、各种类型的串口、并行接口、片内的锁相环 (PLL) 时钟发生器及各种控制电路。

- (4) 指令系统，包括 32 位运算指令、多操作读取指令、并行存储和并行加载的算术指令、单周期重复和块指令重复。

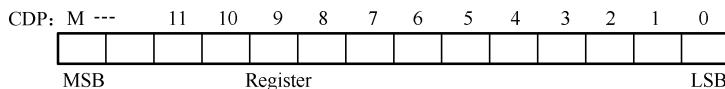

### 1.4.2 TMS320C55x 系列 DSP

TMS320C55x 是 TMS320C5000 系列的新一代产品，C55x 处理速度明显提高，功耗明显降低。与 C54x 相比，C55x 在结构上复杂得多，C55x 具有 2 个 MAC 单元，4 个 40 位累加器，能够在单周期内作 2 个  $17 \times 17$  位的乘法运算。C55x 具有 12 条独立总线，即：1 条程序读总线，1 条程序地址总线，3 条数据读总线，2 条数据写总线，5 条数据地址总线，其指令单元

每次可从存储器中读取 32 位程序代码 (C54x 只能读取 16 位)。C55x 含有指令高速缓冲器 (cache)，以减少对外部存储器的访问，改善数据吞吐率和省电。C55x 采用 1~6 字节的可变字节宽度指令 (C54x 的指令长度为固定的 16 位)，以提高代码密度。

C55x 的指令集是 C54x 指令集的超集，以便与扩展了的总线结构和新增加的硬件执行单元相适应。C55x 像 C54x 一样，保持了代码密度高的优势，以便降低系统成本。C55x 的指令长度从 8~48 位可变，由此可控制代码的大小，比 C54x 降低 40%。减小控制代码的大小，也就意味着降低对存储器的要求，从而降低系统的成本。C55x DSP 是一款嵌入式低功耗、高性能处理器，它具有省电、实时性高的优点，同时外部接口丰富，能满足大多数嵌入式应用需要。C55x 的内部结构框图如图 1.4 所示。

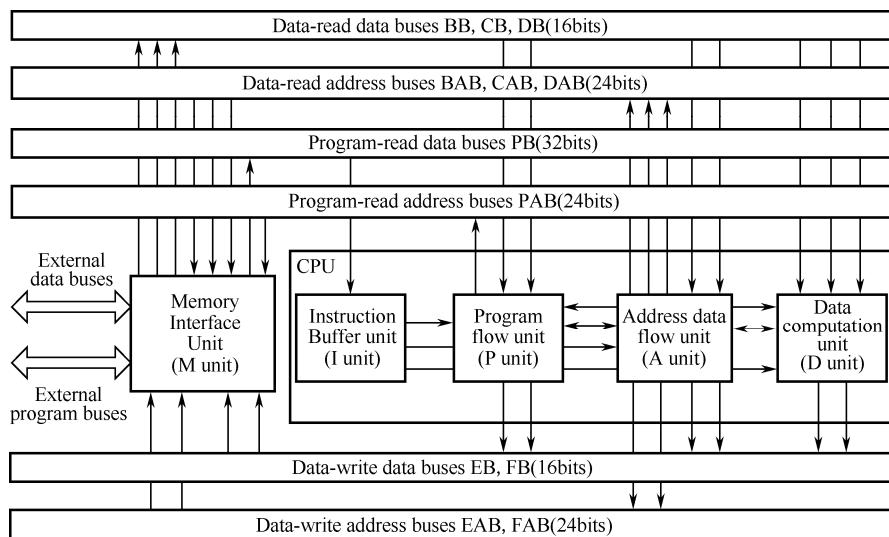

图 1.4 C55x 内部结构框图

按照 C55x 的内部结构框图可将其内部硬件单元划分为 3 个部分：

(1) CPU，C55x 的 CPU 内核由 4 个功能单元组成，即指令缓冲单元 (I 单元)、程序流程单元 (P 单元)、地址流程单元 (A 单元) 和数据运算单元 (D 单元)。

(2) 存储器接口单元，存储器接口单元是一个内部数据流、指令流接口，管理来自所有 CPU、数据空间或 I/O 空间的数据和指令，负责 CPU 和数据空间以及 CPU 和 I/O 空间的数据传输。

(3) 内部总线结构，C55x 具有 12 条独立的总线，1 条 32 位的程序数据总线 (PB)、5 条 16 位的数据总线 (BB、CB、DB、EB、FB)，以及 6 条 24 位的程序地址总线和数据地址总线分别与 CPU 相连。这些总线可以通过存储器接口单元与外部程序总线和外部数据总线相连，实现 CPU 对外部存储器的访问。

### 1.4.3 C54x 与 C55x 的比较

C55x 是在 C54x 基础之上开发得到的，两者之间有很多的关联性，同时 C55x 在结构上做了一定程度的拓展。与 C54x 相比，C55x 增添了 MAC 单元、总线宽度、指令高速缓存器、可变指令长度等，在性能上提升较大。C55x 与 C54x 的具体比较如表 1.1 所示。

表 1.1 C55x 与 C54x 的比较

| 内 容          | C54x        | C55x                  |

|--------------|-------------|-----------------------|

| 乘法单元 (MAC)   | 1           | 2                     |

| 累加器 (ACC)    | 2           | 4                     |

| 数据读总线        | 2           | 3                     |

| 数据写总线        | 1           | 2                     |

| 程序读总线        | 1 (16 位)    | 1 (32 位)              |

| 地址总线         | 4           | 6                     |

| 指令字长         | 16 位        | 8/16/24/32/40/48      |

| 数据字长         | 16 位        | 16 位                  |

| 算术逻辑单元 (ALU) | 1 个 (40 位)  | 1 个 (40 位)、1 个 (16 位) |

| 辅助寄存器字长      | 2 字节 (16 位) | 3 字节 (24 位)           |

| 辅助寄存器        | 8           | 8                     |

| 存储空间         | 统一程序/数据存储空间 | 独立程序/数据存储空间           |

| 临时寄存器        | 0           | 4                     |

#### 1.4.4 TMS320C5000 系列 DSP 外设接口

C5000 系列 DSP 处理器提供了多种内部外设，对于所有的 C54x 和 C55x 系列的 DSP，尽管同一系列它们的 CPU 结构是相同的，但是连接 CPU 的片上外设一般并不相同。对于 C54x 系列的 DSP，其片上外设主要包括通用 I/O 引脚、主机接口 HPI、定时器、时钟发生器、软件可编程的等待状态发生器、直接存储器访问 (DMA) 控制器、标准同步串行口 (SP)、时分复用串行口 (TDM)、缓冲串行口 (BSP)、多通道缓冲串行口 ( McBSP)；对于 C55x 系列 DSP，还提供了外部存储器接口 (EMIF)、指令 cache、电源管理/idle 控制等接口。

### 1.5 TMS320C5000 系列芯片性能分析

#### 1.5.1 主要性能分析

芯片的性能是选择 DSP 进行系统设计时需要重点考虑的一个环节，只有选定了 DSP 芯片，才能进一步设计其外围电路及系统的其他电路，DSP 芯片的选择应该根据实际应用系统的需要来确定。而 DSP 考虑的性能因素主要包括以下几个方面：

(1) DSP 芯片的运算速度，包括指令周期时间 (DSP 主频的倒数)、MAC 时间、MIPS (每秒执行百万条指令)、MFLOPS (每秒执行百万次浮点操作)、FFT 执行时间等。

(2) DSP 芯片的运算精度，定点 DSP 芯片的字长通常为 16 位，浮点芯片的字长一般为 32 位，累加器为 40 位。

(3) DSP 芯片的硬件资源，同系列 DSP 芯片 (如 C54x 系列)，不同型号的芯片内部资源会有所不同，此外片内的 RAM、ROM 数量、总线接口、I/O 接口、外部可拓展的程序和数据空间等也会有所不同。

(4) DSP 芯片的功耗，在实际应用中，在不同的场合对于设备的功耗都有着特殊的要求，因此，功耗是一个需要特别注意的问题。

(5) 其他因素，选择 DSP 芯片还应考虑封装形式、价格、生命周期和质量标准、供货情况等。

## 1.5.2 C54x 系列芯片性能

表 1.2 提供了 C54x 系列 DSP 器件的性能比较。该表显示了每个芯片的片内 RAM 和 ROM、外围设备、指令周期、封装类型、引脚数等重要特性。

表 1.2 C54x 系列 DSP 器件的性能比较

| 器件<br>型号 | DSP<br>/MHz<br>(Max) | ROM<br>/KB | DARAM<br>/KB | SARAM<br>/KB | 外 设  |    |     |     |       |       |     | 封装                           |

|----------|----------------------|------------|--------------|--------------|------|----|-----|-----|-------|-------|-----|------------------------------|

|          |                      |            |              |              | UART | SP | BSP | TDM | McBSP | TIMER | HPI |                              |

| C541     | 40                   | 28         | 5            | 0            | 0    | 2  | 0   | 0   | 0     | 1     | 0   | 100P<br>TQFP                 |

| C542     | 40                   | 2          | 10           | 0            | 0    | 0  | 1   | 1   | 0     | 1     | 1   | 144P<br>TQFP                 |

| C545     | 40,<br>50            | 48         | 6            | 0            | 0    | 1  | 1   | 0   | 0     | 1     | 1   | 128P<br>TQFP                 |

| C546     | 40,<br>50            | 48         | 6            | 0            | 0    | 1  | 1   | 0   | 0     | 1     | 0   | 100P<br>TQFP                 |

| C548     | 50,<br>66,<br>80     | 2          | 16           | 16           | 0    | 0  | 2   | 1   | 0     | 1     | 1   | 144P<br>TQFP<br>/144P<br>BGA |

| C549     | 66,<br>80            | 16         | 16           | 16           | 0    | 0  | 2   | 1   | 0     | 1     | 1   | 144P<br>TQFP<br>/144P<br>BGA |

| C5401    | 50                   | 8          | 16           | 0            | 0    | 0  | 0   | 0   | 2     | 2     | 1   | 144P<br>BGA                  |

| C5402    | 80                   | 8          | 32           | 0            | 0    | 0  | 0   | 0   | 2     | 2     | 1   | 144P<br>LQFP<br>/144P<br>BGA |

| C5404    | 120                  | 128        | 32           | 0            | 1    | 0  | 0   | 0   | 3     | 2     | 1   | 144P<br>LQFP<br>/144P<br>BGA |

续表

| 器件<br>型号 | DSP<br>/MHz<br>(Max) | ROM<br>/KB | DARAM<br>/KB | SARAM<br>/KB | 外 设  |    |     |     |       |       |     | 封装                           |

|----------|----------------------|------------|--------------|--------------|------|----|-----|-----|-------|-------|-----|------------------------------|

|          |                      |            |              |              | UART | SP | BSP | TDM | McBSP | TIMER | HPI |                              |

| C5407    | 120                  | 256        | 80           | 0            | 1    | 0  | 0   | 0   | 3     | 2     | 1   | 144P<br>LQFP<br>/144P<br>BGA |

| C5409    | 120,<br>160          | 32         | 64           | 0            | 0    | 0  | 0   | 0   | 3     | 1     | 1   | 144P<br>TQFP<br>/144P<br>BGA |

| C5410    | 120,<br>160          | 32         | 16           | 112          | 0    | 0  | 0   | 0   | 3     | 1     | 1   | 144P<br>LQFP<br>/176P<br>BGA |

| C5416    | 120,<br>160          | 32         | 128          | 128          | 0    | 0  | 0   | 0   | 3     | 1     | 1   | 144P<br>LQFP<br>/144P<br>BGA |

| C5420    | 100                  | 0          | 64           | 336          | 0    | 0  | 0   | 0   | 6     | 2     | 1   | 144P<br>LQFP<br>/144P<br>BGA |

| C5441    | 133                  | 0          | 1280         | 0            | 0    | 0  | 0   | 0   | 12    | 4     | 1   | 176P<br>LQFP<br>/169P<br>BGA |

### 1.5.3 C55x 系列芯片性能

表 1.3 提供了 C55x 系列 DSP 器件的性能比较。该表显示了每个芯片的片内 RAM 和 ROM、外围设备、指令周期、封装类型、引脚数等重要特性。

表 1.3 C55x 系列 DSP 器件的性能比较

| 器件<br>型号 | DSP<br>/MHz<br>(Max) | ROM<br>/KB | DARAM<br>/KB | SARAM<br>/KB | 外 设 |     |                  |      |       |       |     | 封装          |

|----------|----------------------|------------|--------------|--------------|-----|-----|------------------|------|-------|-------|-----|-------------|

|          |                      |            |              |              | USB | SPI | I <sup>2</sup> C | UART | McBSP | TIMER | HPI |             |

| C5501    | 300                  | 32         | 32           | 16           | 0   | 0   | 1                | 1    | 2     | 4     | 1   | 201P<br>BGA |

| C5502    | 200,<br>300          | 32         | 64           | 16           | 0   | 0   | 1                | 1    | 3     | 4     | 1   | 201P<br>BGA |

续表

| 器件<br>型号 | DSP<br>/MHz<br>(Max) | ROM<br>/KB | DARAM<br>/KB | SARAM<br>/KB | 外设  |     |                  |      |       |       |     | 封装                           |

|----------|----------------------|------------|--------------|--------------|-----|-----|------------------|------|-------|-------|-----|------------------------------|

|          |                      |            |              |              | USB | SPI | I <sup>2</sup> C | UART | McBSP | TIMER | HPI |                              |

| C5503    | 108,<br>144,<br>200  | 64         | 64           | 0            | 0   | 0   | 1                | 0    | 3     | 2     | 1   | 179P<br>BGA                  |

| C5504    | 100,<br>120,<br>150  | 128        | 64           | 192          | 1   | 1   | 1                | 1    | 0     | 3     | 0   | 196P<br>BGA                  |

| C5505    | 100,<br>120,<br>150  | 128        | 64           | 256          | 1   | 1   | 1                | 1    | 0     | 3     | 0   | 196P<br>BGA                  |

| C5506    | 108                  | 0          | 64           | 64           | 1   | 0   | 1                | 0    | 3     | 2     | 0   | 179P<br>BGA                  |

| C5507    | 108,<br>144,<br>200  | 64         | 64           | 64           | 1   | 0   | 1                | 0    | 3     | 2     | 1   | 179P<br>BGA                  |

| C5509    | 144                  | 64         | 64           | 192          | 1   | 0   | 1                | 0    | 3     | 2     | 1   | 144P<br>LQFP<br>/179P<br>BGA |

| C5510    | 160,<br>200          | 32         | 64           | 256          | 0   | 0   | 0                | 0    | 3     | 2     | 1   | 240P<br>BGA                  |

| C5514    | 100,<br>120          | 128        | 64           | 192          | 1   | 1   | 1                | 1    | 0     | 3     | 0   | 196P<br>BGA                  |

| C5515    | 100,<br>120          | 128        | 64           | 256          | 1   | 1   | 1                | 1    | 0     | 3     | 0   | 196P<br>BGA                  |

| C5517    | 75,<br>200           | 128        | 64           | 256          | 1   | 1   | 1                | 1    | 1     | 3     | 1   | 196P<br>BGA                  |

| C5532    | 50,<br>100           | 128        | 64           | 256          | 0   | 1   | 1                | 1    | 0     | 3     | 0   | 144P<br>BGA                  |

| C5533    | 50,<br>100           | 128        | 64           | 256          | 1   | 1   | 1                | 1    | 0     | 3     | 0   | 144P<br>BGA                  |

| C5534    | 50,<br>100           | 128        | 64           | 256          | 1   | 1   | 1                | 1    | 0     | 3     | 0   | 144P<br>BGA                  |

| C5535    | 50,<br>100           | 128        | 64           | 256          | 1   | 1   | 1                | 1    | 0     | 3     | 0   | 144P<br>BGA                  |

| C5545    | 60,<br>100           | 128        | 64           | 256          | 1   | 1   | 1                | 1    | 0     | 3     | 0   | 118P<br>BGA                  |

## 1.6 TMS320C5000 系列 DSP 应用

由于其杰出的性能和优良的性能价格比, TI 的 16 位定点 TMS320C5000 系列 DSP 得到了广泛的应用, 尤其是在通信领域。主要应用包括:

- IP 电话机和 IP 电话网关;

- 数字式助听器;

- 便携式声音/数据/视频产品;

- 调制解调器;

- 手机和移动电话基站, PDA, GPS;

- 传真/语音服务器;

- 数字无线电;

- SOHO (小型办公室和家庭办公室) 的语音和数据系统。

下面举例说明 C54x 和 C55x 在手机中的应用。

20 世纪 90 年代, 全世界的移动电话逐步完成了从模拟到数字式的过渡, 即人们所说的从第一代 (1G) 到第二代 (2G) 的过渡, 并在很短的时间内, 从 2G 向 2.5G 和 3G 发展。

几乎所有 2G 手机采用的基带体系结构, 都是以两个可编程处理器为基础的, 一个是 DSP 处理器, 另一个是 MCU 处理器。在时分多址 (TDMA) 模式中, DSP 芯片负责实现数据流的调制/解调、纠错编码、加密/解密、语音数据的压缩/解压缩; 在码分多址 (CDMA) 模式中, DSP 芯片负责实现符号级功能, 如前向纠错、加密、语音解压缩, 对扩频信号进行调制/解调及后续处理。MCU 负责支持手机的用户界面, 并处理通信协议栈中的上层协议, MCU 采用了 32 位 RISC 内核, ARM7TDM 就是此类 MCU 的典型代表, 早期的 2G 手机中, 这些功能由 C54x 实现, 工作频率约 40MHz; 在 2.5G 手机中, 这些功能由 C55x 实现, 工作频率在 100MHz 以上。3G 手机将实时通信功能与用户交互式应用分开, 实现多媒体通信。开放式多媒体应用平台 (OMAP) 包含多个 DSP 和 MCU 芯片, 应用环境是动态的, 可不断将新的应用软件下载到 DSP 和 MCU 内。

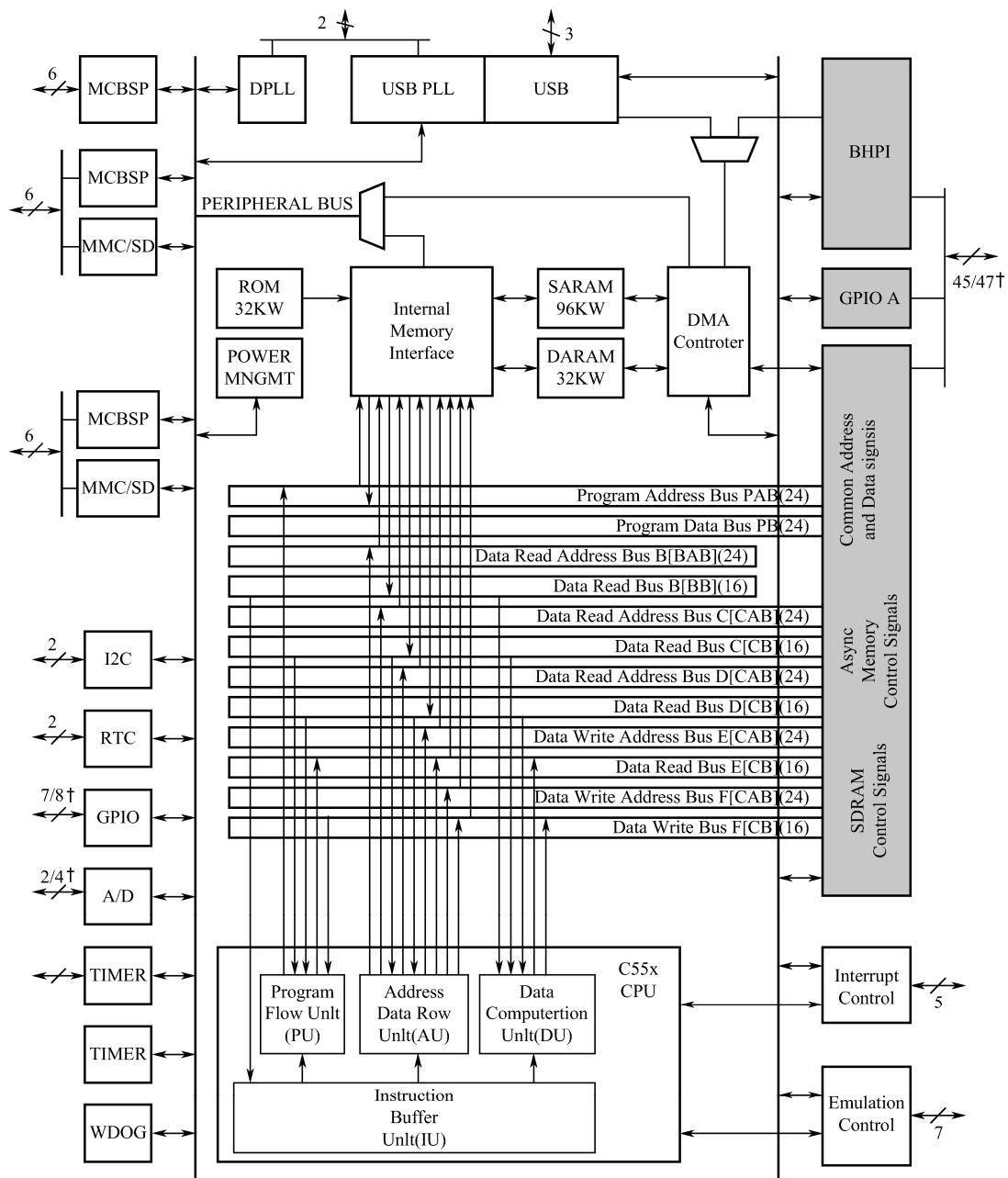

TMS320VC5509A 是 C55x 系列中的新型低功耗高性能定点型 DSP 芯片, 它包含 2 个  $17 \times 17$  乘法器、4 个 40 位 MAC、12 条独立总线, 片上存储器为  $128KB \times 16$ , 其中包含 64KB 的 DADAM 和 192KB 的 SARAM, 外设有 3 个 McBSP 接口和 6 个 DMA 通道, 处理速度可达 288MIPS。本书在后续章节主要以 TMS320C5000 系列的 TMS320VC5509A 为例, 介绍 DSP 音频信号处理的电路设计和应用开发。

# 第 2 章 CCS 集成开发环境

## 2.1 CCS 概述

CCS (Code Composer Studio) 是 TI 公司研发的一款具有环境配置、源文件编辑、程序调试、跟踪和分析等功能的集成开发环境，能够帮助用户在一个软件环境下完成编辑、编译、链接、调试和数据分析等工作。CCS 工作于 Windows 操作系统下，采用图形接口界面，提供环境配置、源文件编辑、程序调试、跟踪和分析等工具。

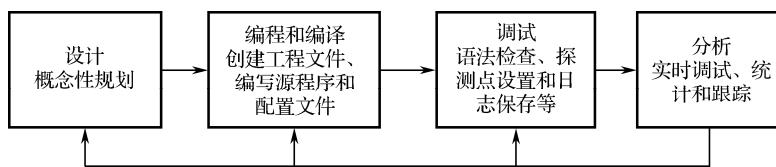

CCS 支持如图 2.1 所示开发周期的所有阶段。

图 2.1 CCS 支持功能

CCS 有两种工作模式：

- (1) 软件仿真器模式 (Simulator)，可以独立于 DSP 芯片，在 PC 上模拟 DSP 的指令集和工作机制，主要用于前期算法实现和调试。

- (2) 硬件仿真器模式 (Emulator)，可以实时运行在 DSP 芯片上，与硬件开发板相结合在线编程和调试应用程序。

CCS 的功能十分强大，它集成了代码的编辑、编译、链接和调试等诸多功能，而且支持 C/C++ 和汇编的混合编程，其主要功能如下：

- (1) 具有集成可视化代码编辑界面，用户可通过其界面直接编写 C、汇编、.cmd 文件等。

- (2) 含有集成代码生成工具，包括汇编器、优化 C 编译器和链接器等，并将代码的编辑、编译、链接和调试等众多功能集成到一个软件环境中。

- (3) 工程项目管理工具可对用户程序实行项目管理。在生成目标程序和程序库的过程中，建立不同程序的跟踪信息，通过跟踪信息对不同的程序进行分类管理。

- (4) 基本调试工具具有装入执行代码、查看寄存器、存储器、反汇编和变量窗口等功能，支持 C 源代码级调试。

- (5) 断点工具，能在调试程序的过程中，完成硬件断点、软件断点和条件断点的设置。

- (6) 探测点工具，可用于算法的仿真，数据的实时监视等。

- (7) 分析工具，包括仿真器和模拟器分析，可用于模拟和监视硬件的功能、评价代码执行的时间。

- (8) 数据的图形显示工具，可以将运算结果用图形显示，包括显示时域/频域波形、眼图、星座图、图像等，并能进行自动刷新。

- (9) 提供 GEL 工具。利用 GEL 扩展语言，用户可以编写自己的控制面板/菜单，设置 GEL

菜单选项，方便直观地修改变量，配置参数等。

- (10) 支持多 DSP 的调试。

- (11) 支持 RTDX 的技术，可在不中断目标系统运行的情况下，实现 DSP 与其他应用程序的数据交换。

- (12) 提供 DSP/BIOS 工具，增强对代码的实时分析能力。

## 2.2 集成代码生成工具

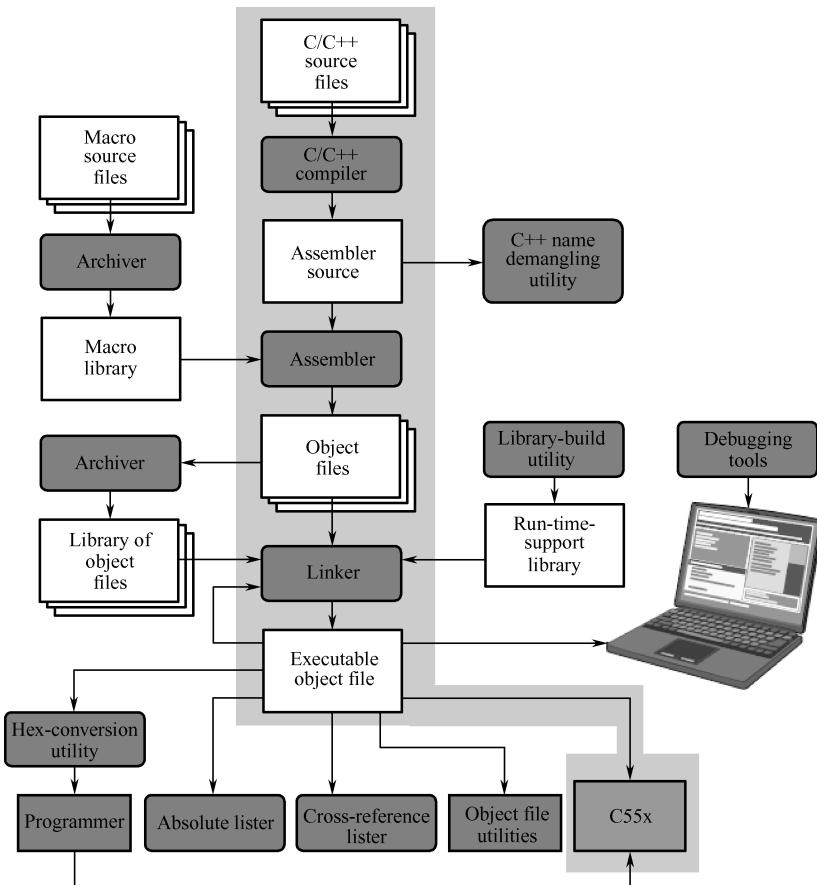

TMS320C55x 集成代码生成工具用来对 C 语言、汇编语言或混合语言编程的 DSP 源程序进行编译汇编，并链接成为可执行的 DSP 程序，主要包括汇编器、链接器、C/C++编译器和建库工具等。代码生成工具奠定了 CCS 所提供的开发环境的基础。图 2.2 是一个典型的软件开发流程图。

图 2.2 软件开发流程

图 2.2 描述的工具如下：

- (1) **C 编译器 (C compiler)**：产生汇编语言源代码。

- (2) **汇编器 (assembler)**：把汇编语言源文件翻译成机器语言目标文件，机器语言格式

为公用目标格式 (COFF)。

(3) **链接器 (linker):** 把多个目标文件组合成单个可执行目标模块。它一边创建可执行模块，一边完成重定位以及决定外部参考。链接器的输入是可重定位的目标文件和目标库文件。

(4) **归档器 (archiver):** 允许把一组文件收集到一个归档文件中。归档器也允许通过删除、替换、提取或添加文件来调整库。

(5) **助记符到代数汇编语言转换公用程序 (mnemonic-to-algebraic assembly translator utility):** 把含有助记符指令的汇编语言源文件转换成含有代数指令的汇编语言源文件。

(6) **建库程序 (library-build utility):** 建立满足要求的“运行支持库”。

(7) **运行支持库 (run-time-support libraries):** 它包括 C 编译器所支持的 ANSI 标准运行支持函数、编译器公用程序函数、浮点运算函数和 C 编译器支持的 I/O 函数。

(8) **十六进制转换公用程序 (hex conversion utility):** 它把 COFF 目标文件转换成 TI-Tagged、ASCII-hex、Intel、Motorola-S 或 Tektronix 等目标格式，可以把转换好的文件下载到 EPROM 编程器中。

(9) **交叉引用列表器 (cross-reference lister):** 它用目标文件产生参照列表文件，可显示符号及其定义，以及符号所在的源文件。

(10) **绝对列表器 (absolute lister):** 它输入目标文件，输出.abs 文件，通过汇编.abs 文件可产生含有绝对地址的列表文件。如果没有绝对列表器，这些操作将需要冗长乏味的手工操作才能完成。

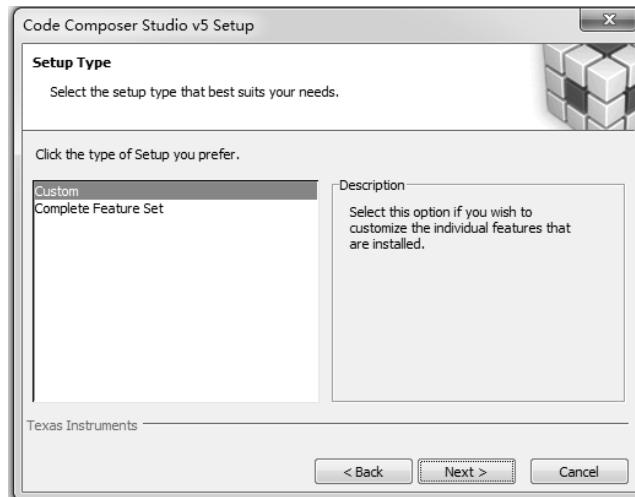

## 2.3 CCSv5.1 的安装

CCSv5.1 为 CCS 软件的新版本，其功能更强大、性能更稳定、可用性更高。

(1) 运行下载的安装程序 `ccs_setup_5.1.1.00031.exe`，当运行到如图 2.3 处时，选择“Custom”选项，进入手动选择安装通道。

图 2.3 安装过程 1

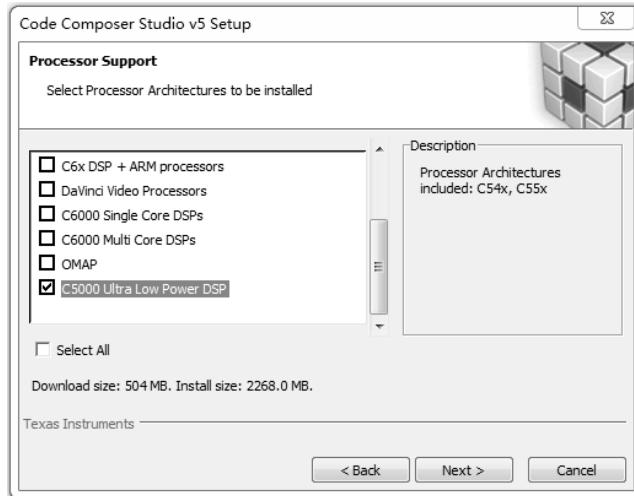

(2) 单击“Next”按钮得到如图 2.4 所示窗口, 根据自己的需要选择要安装的内容, CCSv5.1 支持 MSP430 系列 MCU、ARM、C2000、C5000、C6000 单/多核、DaVinci 等一系列处理器。如果只对 C5000 系列 DSP 进行编程, 则只选择 C5000 Ultra Low Power DSP 一项即可。

图 2.4 安装过程 2

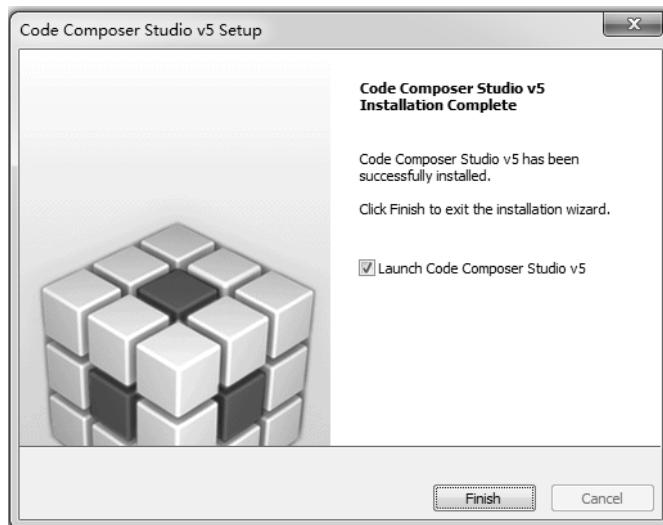

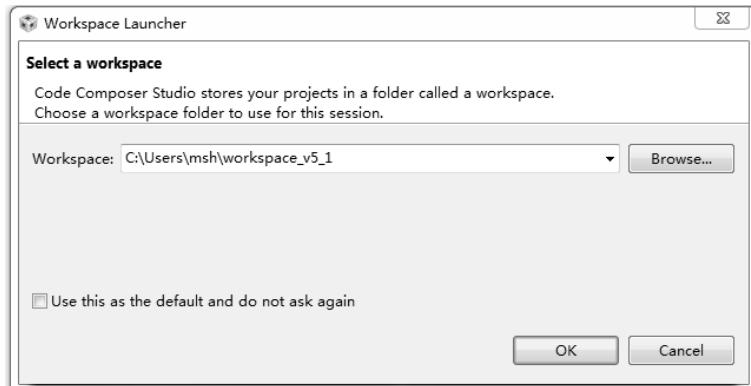

(3) 安装完成后结果如图 2.5 所示, 单击“Finish”按钮, 将运行 CCS, 弹出如图 2.6 所示窗口。打开“我的电脑”, 在某一磁盘下创建文件夹路径, 单击“Browse”按钮, 将工作区间链接到所建文件夹, 不勾选“Use this as the default and do not ask again”。

图 2.5 软件安装完成

图 2.6 Workspace 选择窗口

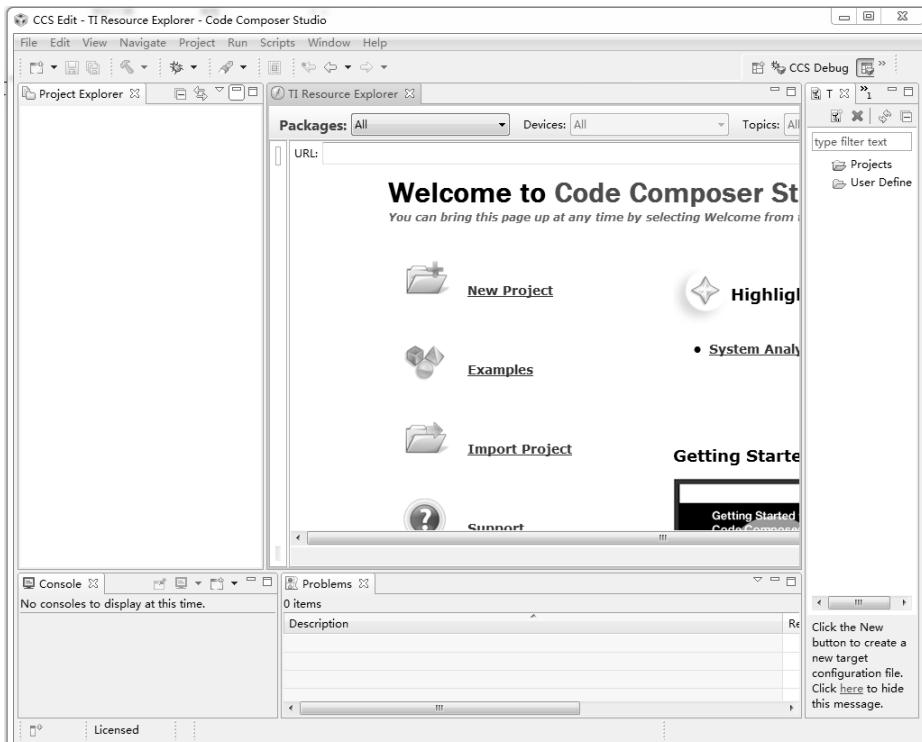

单击“OK”按钮，添加 license 文件，完成激活操作，完成后界面如图 2.7 所示。

图 2.7 CCSv5 软件开发集成环境界面

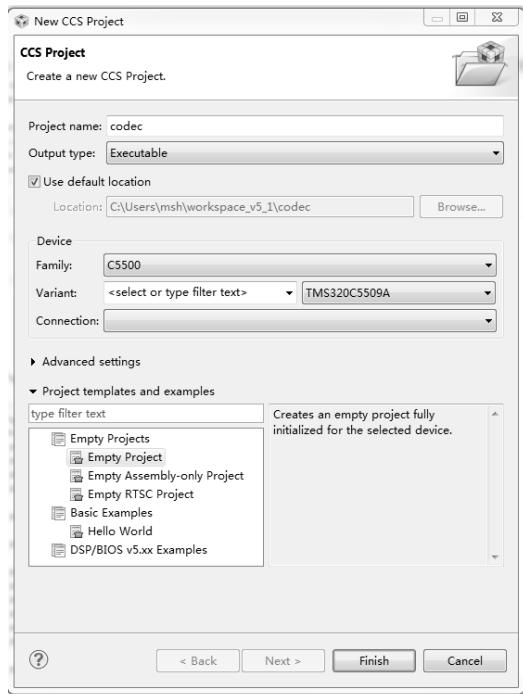

## 2.4 利用CCSv5.1 新建工程

### 1. 新建工程

新建工程步骤如下：

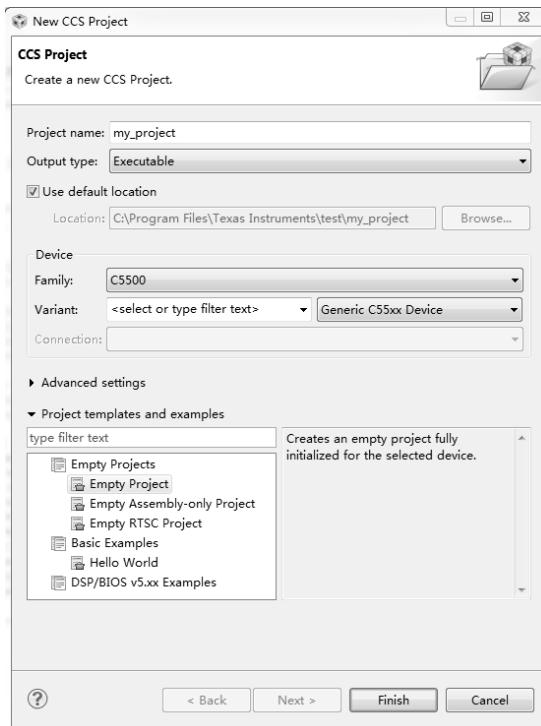

- (1) 打开 CCSv5.1 并确定工作区间，然后选择 File→New→CCS Project，弹出如图 2.8

所示对话框。

图 2.8 新建 CCS 工程对话框

- (2) 在 Project name 中输入新建工程的名称，在此输入 my\_project。

- (3) 在 Output type 中有两个选项：Executable 和 Static library，前者为构建一个完整的可执行程序，后者为静态库。在此保留 Executable。

- (4) 在 Device 部分选择器件的型号，在 Family 中选择 C5500；Variant 选择默认，芯片选择 Generic C55xx Device；Connection 保持默认。

- (5) 选择空工程，然后单击“Finish”按钮完成新工程的创建。

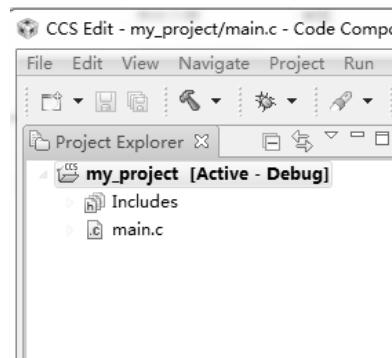

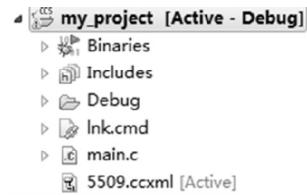

- (6) 创建的工程将显示在 Project Explorer 中，如图 2.9 所示。

图 2.9 初步创建的新工程

## 2. 新建或导入.h 或.c 文件

新建或导入已有.h 或.c 文件步骤如下。

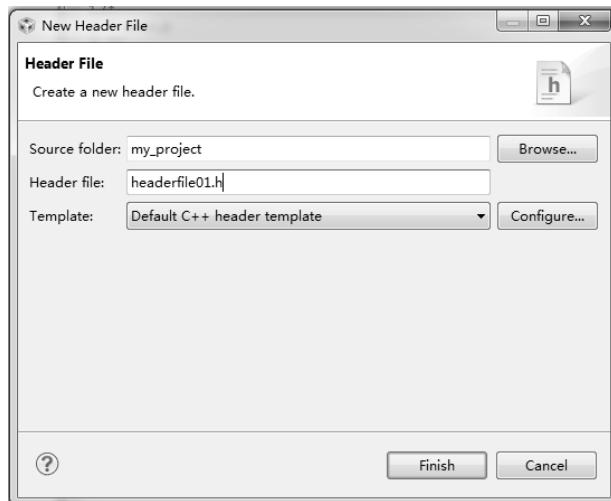

(1) 新建.h 文件: 在工程名上单击右键, 选择 New→Header File, 得到如图 2.10 所示对话框。

图 2.10 新建.h 文件对话框

在 Header file 中输入头文件的名称, 注意必须以.h 结尾, 在此输入 my01.h。

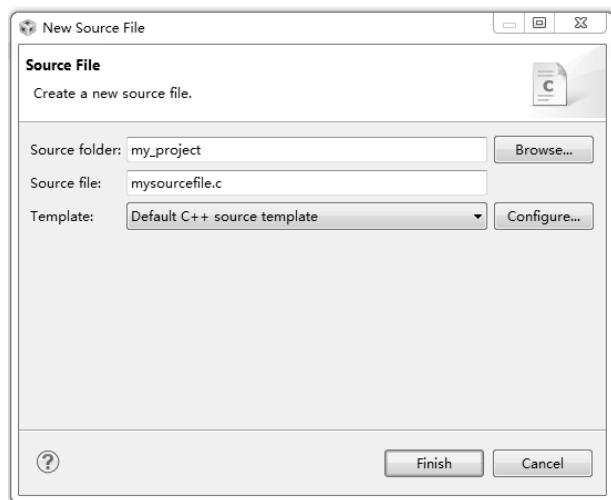

(2) 新建.c 文件: 在工程名上单击右键, 选择 New→Source File, 得到如图 2.11 所示对话框。

图 2.11 新建.c 文件对话框

在 Source file 中输入.c 文件的名称, 注意必须以.c 结尾, 在此输入 my01.c。

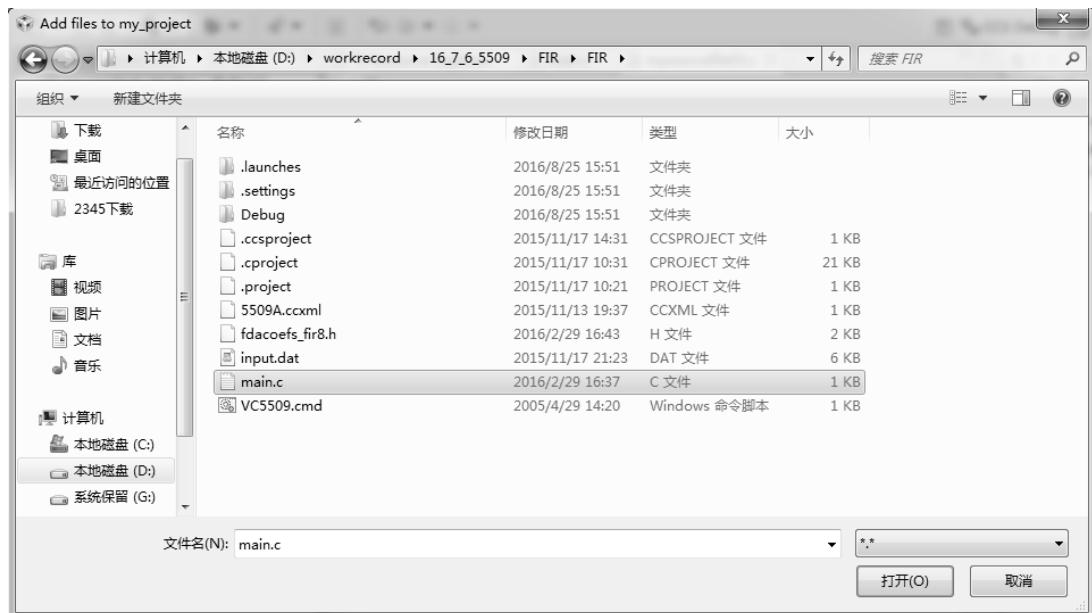

(3) 导入已有.h 或.c 文件: 在工程名上单击右键, 选择 Add Files, 得到如图 2.12 所示对话框。

图 2.12 导入已有文件对话框

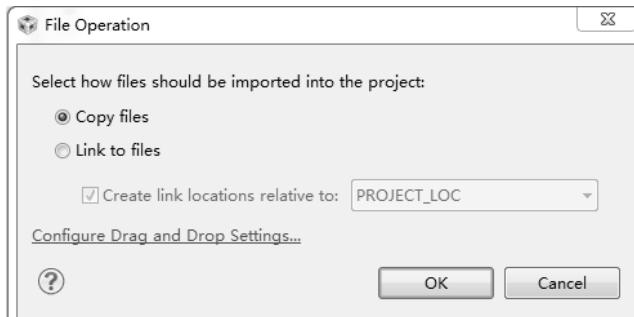

找到所需导入的文件位置，单击“打开”按钮，得到如图 2.13 所示对话框。

图 2.13 添加或连接现有文件

选择 Copy files，单击“OK”按钮，即可将已有文件导入到工程中。

## 2.5 利用 CCSv5.1 导入已有工程

利用 CCSv5.1 导入已有工程步骤如下：

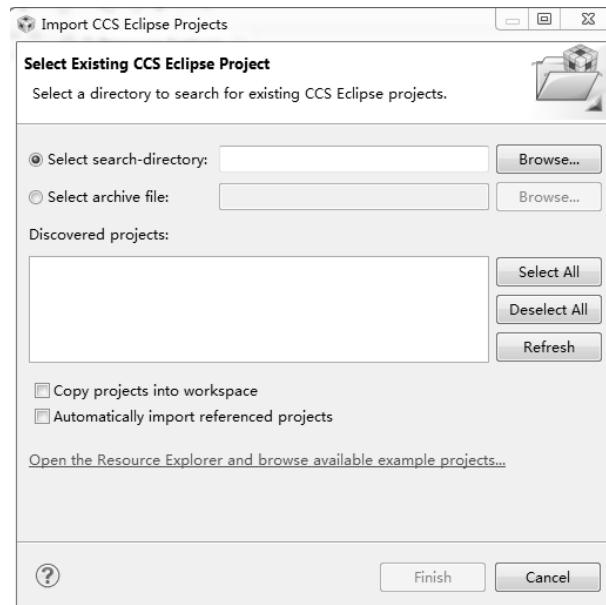

- (1) 打开 CCSv5.1 并确定工作区间，选择 File→Import，展开 Code Composer Studio，选择 Existing CCS/CCE Eclipse Projects。单击“Next”按钮，得到如图 2.14 所示对话框。

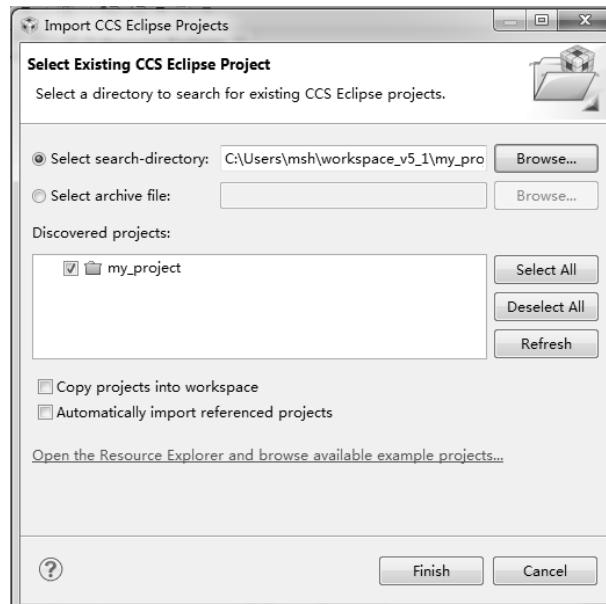

- (2) 单击“Browse”按钮，选择需导入的工程所在目录，如图 2.15 所示。

- (3) 单击“Finish”按钮，即可完成既有工程的导入。

图 2.14 选择导入工程目录

图 2.15 选择导入工程

## 2.6 利用 CCSv5.1 配置工程选项

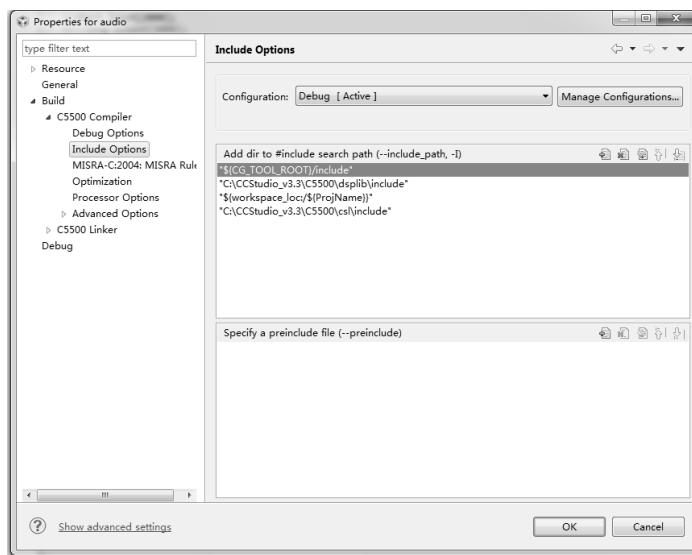

### 1. Include 路径的配置

Include 路径配置的操作方法如下：

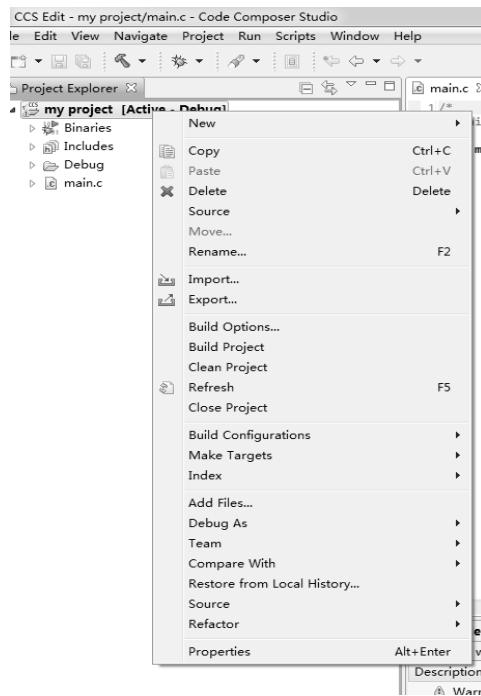

(1) 右击工程，在下拉菜单中选中“Properties”命令，如图 2.16 所示，弹出工程设置界面，如图 2.17 所示。

图 2.16 工程设置

图 2.17 工程设置界面

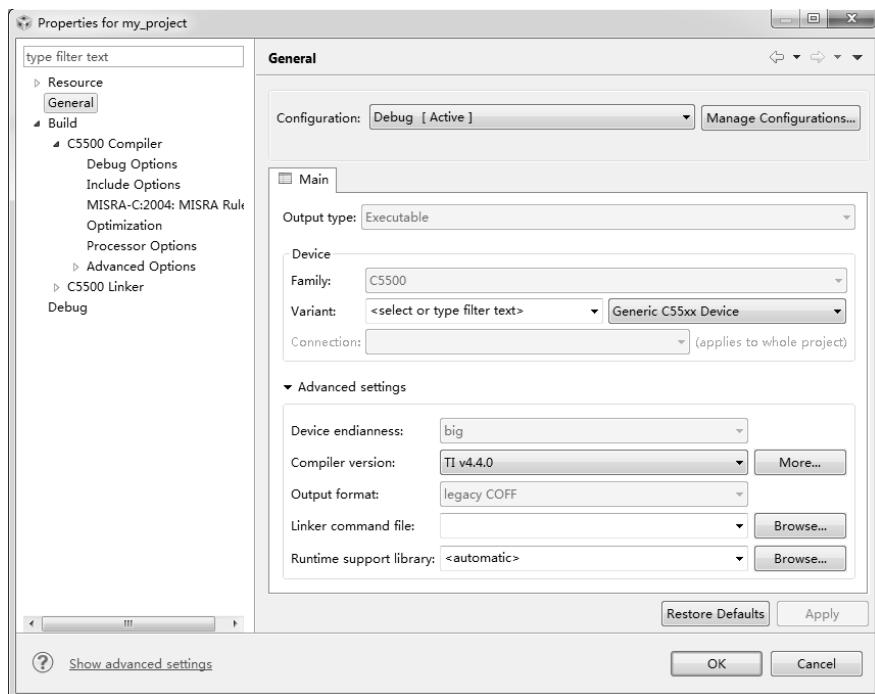

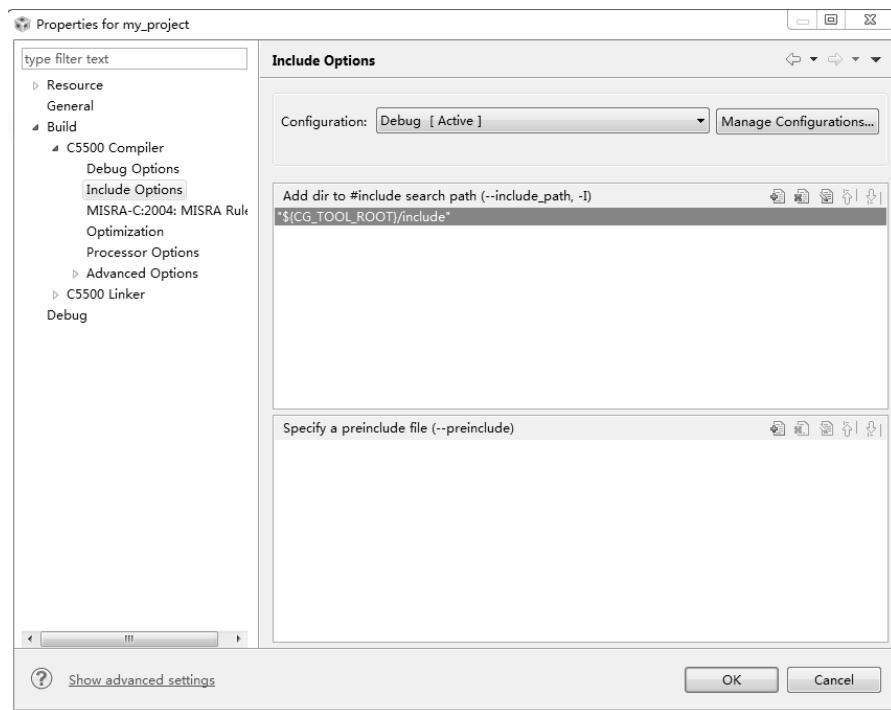

(2) 单击“Build”选项 C5500 Compiler 中的 Include Options，如图 2.18 所示。

图 2.18 添加编译包含路径

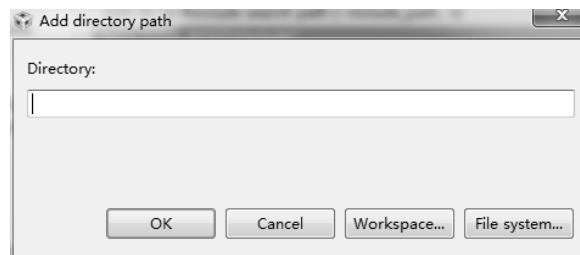

(3) 单击添加按钮 ，添加路径，如图 2.19 所示。

图 2.19 添加头文件路径

(4) 在路径栏添加了路径后，单击“OK”按钮确认设置，该路径下的.h 文件便可以直接进行引用。

## 2. Lib 路径的配置

在进行 DSPLib 和 CSL 等功能的配置时，往往还需要将库包含在工程中，其操作方法如下：

- (1) 右击工程，在下拉菜单中选择“Properties”按钮，弹出工程设置界面如图 2.17 所示。

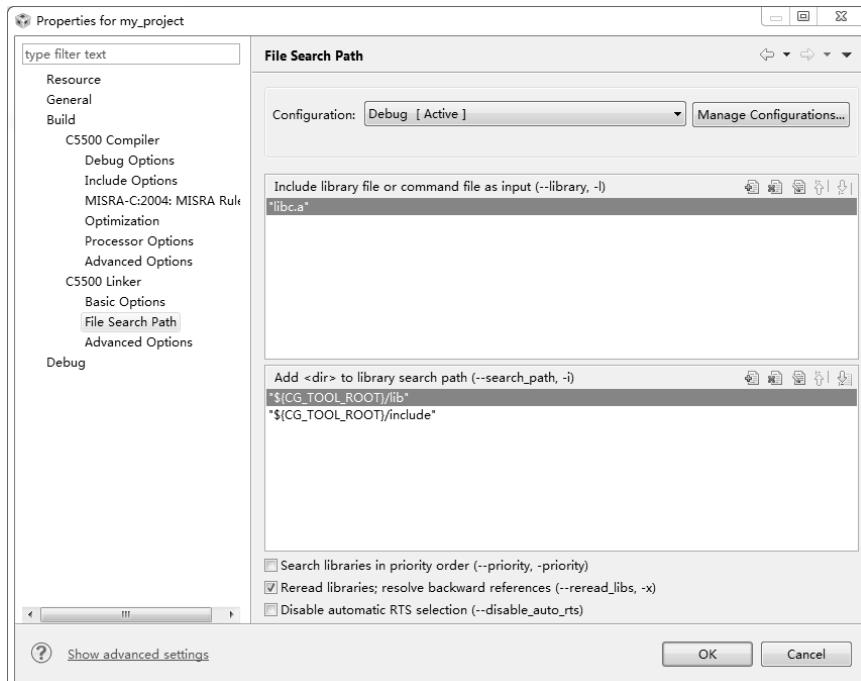

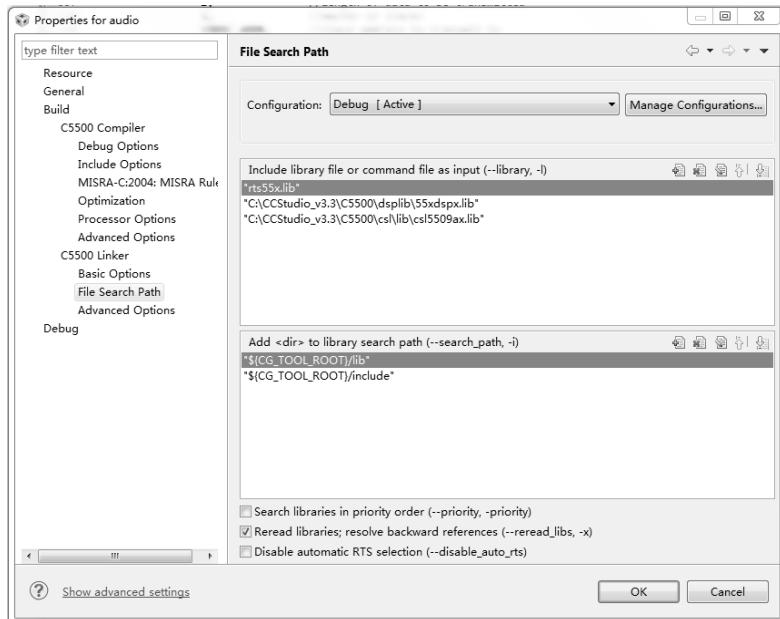

- (2) 单击“Build”选项 C5500 Linker 中的 File Search Path，如图 2.20 所示。

图 2.20 添加库文件

(3) 单击添加按钮 添加路径, 如图 2.21 所示。

图 2.21 添加库路径

(4) 添加库文件路径后, 单击“OK”按钮完成添加, 添加后可直接使用库中已有的函数。

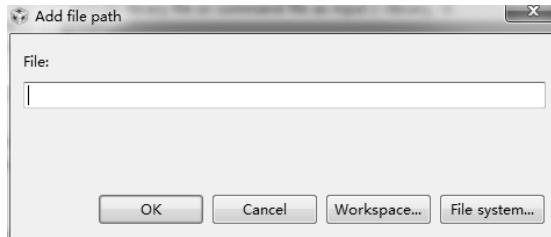

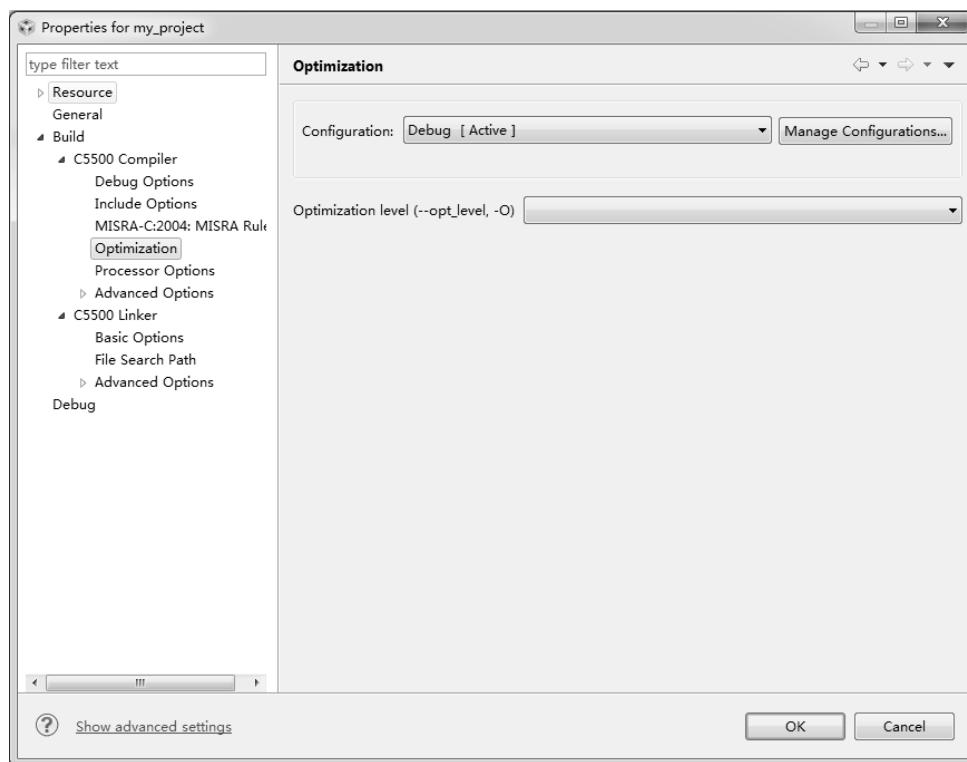

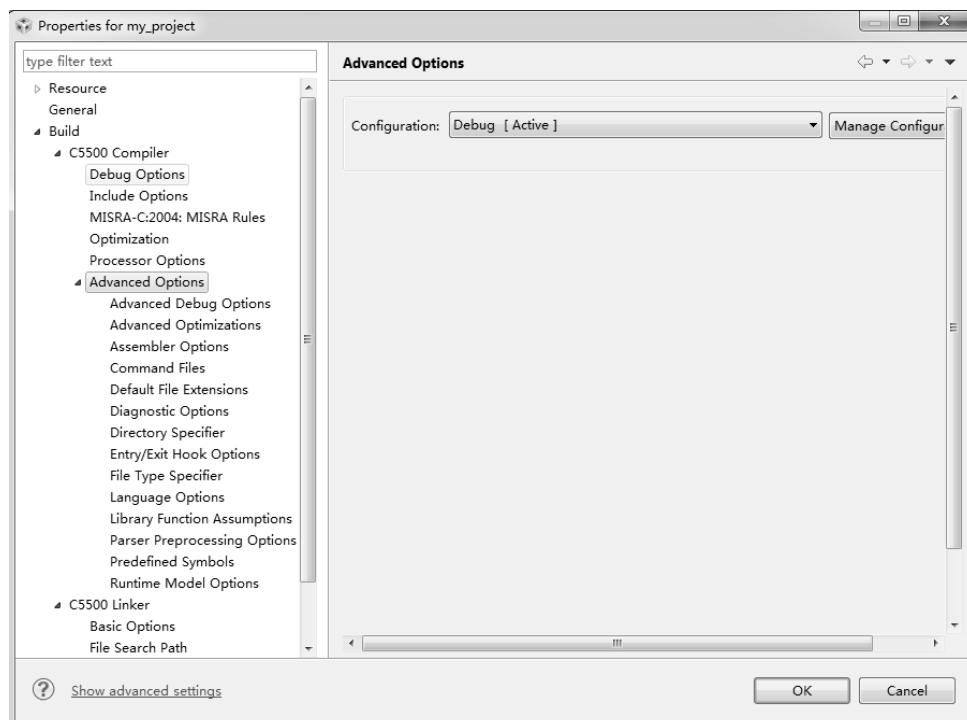

### 3. 程序优化选项的配置

程序优化选项配置的操作方法如下:

(1) 单击“工程”选项卡, 在下拉菜单中选择“Properties”按钮, 弹出工程设置界面如图 2.17 所示。

(2) 单击“Build”选项 C5500 Compiler 中的 Optimization 选项, 设置界面如图 2.22 所示。

(3) 设置 Optimization level 选项。Optimization level 可以从 0 到 3 实现优化等级的设置, 等级越高, 优化效果越明显。

(4) 如需更加详细的配置, 可在 Build 选项 C5500 Compiler 的 Optimization 选项中进行, 如图 2.23 所示。

图 2.22 优化设置界面

图 2.23 工程优化配置

CCS 工程配置菜单常用配置选项，除上述配置之外，还可以对更多编译及链接选项进行配置，在此不再赘述，读者有兴趣可以深入研究。

## 2.7 利用CCSv5.1 调试工程

### 1. 创建目标配置文件

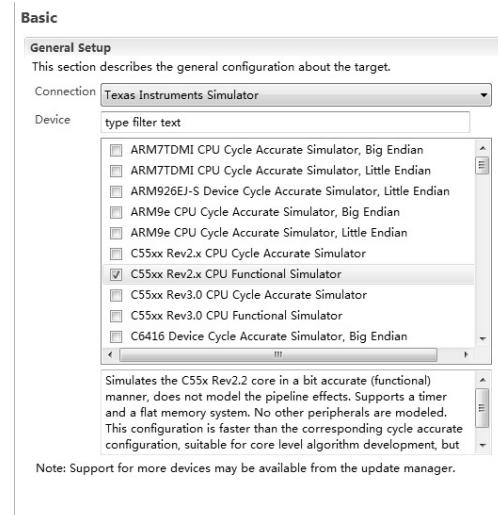

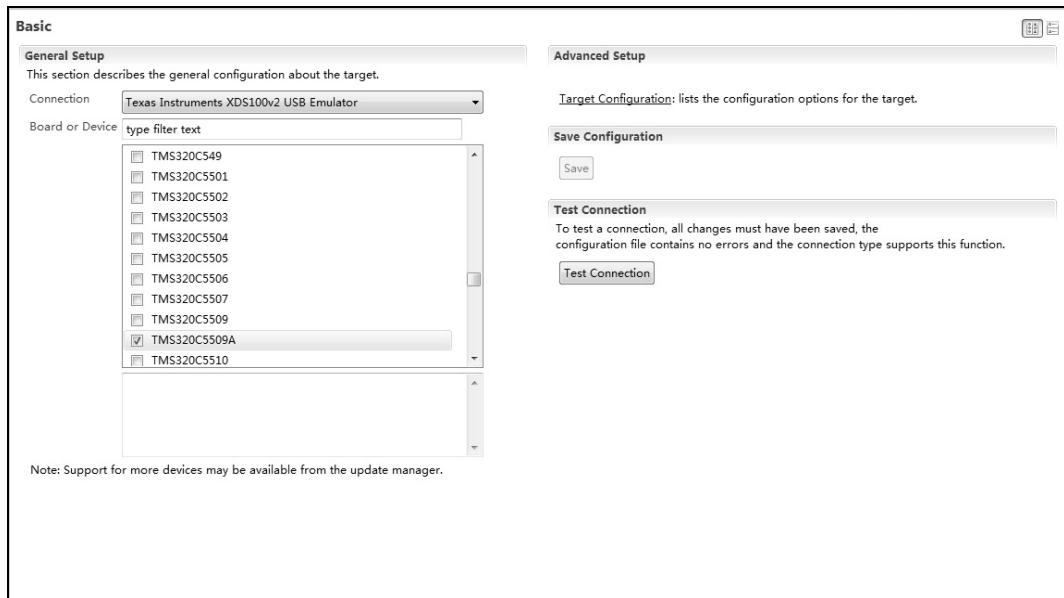

在开始调试之前，有必要确认目标配置文件是否已经创建并配置正确。首先导入工程，如图 2.24 所示，其中 ccxml 目标配置文件已经正确创建，即可以进行编译调试，无需重新创建。若目标配置文件未创建或创建错误，则需进行创建。为了介绍目标配置文件的创建过程，在此对 LAB1 的工程再次创建目标配置文件。

创建目标配置文件步骤如下：

(1) 右键单击项目名称，并选择 New→Target Configuration File。

(2) 在 File name 中输入后缀为.ccxml 的配置文件名，由于创建 TMS320VC5509A 开发板的目标配置文件，因此，将配置文件命名为 5509.ccxml。

(3) 单击“Finish”按钮，将打开目标配置编辑器，如图 2.25 所示。

图 2.24 工程浏览器

图 2.25 目标配置编辑器

### 2. 启动调试器

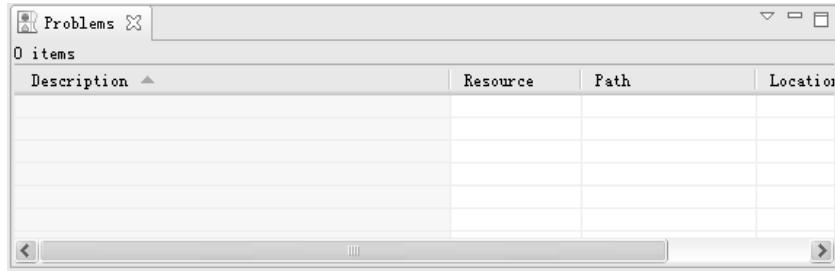

(1) 将工程进行编译通过：选择 Project→Build Project，编译目标工程。在第一次编译目标工程时，会在 Problems 选项卡中显示错误和警告。修改工程至没有错误，即提示如图 2.26 所示，就可以进行下载调试。

图 2.26 工程调试结果

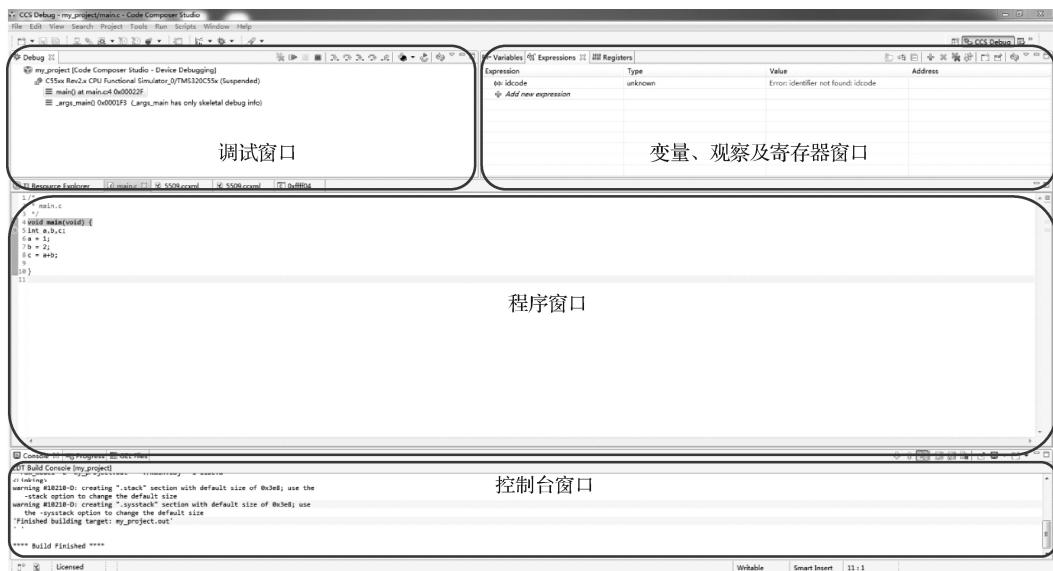

(2) 单击绿色的“Debug”按钮 进行下载调试，得到如图 2.27 所示界面。界面分为调试窗口，变量、观察及寄存器窗口，程序窗口以及控制台窗口。

图 2.27 调试窗口界面

(3) 单击运行图标 运行程序，观察显示的结果。在程序调试的过程中，可通过设置断点来调试程序：选择需要设置断点的位置，右击鼠标选择 Breakpoints→Breakpoint，断点设置成功后将显示图标 ，可以通过双击该图标来取消该断点。程序运行的过程中可以通过单步调试按钮 配合断点单步的调试程序，其中 (Step into) 为可进入子函数的单步执行， (Step over) 则直接越过子函数，将子函数作为一步运行，而 则是相对于前两者的汇编语言的单步调试，而 (Step return) 就是单步执行到子函数内时，用 step return 就可以执行完子函数余下部分，并返回上一层函数。此外还可以单击重新开始图标 定位到 main() 函数，单击复位按钮 复位。可通过中止按钮 返回编辑界面。

(4) 在程序调试的过程中，可以通过 CCSv5.1 查看变量、寄存器、汇编程序或者 Memory 等的信息，显示出程序运行的结果，以和预期的结果进行比较，从而顺利地调试程序。选择菜单 View→Variables 命令，可以查看变量的值，如图 2.28 所示。

| Name   | Type | Value | Location    |

|--------|------|-------|-------------|

| (v)= a | int  | 1     | 0x0332@DATA |

| (v)= b | int  | 2     | 0x0333@DATA |

| (v)= c | int  | 3     | 0x0334@DATA |

图 2.28 变量查看窗口

(5) 选择菜单 View→Registers 命令, 可以查看寄存器的值, 如图 2.29 所示。

| Name | Value      | Description   |

|------|------------|---------------|

| PC   | 0x00023E   | Core Register |

| XSP  | 0x000332   | Core Register |

| XSSP | 0x000526   | Core Register |

| RETA | 0x0001F3   | Core Register |

| CFC  | 0x00       | Core Register |

| AC0  | 0xFFFFFFFF | Core Register |

| AC1  | 0xFFFFFFFF | Core Register |

图 2.29 寄存器查看窗口

(6) 选择菜单 View→Expressions 命令, 可以得到观察窗口, 如图 2.30 所示。可以通过

添加观察变量, 或者在所需观察的变量上右击, 选择 Add Watch Expression 将其添加到观察窗口。

| Expression | Type | Value | Address |

|------------|------|-------|---------|

|            |      |       |         |

图 2.30 观察窗口

(7) 选择菜单 View→Disassembly 命令, 可以得到汇编程序观察窗口, 如图 2.31 所示。

| main:                          |                                          |

|--------------------------------|------------------------------------------|

| 00022f:                        | 4efd ADD # -3, SP                        |

| 6                              | a = 1; MOV #1, *SP(#00h)                 |

| 000231:                        | e60001 b = 2; MOV #2, *SP(#01h)          |

| 000234:                        | e60202 c = a+b; MOV *SP(#01h), AR1       |

| 000237:                        | a902 ADD *SP(#00h), AR1, AR1             |

| 000239:                        | d60099 MOV AR1, *SP(#02h)                |

| 00023c:                        | c904 }                                   |

| 10                             | 00023e: 4e03 AADD # 3, SP                |

| 000240:                        | 4804 RET                                 |

| <u>register_unlock:</u>        |                                          |

| 000242:                        | eb11088002 MOV AC0, dbl(*abs16(#08002h)) |

| 000247:                        | 4804 RET                                 |

| <u>register_lock:</u>          |                                          |

| 000249:                        | eb11088000 MOV AC0, dbl(*abs16(#08000h)) |

| 00024e:                        | 4804 RET                                 |

| <u>nop:</u>                    |                                          |

| 000250:                        | 4804 RET                                 |

| <u>abort:</u>                  |                                          |

| 000252:                        | 20 NOP                                   |

| <u>C\$EXIT:</u>                |                                          |

| 000253:                        | 20 NOP                                   |

| 000254:                        | 16000c SIM_TRIG                          |

| 000257:                        | 4a7e B #0x000257                         |

| <u>\$vectors.asm:99:101\$:</u> |                                          |

| 000259:                        | 4a7e B \$vectors.asm:99:101\$            |

| 00025f:                        | 20 NOP                                   |

图 2.31 汇编程序观察窗口

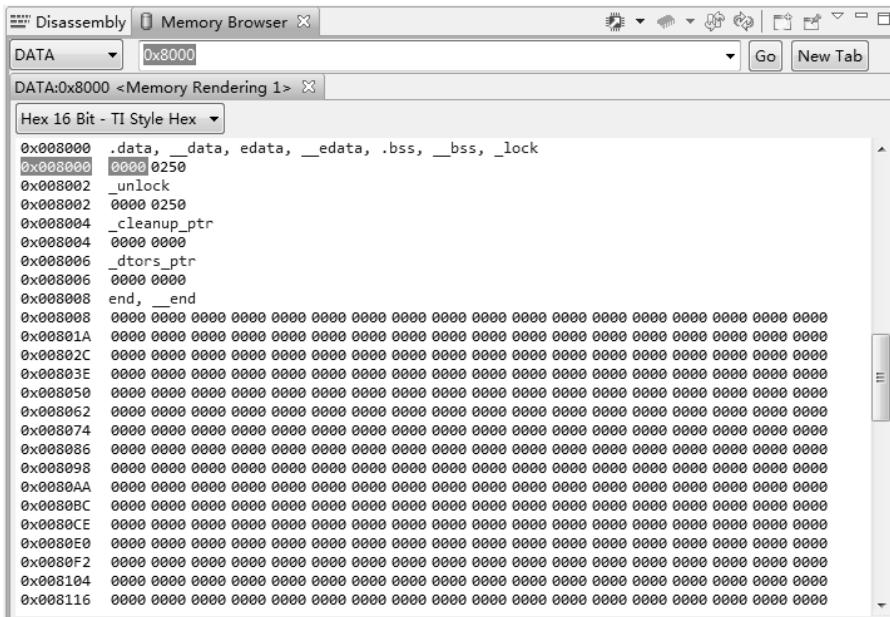

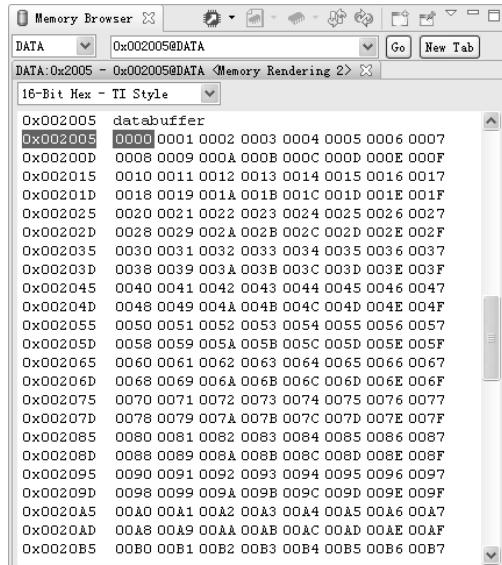

(8) 选择菜单 View→Memory Browser 命令, 可以得到内存查看窗口, 如图 2.32 所示。

图 2.32 内存查看窗口

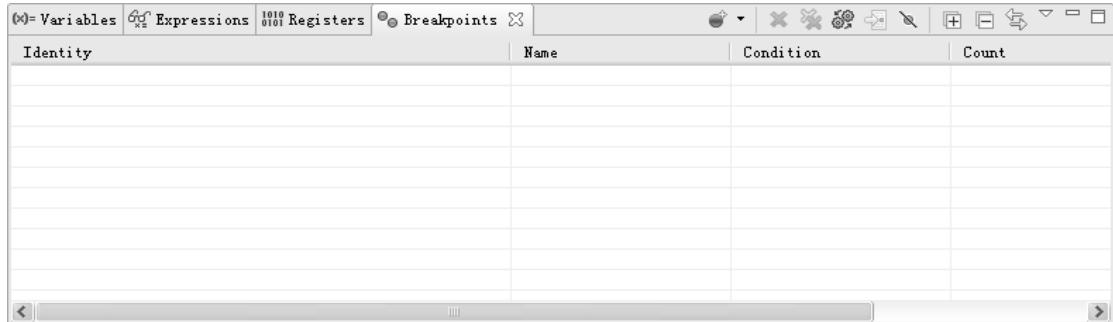

(9) 选择菜单 View→Break points 命令, 可以得到断点查看窗口, 如图 2.33 所示。

图 2.33 断点查看窗口

## 2.8 CCSv5.1 资源管理器简介及应用

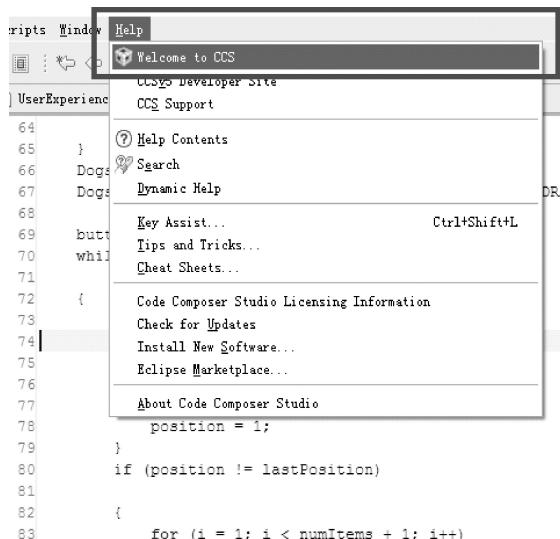

CCSv5.1 具有强大的功能, 并且其内部的资源也非常丰富, 利用其内部资源进行 DSP 开发, 将会非常方便。下面给出 CCSv5.1 资源管理器的应用。如图 2.34 所示, 通过 Help→Welcome to CCS 打开 CCSv5.1 的欢迎界面。

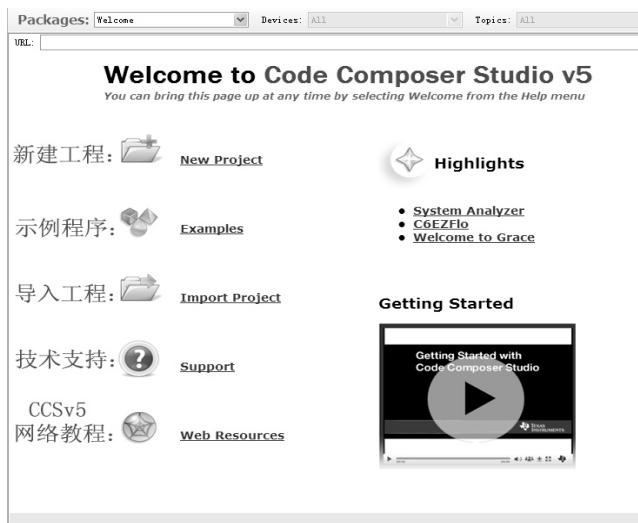

具体 TI 欢迎界面如图 2.35 所示, 利用 New Project 链接可以新建 CCS 工程; 利用 CCSv5.1 新建工程; 利用 Examples 链接可以搜索到示例程序资源; 利用 Import Project 链接可以导入已有 CCS 工程文件; 利用 CCSv5.1 导入已有工程; 利用 Support 链接可以在线获得技术支持;

利用 Web Resources 链接可以进入 CCSv5.1 网络教程，学习 CCSv5.1 有关知识。

图 2.34 欢迎界面打开途径

图 2.35 TI 欢迎界面

# 第 3 章 TMS320VC5509A CPU 寄存器

## 3.1 寄存器列表

表 3.1 按照字母顺序列出了 C55x CPU 中的寄存器。

表 3.1 C55x CPU 寄存器一览表

| 名 称                              | 说 明                 | 大 小       |

|----------------------------------|---------------------|-----------|

| AC0~AC3                          | 累加器 0~3             | 40 位 (每个) |

| AR0~AR7                          | 辅助寄存器 0~7           | 16 位 (每个) |

| BK03, BK47, BKC                  | 循环缓冲区大小寄存器          | 16 位 (每个) |

| BRC0, BRC1                       | 块循环计数器 0 和 1        | 16 位 (每个) |

| BRS1                             | BRC1 保存寄存器          | 16 位      |

| BSA01, BSA23, BSA45, BSA67, BSAC | 循环缓冲区起始地址寄存器        | 16 位 (每个) |

| CDP                              | 系数数据指针 (XCDP 的低位部分) | 16 位      |

| CDPH                             | XCDP 的高位部分          | 7 位       |

| CFCT                             | 控制流关系寄存器            | 8 位       |

| CSR                              | 计算单循环寄存器            | 16 位      |

| DBIER0, DBIER1                   | 调试中断使能寄存器 0 和 1     | 16 位 (每个) |

| DP                               | 数据页寄存器 (XDP 的低位)    | 16 位      |

| DPH                              | XDP 的高位部分           | 7 位       |

| IERO, IER1                       | 中断使能寄存器 0 和 1       | 16 位 (每个) |

| IFR0, IFR1                       | 中断标志寄存器 0 和 1       | 16 位 (每个) |

| IVPD, IVPH                       | 中断向量指针              | 16 位 (每个) |

| PC                               | 程序计数器               | 24 位      |

| PDP                              | 外设数据页寄存器            | 9 位       |

| REA0, REA1                       | 块循环结束地址寄存器 0 和 1    | 24 位 (每个) |

| RETA                             | 返回地址寄存器             | 24 位      |

| RPC                              | 单循环计数器              | 16 位      |

| RSA0, RSA1                       | 块循环结束地址寄存器 0 和 1    | 24 位 (每个) |

| SP                               | 数据堆栈指针              | 16 位      |

| SPH                              | XSP 和 XSSP 的高位      | 7 位       |

| SSP                              | 系统堆栈指针              | 16 位      |

| ST0_55~ST3_55                    | 状态寄存器 0~3           | 16 位 (每个) |

续表

| 名 称        | 说 明         | 大 小       |

|------------|-------------|-----------|

| T0~T3      | 临时寄存器       | 16 位 (每个) |

| TRN0, TRN1 | 变换寄存器 0 和 1 | 16 位 (每个) |

| XAR0~XAR7  | 扩展辅助寄存器 0~7 | 23 位 (每个) |

| XCDP       | 扩展系数数据指针    | 23 位      |

| XDP        | 扩展数据页寄存器    | 23 位      |

| XSP        | 扩展数据堆栈指针    | 23 位      |

| XSSP       | 扩展系统堆栈指针    | 23 位      |

### 3.1.1 寄存器的存储器映射

表 3.2 给出了存储器映射寄存器，它们是被映射到 DSP 数据空间地址的 CPU 寄存器。

表 3.2 存储器映射寄存器

| 地 址                                                                                                                       | 寄 存 器        | 名 称       | 位 范 围 |

|---------------------------------------------------------------------------------------------------------------------------|--------------|-----------|-------|

| 00 0000h                                                                                                                  | IER0         | 中断使能寄存器 0 | 15~0  |

| 00 0001h                                                                                                                  | IFR0         | 中断标志寄存器 0 | 15~0  |

| 00 0002h<br>(适用于 C55x 代码)                                                                                                 | ST0_55       | 状态寄存器 0   | 15~0  |

| <b>备注：</b> 地址 00 0002h 只适用于访问 ST0_55 的本地 TMS320C55x 代码，若要用 TMS320C54x 代码访问 ST0，则需将其写入地址 00 0006h 来访问 ST0_55。              |              |           |       |

| 00 0003h<br>(适用于 C55x 代码)                                                                                                 | ST1_55       | 状态寄存器 1   | 15~0  |

| <b>备注：</b> 地址 00 0003h 只适用于访问 ST1_55 的本地 TMS320C55x 代码，若要用 TMS320C54x 代码访问 ST1，则需将其写入地址 00 0007h 来访问 ST1_55。              |              |           |       |

| 00 0004h<br>(适用于 C55x 代码)                                                                                                 | ST3_55       | 状态寄存器 3   | 15~0  |

| <b>备注：</b> 地址 00 0004h 只适用于访问 ST3_55 的本地 TMS320C55x 代码，若要用 TMS320C54x 代码访问处理器模式状态寄存器 (PMST)，则需将其写入地址 00 001Dh 来访问 ST3_55。 |              |           |       |

| 00 0005h                                                                                                                  | —            | 保留 (不使用)  | —     |

| 00 0006h<br>(适用于 C54x 代码)                                                                                                 | ST0 (ST0_55) | 状态寄存器 0   | 15~0  |

| <b>备注：</b> 地址 00 0006h 是 ST0_55 的保护地址，将它写入 TMS320C54x 代码来访问 ST0。本地 TMS320C55x 代码访问 ST0_55 时需使用地址 00 0002h。                |              |           |       |

| 00 0007h<br>(适用于 C54x 代码)                                                                                                 | ST1 (ST1_55) | 状态寄存器 1   | 15~0  |

| <b>备注：</b> 地址 00 0007h 是 ST1_55 的保护地址，将它写入 TMS320C54x 代码来访问 ST1。本地 TMS320C55x 代码访问 ST1_55 时需使用地址 00 0003h。                |              |           |       |

续表

| 地 址      | 寄 存 器 | 名 称                 | 位 范 围 |

|----------|-------|---------------------|-------|

| 00 0008h | AC0L  | 累加器 0               | 15~0  |

| 00 0009h | AC0H  |                     | 31~16 |

| 00 000Ah | AC0G  |                     | 39~32 |

| 00 000Bh | AC1L  | 累加器 1               | 15~0  |

| 00 000Ch | AC1H  |                     | 31~16 |

| 00 000Dh | AC1G  |                     | 39~32 |

| 00 000Eh | T3    | 临时寄存器 3             | 15~0  |

| 00 000Fh | TRN0  | 变换寄存器 0             | 15~0  |

| 00 0010h | AR0   | 辅助寄存器 0             | 15~0  |

| 00 0011h | AR1   | 辅助寄存器 1             | 15~0  |

| 00 0012h | AR2   | 辅助寄存器 2             | 15~0  |

| 00 0013h | AR3   | 辅助寄存器 3             | 15~0  |

| 00 0014h | AR4   | 辅助寄存器 4             | 15~0  |

| 00 0015h | AR5   | 辅助寄存器 5             | 15~0  |

| 00 0016h | AR6   | 辅助寄存器 6             | 15~0  |

| 00 0017h | AR7   | 辅助寄存器 7             | 15~0  |

| 00 0018h | SP    | 数据堆栈指针              | 15~0  |

| 00 0019h | BK03  | AR0~AR3 的循环缓冲区大小寄存器 | 15~0  |

备注：在 TMS320C54x 兼容模式下 (C54CM=1)，BK03 用于所有的辅助寄存器。C54CM 是状态寄存器 1 (ST1\_55) 里的一个位。

|                           |               |                  |      |

|---------------------------|---------------|------------------|------|

| 00 001Ah                  | BRC0          | 块循环计数器 0         | 15~0 |

| 00 001Bh                  | RSA0L         | 块循环起始地址寄存器 0 的低位 | 15~0 |

| 00 001Ch                  | REA0L         | 块循环结束地址寄存器 0 的低位 | 15~0 |

| 00 001Dh<br>(适用于 C54x 代码) | PMST (ST3_55) | 状态寄存器 3          | 15~0 |

备注：地址 00 001Dh 是 ST3\_55 的保护地址，将 TMS320C54x 代码写入该地址来访问处理器模式状态寄存器 (PMST)。本地 TMS320C54x 代码要访问 ST3\_55 地址需使用地址 00 0004h。

|          |      |                         |       |

|----------|------|-------------------------|-------|

| 00 001Eh | XPC  | 与 C54x 代码相兼容的程序计数器扩展寄存器 | 7~0   |

| 00 001Fh | —    | 保留 (不使用)                | —     |

| 00 0020h | T0   | 临时寄存器 0                 | 15~0  |

| 00 0021h | T1   | 临时寄存器 1                 | 15~0  |

| 00 0022h | T2   | 临时寄存器 2                 | 15~0  |

| 00 0023h | T3   | 临时寄存器 3                 | 15~0  |

| 00 0024h | AC2L | 累加器 2                   | 15~0  |

| 00 0025h | AC2H |                         | 31~16 |

续表

| 地 址      | 寄 存 器 | 名 称                                         | 位 范 围 |

|----------|-------|---------------------------------------------|-------|

| 00 0026h | AC2G  | 累加器 2                                       | 39~32 |

| 00 0027h | CDP   | 系统数据指针                                      | 15~0  |

| 00 0028h | AC3L  |                                             | 15~0  |

| 00 0029h | AC3H  | 累加器 3                                       | 31~16 |

| 00 002Ah | AC3G  |                                             | 39~32 |

| 00 002Bh | DPH   | 扩展数据页寄存器的高位                                 | 6~0   |

| 00 002Ch | —     | 保留（不使用）                                     | —     |

| 00 002Dh | —     | 保留（不使用）                                     | —     |

| 00 002Eh | DP    | 数据页寄存器                                      | 15~0  |

| 00 002Fh | PDP   | 外设数据页寄存器                                    | 8~0   |

| 00 0030h | BK47  | AR4~AR7 的循环缓冲区大小寄存器                         | 15~0  |

| 00 0031h | BKC   | CDP 的循环缓冲区大小寄存器                             | 15~0  |

| 00 0032h | BSA01 | AR0 和 AR1 的循环缓冲区起始地址寄存器                     | 15~0  |

| 00 0033h | BSA23 | AR2 和 AR3 的循环缓冲区起始地址寄存器                     | 15~0  |

| 00 0034h | BSA45 | AR4 和 AR5 的循环缓冲区起始地址寄存器                     | 15~0  |

| 00 0035h | BSA67 | AR0 和 AR1 的循环缓冲区起始地址寄存器                     | 15~0  |

| 00 0036h | BSAC  | CDP 的循环缓冲区起始地址寄存器                           | 15~0  |

| 00 0037h | —     | BIOS 保留。一个用来保存 BIOS 操作所需的数据表指针起始地址的 16 位寄存器 | —     |

| 00 0038h | TRN1  | 变换寄存器 1                                     | 15~0  |

| 00 0039h | BRC1  | 块循环计数器 1                                    | 15~0  |

| 00 003Ah | BRS1  | BRC1 保存寄存器                                  | 15~0  |

| 00 003Bh | CSR   | 计算单循环寄存器                                    | 15~0  |

| 00 003Ch | RSA0H | 块循环起始地址寄存器 0                                | 23~16 |

| 00 003Dh | RSA0L |                                             | 15~0  |

| 00 003Eh | REA0H | 块循环结束地址寄存器 0                                | 23~16 |

| 00 003Fh | REA0L |                                             | 15~0  |

| 00 0040h | RSA1H | 块循环起始地址寄存器 1                                | 23~16 |

| 00 0041h | RSA1L |                                             | 15~0  |

| 00 0042h | REA1H | 块循环结束地址寄存器 1                                | 23~16 |

| 00 0043h | REA1L |                                             | 15~0  |

续表

| 地 址               | 寄 存 器  | 名 称                     | 位 范 围 |

|-------------------|--------|-------------------------|-------|

| 00 0044h          | RPTC   | 单循环计数器                  | 15~0  |

| 00 0045h          | IERT1  | 中断使能寄存器 1               | 10~0  |

| 00 0046h          | IFR1   | 中断标志寄存器 1               | 10~0  |

| 00 0047h          | DBIER0 | 调试中断使能寄存器 0             | 15~0  |

| 00 0048h          | DBIER1 | 调试中断使能寄存器 1             | 10~0  |

| 00 0049h          | IVPD   | 向量 0~15 和 24~31 的中断向量指针 | 15~0  |

| 00 004Ah          | IVPH   | 向量 16~23 的中断向量指针        | 15~0  |

| 00 004Bh          | ST2_55 | 状态寄存器 2                 | 15~0  |

| 00 004Ch          | SSP    | 系统堆栈指针                  | 15~0  |

| 00 004Dh          | SP     | 数据堆栈指针                  | 15~0  |

| 00 004Eh          | SPH    | 扩展堆栈指针的高位               | 6~0   |

| 00 004Fh          | CDPH   | 扩展系数数据指针的高位             | 6~0   |

| 00 0050h~00 005Fh | —      | 保留（不适用）                 | —     |

### 注意：

(1) ST0\_55, ST1\_55 和 ST3\_55 均可在两个地址中访问。在一个地址中，所有的 TMS320C55x 位都是可用的；在另外一个地址（被保护地址）中，某些位是无法被修改的。被保护的地址用来支持写入 ST0, ST1 和 PMST (ST3\_55 对应的 C54xTM) 的 TMS320C54xTM 码。

(2) T3, RSA0L, REA0L 和 SP 均可在两个地址中互相访问。对于使用 DP 直接寻址模式映射到内存的寄存器访问，汇编器将会替代两个地址中的高位地址：T3 = 23h (而非 0Eh), RSA0L = 3Dh (而非 1Bh), REA0L = 3Fh (而非 1Ch), SP = 4Dh (而非 18h)。

(3) 加载 BRC1 的任何 C55x 指令都将把相同的值加载到 BRS1。

### 3.1.2 累加器 (AC0~AC3)

CPU 包含 4 个 40 位的累加器：AC0, AC1, AC2 和 AC3。这些寄存器的基本功能是协助 D 单元的算术逻辑单元 (ALU)、乘法和累加单元 (MACs) 与移位器进行数据计算。这 4 个累加器基本上是等价的，当然某些情况下除外。例如，当一些指令被限制在确定的累加对分组中时：

SWAP AC0, AC2; 有效指令

SWAP AC1, AC3; 有效指令

但是，SWAP AC0, AC1; 无效指令

每个累加器都被分割为一个低字 (ACxL), 一个高字 (ACxH), 以及八个保护位 (ACxG)。可以运用访问存储器映射寄存器的寻址模式来单独访问这些部分。

在 TMS320C54x 兼容模式下 (C54CM=1)，累加器 AC0 和 AC1 分别对应 TMS320C54x 累加器 A 和 B。

### 3.1.3 变换寄存器 (TRN0, TRN1)

TRN0 和 TRN1 这两个变换寄存器被用在比较和选择极值指令中：

(1) 用于执行校正 TRN0 和 TRN1 的两个 16 位极值选择的语句依靠对两个累加器的高位字的比较和低位字的比较。TRN0 的校正依靠两个累加器的高位字的比较，TRN1 的校正则依靠对两个累加器的低位字进行比较。

(2) 用于执行校正选定的变换寄存器 (TRN0 或 TRN1) 的单一 40 位极值选择的语法依靠对两个累加器全部 40 位进行比较。

TRN0 和 TRN1 可以保存实现维特比算法新指标的变换决定。

### 3.1.4 临时寄存器 (T0~T3)

CPU 包含 4 个 16 位通用临时寄存器：T0、T1、T2 和 T3。下面是临时寄存器可以实现的一些功能：

- 存放乘法、乘加以及乘减的运算里的被乘数；

- 存放 D 单元里加法、减法和装载指令的移位数；

- 通过交换辅助寄存器 (AR0~AR7) 和临时寄存器的内容来追踪多个指针值；

- 为 D 单元里 ALU 的双 16 位操作存放维特比蝶形变换尺度。

注意：如果 C54CM=1 (TMS320C54x 兼容模式打开)，T2 受制于状态寄存器 ST1\_55 的 ASM 位，并且不能用作通用寄存器。

### 3.1.5 数据和 I/O 空间寻址寄存器

表 3.3 列出了数据和 I/O 空间寻址的寄存器。

表 3.3 数据和 I/O 空间寻址寄存器

| 寄 存 器                            | 功 能                     |

|----------------------------------|-------------------------|

| XAR0~XAR7 或 AR0~AR7              | 指向数据空间中的一个数据值用于间接寻址模式访问 |

| XCDP 和 CDP                       | 指向数据空间中的一个数据值用于间接寻址模式访问 |

| BSA01, BSA23, BSA45, BSA67, BSAC | 指定一个循环缓冲区的首地址加到一个指针上    |

| BK03, BK47, BKC                  | 指定一个循环缓冲区的大小            |

| XDP 和 DP                         | 指定 DP 直接寻址模式访问的首地址      |

| PDP                              | 确定 I/O 空间的访问的外设数据页      |

| XSP 和 SP                         | 指向数据堆栈上的一个值             |

| XSSP 和 SSP                       | 指向系统堆栈上的一个值             |

#### 1. 辅助寄存器 (XAR0~XAR7 或 AR0~AR7)

CPU 包括了 8 个扩展的辅助寄存器 XAR0~XAR7(见表 3.4)。每个高位部分(比如 AR0H)用来指定访问数据空间所需的 7 位主数据页；每个低位部分(比如 AR0)可用作：

- 7 位主数据页的 16 位偏移量(形成 23 位的地址)；

- 一个位地址(用于访问单独的位或位对指令中)；

- 一个通用寄存器或计数器；

- 用于选择与循环缓冲区首地址相关位的一个指标。

表 3.4 扩展辅助寄存器及其组成部分

| 寄存器  | 名称            | 可访问性                   |

|------|---------------|------------------------|

| XARn | 扩展辅助寄存器 n     | 只可通过专用指令访问，不映射到内存      |

| ARn  | 辅助寄存器 n       | 可通过专用指令访问，也可作为存储器映射寄存器 |

| ARnH | 扩展辅助寄存器 n 的高位 | 只能通过访问 XARn 来访问        |

XAR0~XAR7 或 AR0~AR7 用在 AR 间接寻址模式和双 AR 间接寻址模式中。在 A 单元的 ALU 中，在 AR0~AR7 上可以执行基本的算术、逻辑和移位运算。这些操作可以和在数据地址产生单元 (DAGEN) 的辅助寄存器上执行的地址修改操作同时进行。

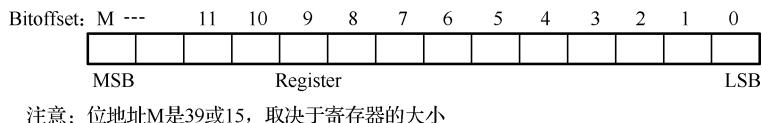

## 2. 系数数据指针 (XCDP 和 CDP)

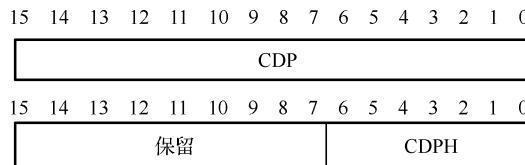

CPU 在内存中映射了一个系数数据指针 (CDP) 和一个相关扩展寄存器 (CDPH)，如图 3.1 所示。

图 3.1 CDP 和 CDPH

CPU 通过连接 CDP 和 CDPH 形成一个扩展的 CDP，称作 XCDP (见表 3.5)。其高位部分 (CDPH) 用来规定访问数据空间的 7 位主数据页；低位部分 (CDP) 可用作：

- 7 位主数据页的 16 位偏移量 (形成 23 位地址)；

- 一个位地址 (用在访问单独的位和位对指令中)；

- 一个通用寄存器或计数器；

- 用于选择与循环缓冲区首地址相关位的一个指标。

表 3.5 扩展系数数据指针和它的组成

| 寄存器  | 名称            | 可访问性                                         |

|------|---------------|----------------------------------------------|

| XCDP | 扩展系数数据指针      | 只能通过专用指令访问，不映射到内存                            |

| CDP  | 系数数据指针        | 可通过专用指令访问，也可作为存储器映射寄存器                       |

| CDPH | 扩展系数数据指针的高位部分 | 可作为存储器映射寄存器被访问。可通过访问 XCDP 来访问 CDPH，它没有专用访问指令 |

XCDP 或者 CDP 用在 CDP 的间接寻址模式和系数间接寻址模式中。CDP 可用在任一访问某个数据空间值的指令中。不过，在双乘加 (MAC) 的指令中 CDP 将更方便使用，因为它给 D 单元双 MAC 操作者提供了又一个独立的运算元。

### 3. 循环缓冲区首地址寄存器 (BSA01, BSA23, BSA45, BSA67, BSAC)

CPU 包含了 5 个 16 位的循环缓冲区首地址寄存器, 它们可以定义一个带有首地址的循环缓冲区并且不受到任何队列限制所束缚。

每一个缓冲区首地址寄存器都和一个特定的指针或数个指针相关联 (见表 3.6)。只有当指针被配置在 ST\_255 状态寄存器中进行循环寻址时, 一个缓冲区首地址才被加到指针值上。

表 3.6 循环缓冲区首地址寄存器和相关联的指针

| 寄存器   | 指针        | 提供主数据页的寄存器         |

|-------|-----------|--------------------|

| BSA01 | AR0 或 AR1 | AR0:AR0H; AR1:AR1H |

| BSA23 | AR2 或 AR3 | AR2:AR2H; AR3:AR3H |

| BSA45 | AR4 或 AR5 | AR4:AR4H; AR5:AR5H |

| BSA67 | AR6 或 AR7 | AR6:AR6H; AR7:AR7H |

| BSAC  | CDP       | CDPH               |

举一个运用缓冲区首地址的例子, 考虑如下指令:

```

MOV *AR6, T2 ; Load T2 with a value from the circular

; buffer of words referenced by XAR6.

```

在这个例子中, 将 AR6 配置在循环寻址中, 地址以如下形式产生:

```

AR6H:(BSA67 + AR6)= XAR6 + BSA67

```

主数据页值 (AR6H) 由 AR6 的总和以及与它关联的缓冲区首地址 (BSA67) 连接得到。当以兼容模式 (C54CM=1) 运行 TMS320C54x 码时, 要确保缓冲区首地址寄存器包含 0。

### 4. 循环缓冲区大小寄存器 (BK03, BK47, BKC)

3 个 16 位循环缓冲区大小寄存器指定了循环缓冲区的大小 (最大为 65535)。每一个缓冲区大小寄存器与一个或几个特定的指针相关联 (见表 3.7)。

表 3.7 环缓冲区大小寄存器和相关联的指针

| 寄存器  | 指针                  |

|------|---------------------|

| BK03 | AR0, AR1, AR2 或 AR3 |

| BK47 | AR4, AR5, AR6 或 AR7 |

| BKC  | CDP                 |

### 5. 数据页寄存器 (XDP 和 DP)

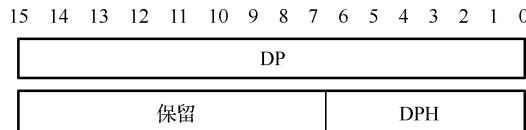

CPU 在内存中映射了一个数据页寄存器 DP 和一个相关的扩展寄存器 DPH, 如图 3.2 所示。

图 3.2 DP 和 DPH

CPU 连接这两个寄存器形成一个扩展数据页寄存器 XDP，如图 3.3 和表 3.8 所示。高位部分 (DPH) 用来指定访问数据空间的 7 位主数据页，低位部分 (DP) 指定了 16 位的偏移 (本地数据页)，用来和主数据页相连接构成 23 位的地址。

图 3.3 扩展数据页寄存器和它的组成

表 3.8 扩展数据页寄存器和它的组成

| 寄 存 器 | 名 称           | 可 访 问 性                |

|-------|---------------|------------------------|

| XDP   | 扩展数据页寄存器      | 只能通过专用指令访问，它不映射到内存     |

| DP    | 数据页寄存器        | 可通过专用指令访问，也可作为存储器映射寄存器 |

| DPH   | 扩展数据页寄存器的高位部分 | 可通过专用指令访问，也可作为存储器映射寄存器 |

在 DP 直接寻址模式中，XDP 指定了一个 23 位的地址，在 K16 绝对寻址模式中，DPH 和一个 16 位的即时值相连接构成 23 位的地址。

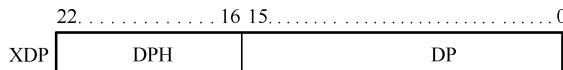

## 6. 外设数据页寄存器 (PDP)

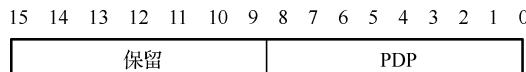

对于 PDP 直接寻址模式，9 位的外设数据页寄存器 (PDP) 从 64K 字的 I/O 空间中挑选出一个 128 字的页。

如图 3.4 所示，PDP 是一个存在于 16 位寄存器位置之中的 9 位域。其中的 9~15 位均被 CPU 忽略。

这个寄存器可以通过特定指令访问并可作为一个存储器映射寄存器使用。

图 3.4 外设数据页寄存器

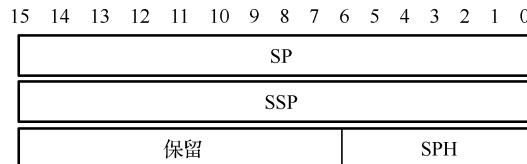

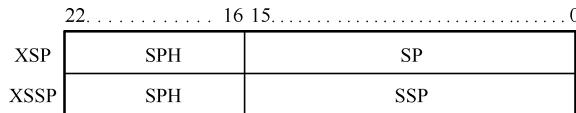

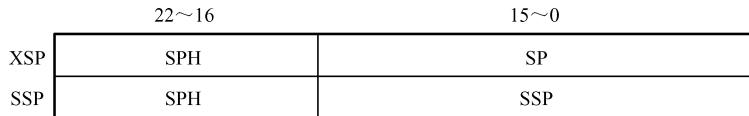

## 7. 堆栈指针 (XSP/SP, XSSP/SSP)

CPU 将一个数据堆栈指针 (SP)、一个系统堆栈指针 (SSP) 和一个相关的扩展寄存器 (SPH) 包含在其存储器映射中，如图 3.5 所示。

当访问数据堆栈时，CPU 把 SP 和 SPH 连接到一起形成一个扩展的 SP 称作 XSP。XSP 包含了最后放进数据堆栈值的地址。SPH 保存 7 位的内存主数据页，SP 指向这一页特定的字。

类似地，当访问系统堆栈时，CPU 把 SPH 和 SSP 连接在一起形成 XSSP。XSSP 包含最后放进系统堆栈值的地址，如图 3.6 所示。

图 3.5 SP、SSP 和 SPH

图 3.6 XSP 和 XSSP

表 3.9 列出了堆栈指针寄存器及其访问属性。

表 3.9 堆栈指针寄存器

| 寄存器  | 名称               | 可访问性                                                                             |

|------|------------------|----------------------------------------------------------------------------------|

| XSP  | 扩展数据堆栈指针         | 只能通过专用指令访问, 它不映射到内存                                                              |

| SP   | 数据堆栈指针           | 可通过专用指令访问, 也可作为存储器映射寄存器                                                          |

| XSSP | 扩展系统堆栈指针         | 只能通过专用指令访问, 它不映射到内存                                                              |

| SSP  | 系统堆栈指针           | 可通过专用指令访问, 也可作为存储器映射寄存器                                                          |

| SPH  | XSP 和 XSSP 的高位部分 | 可作为存储器映射寄存器被访问, 也可通过访问 XSP 或 XSSP 来访问它, 它没有专门指令<br><br>注意: 写 XSP 和 XSSP 都会影响 SPH |

XSP 用在 SP 直接访问模式中。表 3.10 列出了如何使用和修改 SP 和 SSP 的指令。

表 3.10 使用和修改 SP 和 SSP 的指令

| 指令类型                       | 指令描述                                      |

|----------------------------|-------------------------------------------|

| 软件中断、软件自陷、软件复位、无条件调用、有条件调用 | 这些指令将数据压入数据堆栈和系统堆栈中。SP 和 SSP 在每对数据值压入前减小  |

| 入栈                         | 这条指令只把数据压入数据堆栈。每次数据压入前, SP 减小             |

| 无条件返回、有条件返回、中断返回           | 这些指令将数据从数据堆栈和系统堆栈中推出。SP 和 SSP 在每对数据值推出后增加 |

| 出栈                         | 这条指令只将数据堆栈里的数据推出。SP 在每次数据推出后增加            |

堆栈指针增加或减小由 SP 和 SSP 决定。在不改变扩展寄存器 (SPH) 的值时, 无法从主数据页中进行堆栈寻址。

注意: 尽管当增加超过 FFFFh 或者减小超过 0000h 时可以使指针值绕回, 但在实际情况下要避免这样做。

### 3.1.6 程序流寄存器 (PC, RETA, CFCT)

表 3.11 列出了 CPU 用来维持适当程序流的三个寄存器。

表 3.11 程序流寄存器

| 寄存器  | 说    明                                                                                                                                                |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| PC   | 程序计数器。这个 24 位的寄存器存放 I 单元里解码的 1~6 字节代码的地址。当 CPU 执行中断或调用时, 当前 PC 值 (返回地址) 被存储, 新的地址装入 PC。当 CPU 从中断服务程序或子程序调用返回时, PC 重新存储返回地址                            |

| RETA | 返回地址寄存器。当所选择的堆栈结构运用快速返回处理时, 在子程序执行的同时 RETA 暂存返回地址。RETA 和 CFCY 一起保证了多层次子程序的高效执行。可以通过专用 32 位装入和存储指令对一对 RETA 和 CFCT 进行读/写                                |

| CFCT | 程序流关系寄存器。CPU 记录了激活的循环 (循环的前后关系)。当所选择的堆栈结构运用快速返回处理时, 在子程序执行的同时 CFCT 充当 8 位循环关系暂存器。CFCT 和 RETA 一起保证了多层次子程序的高效执行。可以通过专用 32 位装入和存储指令对一对 RETA 和 CFCT 进行读/写 |

备注: 利用 DSP 硬件复位, RETA 和 CFCT 将清零, 并且不受入/出栈指令和软件复位影响。

CPU 由内部位按照一定规则来存放循环的前后关系, 即子程序里循环的状态 (激活或未激活)。当 CPU 跟随一次中断或调用, 循环关系就储存在 CFCT。当 CPU 从一次中断或者被调用的子程序中返回时, 循环关系从 CFCT 中恢复, 在 8 位 CFCT 中, 循环关系位以表 3.12 所示的形式出现。

表 3.12 CFCT 中循环关系位的形式

| 位    数 | 说    明                         |        |        |

|--------|--------------------------------|--------|--------|

| 7      | 该位表示一个单循环是否激活: 0——未激活, 1——激活   |        |        |

| 6      | 该位表示一个条件单循环是否激活: 0——未激活, 1——激活 |        |        |

| 5~4    | 保留                             |        |        |

|        | 块重复代码                          | 0 层循环  | 1 层循环  |

| 3~0    | 0                              | 未激活    | 未激活    |

|        | 2                              | 激活, 外部 | 未激活    |

|        | 3                              | 激活, 本地 | 未激活    |

|        | 7                              | 激活, 外部 | 激活, 外部 |

|        | 8                              | 激活, 外部 | 激活, 本地 |

|        | 9                              | 激活, 本地 | 激活, 本地 |

|        | 其他: 保留                         | —      | —      |

### 3.1.7 中断管理寄存器

表 3.13 列出了中断管理寄存器。

表 3.13 中断管理寄存器

| 寄 存 器         | 功 能                   |

|---------------|-----------------------|

| IVPD          | 指向中断向量 0~15 和 24~31   |

| IVPH          | 指向中断向量 16~23          |

| IFR0、IFR1     | 指示被请求可屏蔽中断            |

| IER0、IER1     | 使能或制止可屏蔽中断            |

| DBIER0、DBIER1 | 调试中配置选择可屏蔽中断为时间严格要求中断 |

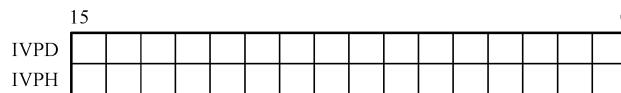

#### 1. 中断向量指针 (IVPD, IVPH)

两个 16 位中断向量指针 IVPD 和 IVPH (如图 3.7 所示) 指向程序空间中最大 32 个中断向量。IVPD 为中断向量 0~15 和 24~31 指向 256 字节程序页。IVPH 为中断向量 16~23 指向 256 字节的程序页。

图 3.7 中断向量指针

若 IVPD 和 IVPH 值相同, 所有的中断向量都在同一 256 字节程序页中。DSP 硬件复位时 IVPD 和 IVPH 都装入到 FFFFh 地址中。它们都不受软件复位的影响。

在修改 IVP 之前要确保:

- 可屏蔽中断全局禁止 (INTM=1), 这样可以在 IVP 被修改后指向到新向量前阻止可屏蔽中断发生;

- 每个硬件不可屏蔽中断对于旧 IVPD 值和新 IVPD 值都有一个中断向量和中断服务程序, 这样在修改 IVPD 的过程中, 当硬件不可避免中断发生时可阻止非法指令码的收回。

表 3.14 列出了针对不同中断向量地址的构成。CPU 将一个 16 位的中断向量指针和一个 5 位向量编号相连 (比如 IV1 是 00001, IV16 是 10000), 然后向左移 3 位。

表 3.14 中断向量地址

| 向 量       | 中 断                  | 向 量 地 址 |             |       |

|-----------|----------------------|---------|-------------|-------|

|           |                      | 位 23~8  | 位 7~3       | 位 2~0 |

| IV0       | 复位                   | IVPD    | 00000       | 000   |

| IV1       | 不可屏蔽硬件中断 NMI         | IVPD    | 00001       | 000   |

| IV2~IV15  | 可屏蔽中断                | IVPD    | 00010~01111 | 000   |

| IV16~IV23 | 可屏蔽中断                | IVPH    | 10000~10111 | 000   |

| IV24      | 总线错误中断 (可屏蔽) BERRINT | IVPD    | 11000       | 000   |

续表

| 向量        | 中 断                  | 向量地址   |             |       |

|-----------|----------------------|--------|-------------|-------|

|           |                      | 位 23~8 | 位 7~3       | 位 2~0 |

| IV25      | 数据记录中断（可屏蔽）DLOGINT   | IVPD   | 11001       | 000   |

| IV26      | 实时操作系统中断（可屏蔽）RTOSINT | IVPD   | 11010       | 000   |

| IV27~IV31 | 通用软件中断 INT27~INT31   | IVPD   | 11011~11111 | 000   |

## 2. 中断标志寄存器 (IFR0, IFR1)

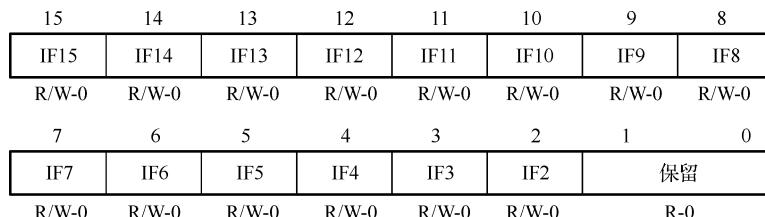

IFR1 和 IFR0 是两个 16 位的中断标志寄存器（如表 3.15 和表 3.16 所示）。它们包含所有可屏蔽中断的标志位。当一次可屏蔽中断请求抵达 CPU 时，IFR 中相应的标志位置 1。这意味着中断挂起等待 CPU 响应。图 3.8 描述了 IFR1 和 IFR0 的一般呈现方式。读 IFR 可以鉴定挂起的中断，写入 IFR 可以清空挂起的中断。写 1 到相应的 IFR 位可以清零中断请求。例如：

```

; Clear flags IF14 and IF2:

MOV #01000000000000100b, mmap(@IFR0)

```

表 3.15 中断标志寄存器 IFR1

| 位   | 名 称       | 描 述          | 可 访 问 性 | HW 复位 | 读 位 解 释                                  |

|-----|-----------|--------------|---------|-------|------------------------------------------|

| 10  | RTOSINTF  | 实时操作系统中断的标志位 | 读/写     | 0     | 0: RTOSINT 非未决;<br>1: RTOSINT 未决         |

| 9   | DLOGINTF  | 数据记录中断的标志位   | 读/写     | 0     | 0: DLOGINT 非未决;<br>1: DLOGINT 未决         |

| 8   | BERINTFR  | 总线错误中断的标志位   | 读/写     | 0     | 0: BERRINT 非未决;<br>1: BERRINT 未决         |

| 0~7 | IF16~IF23 | 中断标志位        | 读/写     | 0     | 0: 与对应中断向量关联的中断非未决;<br>1: 与对应中断向量关联的中断未决 |

表 3.16 中断标志寄存器 IFR0

| 位    | 名 称      | 描 述   | 可 访 问 性 | HW 复位 | 读 位 解 释                                  |

|------|----------|-------|---------|-------|------------------------------------------|

| 2~15 | IF2~IF15 | 中断标志位 | 读/写     | 0     | 0: 与对应中断向量关联的中断非未决;<br>1: 与对应中断向量关联的中断未决 |

将 IFR 当前内容写回到 IFR 中，所有挂起的中断均可清零。硬件中断请求的响应也可将相应的 IFR 位清零，而器件复位会使所有 IFR 位清零。

## 3. 中断使能寄存器 (IER0, IER1)

将 IER1 或 IER0（如表 3.17 和表 3.18 所示）使能位置 1 可产生可屏蔽中断，使能位置 0 可禁止可屏蔽中断。DSP 硬件复位会使所有 IER 位清零，禁止所有可屏蔽中断。图 3.9 描述了基本的 C55x 中断使能寄存器。IER 不受软件复位指令影响。在全局使能 (INTM=0) 可屏蔽中断前要初始化 IER 寄存器。

|      |         |         |         |         |          |          |          |         |

|------|---------|---------|---------|---------|----------|----------|----------|---------|

| IFR1 | 15      | 14      | 13      | 12      | 11       | 10       | 9        | 8       |

|      | 保留      |         |         |         | RTOSINTF | DLOGINTF | BERRINTF |         |

|      |         |         |         |         | R/W1C-0  | R/W1C-0  | R/W1C-0  |         |

|      | 7       | 6       | 5       | 4       | 3        | 2        | 1        | 0       |

|      | IF23    | IF22    | IF21    | IF20    | IF19     | IF18     | IF17     | IF16    |

|      | R/W1C-0 | R/W1C-0 | R/W1C-0 | R/W1C-0 | R/W1C-0  | R/W1C-0  | R/W1C-0  | R/W1C-0 |

| IFR0 | 15      | 14      | 13      | 12      | 11       | 10       | 9        | 8       |

|      | IF15    | IF14    | IF13    | IF12    | IF11     | IF10     | IF9      | IF8     |

|      | R/W1C-0 | R/W1C-0 | R/W1C-0 | R/W1C-0 | R/W1C-0  | R/W1C-0  | R/W1C-0  | R/W1C-0 |

|      | 7       | 6       | 5       | 4       | 3        | 2        | 1        | 0       |

|      | IF7     | IF6     | IF5     | IF4     | IF3      | IF2      | 保留       |         |

|      | R/W1C-0 | R/W1C-0 | R/W1C-0 | R/W1C-0 | R/W1C-0  | R/W1C-0  | R-0      |         |

图 3.8 中断标志寄存器 IFR0、IFR1

表 3.17 中断使能寄存器 IER1

| 位   | 名 称       | 描 述          | 可访问性 | HW 复位 | 读 位 解 释                                 |

|-----|-----------|--------------|------|-------|-----------------------------------------|

| 10  | RTOSINTE  | 实时操作系统中断的使能位 | 读/写  | 0     | 0: 禁止 RTOSINT;<br>1: 使能 RTOSINT         |

| 9   | DLOGINTE  | 数据记录中断的使能位   | 读/写  | 0     | 0: 禁止 DLOGINT;<br>1: 使能 DLOGINT         |

| 8   | BERRINTE  | 总线错误中断的使能位   | 读/写  | 0     | 0: 禁止与对应中断向量关联的中断;<br>1: 使能与对应中断向量关联的中断 |

| 0~7 | IE16~IE23 | 中断使能位        | 读/写  | 0     | 0: 禁止与对应中断向量关联的中断;<br>1: 使能与对应中断向量关联的中断 |

表 3.18 中断使能寄存器 IER0

| 位    | 名称       | 描 述   | 可访问性 | HW 复位 | 读 位 解 释                                 |

|------|----------|-------|------|-------|-----------------------------------------|

| 2~15 | IE2~IE15 | 中断标志位 | 读/写  | 0     | 0: 禁止与对应中断向量关联的中断;<br>1: 使能与对应中断向量关联的中断 |

|      |       |       |       |       |          |          |          |       |

|------|-------|-------|-------|-------|----------|----------|----------|-------|

| IFR1 | 15    | 14    | 13    | 12    | 11       | 10       | 9        | 8     |

|      | 保留    |       |       |       | RTOSINTF | DLOGINTF | BERRINTF |       |

|      |       |       |       |       | R/W-0    | R/W-0    | R/W-0    |       |

|      | 7     | 6     | 5     | 4     | 3        | 2        | 1        | 0     |

|      | IF23  | IF22  | IF21  | IF20  | IF19     | IF18     | IF17     | IF16  |

|      | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0    | R/W-0    | R/W-0    | R/W-0 |

| IFR0 | 15    | 14    | 13    | 12    | 11       | 10       | 9        | 8     |

|      | IF15  | IF14  | IF13  | IF12  | IF11     | IF10     | IF9      | IF8   |

|      | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0    | R/W-0    | R/W-0    | R/W-0 |

|      | 7     | 6     | 5     | 4     | 3        | 2        | 1        | 0     |

|      | IF7   | IF6   | IF5   | IF4   | IF3      | IF2      | 保留       |       |

|      | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0    | R/W-0    | R-0      |       |

图 3.9 中断标志寄存器 IER0、IER1

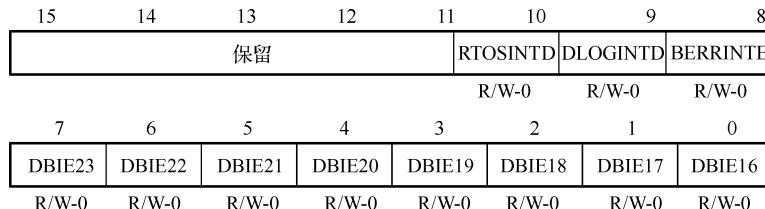

#### 4. 调试中断使能寄存器 (DBIER0, DBIER1)

DBIER1、DBIER0 这两个 16 位调试中断使能寄存器 (如表 3.19 和表 3.20 所示) 只有当 CPU 在调试器实时仿真模式中停机时才被使用。若在实时模式中 CPU 处于运行中，则将执行标准中断处理过程而忽略 DBIER。

表 3.19 调试中断使能寄存器 DBIER1

| 位   | 名 称           | 描 述            | 可访问性 | HW 复位 | 读 位 解 释                                 |

|-----|---------------|----------------|------|-------|-----------------------------------------|

| 10  | RTOSINTD      | 实时操作系统中断的调试使能位 | 读/写  | 0     | 0: 禁止 RTOSINT;<br>1: 使能 RTOSINT         |

| 9   | DLOGINTD      | 数据记录中断的调试使能位   | 读/写  | 0     | 0: 禁止 DLOGINT;<br>1: 使能 DLOGINT         |

| 8   | BERRINTD      | 总线错误中断的调试使能位   | 读/写  | 0     | 0: 禁止 BERRINT;<br>1: 使能 BERRINT         |

| 0~7 | DBIE16~DBIE23 | 调试中断使能位        | 读/写  | 0     | 0: 禁止与对应中断向量关联的中断;<br>1: 使能与对应中断向量关联的中断 |

表 3.20 调试中断使能寄存器 DBIER0

| 位    | 名 称          | 描 述     | 可访问性 | HW 复位 | 读 位 解 释                                 |

|------|--------------|---------|------|-------|-----------------------------------------|

| 2~15 | DBIE2~DBIE15 | 调试中断使能位 | 读/写  | 0     | 0: 禁止与对应中断向量关联的中断;<br>1: 使能与对应中断向量关联的中断 |

DBIER 使能的可屏蔽中断被定义为时间关键中断。当 CPU 在实时模式中停止工作时，唯一服务的中断就是时间关键中断，它们也可在 IER 中被启用。

读 DBIER 来鉴定时间关键中断，写 DBIER 来启动和禁止时间关键中断。设置相应位来启动中断，将相应位清零来禁止中断。图 3.10 和图 3.11 分别描述了 DBIER1 和 DBIER0。

图 3.10 调试中断寄存器 DBIER1

图 3.11 调试中断寄存器 DBIER0

- 注意：① DBIER 不受软件复位指令影响，在使用实时仿真模式之前要初始化 DBIER；

② 所有的 DBIER 位都被 DSP 硬件复位清零来禁止一切时间关键中断。

### 3.1.8 循环控制寄存器

循环控制寄存器包括单循环寄存器和块循环寄存器。单循环寄存器用于重复单个指令，块循环寄存器用于重复一块或多块指令。

#### 1. 单循环寄存器 (RPTC, CSR)

16 位的单循环指令寄存器 RPTC 和 CSR 用来重复单循环指令(或者并行执行的两条单循环指令)。在第一次执行前重复数  $N$  被转入单循环计数器 (RPTC) 中；当第一次执行完成后，指令又被执行  $N$  次。因此，总执行次数为  $N+1$ 。

在一些无条件单循环指令语句里，可以使用计算单循环寄存器 (CSR) 来确定重复数  $N$ 。在第一次指令执行或指令对重复前 CSR 里的值会复制到 RPTC 中。RPTC 和 CSR 有 16 位，可以对一条指令进行多达 65536 次连续执行 (第一次执行加 65535 次循环)。

#### 2. 块循环寄存器 (BRC0, BRC1, BRS1, RSA0, RSA1, REA0, REA1)

块循环指令可以实现重复指令块的循环。可以将一个块循环嵌套在另一个中，生成一个内 (1 层) 循环和一个外 (0 层) 循环。表 3.21 列出了与 0 层和 1 层相关的 C55x 寄存器，这些寄存器将受 C54x 兼容模式位的影响。

表 3.21 块循环寄存器

| 0 层循环寄存器 |                                        | 1 层循环寄存器 (C54CM=1 时不使用) |                                                                                                                               |

|----------|----------------------------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| 寄存器      | 说 明                                    | 寄存器                     | 说 明                                                                                                                           |

| BRC0     | 块循环计数器 0。该 16 位寄存器记录了指令块初始循环执行后的重复次数   | BRC1                    | 块循环计数器 1。该 16 位寄存器记录了指令块初始循环执行后的重复次数                                                                                          |

| RSA0     | 块循环初始地址寄存器 0。该 24 位寄存器记录了指令块中首条指令的地址   | RSA1                    | 块循环初始地址寄存器 1。该 24 位寄存器记录了指令块中首条指令的地址                                                                                          |

| REA0     | 块循环结束地址寄存器 0。该 24 位寄存器记录了指令块中最后一条指令的地址 | REA1                    | 块循环结束地址寄存器 1。该 24 位寄存器记录了指令块中最后一条指令的地址                                                                                        |

|          |                                        | BRS1                    | BRC1 保存寄存器。任何时候只要 BRC1 被装入，BRS1 就被装入相同值。在 1 层循环执行时 BRS1 内容不会修改。每当 1 层循环被触发时，BRS1 使 BRC1 重新初始化，使得 BRC1 可在 0 层循环外初始化，减少了每次重复的时间 |

##### (1) 若 C54CM=0，为 C55x 原始模式

当循环被激活并有中断或响应执行时，CPU 会把激活的循环记录下来。这会调用子程序中位于 0 层的资源。当 CPU 对块循环指令进行译码时，它首先决定是否有循环已经被执行。若 CPU 发现激活的 0 层循环，它将使用 1 层循环寄存器，否则使用 0 层寄存器。

##### (2) 若 C54CM=1，为 C55x 兼容模式

块循环只能激活 0 层的循环寄存器。1 层的循环寄存器不被使用。通过上下关系的保存/恢复和块循环激活标志 (BRAF) 可以在 C54x DSP 上执行嵌套块循环操作。块循环指令对

BRAF 置位，并且当 BRC0 包含 0 时，在块循环操作的最后 BRAF 会被清零。

当块循环在 C54x 兼容模式下开始时，BRAF 位会自动设置以表明有循环正在进行。若程序要求从 C54CM=1 模式到 C54CM=0 模式切换，在切换前或切换时 BRAF 位必须清零。有三种选择：

- 等待直到循环结束（BRAF 自动清零）后，清零 C54CM；

- 将 BRAF 清零后清零 C54CM；

- 利用修改状态寄存器 ST1\_55 的指令同时清零 BRAF 和 C54CM。

注意：要确保 0 循环的最后三条指令不被写入 BRC0。同样，也要确保 1 循环的最后三条指令不被写入 BRC1。

### 3.1.9 状态寄存器 (ST0\_55~ST3\_55)

4 个 16 位的状态寄存器（如图 3.12 所示）含有控制位和标志位。控制位影响 C55x DSP 的运行，标志位则反映 DSP 当前状态或指示运行结果。图 3.12 中的阴影位表示向状态寄存器保护地址的写操作无效，在进行读操作时这个位总是 0；R/W 表示可进行读/写访问；-0 和-1 表示 DSP 复位后的值。

| ST0_55 |       |       |          |              |        |       |              |  |

|--------|-------|-------|----------|--------------|--------|-------|--------------|--|

| 15     | 14    | 13    | 12       | 11           | 10     | 9     | 8~0          |  |

| ACOV2  | ACOV3 | TC1   | TC2      | CARRY        | ACOV0  | ACOV1 | DP           |  |

| R/W-0  | R/W-0 | R/W-1 | R/W-1    | R/W-1        | R/W-1  | R/W-0 | R/W-00000000 |  |

| ST1_55 |       |       |          |              |        |       |              |  |

| 15     | 14    | 13    | 12       | 11           | 10     | 9     | 8            |  |

| BRAF   | CPL   | XF    | HM       | INTM         | M40    | SATD  | SXMD         |  |

| R/W-0  | R/W-0 | R/W-1 | R/W-0    | R/W-1        | R/W-0  | R/W-0 | R/W-1        |  |

| 7      | 6     | 5     | 4        | 3            | 2      | 1     | 0            |  |

| C16    | FRCT  | C54CM | ASM      |              |        |       |              |  |

| R/W-0  | R/W-0 | R/W-1 | R/W-0000 |              |        |       |              |  |

| ST2_55 |       |       |          |              |        |       |              |  |

| 15     | 14    | 13    | 12       | 11           | 10     | 9     | 8            |  |

| ARMS   | 保留    |       | DBGM     | EALLOW       | RDM    | 保留    | CDPLC        |  |

| R/W-0  | R-11b |       | R/W-1    | R/W-0        | R/W-0  | R-0   | R/W-0        |  |

| 7      | 6     | 5     | 4        | 3            | 2      | 1     | 0            |  |

| AR7LC  | AR6LC | AR5LC | AR4LC    | AR3LC        | AR2LC  | AR1LC | AR0LC        |  |

| R/W-0  | R/W-0 | R/W-0 | R/W-0    | R/W-0        | R/W-0  | R/W-0 | R/W-0        |  |

| ST3_55 |       |       |          |              |        |       |              |  |

| 15     | 14    | 13    | 12       | 11           | 10     | 9     | 8            |  |

| CAFZR  | CAEN  | CACLR | HINT     | 保留（总是写1100b） |        |       |              |  |

| R/W-0  | R/W-0 | R/W-0 | R/W-1    | R/W-1100b    |        |       |              |  |

| 7      | 6     | 5     | 4        | 3            | 2      | 1     | 0            |  |

| CBERR  | MPNMC | SATA  | 保留       | 保留           | CLKOFF | SMUL  | SST          |  |

| R/W-0  | R/W-0 | R/W-0 | R/W-0    | R/W-0        | R/W-0  | R/W-0 | R/W-0        |  |

图 3.12 状态寄存器

ST0\_55, ST1\_55 和 ST3\_55 均可在两个地址中访问。在一个地址中,所有的 TMS320C55x 位都是可用的。在另外一个地址(被保护地址)中,图 3.12 中突出显示的阴影位是无法被修改的。

注意:①任何时候都要把 1100b (Ch) 写入 ST3\_55 的 11~8 位;②某些没有指令 Cache 的 C55x 器件不使用 CAFRZ、CAEN 和 CACLR 位。

## 3.2 存储器和 I/O 空间

C55x DSP 为存储空间的访问提供了统一的数据/程序空间和 I/O 空间。数据空间地址用来访问通用型存储器和存储器映射 CPU 寄存器,程序空间地址用于 CPU 从存储器中读取指令,I/O 空间用于和外设之间进行双向通信。此外,还有一个片上启动加载器用来帮助加载代码和数据到内存中。

### 3.2.1 存储器概述

所有的 16MB 存储空间都可作为程序寻址空间或数据寻址空间(如图 3.13 所示)。当 CPU 利用程序空间从存储器中读取程序指令时,使用 24 位的地址访问相关字节;当程序访问数据空间时,它使用 23 位的地址访问相关的 16 位字节。在这两种情况下,地址总线都是 24 位值,不过在数据寻址时,地址总线上的最低位要强制为 0。

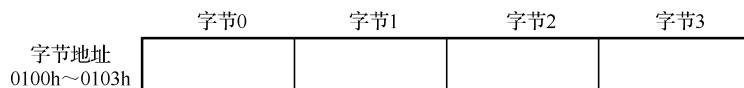

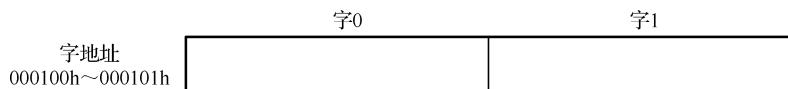

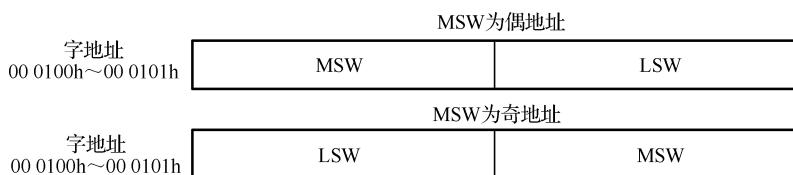

|          | 数据空间地址<br>(十六进制范围)                      | 数据/程序内存 | 程序空间地址<br>(十六进制范围)                 |

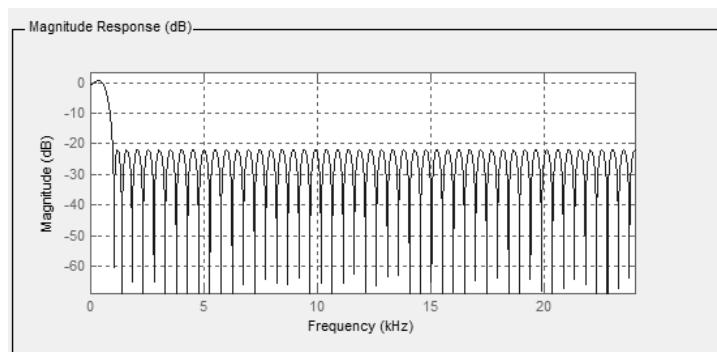

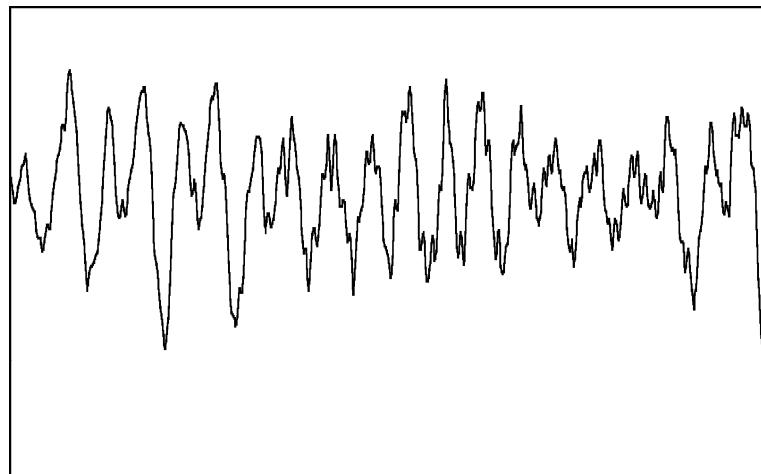

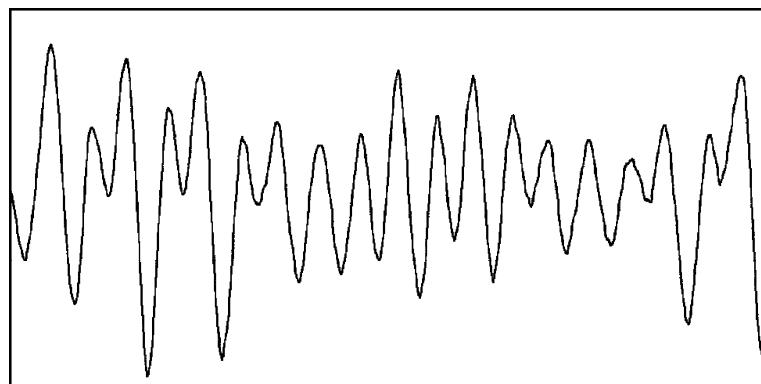

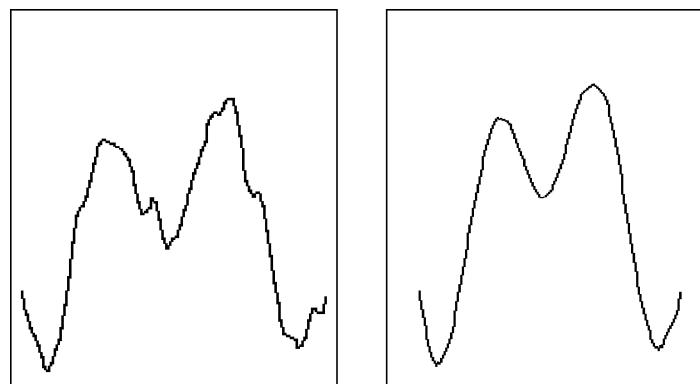

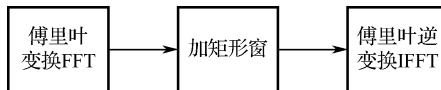

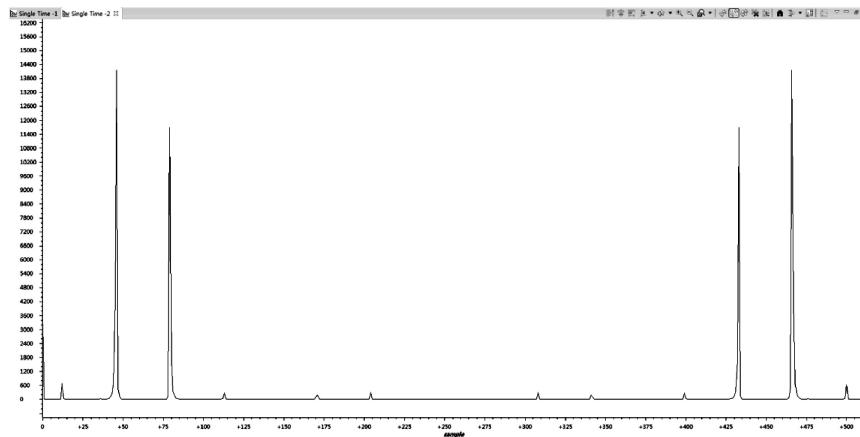

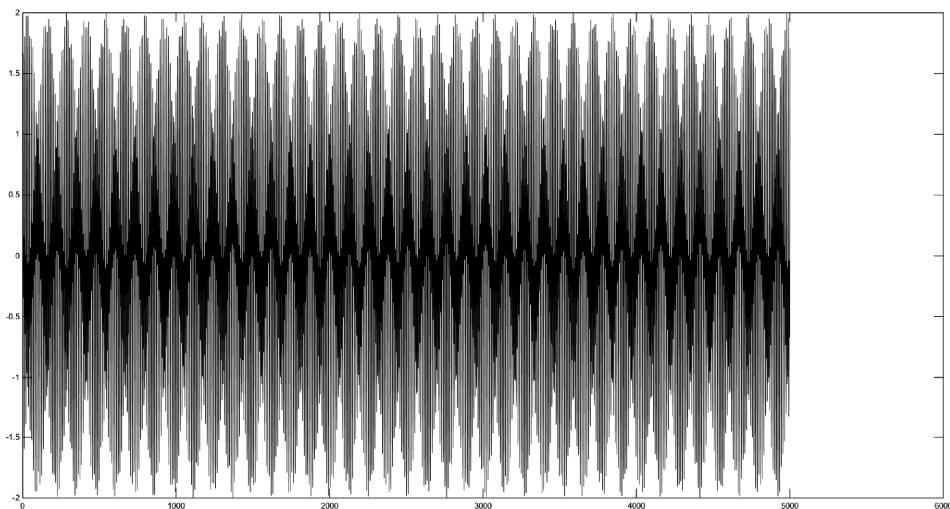

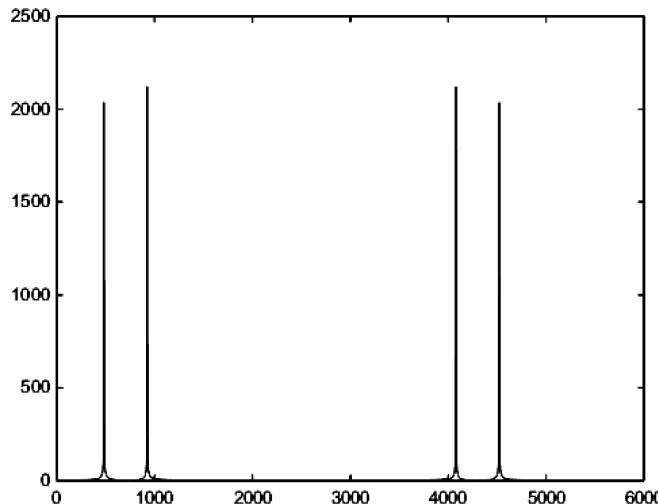

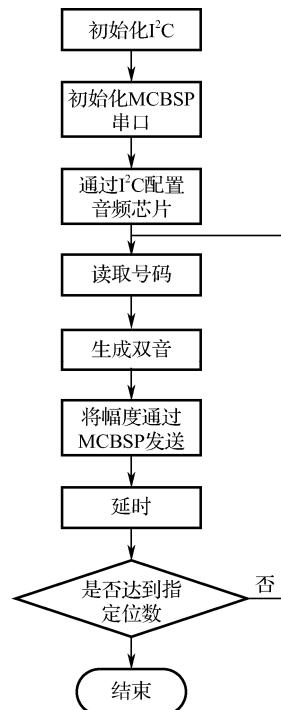

|----------|-----------------------------------------|---------|------------------------------------|