EDA 设计智汇馆高手速成系列

# PADS 电路板设计超级手册

黄杰勇 林超文 周佳辉 骆 鑫 编著

電子工業出版社

Publishing House of Electronics Industry

北京·BEIJING

## 内 容 简 介

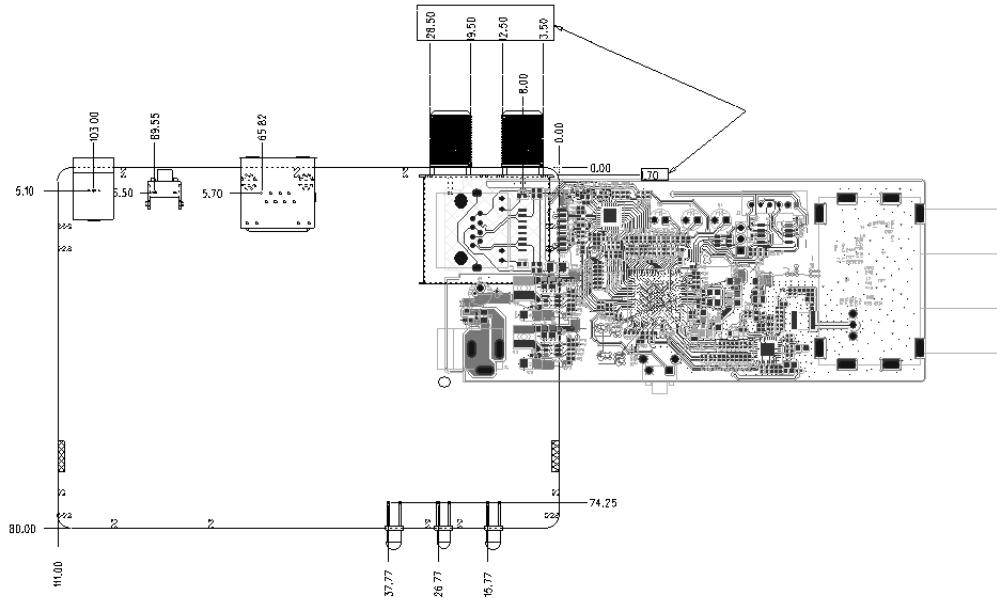

本书主要介绍印刷电路板（PCB）设计软件 PADS 的常用操作和一些设计技巧，配合大量的示意图，以实用、易懂的方式描述，让读者迅速掌握软件的操作技巧，为学习 PCB 设计打下良好的基础。

本书主要内容包括网络表篇、结构篇、软件参数设置、封装、布局、布线、设计验证、文件输出、实战技巧。

本书适合从事 PCB 设计的人员阅读，也可作为工程师、在校学生 PCB 设计的参考手册。

## 图书在版编目 (CIP) 数据

PADS 电路板设计超级手册/黄杰勇等编著. —北京：电子工业出版社，2016.11

(EDA 设计智汇馆高手速成系列)

ISBN 978 - 7 - 121 - 30044 - 8

I. ①P… II. ①黄… III. ①印刷电路 - 计算机辅助设计 - 应用软件 - 手册 IV. ①TN410.2 - 62

中国版本图书馆 CIP 数据核字 (2016) 第 240298 号

策划编辑：张 迪 (zhangdi@ phei. com. cn)

责任编辑：张 迪

印 刷：

装 订：

出版发行：电子工业出版社

北京市海淀区万寿路 173 信箱 邮编 100036

开 本：787 × 1092 1/16 印张：14.75 字数：377 千字

版 次：2016 年 11 月第 1 版

印 次：2016 年 11 月第 1 次印刷

印 数：3 000 册 定价：39.80 元

凡所购买电子工业出版社图书有缺损问题，请向购买书店调换。若书店售缺，请与本社发行部联系，联系及邮购电话：(010)88254888, 88258888。

质量投诉请发邮件至 zlts@ phei. com. cn，盗版侵权举报请发邮件至 dbqq@ phei. com. cn。

本书咨询联系方式：(010) 88254590; wangjd@ phei. com. cn。

# 前　　言

PADS 是 Mentor Graphics 公司的电路原理图和印刷电路板（Printed Circuit Board，PCB）设计工具套件，该软件是国内从事电路设计的工程师喜欢使用的电路设计软件之一，是 PCB 设计领域的用户常用的工具软件。PADS 以其强大的交互式布局布线功能，操作便捷、易上手等特点，在消费电子、医疗电子、通信、半导体等活跃的工业领域得到了广泛应用。撰写本书的目的是通过 PADS 软件的各种示例操作、应用技巧，为广大使用 PADS 软件的设计者、使用者、学习爱好者在设计 PCB 中提供指导，提高设计效率。

目前市场上介绍 PADS 的教材很多，主要以介绍软件使用为主。本书则以 PADS 软件设计 PCB 的一些常见操作和技巧进行汇总，按照 PCB 设计的流程，从网络导入、结构开始，进而介绍软件参数的设置、器件的封装、元器件的布局、PCB 的走线，再到设计验证和相关文件的输出，最后介绍实战技巧。对于初学者，软件使用不熟悉，PCB 设计的效率会降低。本书汇总的常见设置和技巧，实用性很强。例如，第 1 章里介绍了 OrCAD Capture 和 Altium Designer 原理图转 PADS Logic 原理图的具体方法，非常适用于解决文件格式互转的问题；第 3 章的软件参数设置，汇总了 PCB 设计中常见的设置问题，像隐藏过孔 X 的图像、圆弧拐角等；第 5 章里介绍的 Net 标注法布局、飞线引导法布局、输入坐标布局、组合布局、BGA 器件布局，这些方法能大大提高设计人员 PCB 布局的效率；第 6 章介绍里 PCB 走线的常用设置；第 9 章有具体例子的设计技巧和注意事项：时钟电路、电源模块、HDMI 接口、USB 接口、耳机接口、以太网接口等。本书共 9 章，具体内容以下：

- 第 1 章：网络表

- 第 2 章：结构篇

- 第 3 章：软件参数与规则设置

- 第 4 章：封装

- 第 5 章：布局

- 第 6 章：布线

- 第 7 章：设计验证

- 第 8 章：PADS logic 文件输出

- 第 9 章：实战技巧

这是一本基于 PADS 电路板设计的参考工具书，内容循序渐进，通俗易懂，图文并茂，读者如果想牢牢掌握具体的技巧，需要不断练习、实践，只有在实践中通过反思积累才能指导实践。

参加本书编写的有黄杰勇、林超文、周佳辉、骆鑫。本书在编写过程中无论从资料收集还是技术交流都得到国内同行的大力支持，在此表示衷心的感谢。

由于时间短仓促，加之作者水平有限，书中难免存在缺点和不足之处，敬请读者批评指正。

编著者

2016 年 7 月 20 日

# 目 录

|                                                |    |

|------------------------------------------------|----|

| <b>第1章 网络表 .....</b>                           | 1  |

| 1. 1 PADS Logic 同步网表到 PADS Layout .....        | 1  |

| 1. 2 导入第三方网络表前配置库文件.....                       | 5  |

| 1. 3 OrCAD 原理图导出 ASC 网表 .....                  | 7  |

| 1. 4 导出 Altium Designer 原理图网表 .....            | 11 |

| 1. 5 导入网络表 (. asc 文件) .....                    | 16 |

| 1. 6 OrCAD Capture 原理图转 PADS Logic 原理图 .....   | 17 |

| 1. 7 Altium Designer 原理图转 PADS Logic 原理图 ..... | 21 |

| 1. 8 PADS Logic 原理图和 PADS Layout 的交互 .....     | 23 |

| 1. 9 导入第三方网表提示找不到元件 .....                      | 24 |

| 1. 10 成功导入 OrCAD 的网表后没有 Value 值 .....          | 25 |

| <b>第2章 结构篇 .....</b>                           | 27 |

| 2. 1 PADS Layout 导入 DXF 结构图 .....              | 27 |

| 2. 2 两种导入 DXF 文件方法的区别 .....                    | 29 |

| 2. 3 调出结构图中的隐藏标注 .....                         | 30 |

| 2. 4 在设计中导入新结构 .....                           | 32 |

| 2. 5 使用导入的方法—出现比导出导入格式版本高 .....                | 35 |

| 2. 6 超出最大数据库坐标值 .....                          | 35 |

| 2. 7 使用 2. 6 节的方法导入后还是空白 .....                 | 38 |

| 2. 8 导入的结构图比实际小 .....                          | 41 |

| 2. 9 2D 线转换板框 .....                            | 43 |

| 2. 10 绘制生成板框 .....                             | 47 |

| 2. 11 设置原点 .....                               | 51 |

| 2. 12 摆放结构器件 .....                             | 52 |

| 2. 13 将结构图放置到其他层 .....                         | 59 |

| 2. 14 覆铜时提示尝试减小平滑半径和覆铜边框宽度 .....               | 61 |

| 2. 15 板框被选中却不能移动 .....                         | 62 |

| <b>第3章 软件参数与规则设置 .....</b>                     | 63 |

| 3. 1 鼠标光标设置 .....                              | 63 |

| 3. 2 更改设计单位 .....                              | 64 |

| 3. 3 走线显示不正常 .....                             | 65 |

| 3. 4 备份文件设置 .....                              | 66 |

| 3. 5 绘图或走线时改变线的角度 .....                        | 67 |

| 3. 6 DRC 设置 .....                              | 68 |

| 3. 7 长度最小化 .....                               | 68 |

| 3. 8 栅格设置 .....                                | 70 |

| 3. 9 对象捕获 .....                                | 71 |

| 3. 10 添加泪滴 .....                               | 71 |

|            |                       |     |

|------------|-----------------------|-----|

| 3.11       | 转化为空心过孔               | 72  |

| 3.12       | 显示保护的导线               | 74  |

| 3.13       | 热焊盘中正交，斜交，过孔覆盖的区别     | 75  |

| 3.14       | 隐藏过孔 X 的图像            | 76  |

| 3.15       | 移除碎铜                  | 77  |

| 3.16       | PADS 各层的用途和作用         | 79  |

| 3.17       | Layer25 层的作用          | 79  |

| 3.18       | 无平面、CAM 平面和分割/混合平面的区别 | 80  |

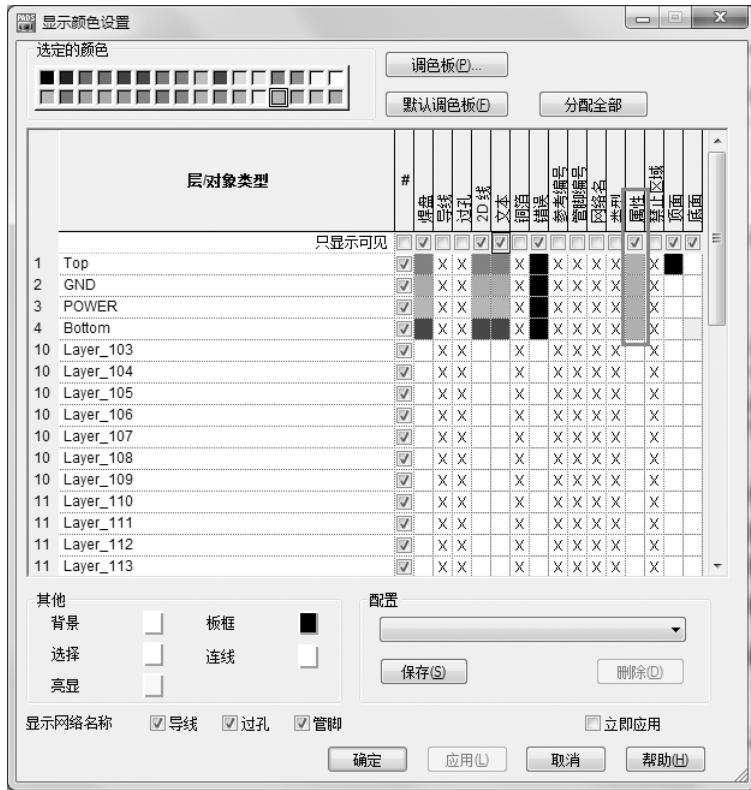

| 3.19       | 颜色设置                  | 81  |

| 3.20       | 原点设置                  | 83  |

| 3.21       | 设置原点——元器件中心           | 83  |

| 3.22       | 设置原点——斜交拐角            | 84  |

| 3.23       | 设置原点——圆弧拐角            | 84  |

| 3.24       | 板层层数设置                | 85  |

| 3.25       | 默认线宽线距设置              | 86  |

| 3.26       | 建立类规则                 | 87  |

| 3.27       | BGA 元器件规则设置           | 88  |

| 3.28       | 网络规则设置                | 90  |

| 3.29       | 层未对布线启用               | 90  |

| 3.30       | 布线中过孔设置               | 90  |

| 3.31       | 新建过孔的设置               | 91  |

| 3.32       | 常用的过孔大小               | 92  |

| 3.33       | 修改元件边框宽度              | 92  |

| 3.34       | 消除拐角处的方框              | 93  |

| 3.35       | 新添加的文本有边框             | 93  |

| 3.36       | 自动填充                  | 94  |

| 3.37       | 自交叉多边形                | 94  |

| 3.38       | 底面视图的作用               | 95  |

| 3.39       | 快速显示整板                | 95  |

| 3.40       | 找不到工具栏                | 96  |

| 3.41       | 鼠标中键缩放失灵和删除自定义快捷键     | 98  |

| 3.42       | 切换中英文界面               | 98  |

| 3.43       | 笔记本电脑 Fn + 功能键        | 99  |

| 3.44       | 启动软件不进入欢迎使用界面         | 99  |

| <b>第4章</b> | <b>封装</b>             | 100 |

| 4.1        | 封装编辑器                 | 100 |

| 4.2        | 元件中心的热焊盘              | 100 |

| 4.3        | 异形封装的创建               | 101 |

| 4.4        | 用封装向导创建封装             | 102 |

| 4.5        | 封装向导中行距三个“选项”的区别      | 103 |

| 4.6        | 连续放置相同间距的焊盘           | 103 |

| 4.7        | 定原点于元器件中心             | 104 |

| 4.8        | 元件丝印标识                | 105 |

|            |                          |            |

|------------|--------------------------|------------|

| 4.9        | 修改 BGA 封装上端点编号大小 .....   | 106        |

| 4.10       | 金属化过孔和非金属化过孔 .....       | 107        |

| 4.11       | 单独修改元器件 PCB 封装 .....     | 108        |

| 4.12       | 如何把自己的封装给别人 .....        | 109        |

| <b>第5章</b> | <b>布局 .....</b>          | <b>111</b> |

| 5.1        | 栅格布局法 .....              | 111        |

| 5.2        | 对齐命令布局 .....             | 112        |

| 5.3        | Net 标注法布局 .....          | 113        |

| 5.4        | 飞线引导法布局 .....            | 114        |

| 5.5        | 输入坐标布局 .....             | 114        |

| 5.6        | 组合布局 .....               | 115        |

| 5.7        | 整个模块旋转 .....             | 116        |

| 5.8        | BGA 器件布局 .....           | 117        |

| 5.9        | 推挤元器件 .....              | 118        |

| 5.10       | 不选中胶粘的元件 .....           | 118        |

| 5.11       | 导线随元器件移动 .....           | 118        |

| <b>第6章</b> | <b>布线 .....</b>          | <b>120</b> |

| 6.1        | 走线的基本操作 .....            | 120        |

| 6.2        | 打孔换层走线 .....             | 121        |

| 6.3        | 走线暂停或结束 .....            | 122        |

| 6.4        | 走线过程中导线加粗 .....          | 122        |

| 6.5        | 走线时改变线宽没反应 .....         | 123        |

| 6.6        | 走线完成后导线加粗 .....          | 123        |

| 6.7        | 走线时怎么走弧线 .....           | 125        |

| 6.8        | 走线完成后转换为弧线 .....         | 126        |

| 6.9        | 走线时选择过孔 .....            | 127        |

| 6.10       | 走线结束后更改过孔 .....          | 128        |

| 6.11       | 过孔删除不了 .....             | 128        |

| 6.12       | 虚拟过孔 .....               | 129        |

| 6.13       | 自动增加过孔 .....             | 129        |

| 6.14       | 自动包地 .....               | 131        |

| 6.15       | 走线立体包地 .....             | 132        |

| 6.16       | 调整走线或形状时移动和拉伸命令的区别 ..... | 132        |

| 6.17       | 走线如何自动保护 .....           | 132        |

| 6.18       | 显示走线长度 .....             | 133        |

| 6.19       | 回路布线 .....               | 134        |

| 6.20       | 无模命令“O”和“T”的区别 .....     | 135        |

| 6.21       | 多条平行信号线间的间距如何保持相等 .....  | 136        |

| 6.22       | 铜箔/覆铜的绘制（后分配网络） .....    | 136        |

| 6.23       | 铜箔/覆铜的绘制（先分配网络） .....    | 137        |

| 6.24       | 铜箔和覆铜的区别 .....           | 138        |

| 6.25       | 灌注、填充、平面连接的区别 .....      | 138        |

| 6.26       | 铜箔加固焊盘 .....             | 139        |

|            |                                 |            |

|------------|---------------------------------|------------|

| 6.27       | 怎样铺网格状的铜皮 .....                 | 139        |

| 6.28       | 铜箔优化全连接 .....                   | 141        |

| 6.29       | 隐藏灌注后的覆铜或连接后的平面 .....           | 142        |

| 6.30       | 灌注后内部覆铜框覆不了铜 .....              | 143        |

| 6.31       | 单个绘图形状的相互转换 .....               | 145        |

| 6.32       | 如何将已经画好的线段更改为铜箔 .....           | 145        |

| 6.33       | 绘制禁止区域 .....                    | 145        |

| 6.34       | 定位孔覆铜怎么避开 .....                 | 146        |

| 6.35       | 复用功能 .....                      | 147        |

| 6.36       | 怎么进入 ECO 功能 .....               | 148        |

| 6.37       | 在 ECO 功能上如何直接添加网络连接 .....       | 149        |

| 6.38       | 在 ECO 功能上如何直接添加元器件 .....        | 149        |

| 6.39       | 在 ECO 功能上如何直接重命名网络 .....        | 150        |

| 6.40       | 在 ECO 功能上如何直接重命名元器件 .....       | 150        |

| 6.41       | 在 ECO 功能上如何直接更改元器件 .....        | 151        |

| 6.42       | 在 ECO 功能上如何直接删除 .....           | 151        |

| 6.43       | PADS Router 显示走线长度 .....        | 152        |

| 6.44       | 区分受保护的导线和过孔 .....               | 152        |

| 6.45       | 没有保护带显示 .....                   | 153        |

| 6.46       | 保护带不明显 .....                    | 154        |

| 6.47       | BGA 封装如何设置才能自动扇出 .....          | 155        |

| 6.48       | PADS Router 中走差分线时相同网络连不上 ..... | 156        |

| 6.49       | 什么时候需要使用关联网络 .....              | 156        |

| 6.50       | PADS Router 推挤功能 .....          | 157        |

| 6.51       | 建立差分对及设置 .....                  | 158        |

| 6.52       | 选中某片区域的差分对 .....                | 159        |

| 6.53       | 无法创建差分对 .....                   | 161        |

| 6.54       | 建立等长的网络组 .....                  | 162        |

| 6.55       | 蛇形走线 .....                      | 165        |

| <b>第7章</b> | <b>设计验证 .....</b>               | <b>167</b> |

| 7.1        | 进入验证设计 .....                    | 167        |

| 7.2        | 检查连接性（开路） .....                 | 168        |

| 7.3        | 检查安全间距（短路） .....                | 169        |

| 7.4        | 验证设计时没有错误数窗口 .....              | 172        |

| 7.5        | 连接性已经解决还有飞线显示 .....             | 173        |

| 7.6        | 插件引脚未勾电镀出现连接性错误 .....           | 173        |

| 7.7        | 元件体与元件体干涉检查 .....               | 174        |

| 7.8        | 检查过孔有没有打在焊盘上 .....              | 177        |

| <b>第8章</b> | <b>PADS logic 文件输出 .....</b>    | <b>179</b> |

| 8.1        | PADS Logic 如何导出低版本 .....        | 179        |

| 8.2        | PADS Layout 如何导出低版本 .....       | 180        |

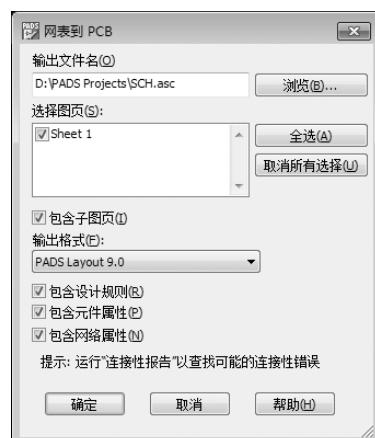

| 8.3        | PADS Logic 导出 Layout 网表 .....   | 181        |

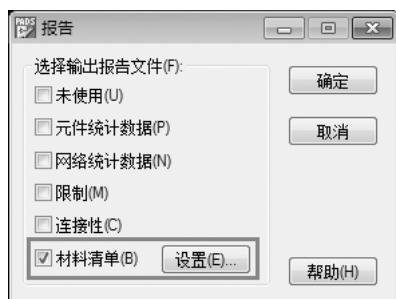

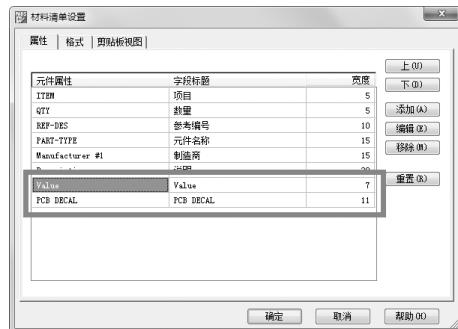

| 8.4        | PADS Logic 导出 BOM 表 .....       | 181        |

|                                            |            |

|--------------------------------------------|------------|

| 8.5 PADS Logic 查看大致 Pin 数 .....            | 183        |

| 8.6 PADS Layout 查看 Pin 脚数 .....            | 185        |

| 8.7 如何统一更改丝印大小 .....                       | 185        |

| 8.8 丝印的线宽不能修改 .....                        | 187        |

| 8.9 如何添加元件参考编号 .....                       | 187        |

| 8.10 添加文本 .....                            | 188        |

| 8.11 丝印方向 .....                            | 189        |

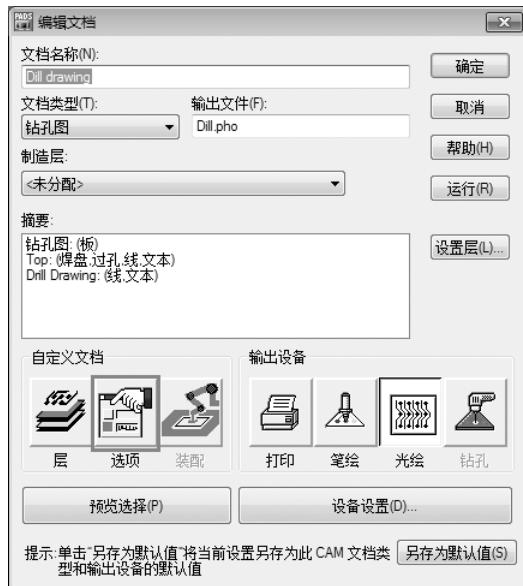

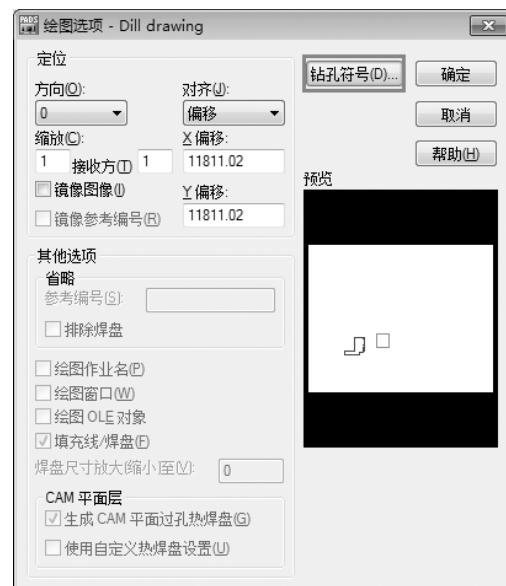

| 8.12 输出 CAM 时出现覆铜报错 .....                  | 189        |

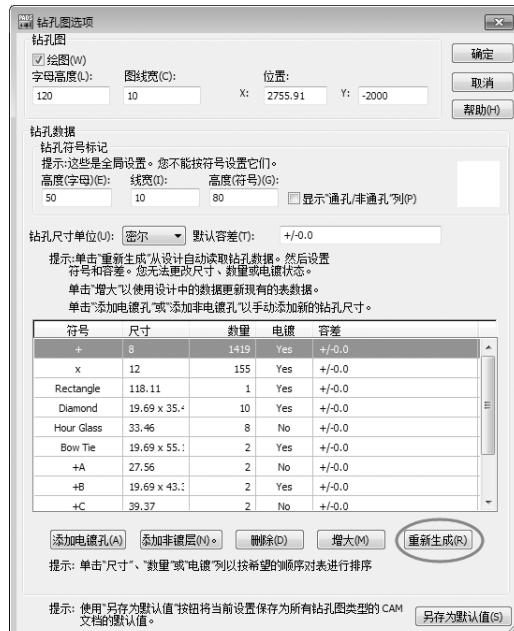

| 8.13 输出 CAM 钻孔文件时，警告没有该尺寸的符号 .....         | 189        |

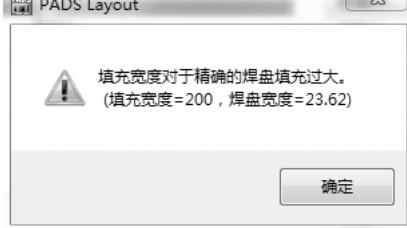

| 8.14 输出 CAM 时出现“填充宽度对于精确的焊盘填充过大”怎么解决 ..... | 191        |

| 8.15 输出 CAM 时出现“偏移过小 - 绘图将居中” .....        | 191        |

| 8.16 阻焊层 CAM “短路” .....                    | 192        |

| 8.17 异型焊盘的封装 CAM 文件如何输出 .....              | 193        |

| 8.18 输出 CAM 时钻孔误差设置 .....                  | 194        |

| 8.19 光绘文件输出 .....                          | 195        |

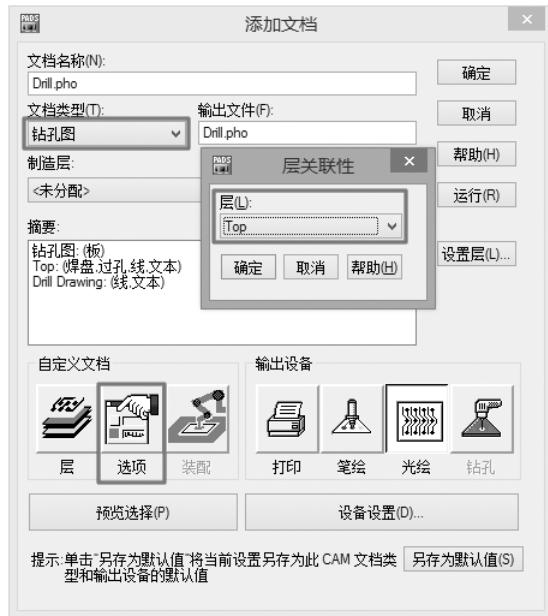

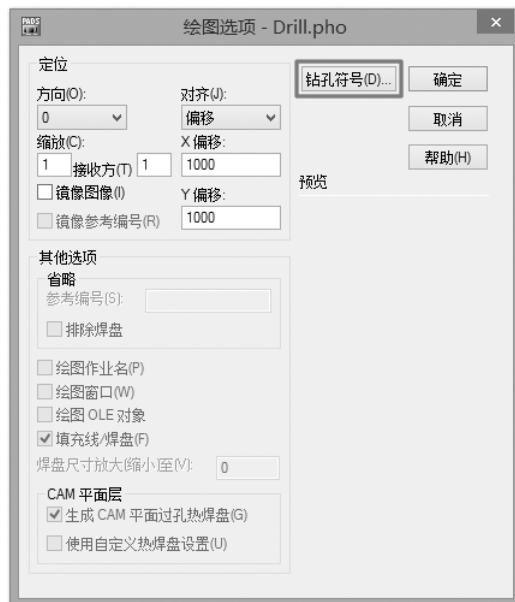

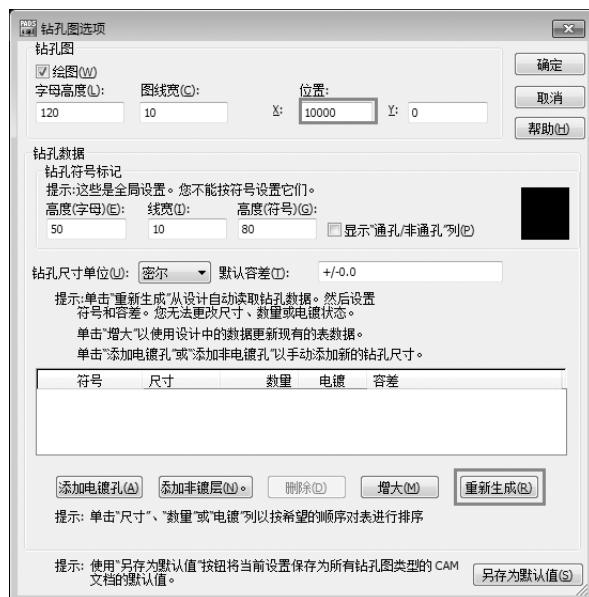

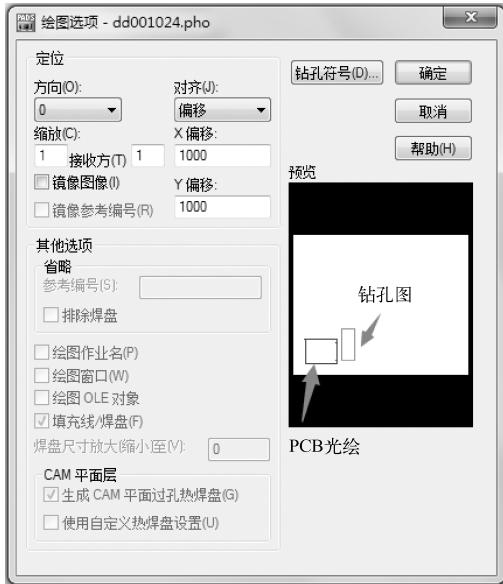

| 8.20 设置钻孔图 .....                           | 198        |

| 8.21 设置 NC 钻孔层 .....                       | 200        |

| 8.22 钢网文件过滤不需要输出的测试点 .....                 | 202        |

| 8.23 导出钢网文件和贴片坐标文件 .....                   | 203        |

| 8.24 导出 CAM 模板 .....                       | 206        |

| 8.25 导出板框 DXF .....                        | 207        |

| 8.26 导出 IPC 网表 .....                       | 207        |

| 8.27 删除历史 CAM 输出路径 .....                   | 208        |

| 8.28 PADS Logic 生成 PDF .....               | 208        |

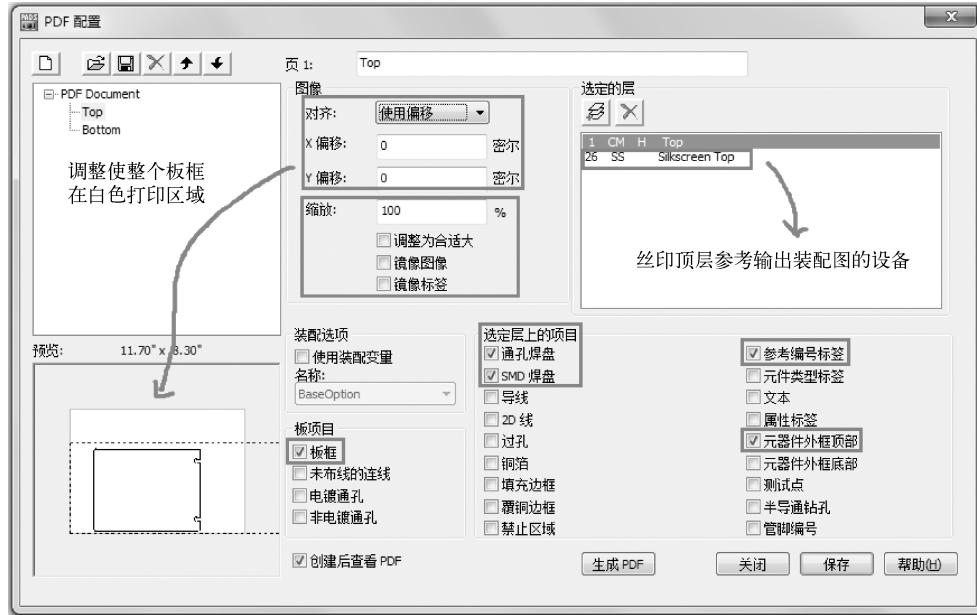

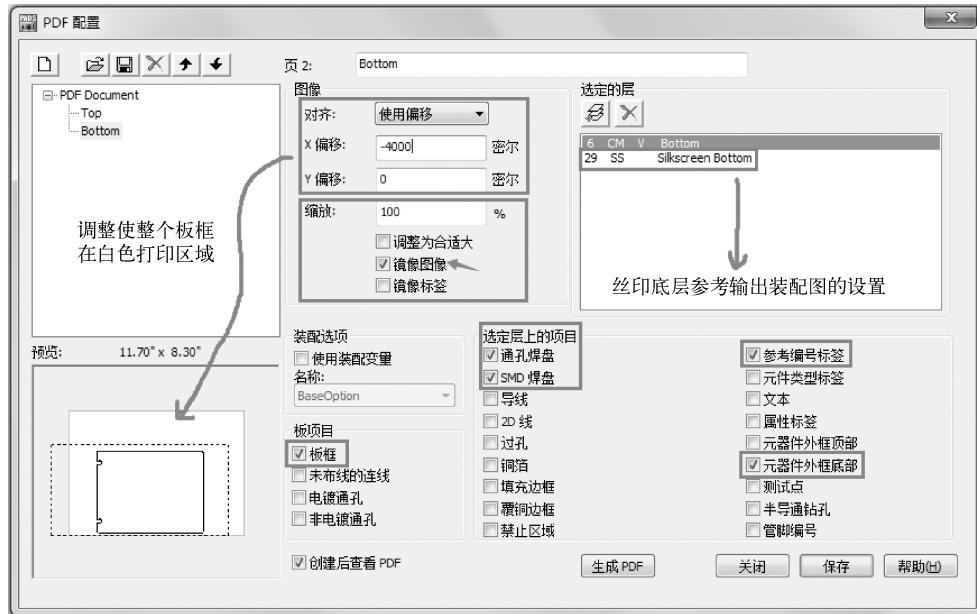

| 8.29 PADS Layout 生成 PDF 装配文件 .....         | 209        |

| 8.30 导出 1:1 的 PDF 核对封装 .....               | 212        |

| 8.31 导出位号图（带属性值） .....                     | 213        |

| 8.32 如何导出等长表 .....                         | 214        |

| <b>第9章 实战技巧 .....</b>                      | <b>216</b> |

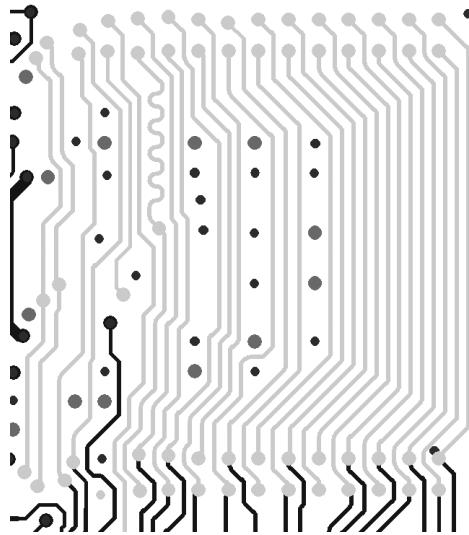

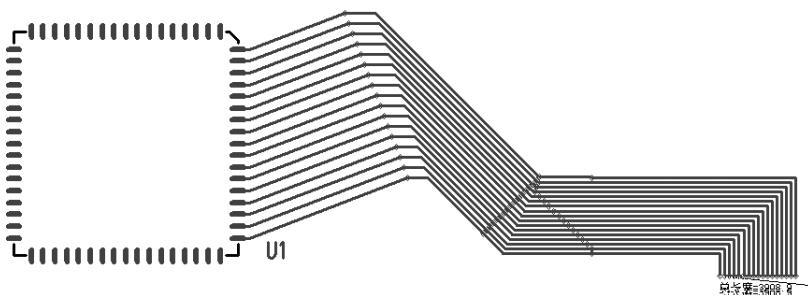

| 9.1 BUS 总线布线 .....                         | 216        |

| 9.2 时钟设计 .....                             | 218        |

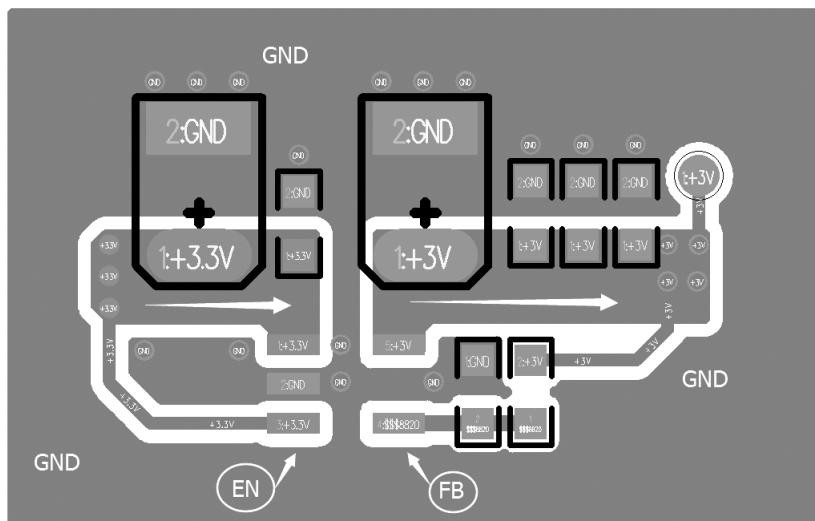

| 9.3 电源模块设计 .....                           | 219        |

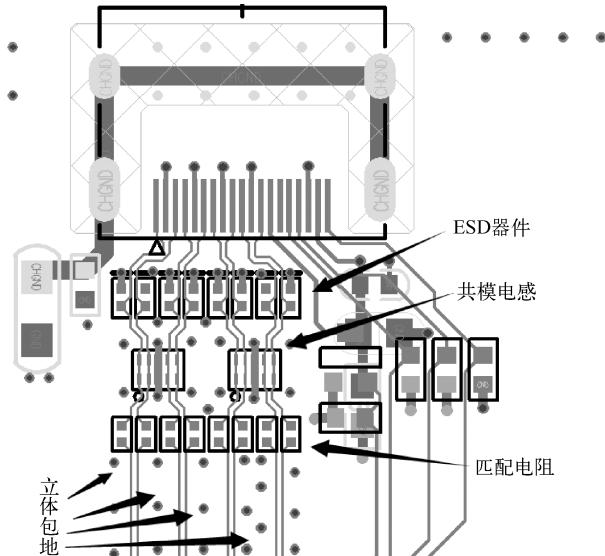

| 9.4 HDMI 设计 .....                          | 219        |

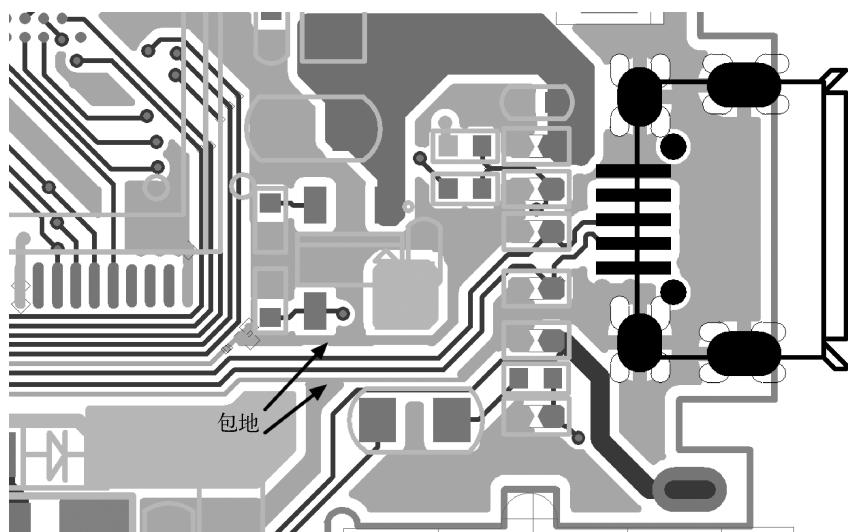

| 9.5 USB2.0 接口设计 .....                      | 220        |

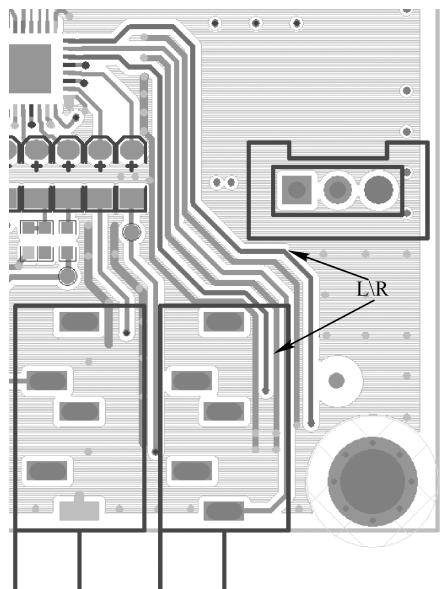

| 9.6 耳机接口设计 .....                           | 221        |

| 9.7 以太网口设计 .....                           | 221        |

| 9.8 当有重叠元素时，应该如何选择 .....                   | 221        |

| 9.9 走线 3W 原则 .....                         | 222        |

| 9.10 多层板 20H 原则 .....                      | 222        |

| 9.11 打开软件宏文件报错 .....                       | 222        |

# 第1章 网络表

原理图画好后，要将原理图中的元件参考编号、元件封装、网络名、网络连接关系等信息导入 EDA 工具中开始 PCB 的设计，而网络表就是包含所有这些信息的一个文件。

## 1.1 PADS Logic 同步网表到 PADS Layout

用 PADS Logic 绘制的原理图可以将网表直接同步到 PADS Layout。

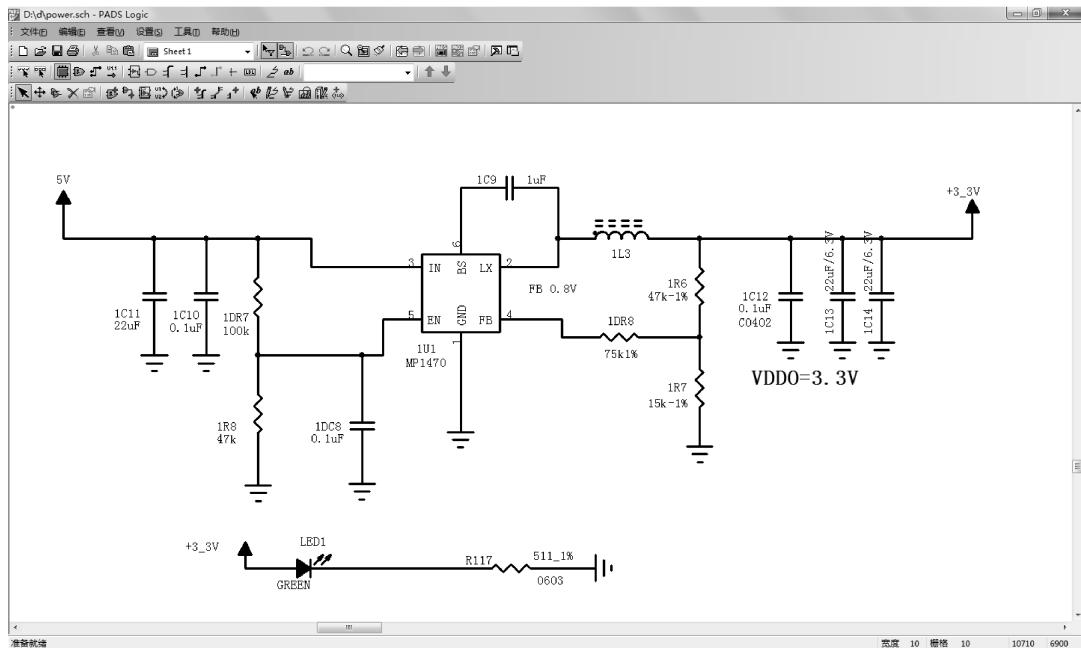

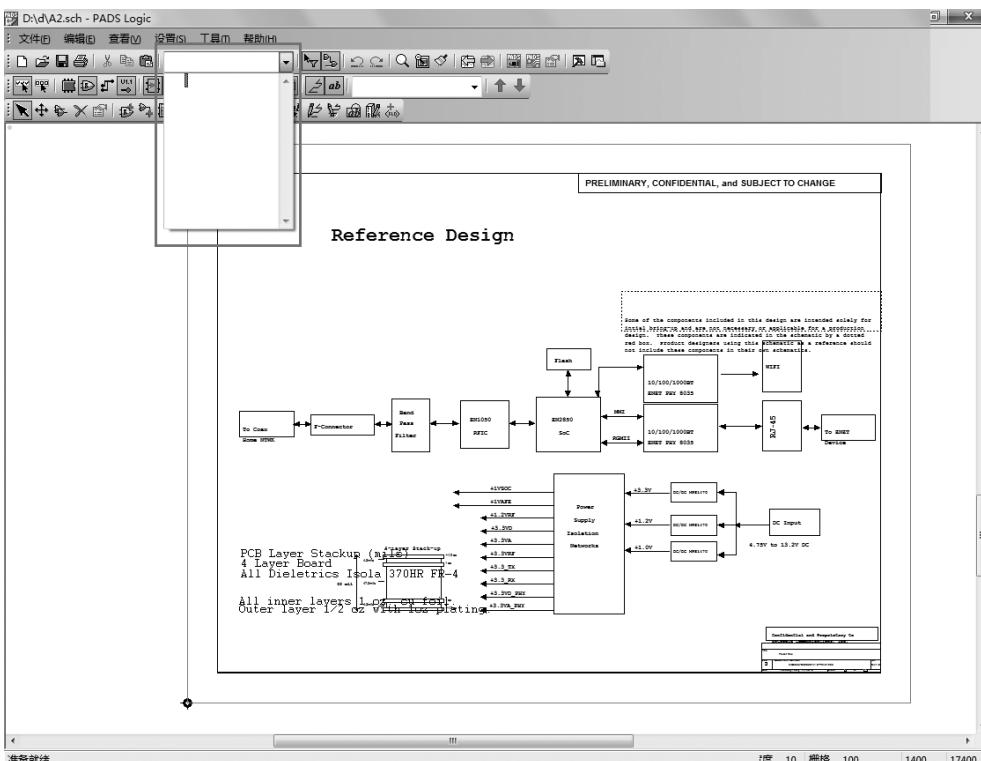

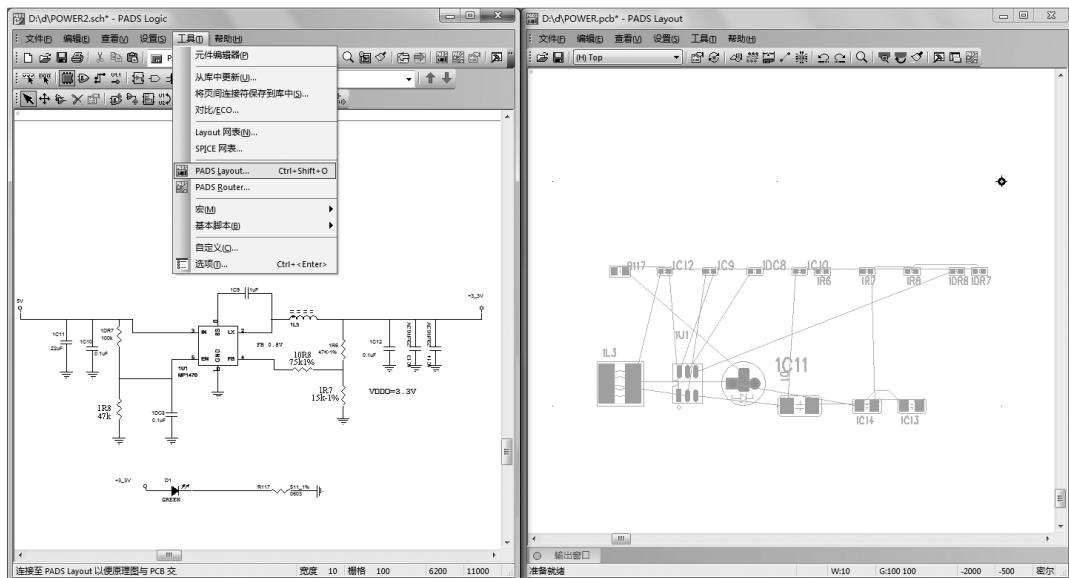

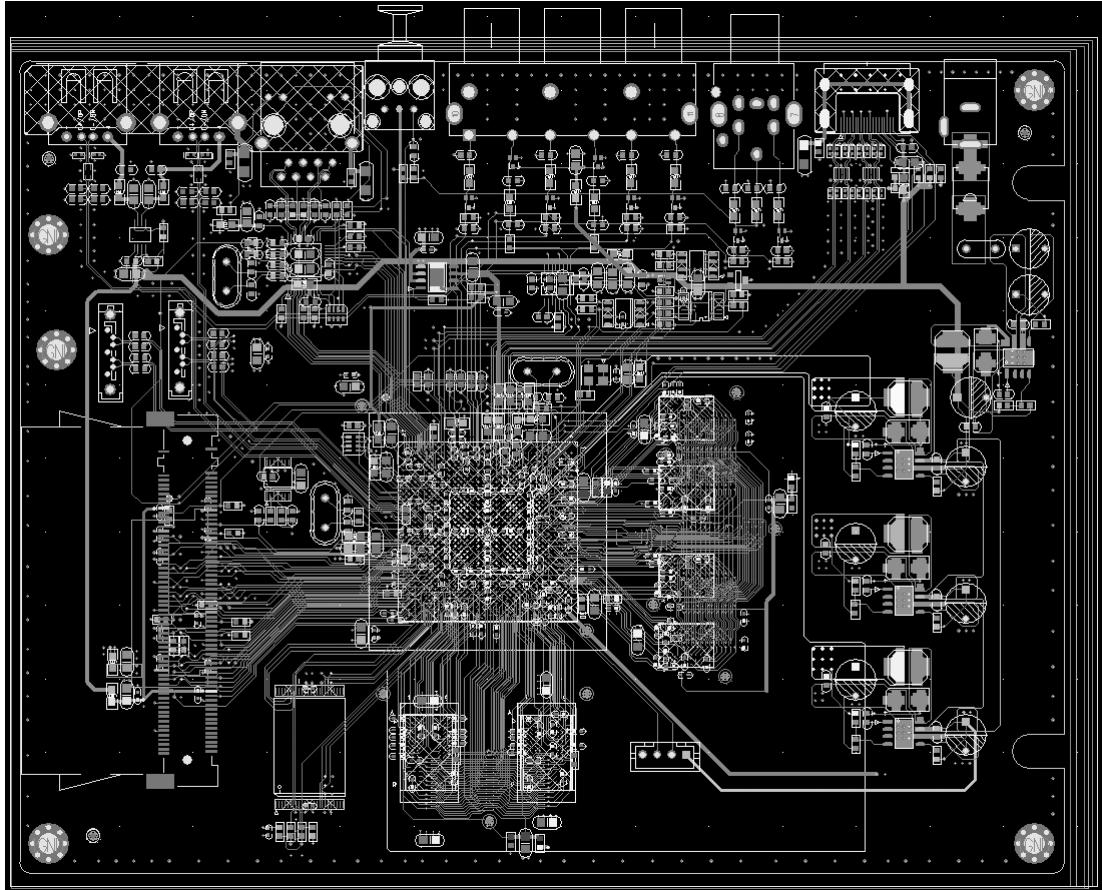

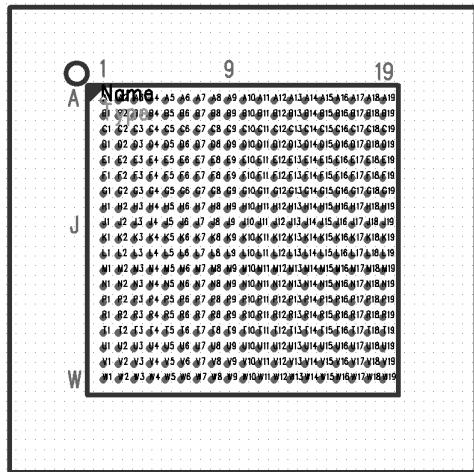

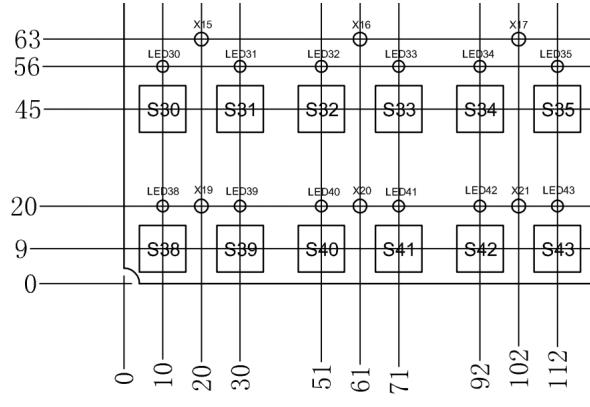

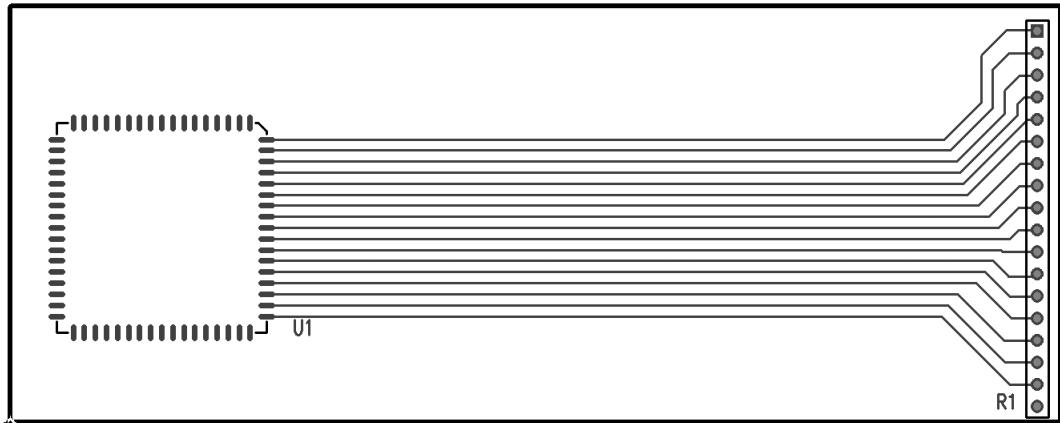

在 PADS Logic 中设计的原理图，如图 1-1 所示。

图 1-1 PADS Logic 的原理图

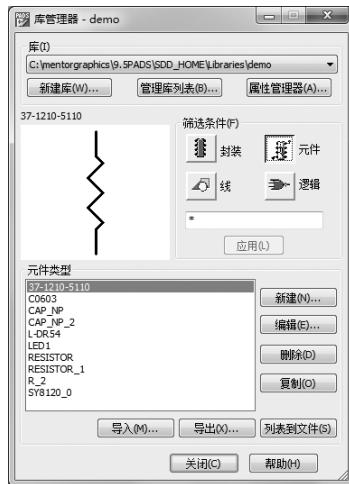

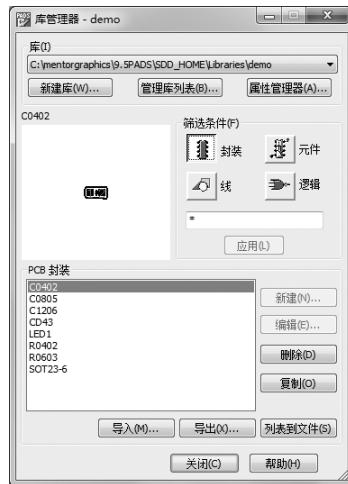

确保设计所用元器件的元件类型（Part Type）和 PCB 封装（PCB Decal）都在当前的元件库中，如图 1-2 和图 1-3 所示（本例使用的库文件为 demo）。

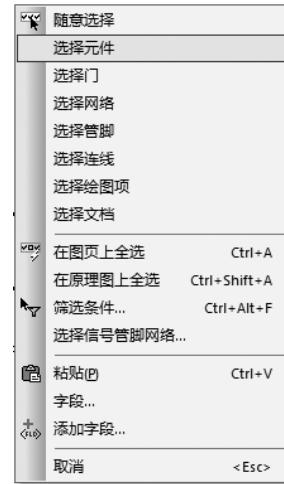

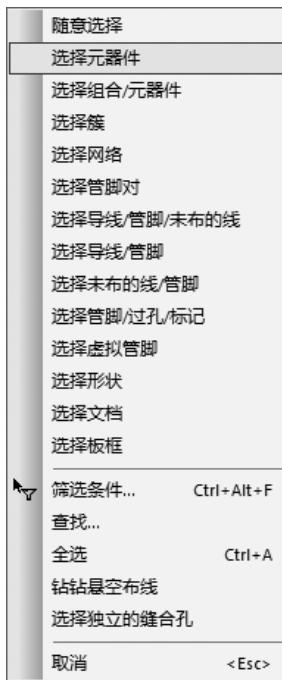

确保为原理图中的每个元件分配了 PCB 封装。在空白处单击鼠标右键，执行菜单命令【选择元件】，如图 1-4 所示。

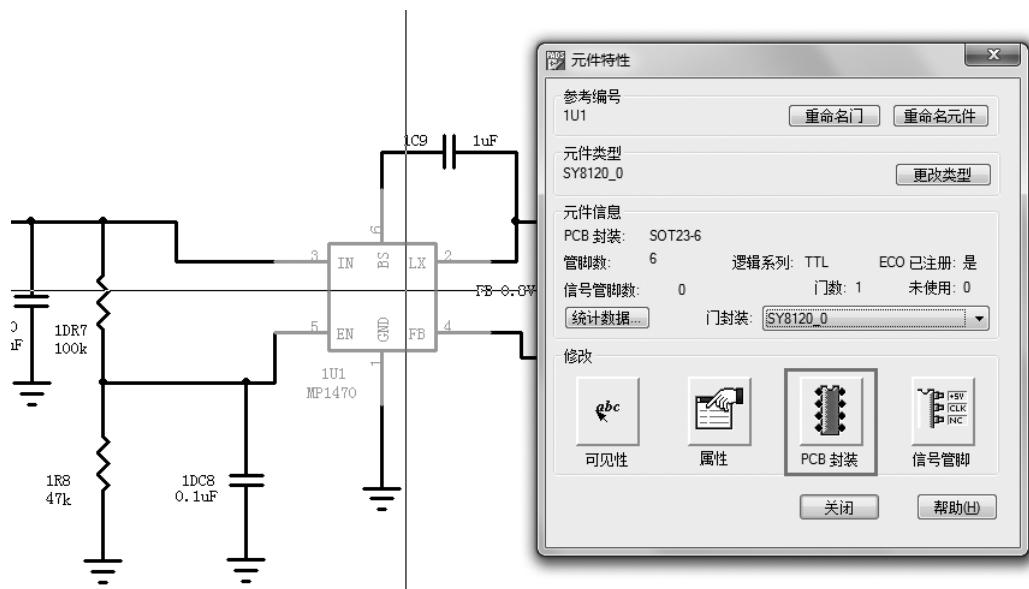

选择任意一个元件，按下组合键【Ctrl + Q】调出“元件特性”窗口，单击窗口中的“PCB 封装”按钮，如图 1-5 所示。

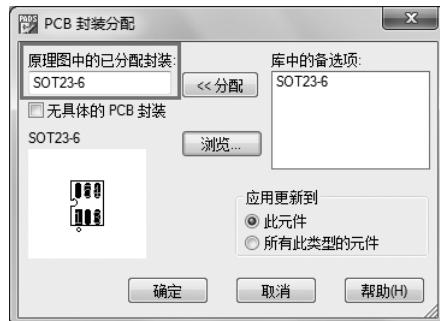

弹出如图 1-6 所示的“PCB 封装分配”窗口，确认指示框中分配了合适的封装，如果没有分配或分配有误，可单击“浏览”按钮在库中找到对应的封装分配给它。

图 1-2 本设计所需的元件类型

图 1-3 本设计所需的 PCB 封装

图 1-4 右键菜单【选择元件】项

图 1-5 “元件特性”窗口

图 1-6 元件的“PCB 封装分配”窗口

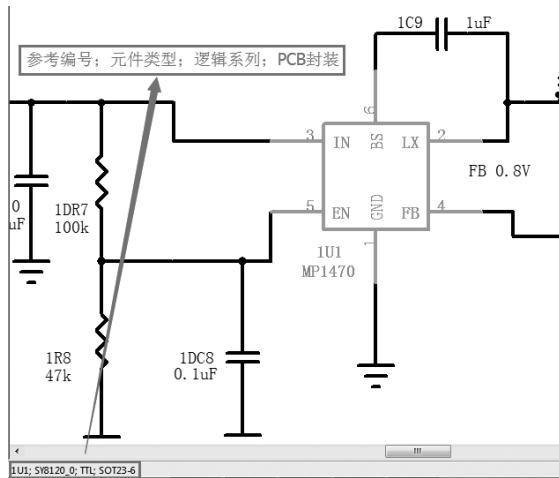

也可以选择元件后在窗口的左下侧状态栏上看到元件信息的概览，如图 1-7 所示。

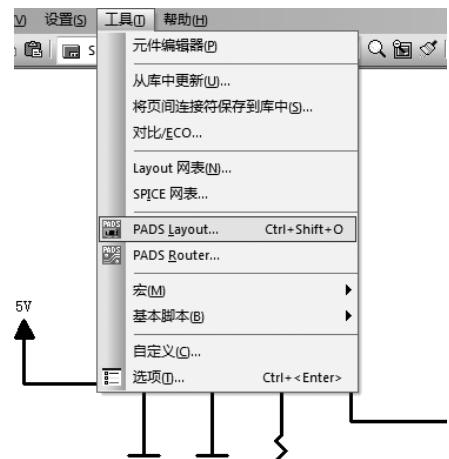

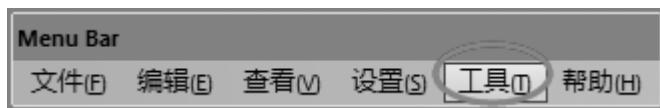

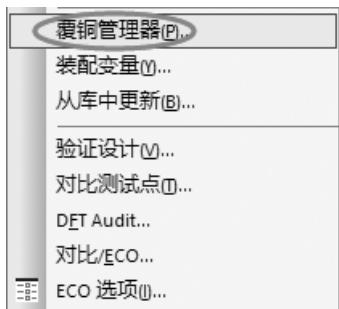

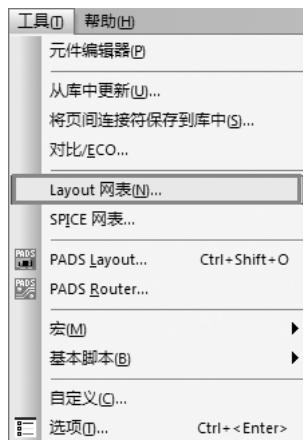

确定每个元件都分配了对应的 PCB 封装之后，单击菜单栏的【工具】，在下拉菜单中执行菜单命令【PADS Layout...】，如图 1-8 所示。

图 1-7 对应元件的信息概览

图 1-8 菜单命令【PADS Layout...】

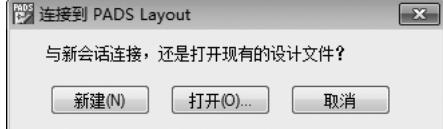

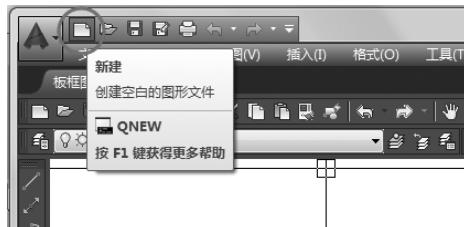

如果在这操作之前没有打开 PADS Layout 的话，则会弹出如图 1-9 所示的对话框，单击【新建】按钮。

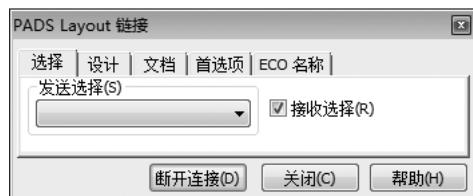

弹出“PADS Layout 链接”的窗口，如图 1-10 所示。

图 1-9 新建或打开 PCB 设计对话框

图 1-10 “PADS Layout 链接”对话框

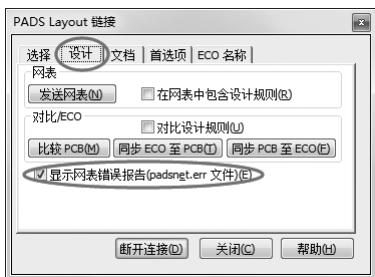

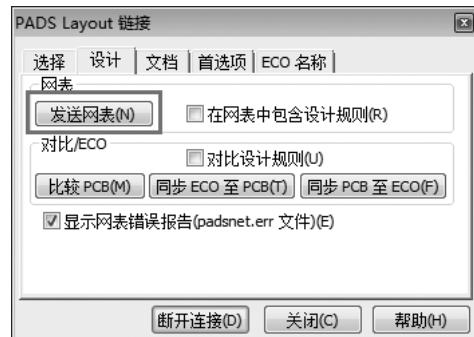

“设计”标签中，设置如图 1-11 所示。

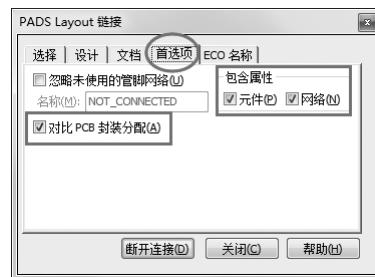

“首选项”标签中，设置如图 1-12 所示。

图 1-11 “设计”标签

图 1-12 “首选项”标签

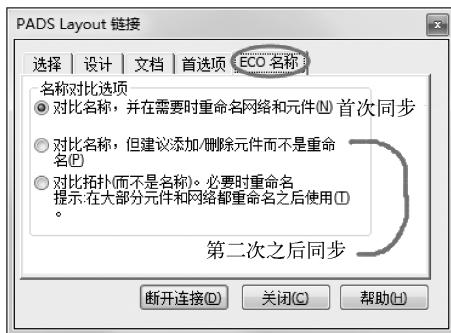

“ECO 名称”标签中，设置如图 1-13 所示。

确认设置正确后，单击“设计”标签，单击“发送网表”按钮，如图 1-14 所示。

图 1-13 “ECO 名称”标签

图 1-14 将 Logic 网表发送到 PADS Layout

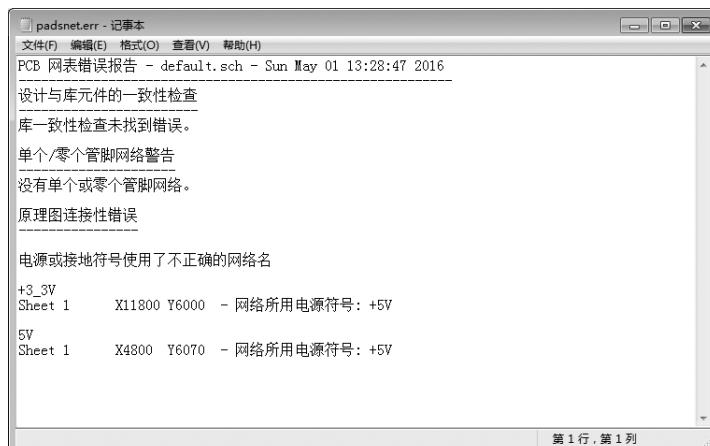

此时可能会弹出网表错误报告，如图 1-15 所示。

“电源或接地符号使用了不正确的网络名”，这个错误可以忽略。

图 1-15 网表错误报告

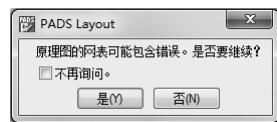

确认没有错误后，关闭报告，会有如图 1-16 所示的窗口询问是否继续，单击【是】按钮继续。

此时软件后台在 PADS 安装目录下的 PADS Projects 文件夹下会自动生成如图 1-17 所示的原理图网表。

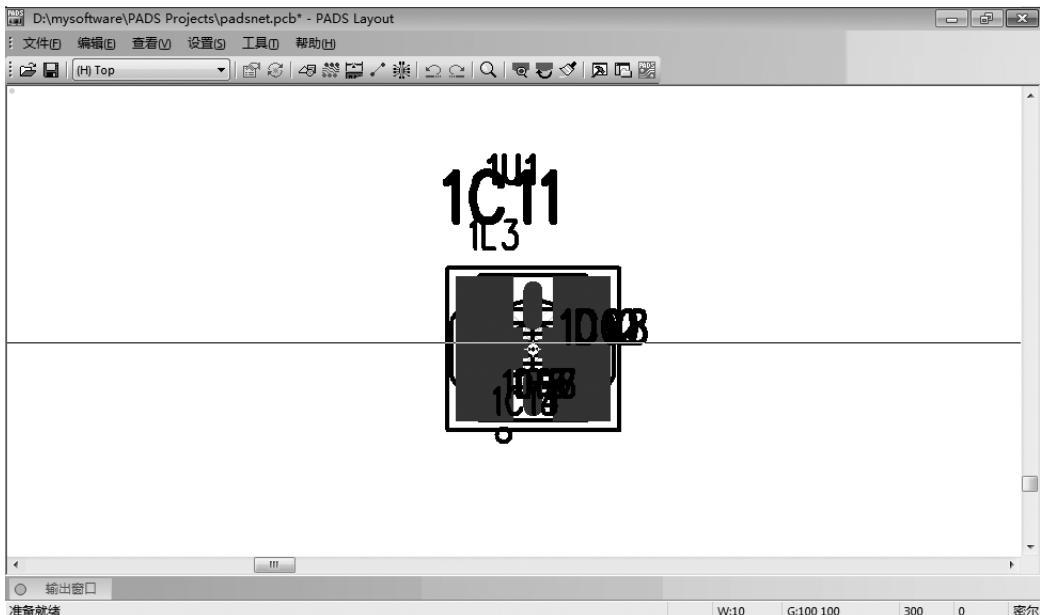

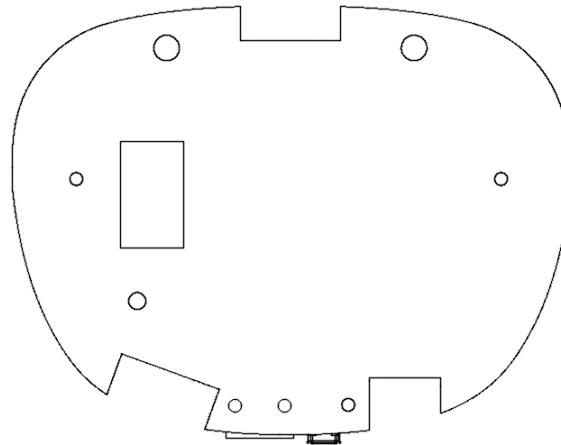

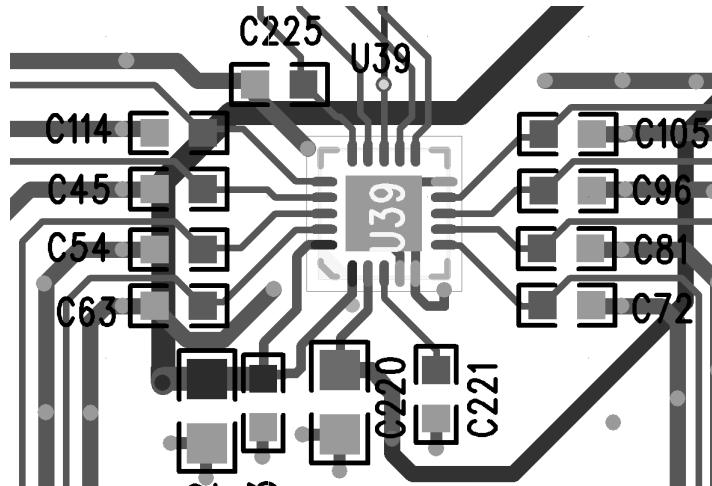

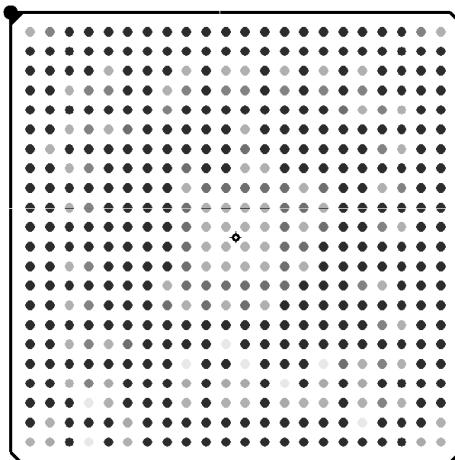

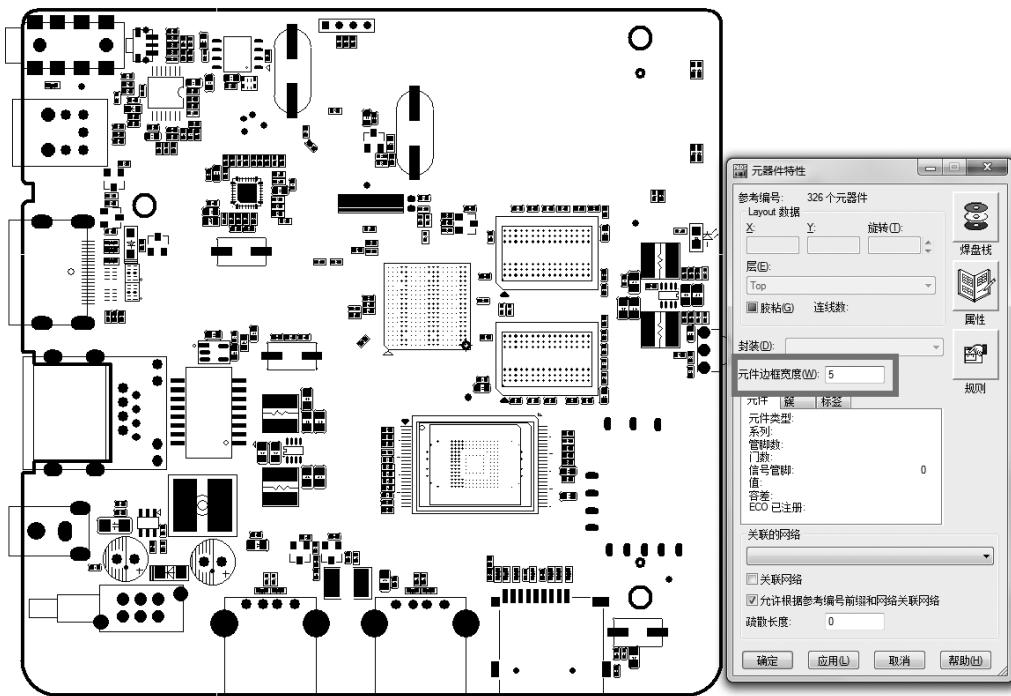

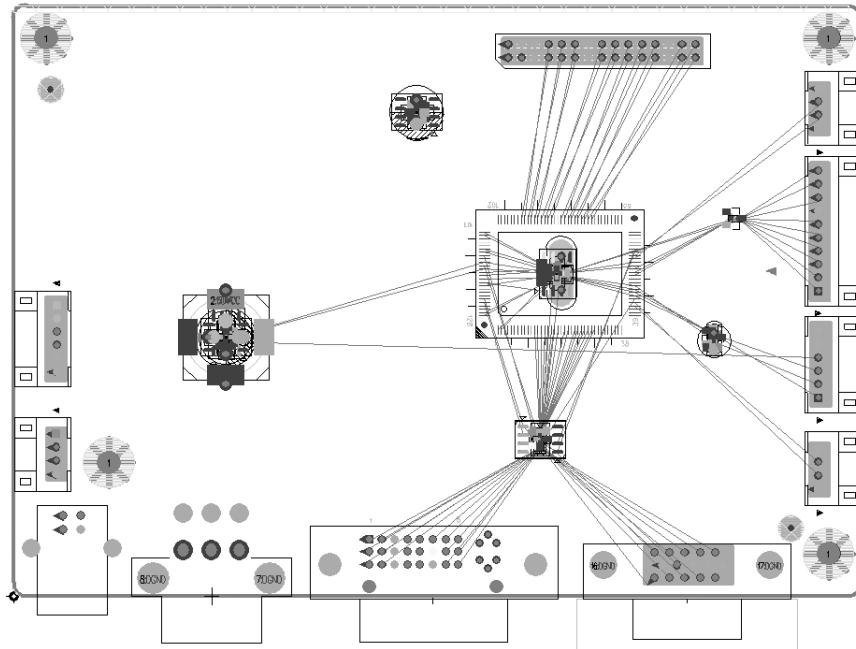

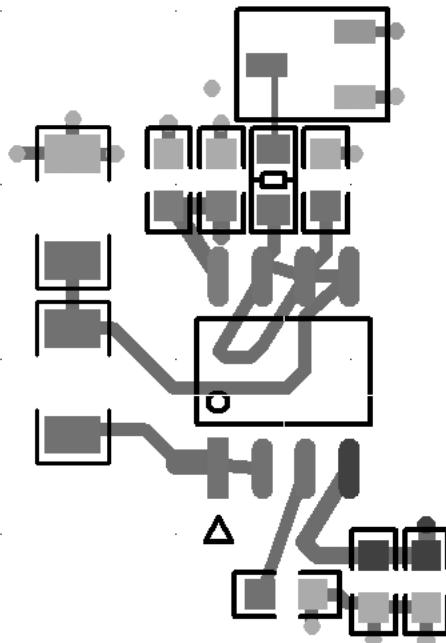

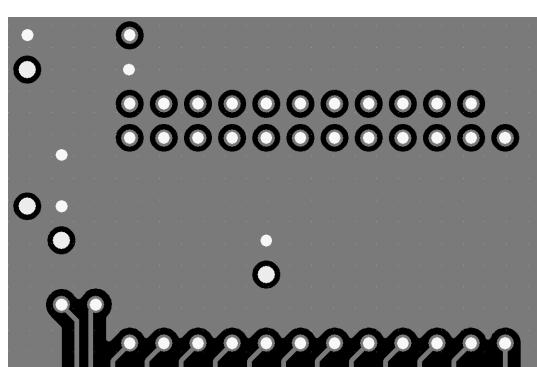

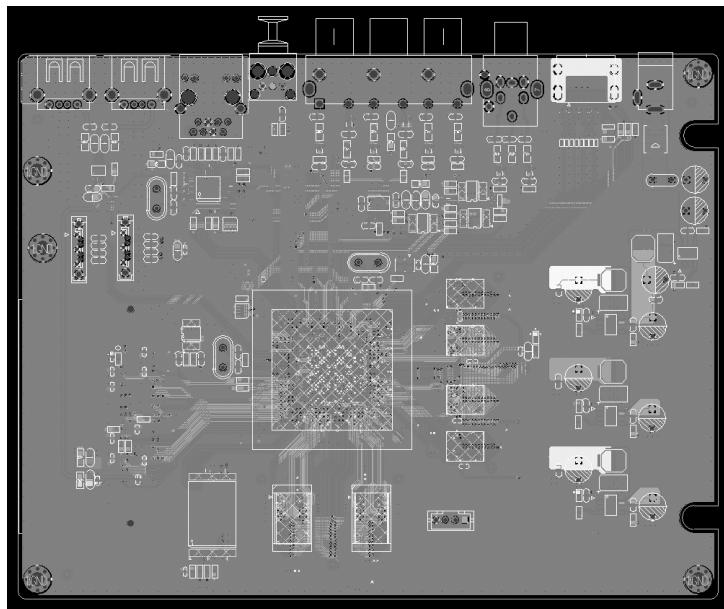

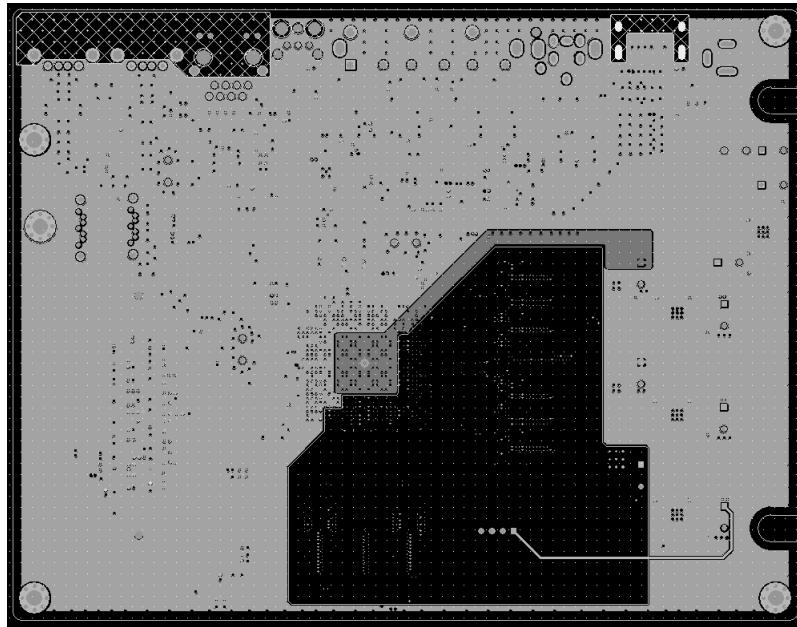

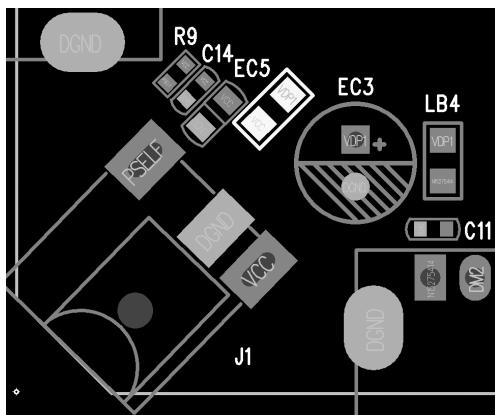

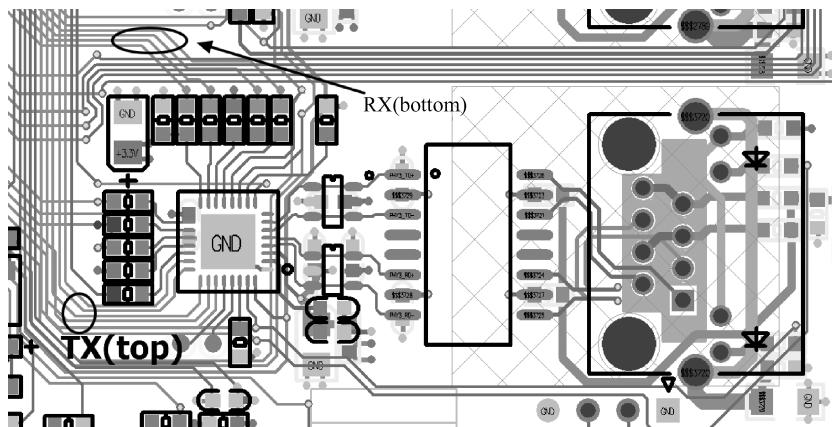

设计所需的所有 PCB 封装就会出现在新建的 PADS Layout 中，并附着在原点上，如图 1-18 所示，此时 PADS Logic 原理图的网表就成功导入到 PADS Layout 中了。

图 1-16 询问是否

继续操作窗口

```

* padnetdesc -记录本

文件(F) 编辑(E) 格式(O) 查看(V) 帮助(H)

1PADS-POWERPC-V9.0-NILS-CP936!来自 PADS LOGIC V9.5 的网表文件

*REMARK= default.sch -- Sun May 01 13:40:39 2016

*REMARK=

*PART*          IMENTS

C1C2          C6090C0402

I1R2          RESISTOR_10R0402

IC9          CAP_NP_28C0402

I1R6          R_10K0402

IC10         CAP_NPC0402

I1R7          RESISTOR8R0402

I1R8          RESISTOR10R0402

IL13          L_DRS548C043

I1R7          R_20R0402

IC13         CAP_NP_28C0805

I1U1          SY8120_08SOT23-6

IC11         CAP_NWC1206

IC14         CAP_NP_28C0805

IDC3          CAP_NP_28C0402

*NET*

*IGNAL+ $$I17852

I1R8.1 1DR7.2 1U1.5 1DC8.1

*IGNAL+ +3.3V

I1R6.1 1L3.2 IC13.1 IC14.1 IC12.1

*IGNAL+ $$I17997

I1R6.6 1C12.2

*IGNAL+ 5V

1DR7.1 IC10.1 IC11.1 1U1.3

*IGNAL+ GND

1DC8.2 1C14.2 1C10.2 1C11.2 1R7.2

IC13.3 1R8.2 1U1.1 IC12.2

*IGNAL+ $$I17369

I1R6.2 1R7.1 1DR8.2

*IGNAL+ $$I18013

I1U1.4 1DR8.1

*IGNAL+ $$I17371

IC9.1 1U1.2 1L3.1

*MISC*          MISCELLANOUS PARAMETERS

ATTRIBUTE VALUES

```

图 1-17 原理图网表

图 1-18 成功导入网表的 PCB

## 1.2 导入第三方网络表前配置库文件

PADS Layout 要成功导入第三方网络表的前提是要确保当前设计的 PADS Layout 库文件中所用元器件的元件类型（Part Type）都分配了对应的 PCB 封装（PCB Decal）。我们建议长期使用第三方软件进行原理图设计的工程师，在建设 PADS 库文件时元件类型名称应和对

应分配的 PCB 封装名称保持一致。

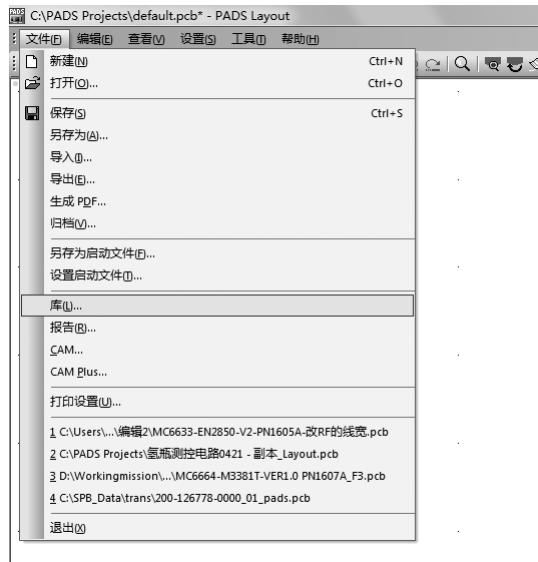

打开 PADS Layout，执行菜单命令【文件】 - 【库】，如图 1-19 所示。

图 1-19 进入“库”选项

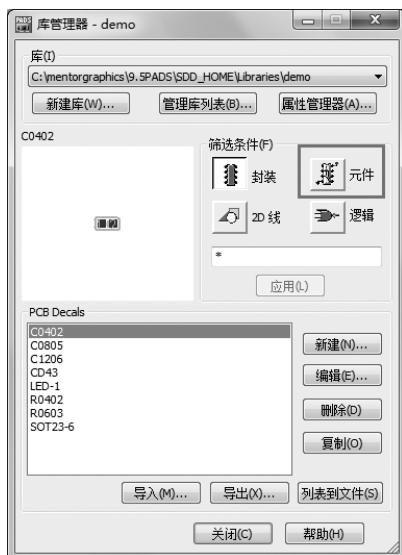

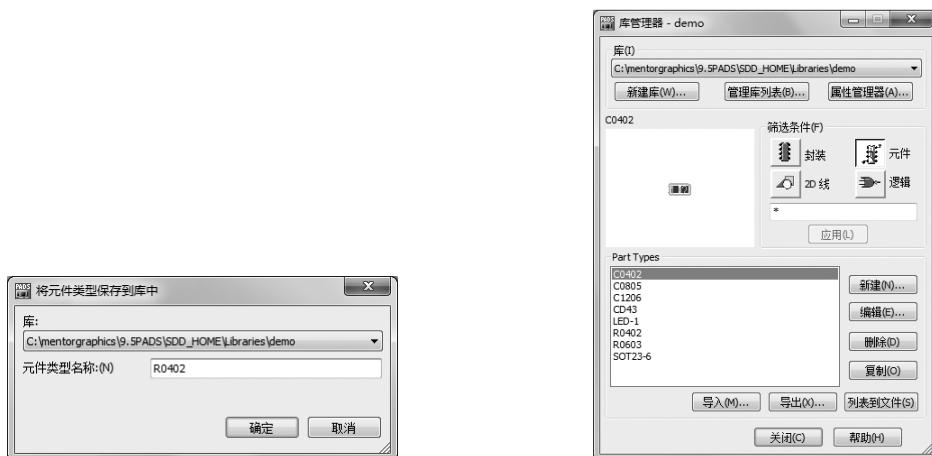

在弹出的“库管理器”对话框中，选择设计需要用到的库，本例库文件为 demo。假设设计需要的 PCB 封装都已经建好了，我们需为每个 PCB 封装都建一个元件类型和它对应，下面以建立 R0402 封装的元件类型为例。

单击“元件”标签，如图 1-20 所示。

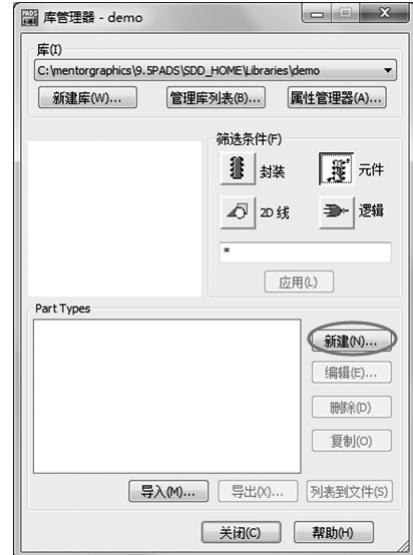

在图 1-21 所示的窗口中单击【新建（N）...】按钮。

图 1-20 demo 元件库

图 1-21 demo 库中的元件类型

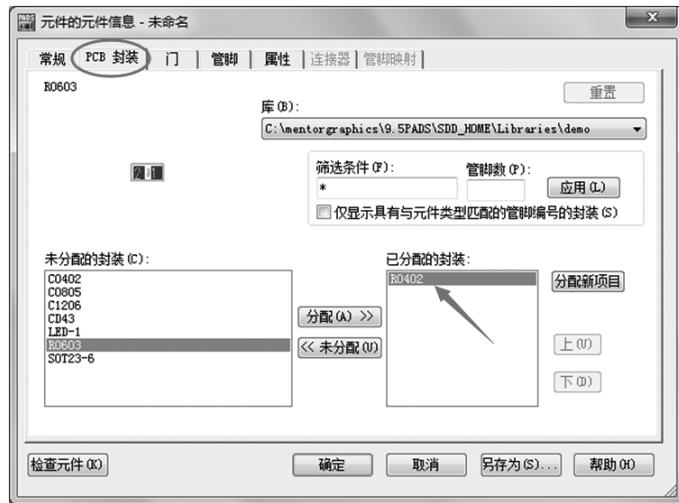

弹出“元件的元件信息”对话框，单击“PCB 封装”标签。

在“未分配的封装”一栏中选择“R0402”封装，单击【分配 (A) >>】按键，将其移到“已分配的封装”一栏，如图 1-22 所示，单击【确定】按钮完成分配。

图 1-22 给元件类型分配 PCB 封装

这时会弹出如图 1-23 所示的窗口，将刚刚分配的 PCB 封装名称作为元件类型的名称，此处为 R0402，单击【确定】保存。

同样的方法建立其他 PCB 封装的元件类型，完成后如图 1-24 所示。

图 1-23 元件类型名称填入分配的 PCB 封装名称

图 1-24 完成后的元件类型列表

### 1.3 OrCAD 原理图导出 ASC 网表

实际工作中，用 OrCAD 绘制的原理图占相当大的比例，OrCAD（原理图绘制）+ PADS（PCB 设计）是十分经典的组合。如果原理图是 OrCAD 绘制的，我们需要从 OrCAD 导出网表，再用 PADS Layout 导入进行 PCB 设计。

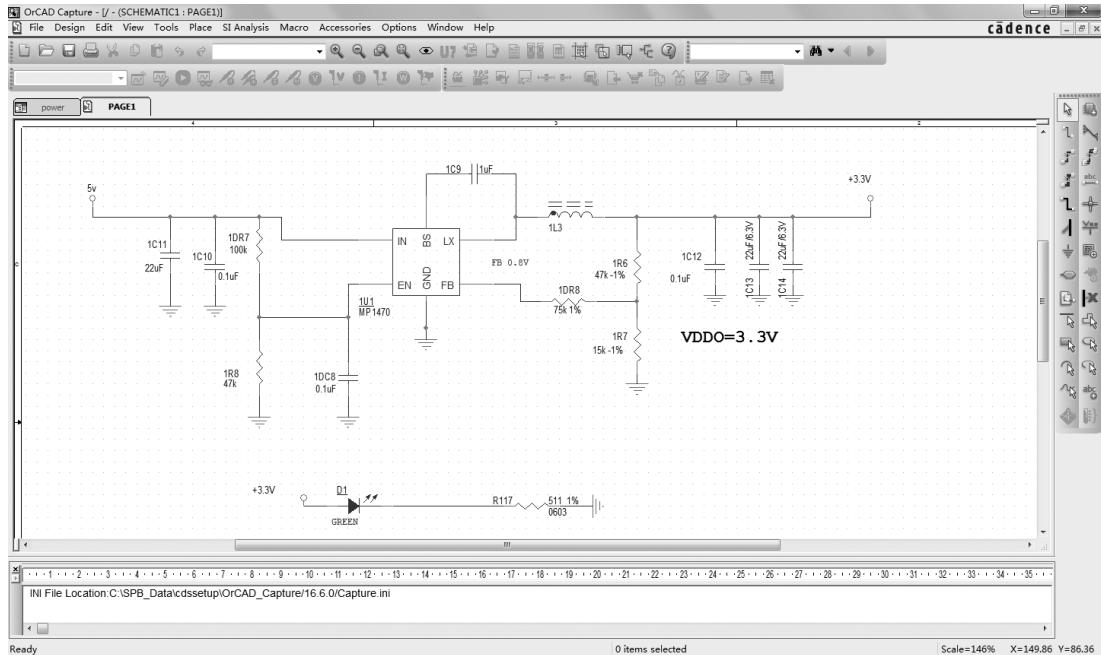

图 1-25 为使用 OrCAD Capture 设计的原理图。

图 1-25 用 OrCAD Capture 设计的原理图

## 1. 为 OrCAD 元件分配封装

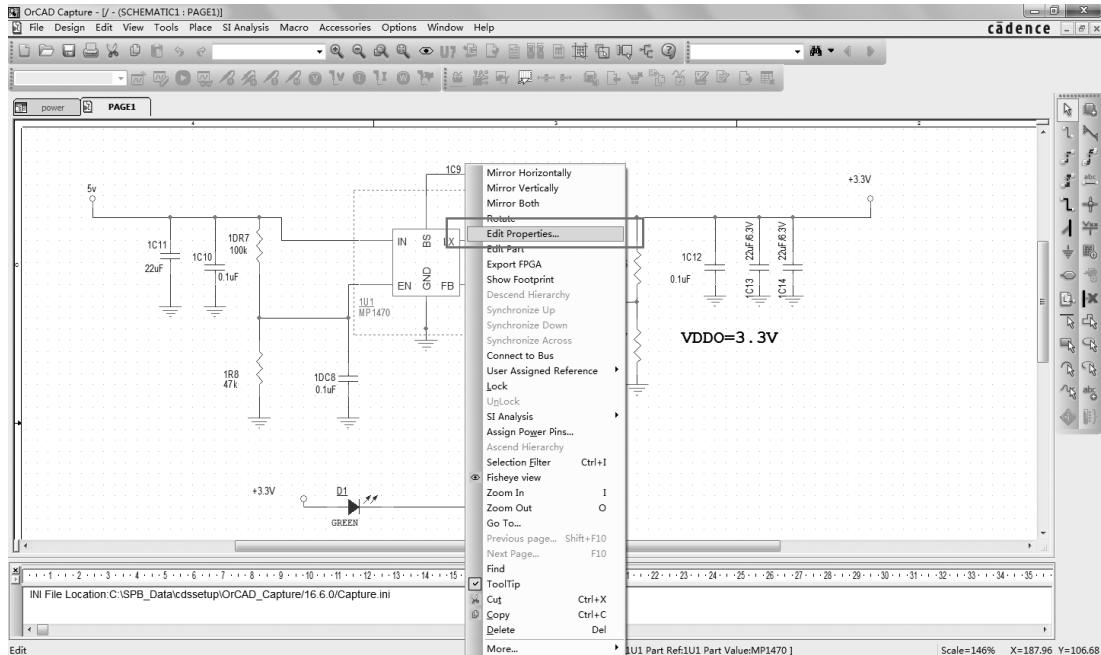

选择元件后，单击鼠标右键，执行菜单命令【Edit Properties】，如图 1-26 所示。

图 1-26 进入编辑属性

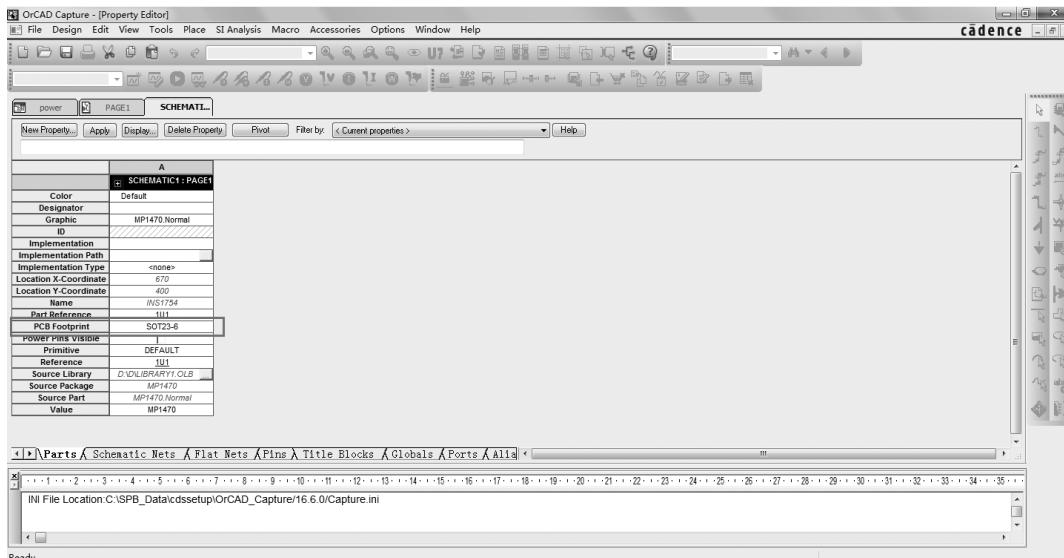

在弹出的特性窗口中的“PCB Footprint”标签中填上 PCB 封装的名字。

**注意：**OrCAD 指定的封装对应的是 PADS 库文件中的元件类型。

如图 1-27 所示，同样的方法为每个元件都分配合适的封装。

图 1-27 填写 PCB 封装名字

## 2. 输出网表

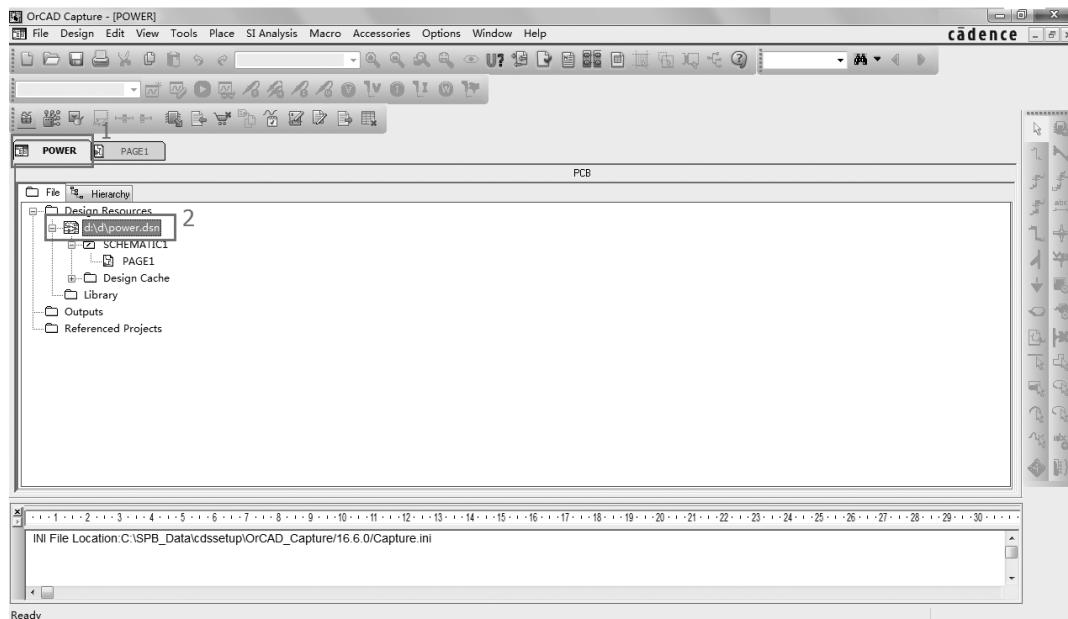

按图 1-28 所示的步骤打开项目管理窗口，选择要输出的“.dsn”项目。

图 1-28 在 OrCAD 中选择要输出的项目

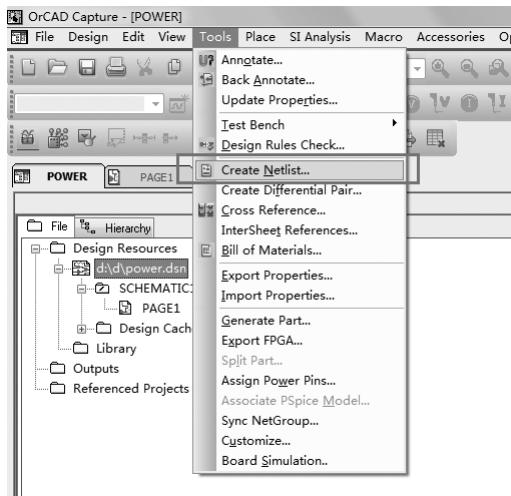

执行菜单命令【Tools】 - 【Create Netlist】，如图 1-29 所示。

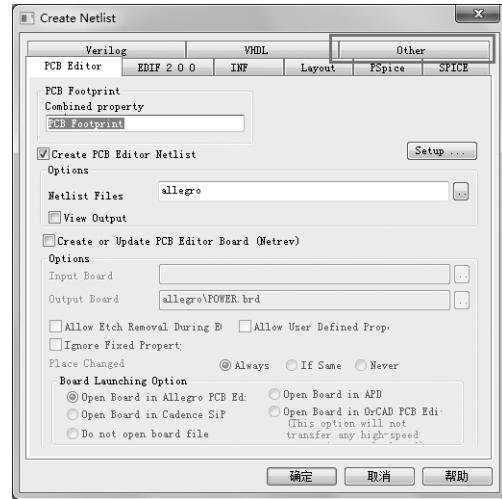

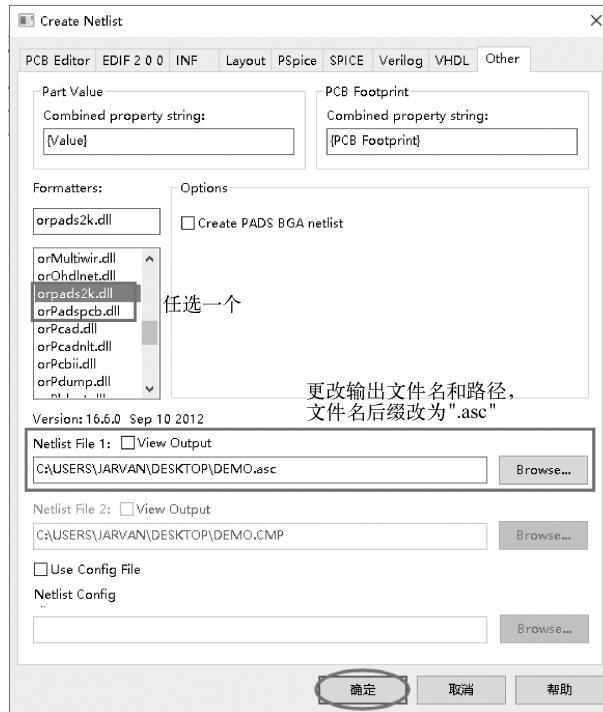

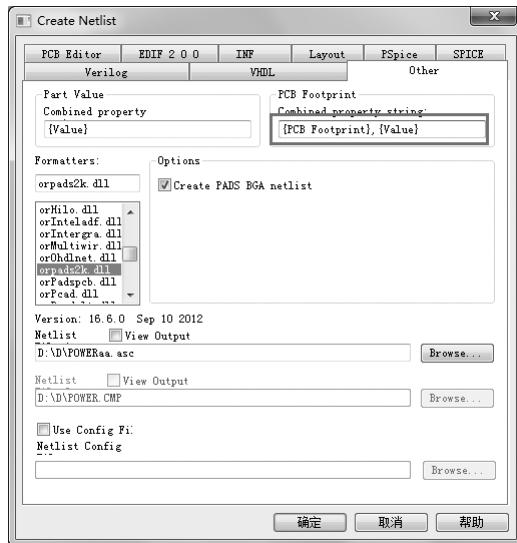

在弹出的“Create Netlist”对话框中单击“Other”选项卡，如图 1-30 所示。

图 1-29 执行菜单命令【Tools】 - 【Create Netlist】

图 1-30 单击“Other”选项卡

在“Formatters”标签中选择“orpads2k.dll”或“orpadspcb.dll”格式，文件名后缀改为“.asc”，可以更改输出路径。如图 1-31 所示，单击【确定】按钮，完成文件输出，可以在相应的文件目录下找到后缀为“.asc”的文件。

图 1-31 OrCAD 输出网表设置

## 1.4 导出 Altium Designer 原理图网表

如果原理图是 Altium Designer 绘制的，那么我们需要从 Altium Designer 导出网表，再用 PADS Layout 导入进行 PCB 设计。

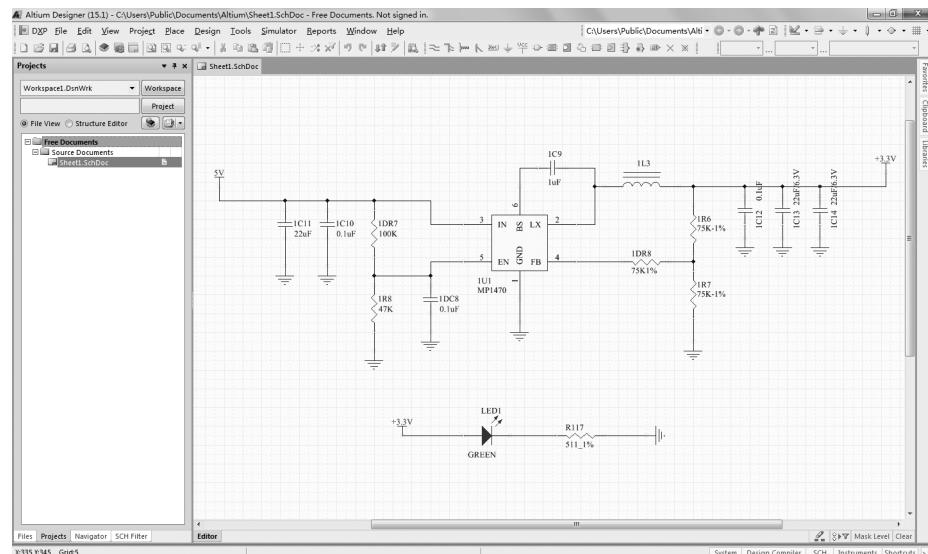

如图 1-32 所示是用 Altium Designer 绘制的原理图。

图 1-32 用 Altium Designer 绘制的原理图

### 1. 分配 PCB 封装

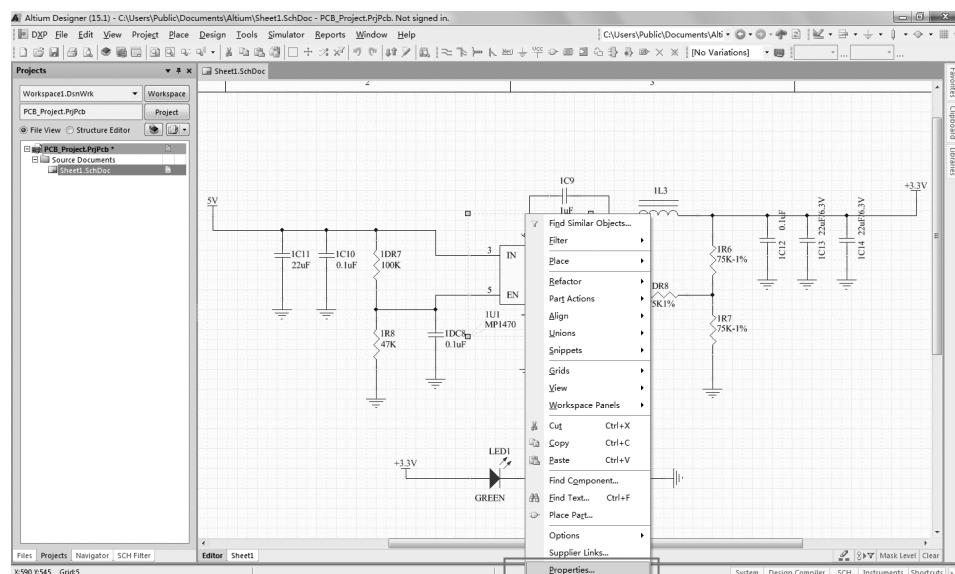

导出网表前须要确保原理图中的每个元件都分配了合适的 PCB 封装。

在原理图上选中元件后单击鼠标右键，执行菜单命令【Properties】，如图 1-33 所示。

图 1-33 打开元件的特性

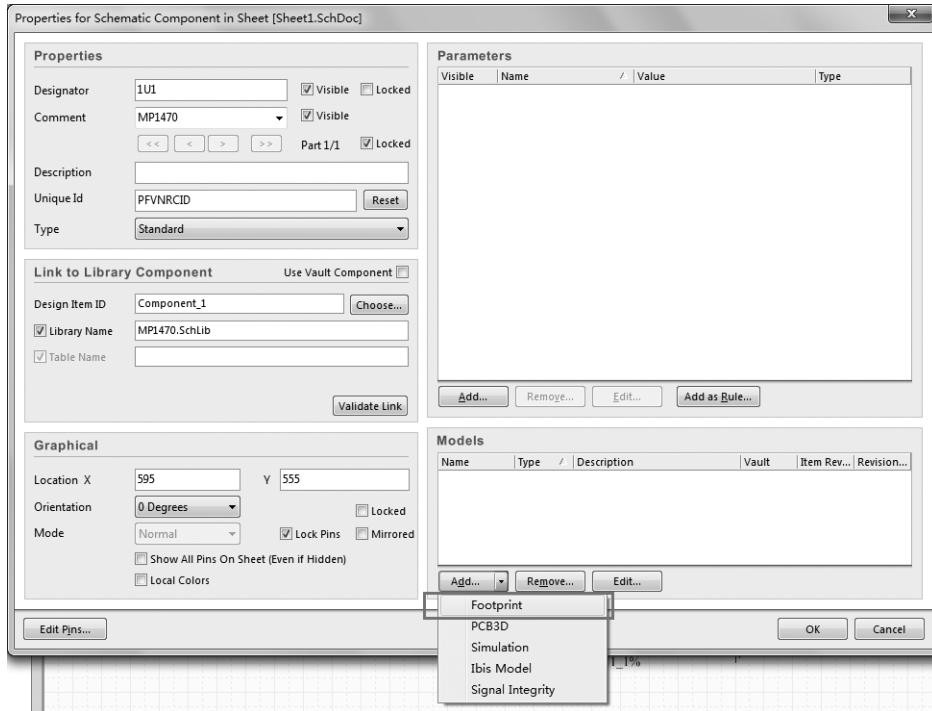

在“Models”栏里，打开【Add】按键右侧的小三角，选择“FootPrint”，添加 PCB 封装，如图 1-34 所示。

图 1-34 添加 PCB 封装模型

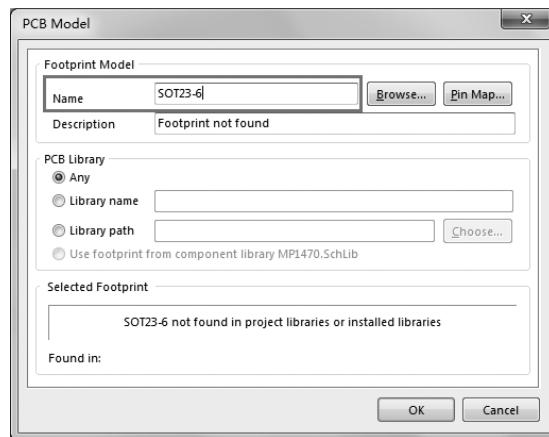

在弹出的“PCB Model”对话框中，将 PCB 封装名称填入“Name”一栏，如图 1-35 所示。

**注意：**此处的封装对应的是 PADS 库文件中元件类型的名称，预览窗口中“提示没有找到……”是正常的。

图 1-35 填入 PCB 封装名称

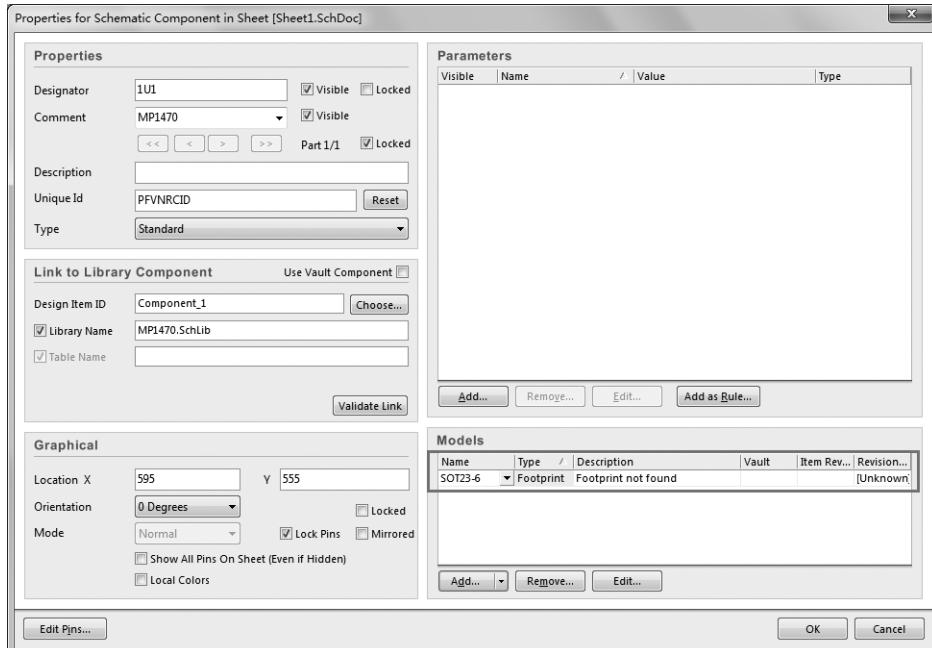

单击【OK】按钮，完成后特性窗口“Models”如图 1-36 所示。接着用同样的方法为每个元件分配好封装。

图 1-36 完成 PCB 封装模型的添加

## 2. 输出网表

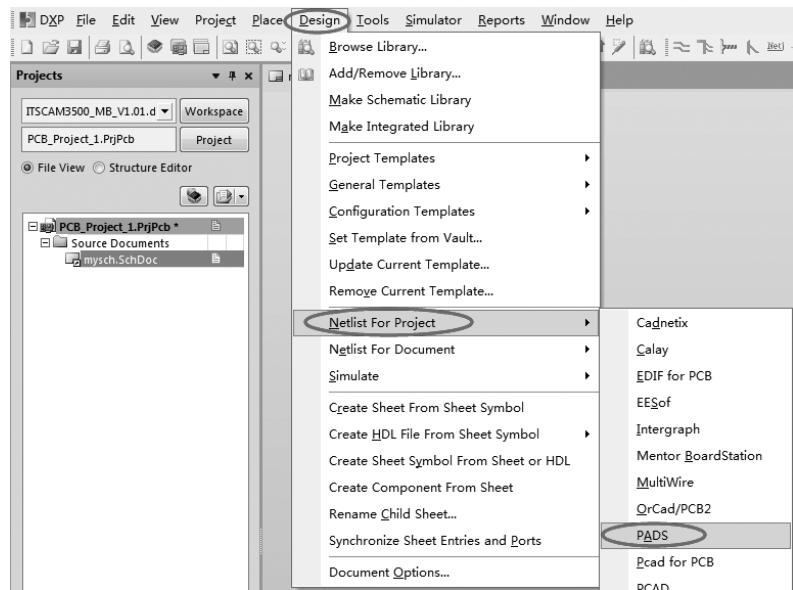

执行菜单命令【Design】 - 【Netlist For Project】 - 【PADS】生成网表，如图 1-37 所示。

图 1-37 完全安装下的输出组件

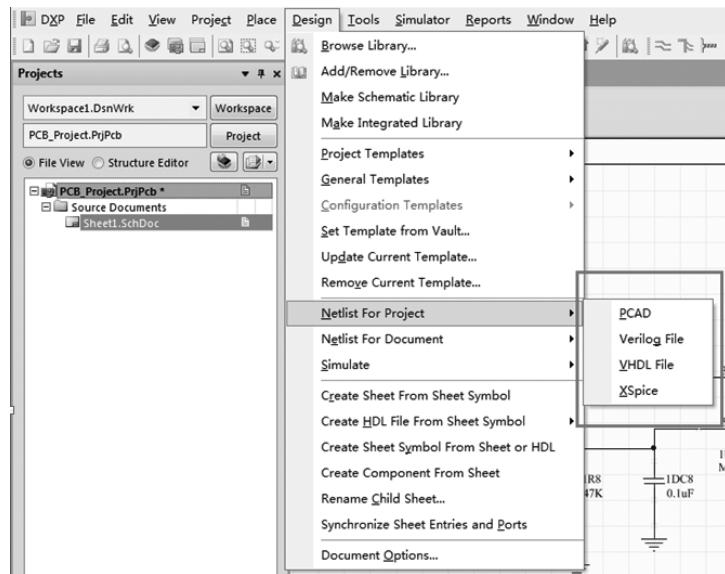

这个步骤需要注意，有些工程师的“Netlist For Project”次级菜单，如图 1-38 所示，并没有【PADS】菜单命令。

图 1-38 默认安装下的输出组件

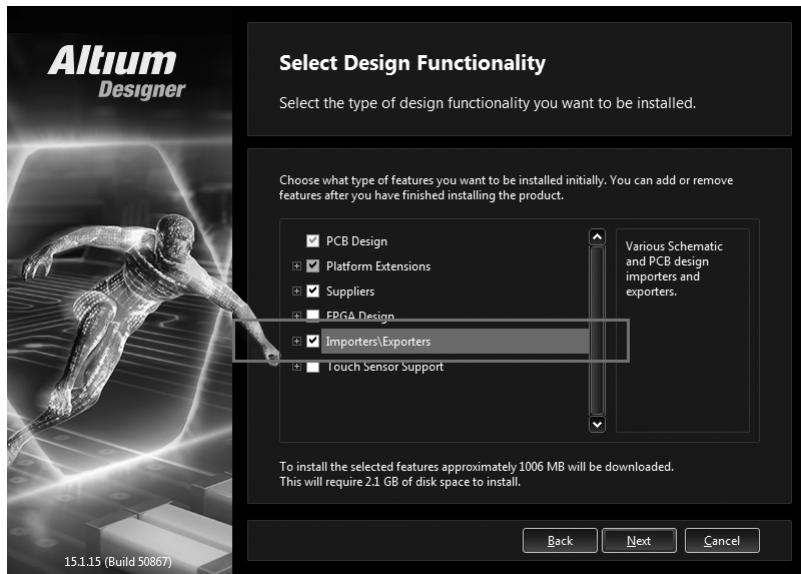

这是因为在安装 Altium Designer 时没有安装相关的“输入\输出组件”造成的，在安装时我们须勾选如图 1-39 所示的“Importers\Exporters”组件。

图 1-39 “Importers\Exporters”组件

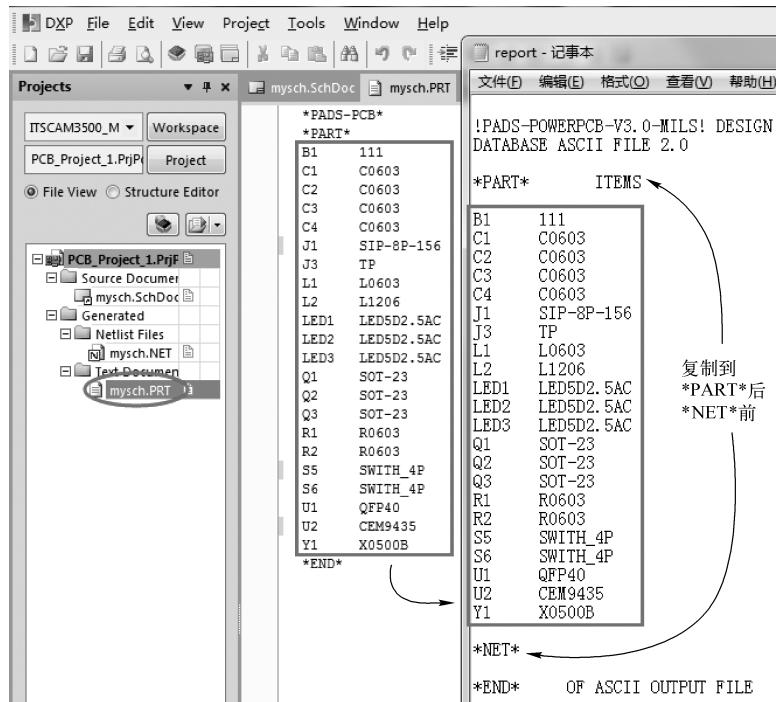

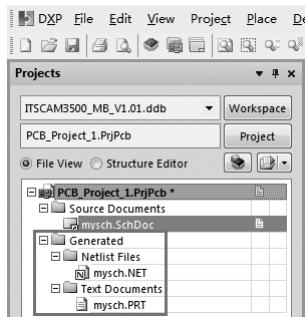

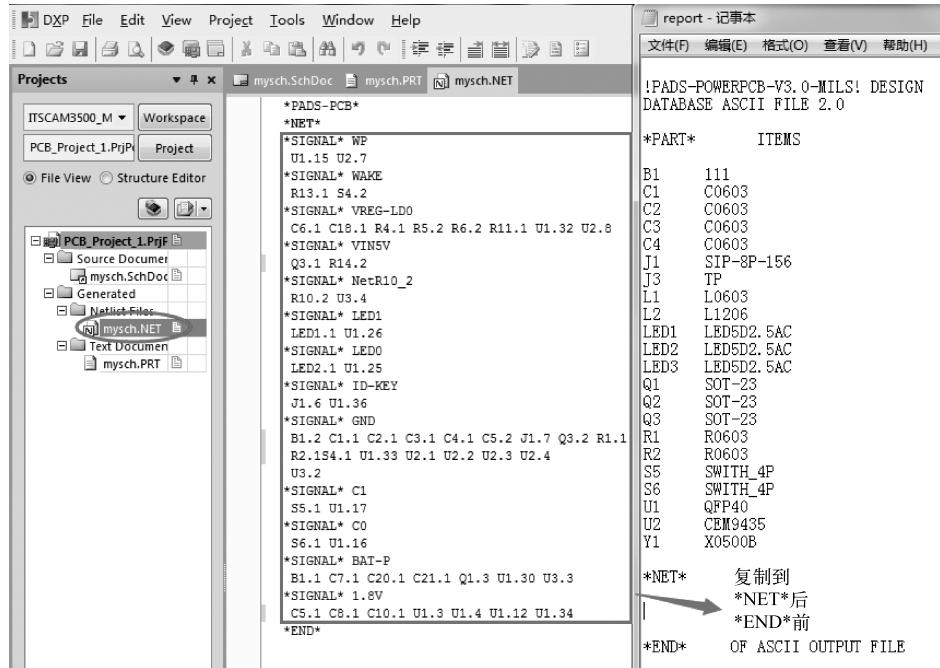

单击输出 PADS 网表后，在左侧项目管理器会出现“\*.NET”和“\*.PRT”两个文件，如图 1-40 所示。

### 3. 合成 ASC 网表

刚刚输出的两个文件还不能作为 PADS 的网表直接由 PADS Layout 导入，我们需要将两个文件的内容合成一个“\*.asc”格式的网表。

在文件夹下新建一个“\*.txt”格式的文本文档，将其重命名为后缀为“\*.asc”的文件。

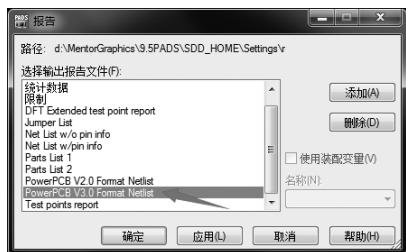

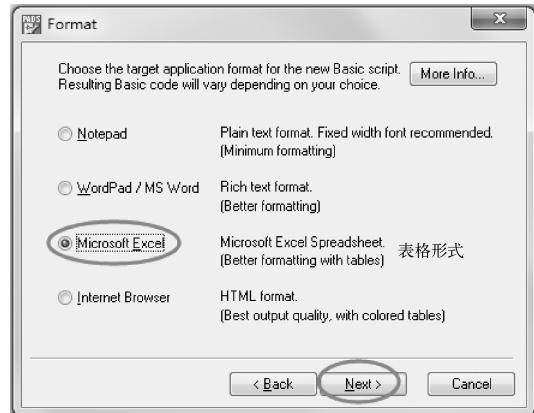

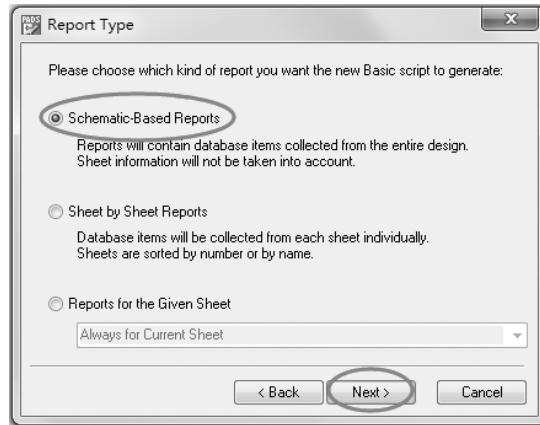

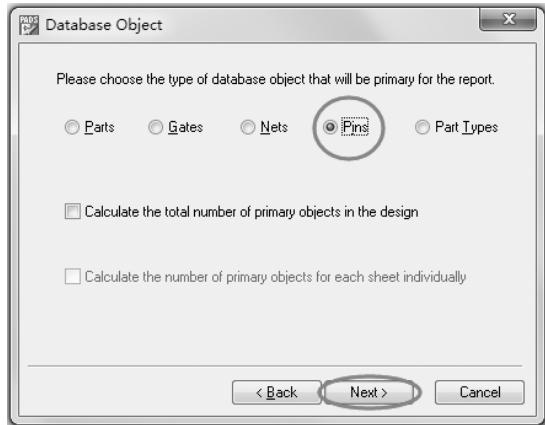

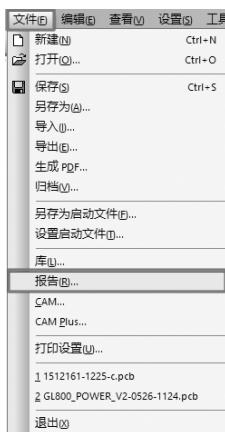

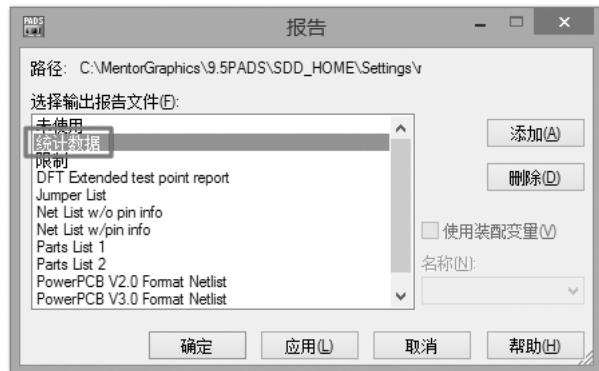

在 PADS Layout 中，执行菜单命令【文件】-【报告】，在弹出的对话框中选择“PowerPCB V3.0 Format Netlist”，如图 1-41 所示。

单击【应用(L)】按钮，弹出如图 1-42 所示的对话框。

图 1-41 查看网表前缀文件

```

!PADS-POWERPCB-V3.0-MILS! DESIGN DATABASE ASCII FILE 2.0

*PART*           ITEMS

*NET*

*END*          OF ASCII OUTPUT FILE

```

图 1-42 网表格式文件

在 Altium Designer 中打开“\*.PRT”文件，将如图 1-43 所示框中的信息复制粘贴到文本文档中“\*PART\*”后、“\*NET\*”前的位置。

图 1-43 复制元件信息到文本文档

图 1-40 输出的网表文件

打开 \*.NET 文件，将如图 1-44 所示框中的信息复制粘贴到文本文档中 “ \* NET \* ” 后、“ \* END \* ” 前的位置。

图 1-44 复制网络连接信息到文本文档

对文件进行保存，后续用 PADS Layout 进行导入 “.asc” 文件。

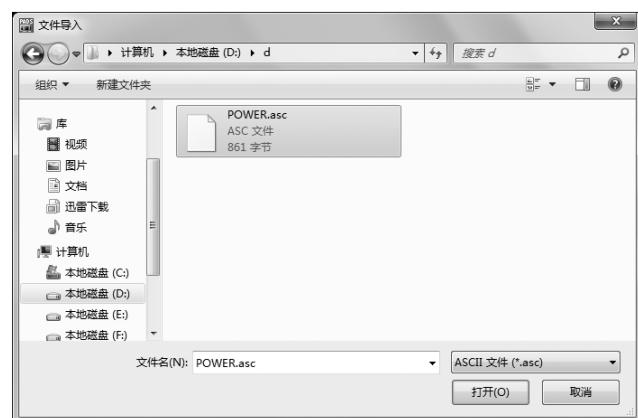

## 1.5 导入网络表 (.asc 文件)

在 PADS Layout 中，执行菜单命令【文件】 - 【导入】，如图 1-45 所示。

弹出“文件导入”对话框，到相应的文件目录下找到“.asc”文件，单击【打开】按钮，如图 1-46 所示。

图 1-45 进入导入选项

图 1-46 选择刚刚输出的网表文件

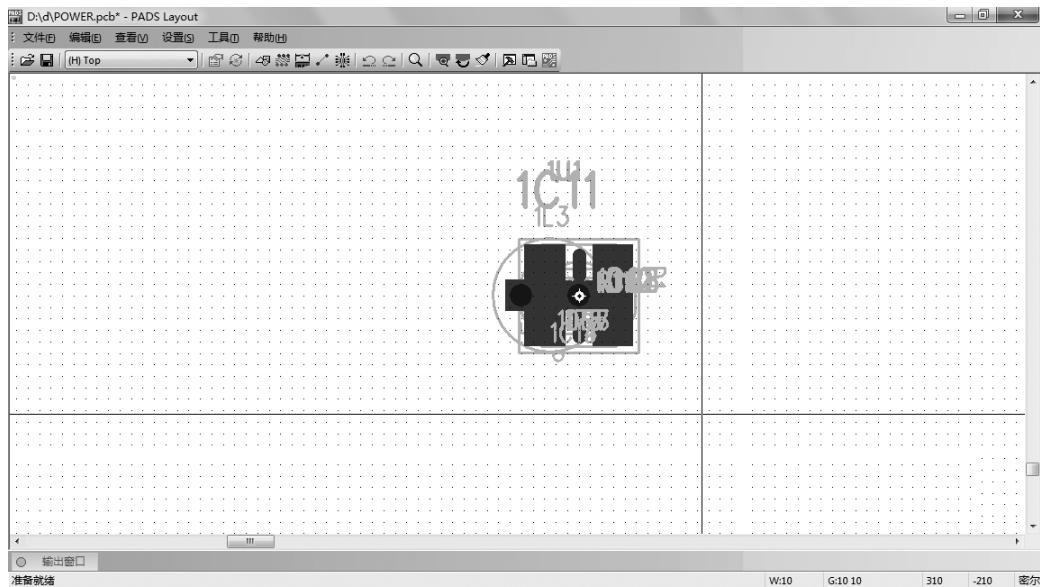

导入成功后，所有 PCB 元器件就会出现在 PADS Layout 中，并附着在原点上，如图 1-47 所示。

图 1-47 成功导入网表

## 1.6 OrCAD Capture 原理图转 PADS Logic 原理图

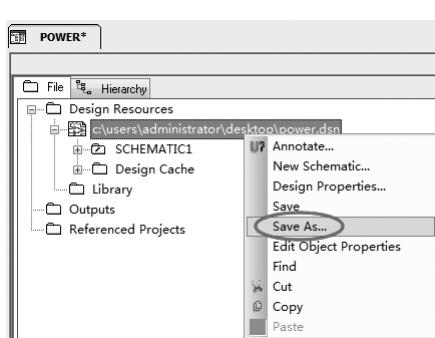

目前 OrCAD 已经出到 17.2 版本，而 PADS Logic 只能导入 16.2 以下版本的 “.dsn” 文件，所以要将高版本的 dsn 文件降为 16.2 以下版本才能导入 PADS Logic 中。

打开 OrCAD Capture 原理图，选中 “.dsn” 文件，单击鼠标右键，执行菜单命令【Save As】另存为，如图 1-48 所示。

在弹出的“Save As”窗口中，更改文件名，本例改为“POWER2”，然后打开“保存类型”的下拉菜单，选择“Capture 16.2 Design (\*.dsn)”，将文件保存在同一文件夹下，如图 1-49 所示。

图 1-48 将 “.dsn” 文件另存为

图 1-49 另存为 16.2 版本的 “.dsn” 文件

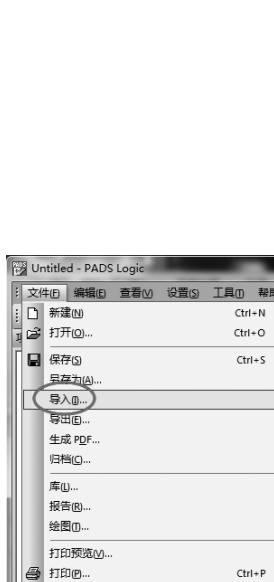

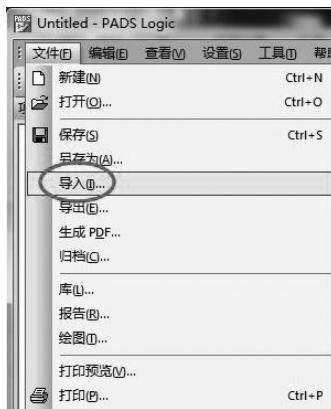

打开 PADS Logic，执行菜单命令【文件】 - 【导入】，如图 1-50 所示。

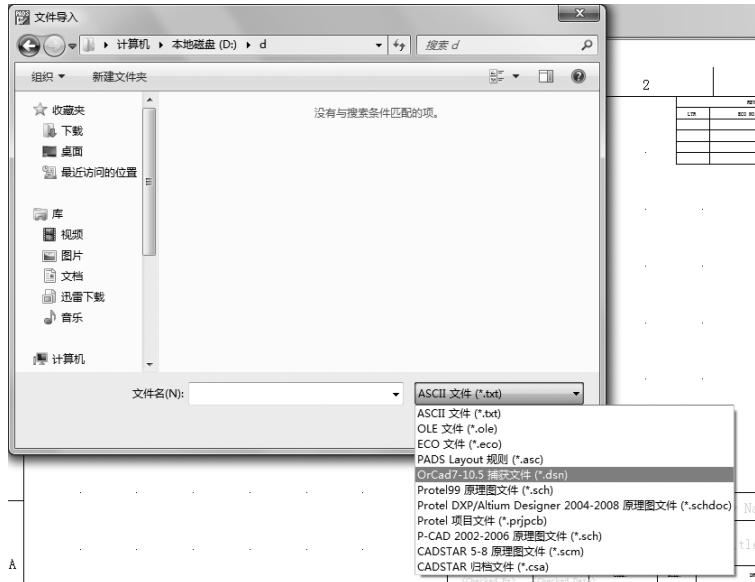

在弹出的“文件导入”对话框中，找到要导入“. dsn”文件保存的路径，在格式下拉菜单中选择“OrCAD7 - 10.5 捕获文件 (\*. dsn)”，如图 1-51 所示。

图 1-50 执行菜单命令

【文件】 - 【导入】

图 1-51 导入“. dsn”文件

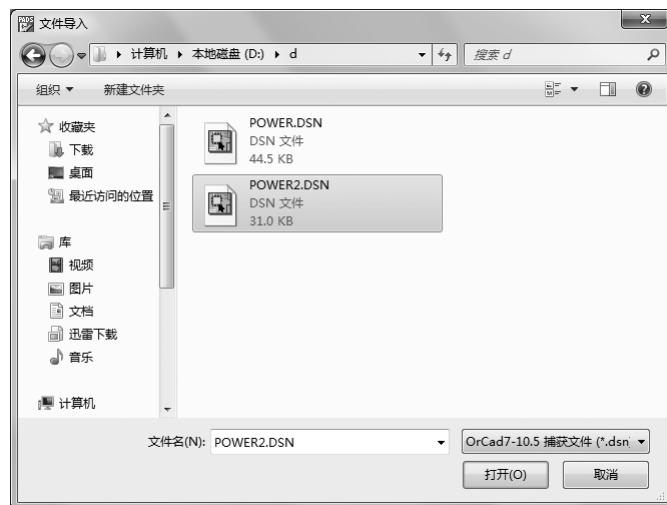

选择刚刚保存的“POWER2. dsn”文件，单击【打开】按钮，如图 1-52 所示。

图 1-52 选择打开保存的 16.2 版本的“. dsn”文件

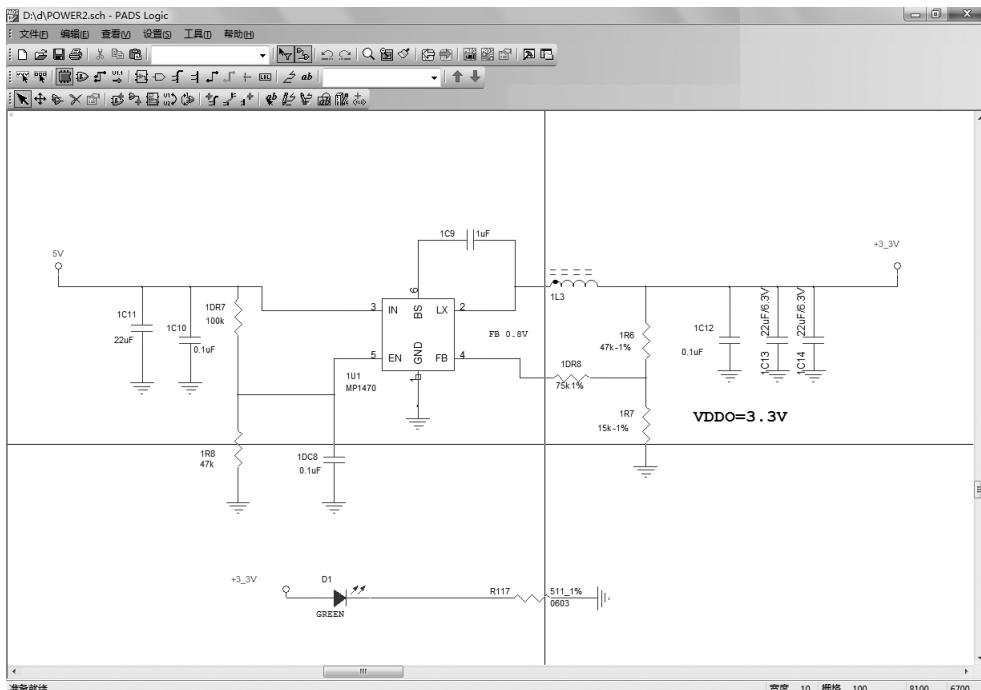

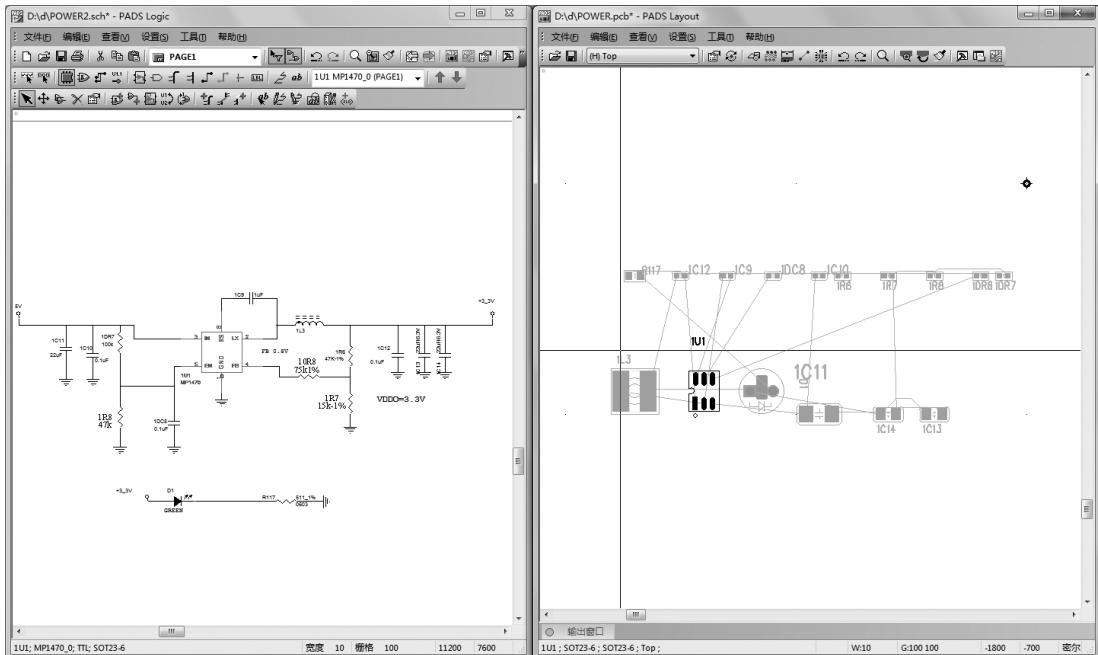

成功导入“. dsn”文件的后 PADS Logic 的原理图，如图 1-53 所示。

对于多图页设计的 OrCAD 原理图，导入 PADS Logic 之后会出现如图 1-54 所示图页下拉菜单一片空白的情况。

第1章 网络表

图 1-53 PADS Logic 成功导入 “.dsn” 文件

图 1-54 图页下拉菜单显示空白

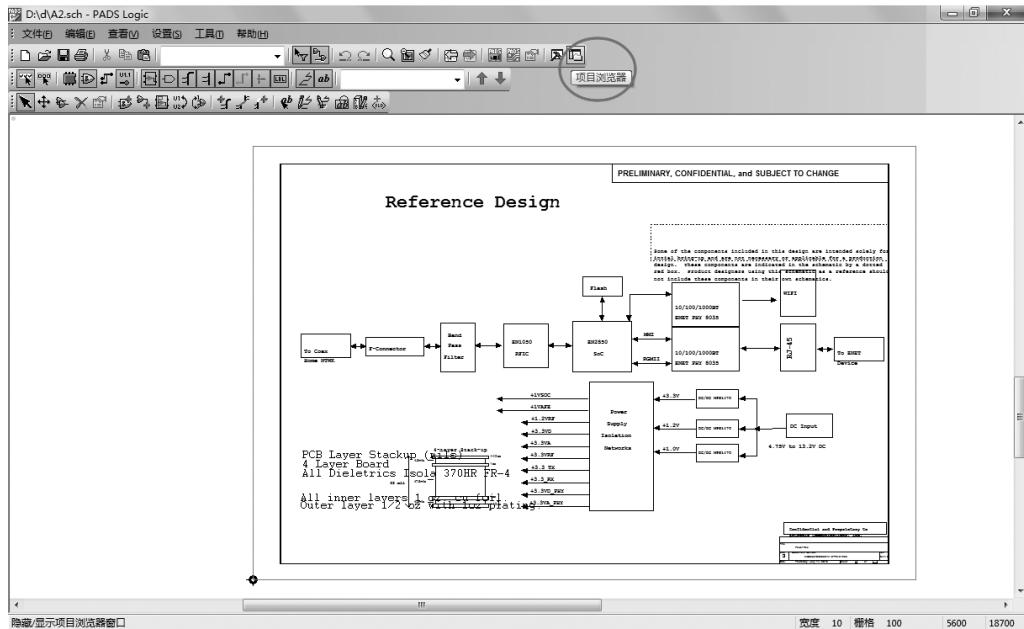

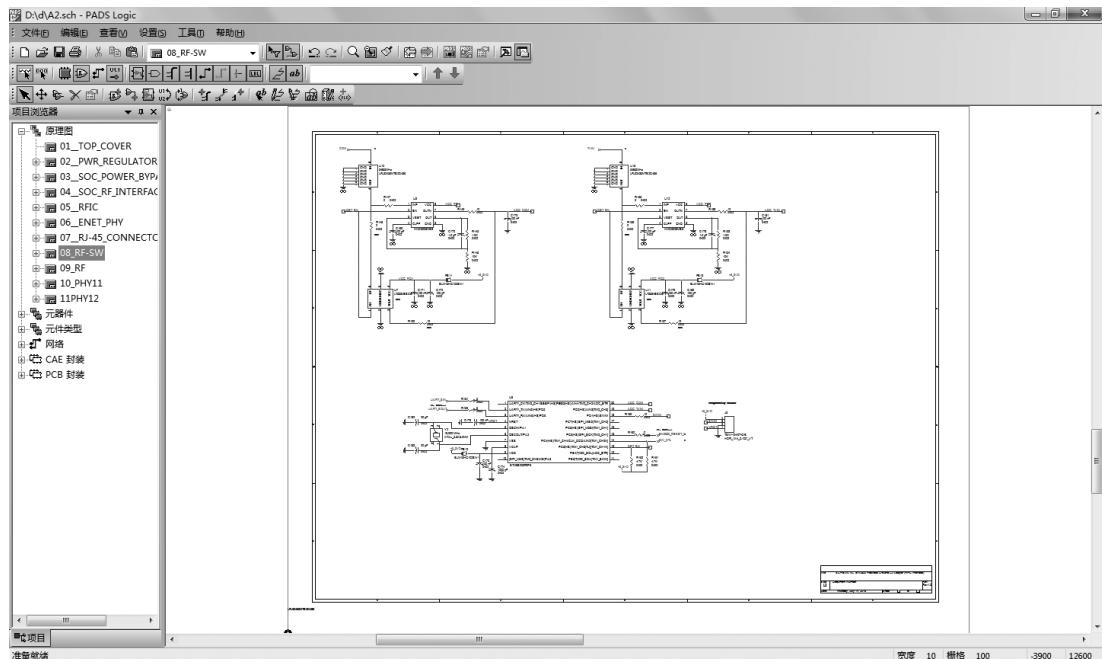

只要按以下步骤操作便可以正常显示，在 PADS Logic 中单击工具栏中的【项目浏览器】按钮，如图 1-55 所示。

图 1-55 单击【项目浏览器】按钮

此时软件左侧会弹出“项目浏览器”，单击展开其中的“原理图”项，随意单击其中一页，如图 1-56 所示。

图 1-56 切换到任一图页

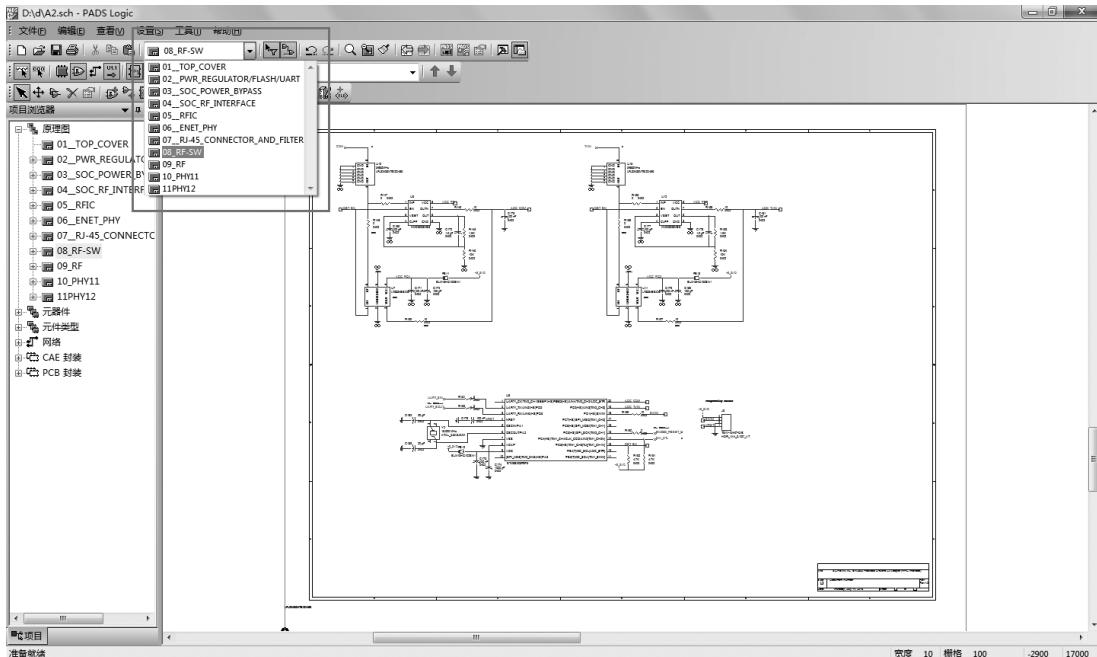

此时再单击工具栏中的图页下拉框，就能正常显示了，如图 1-57 所示。

图 1-57 图页下拉框正常显示图页

## 1.7 Altium Designer 原理图转 PADS Logic 原理图

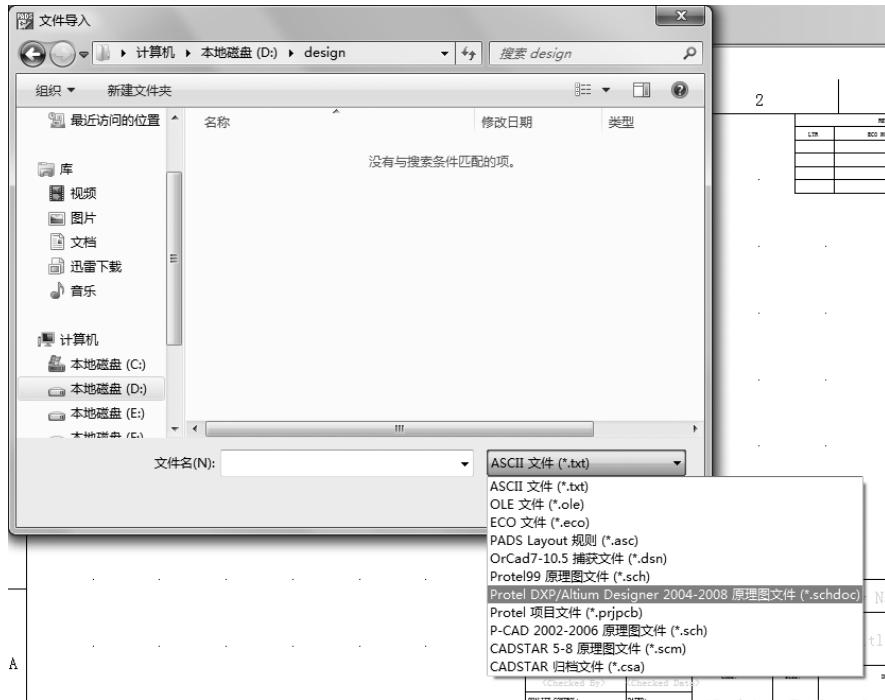

打开 PADS Logic，执行菜单命令【文件】 - 【导入】，如图 1-58 所示。

图 1-58 PADS Logic 中选择导入操作

在弹出的“文件导入”窗口中，导入格式选择“Protel DXP/Altium Designer 2004 – 2008 原理图文件 (\*.schdoc)”，如图 1-59 所示。

图 1-59 选择导入“Protel DXP/Altium Designer 2004 – 2008 原理图文件（\*.schdoc）”格式

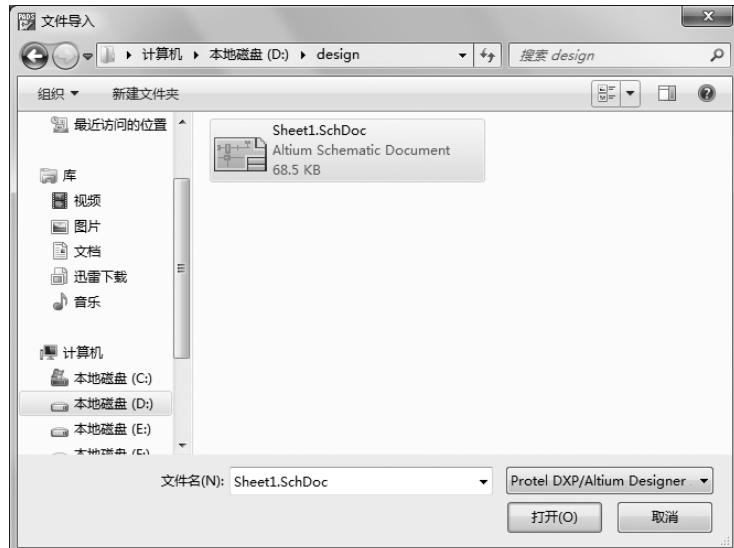

到相应的文件目录下选择 Altium Designer 的原理图文件，单击【打开】按钮即可，如图 1-60 所示。

图 1-60 导入 Altium Designer 原理图

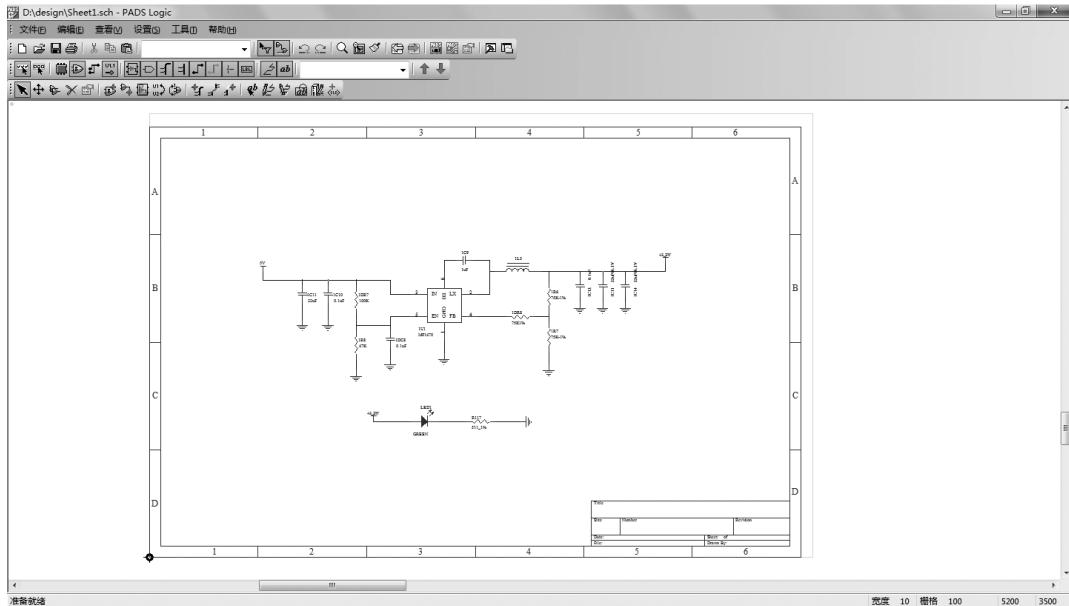

图 1-61 是成功导入到 PADS Logic 的 Altium Designer 原理图。

图 1-61 成功导入到 PADS Logic 的 Altium Designer 原理图

## 1.8 PADS Logic 原理图和 PADS Layout 的交互

第三方原理图是不能和 PADS Layout 进行交互的，要实现交互布局，须要将第三方原理图转换成 PADS Logic 原理图后再和 PADS Layout 进行交互才能实现。

同时打开 PADS Logic 原理图和 PADS Layout 设计，切换到 PADS Logic 原理图，执行菜单命令【工具】 - 【PADS Layout...】，如图 1-62 所示。

图 1-62 执行菜单命令【工具】 - 【PADS Layout...】

接着会弹出如图 1-63 所示的“PADS Layout 链接”窗口，注意勾选“接收选择”。

将原理图和 PCB 窗口分别置于屏幕两侧，单击原理图或 PCB 中的一个元件，另一侧相应的元件也会被高亮显示，说明此时交互已经成功。图 1-64 为选择了元件 1U1，两侧的 1U1 均高亮显示。

需要注意的是，因为其他软件转换过来的 PADS Logic 原理图其中的一些网络名称、元器件属性等有可能会发生改变，所以这样的原理图只能作为交互布局使用，不能用它导网表到 PADS Layout 中。

图 1-63 “PADS Layout 链接”窗口

图 1-64 交互时选择一侧的元素，另一侧对应元素也会相应显示

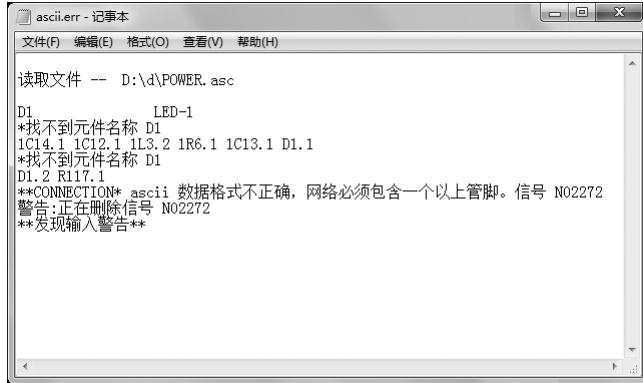

## 1.9 导入第三方网表提示找不到元件

用 PADS Layout 导入第三方网表时，提示找不到元件（此例中为 LED - 1），网表导入失败，如图 1-65 所示，但检查库文件却发现 LED - 1 的元件类型和 PCB 封装均存在，且元件类型分配了 PCB 封装。

我们可以在 PADS Layout 中进入库管理器，选择 LED - 1 的 PCB 封装，单击【编辑】按钮进入封装编辑页面，如图 1-66 所示。

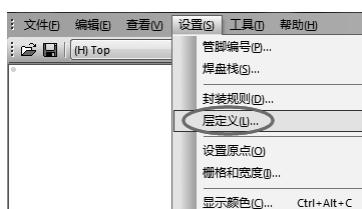

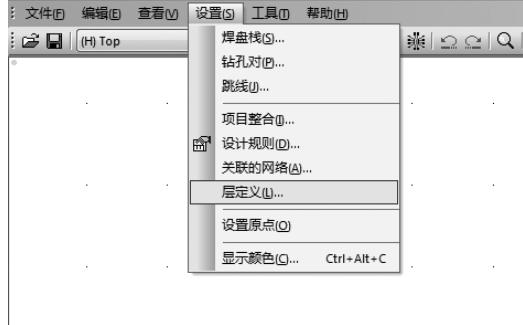

进入“LED - 1”的封装编辑页面后，执行菜单命令【设置】 - 【层定义】，如图 1-67 所示。

图 1-65 提示找不到元件 LED - 1

图 1-66 从库管理器进入元件的编辑页面

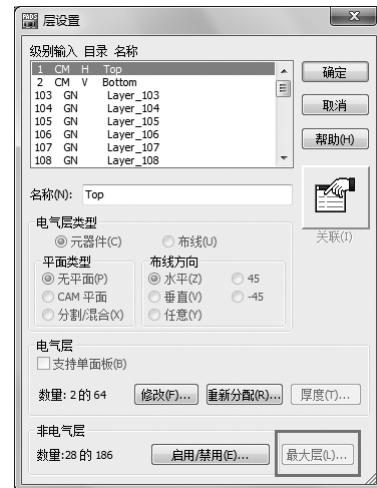

在弹出的“层设置”窗口中，可以看到“最大层”处于不可编辑的状态，如图 1-68 所示，说明这个“LED - 1”的封装是在增加层模式下制作的。

图 1-67 在封装编辑页面进入【层定义】

图 1-68 “层设置”窗口

所以，我们在导入这个网表文件前，要先将 PADS Layout 的层数设置成最大层数的模式才能顺利导入网表。

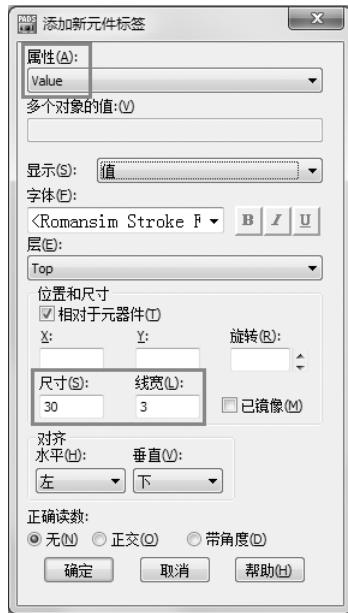

## 1.10 成功导入 OrCAD 的网表后没有 Value 值

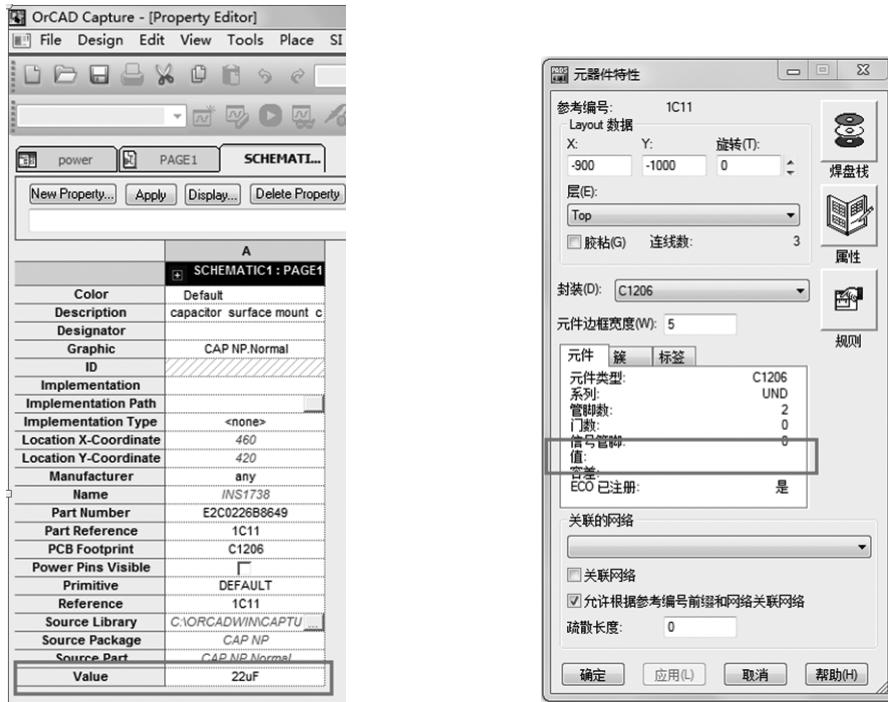

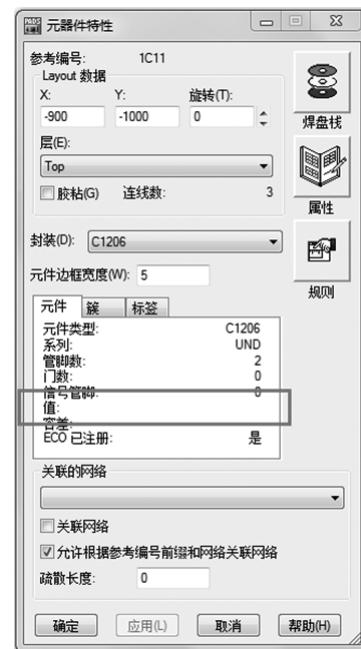

输出 OrCAD 的网表导入后，PCB 设计中的元件阻/容值为空。如图 1-69 所示，在 OrCAD 里已经为每个封装分配了值。

查看成功导入网表的 PCB 中元件有没有阻/容值，如图 1-70 所示。

图 1-69 OrCAD 里已为每个封装分配了值

图 1-70 PCB 中的元件有没有阻/容值

在 OrCAD 中每个封装分配了值的前提下，我们在输出第三方网表时，可以在“PCB Footprint”栏中原先的“{PCB Footprint}”后加入“,{Value}”，然后输出网表，如图 1-71 所示，这样从 PADS Layout 中导入网表后元件的值也会随着被导入。

图 1-71 OrCAD 中输出带阻/容值的网表设置

# 第2章 结构篇

## 2.1 PADS Layout 导入 DXF 结构图

PADS Layout 导入 DXF 有两种方法。

### 1. 方法一

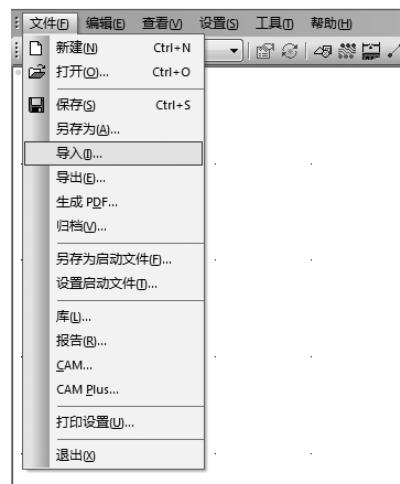

执行菜单命令【文件】 - 【导入】，如图 2-1 所示。

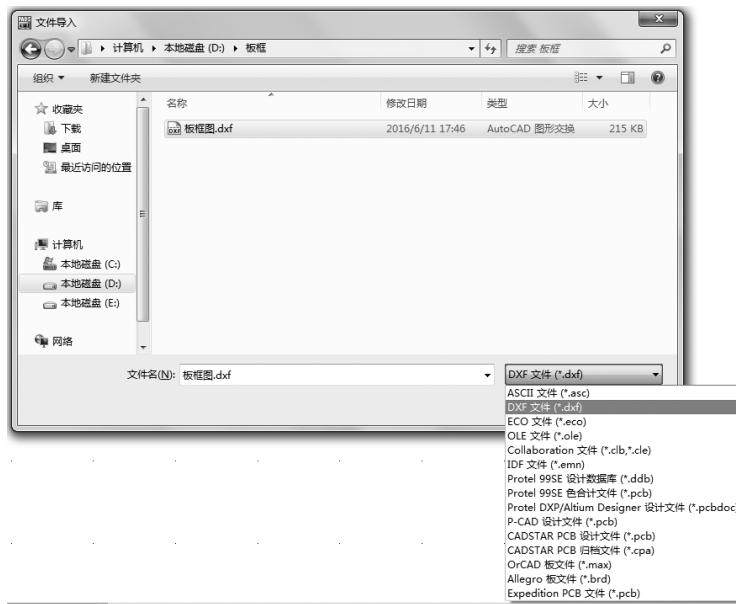

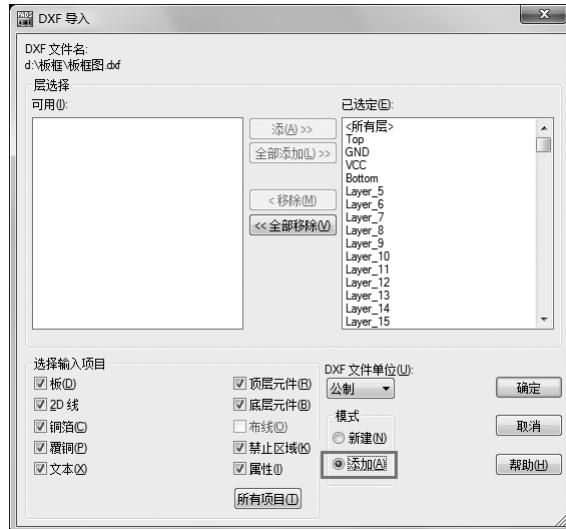

弹出“文件导入”对话框，在下拉框中选择导入的文件格式为“\*.DXF”格式，然后选择要导入的 DXF 文件，单击【打开】按钮，开始导入，如图 2-2 所示。

弹出如图 2-3 所示的窗口，按照默认的设置，单击【确定】按钮即可完成导入。

### 2. 方法二

单击标准工具栏的“绘图工具栏”图标，如图 2-4 所示。

图 2-1 执行菜单命令【文件】

图 2-2 文件导入选择窗口

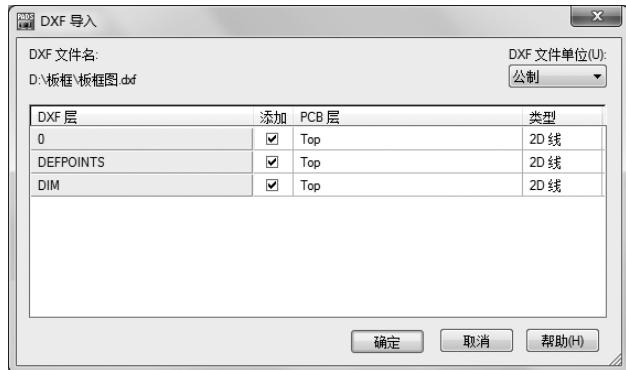

图 2-3 “DXF 导入”窗口

图 2-4 标准工具栏的“绘图工具栏”图标

在弹出的绘图工具栏中，单击“导入 DXF 文件”图标，如图 2-5 所示。

图 2-5 绘图工具栏的“导入 DXF 文件”图标

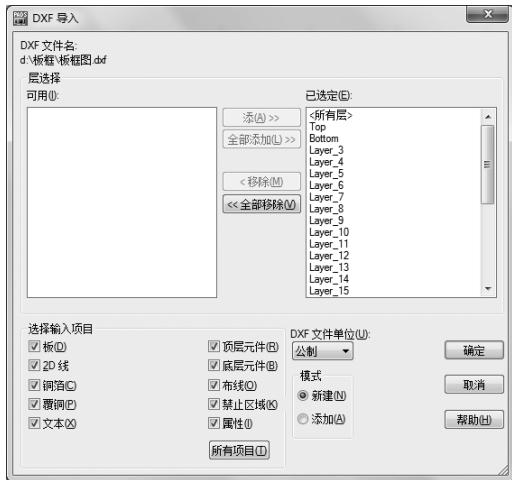

弹出“文件导入”窗口，选择要导入的 DXF 文件，单击【打开】按钮，如图 2-6 所示。

图 2-6 “文件导入”窗口

弹出如图 2-7 所示的窗口，按照默认设置，单击【确定】按钮即可完成导入。

图 2-7 “DXF 导入”窗口

## 2.2 两种导入 DXF 文件方法的区别

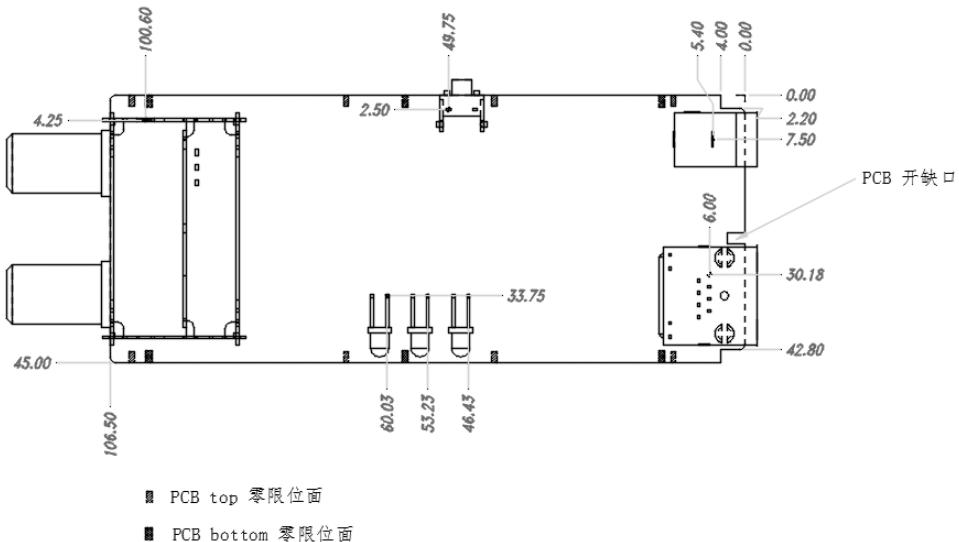

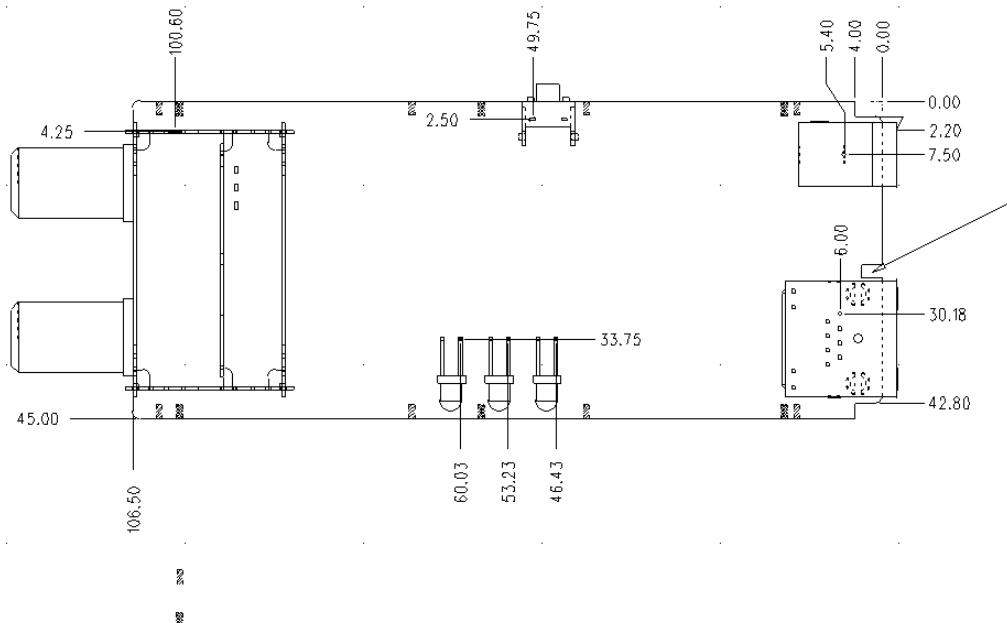

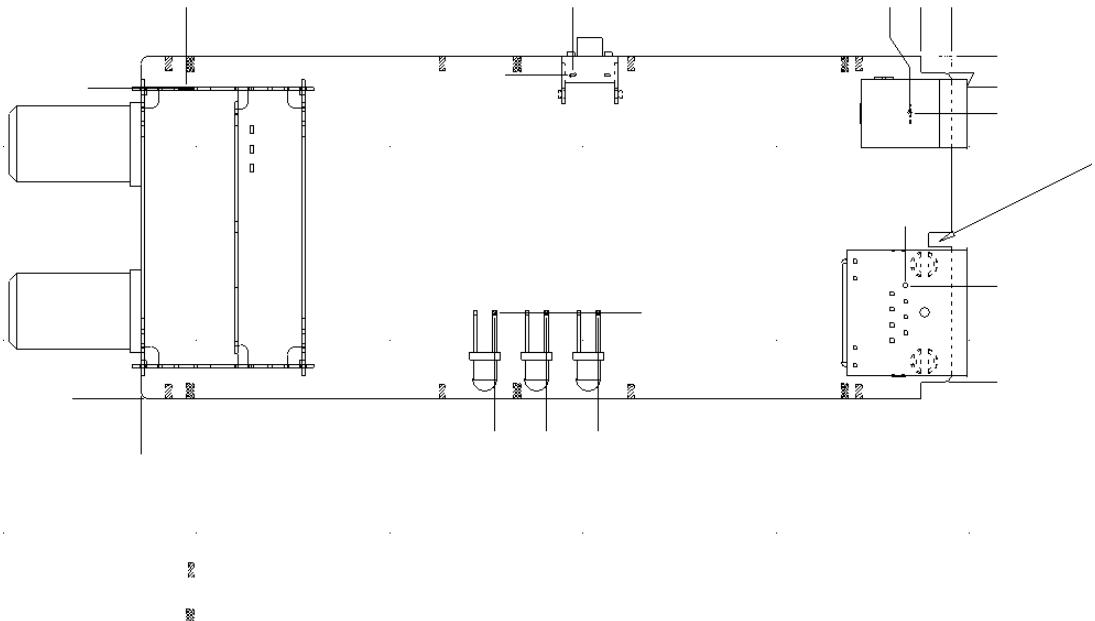

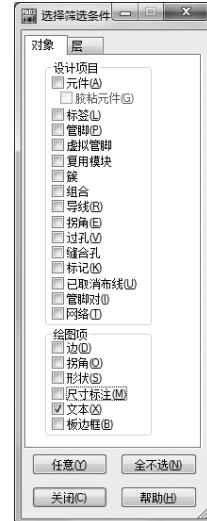

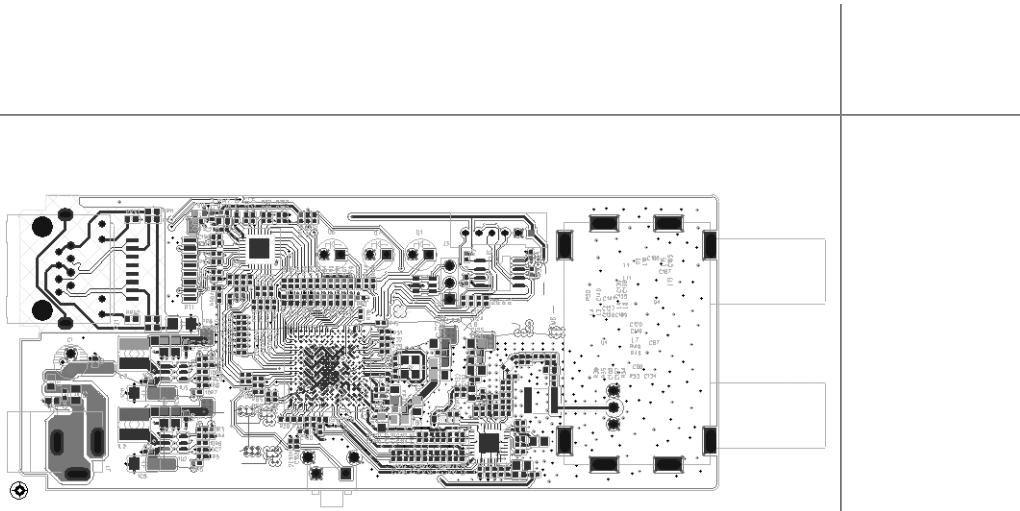

以上两种导入 DXF 文件的方法都能将图形导入，仔细观察导入的图形还存在细微的差别。AutoCAD 里的结构原图如图 2-8 所示。

图 2-8 AutoCAD 结构原图

使用方法一导入的结构图如图 2-9 所示。

使用方法二导入的结构图如图 2-10 所示。

和原图对比可知：使用方法一导入缺少了文字标注。事实上，文字标注只是隐藏了没显示出来，可以按 2.3 小节的步骤解决这个问题；使用方法二导入的结构则不会包含数字及文字标注。

图 2-9 使用方法一导入的结构图

图 2-10 使用方法二导入的结构图

## 2.3 调出结构图中的隐藏标注

要得到完整标示的图形，需要使用以下步骤实现。

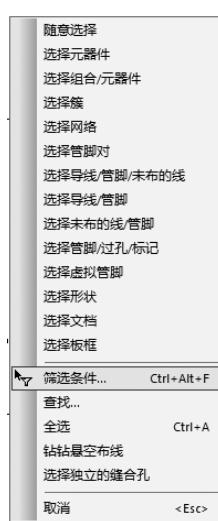

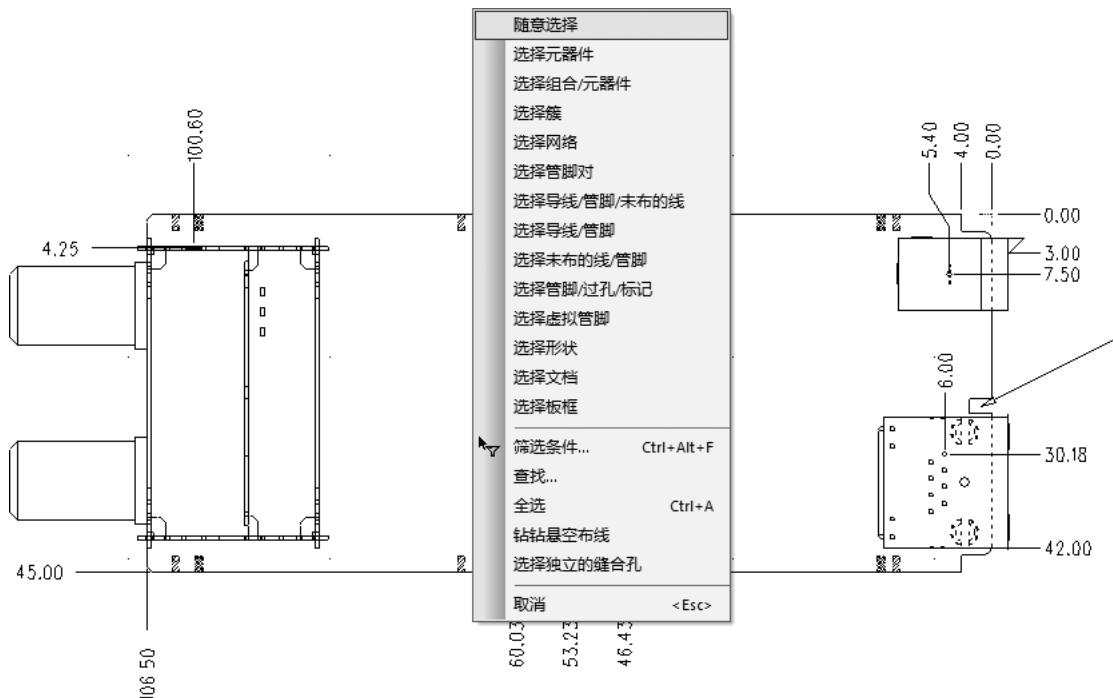

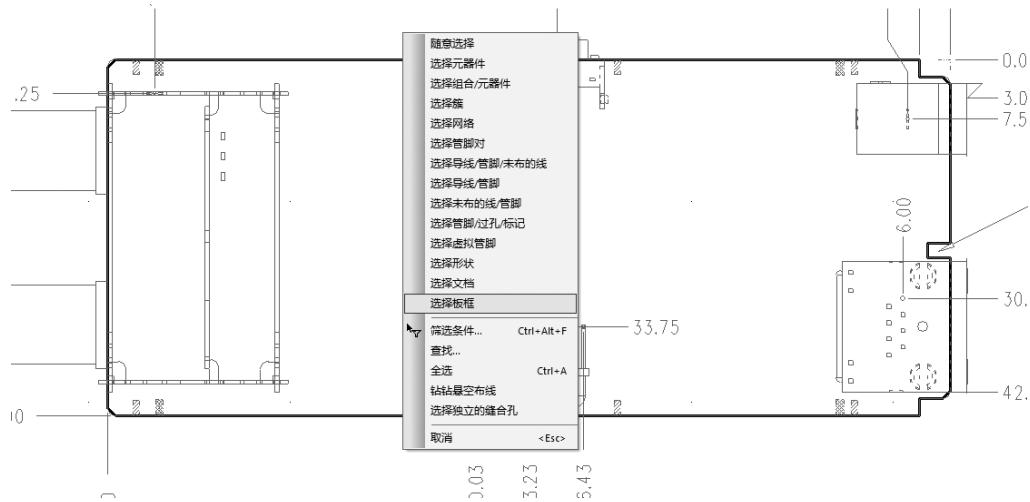

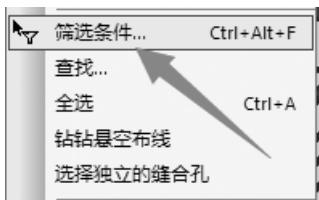

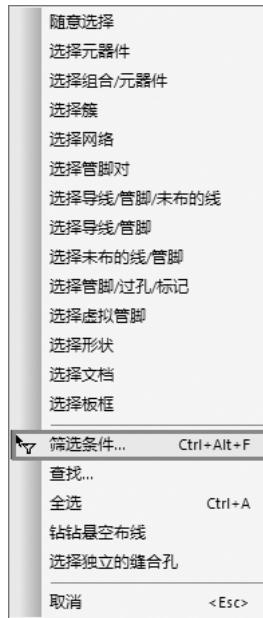

在空白的地方单击鼠标右键，执行菜单命令【筛选条件】，如图 2-11 所示。

在如图 2-12 所示弹出的窗口中，只勾选“文本”，单击【关闭】按钮关闭选择“筛选条件”窗口。

图 2-11 执行菜单命令【筛选条件】

图 2-12 勾选【文本】

按下键盘上的【Ctrl + A】组合键，或者用鼠标框选整个操作面板，选择全部文本（我们看不到文本被选择，实际上文本已经被选择上了）。

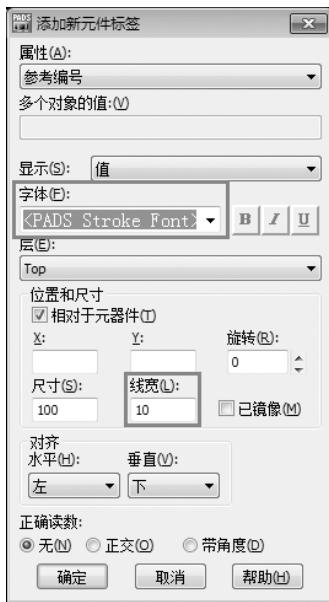

单击鼠标右键，执行菜单命令【特性】，单击“字体”下拉选择框，选择“宋体”，如图 2-13 所示，单击【确认】按钮完成参数修改。

图 2-13 【文本特性】窗口

编辑导入后的结构如图 2-14 所示。

图 2-14 编辑导入后的结构

## 2.4 在设计中导入新结构

导入结构图是一个项目最开始的步骤，实际工作中，PCB 结构并没有最终确定下来，这时候就需要以下方法将新结构导入正在进行设计的 PCB 中。

在设计中途添加新的 PCB 结构，如果原点设置的位置不当，则会造成如图 2-15 所示的

图 2-15 新结构图和设计中的其他元素重合

新结构图和设计中其他元素重合的情况，还要对它们进行分离，增加工作难度和工作量。所以，首先要把 PADS Layout 设计中的原点设置在适当远离设计区域的位置，这样添加新的 PCB 结构图就不会和原来的各种设计元素重合，带来额外的工作量。

### 1. 设置合适的导入原点

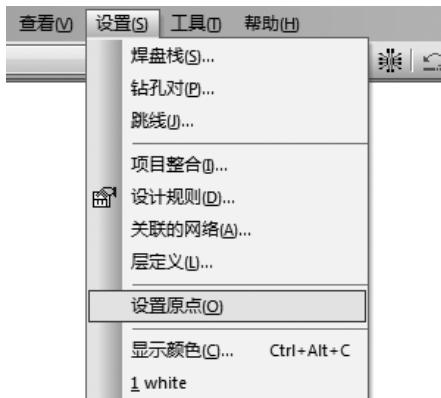

执行菜单命令【设置】 - 【设置原点】，如图 2-16 所示。

图 2-16 执行菜单命令【设置】 - 【设置原点】

在远离其他设计元素的右上角，如图 2-17 所示十字光标的位置，按下鼠标左键设置原点。

图 2-17 原点位置选择在远离设计区域的位置

这样，导入新结构后，结构图就不会和原来的设计元素有交叉了。图 2-18 为设置原点后再导入新结构图的结果。

图 2-18 设置原点后再导入新结构图的结果

## 2. 设计中导入新结构步骤

### 1) 方法一

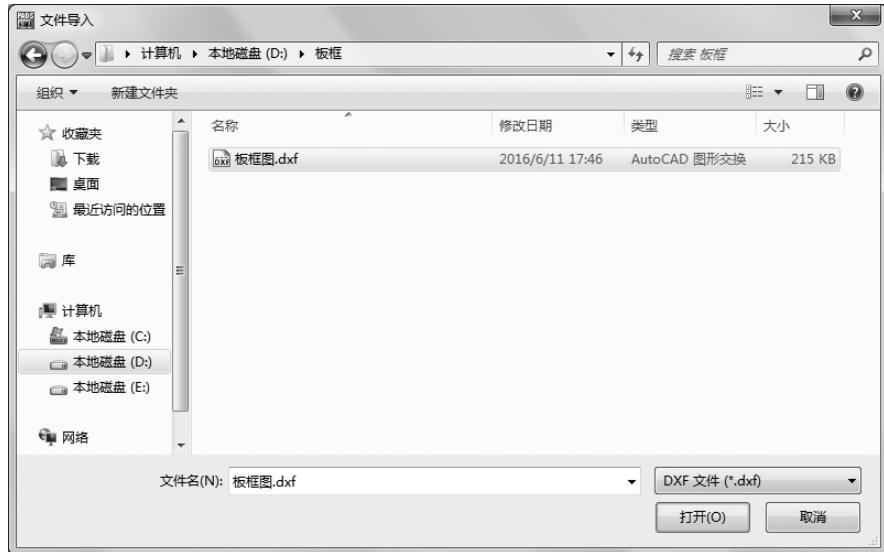

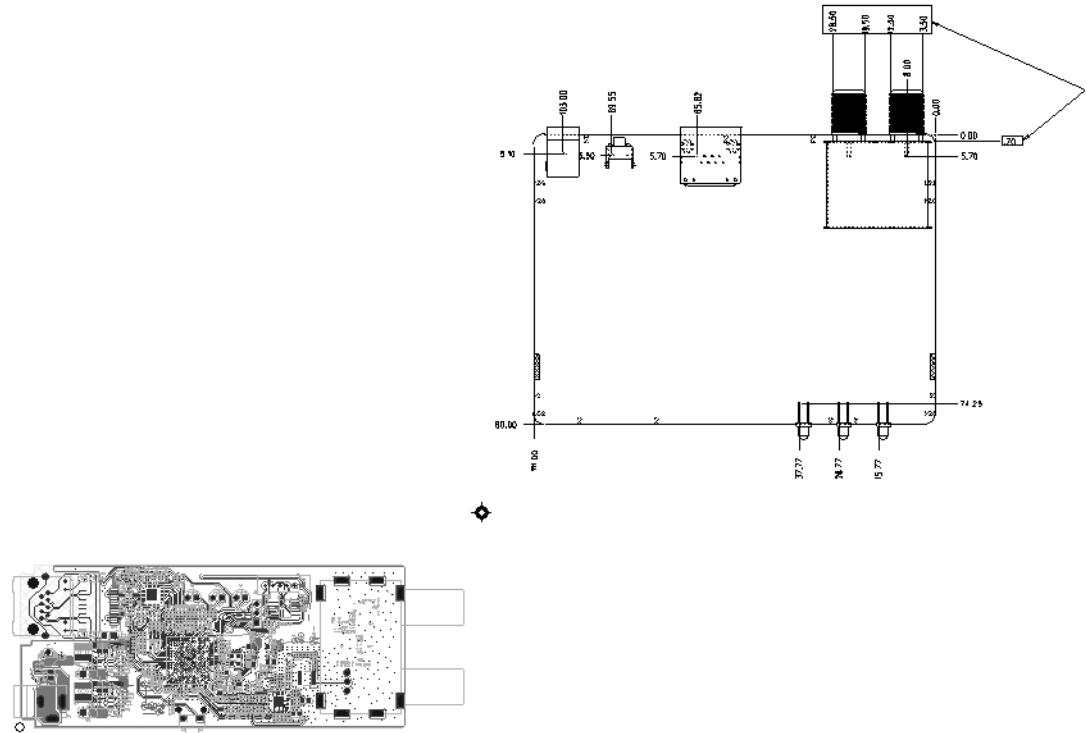

方法一步骤同 2.1 小节的方法一，但在弹出的“DXF 导入”窗口中，要将“模式”选择为“添加”（见图 2-19），最后单击【确定】按钮即可。

图 2-19 将“模式”选择为“添加”

## 2) 方法二

方法二与 2.1 小节的方法二相同，只要单击“导入 DXF 文件”图标，按步骤进行即可。

图 2-20 绘图工具栏的“导入 DXF 文件”图标

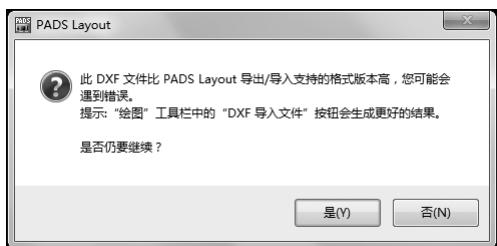

## 2.5 使用导入的方法一出现比导出导入格式版本高

遇到如图 2-21 所示的这个窗口，我们单击【是】按钮继续之后，通常会出现如图 2-22 所示的以近似线段替代椭圆的窗口。

图 2-21 导入的 DXF 版本过高提示

图 2-22 近似线段替代椭圆的窗口

在单击几个【确定】按钮之后，导入的结构图对比原图会有一些缺失，有些文字会出现多余的字符等，如果不影响到整体倒是没什么关系的。

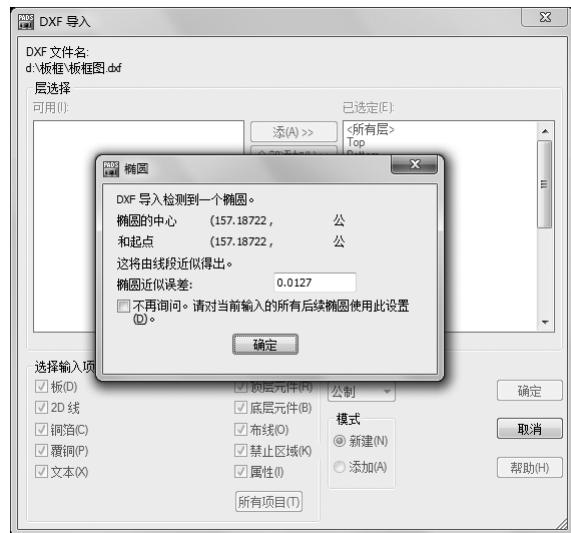

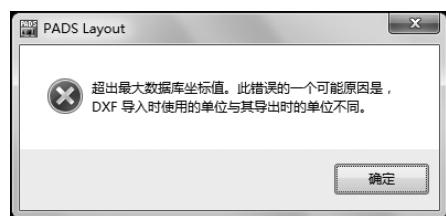

## 2.6 超出最大数据库坐标值

导入时出现如图 2-23 所示的错误。

首先要确认导入的结构图是否尺寸过大，PADS 工作区域最大为 56inch × 56inch，大约为 14.2m × 14.2m，普通产品很难达到这个面积。

排除了这个原因后，第二个原因也如窗口提示的那样，导入 DXF 文件时选择的文件单位和 DXF 本身设计时的单位不一致。PADS 在导入 DXF 文件时会自动选择导入单位（有时候并非 DXF 本身设计时的单位），如果不是导入时手动选择了

图 2-23 超出最大数据库坐标值错误

单位，一般也不会是这个原因。当我们的结构图导入不成功时，以下方法可以解决绝大部分的问题。

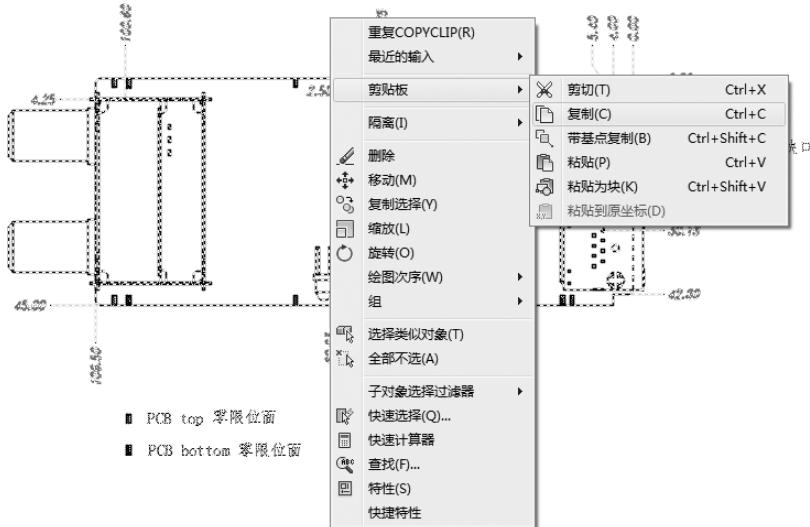

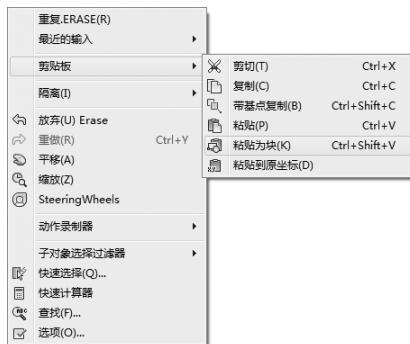

首先我们用 AutoCAD 打开刚刚要导入的 DXF 文件（这里以 AutoCAD2015 为例）。用鼠标框选所有图形，单击鼠标，右键执行菜单命令【剪贴板】 - 【复制】，如图 2-24 所示。

图 2-24 复制图形

单击“新建”图标，新建一个空白图形文件，如图 2-25 所示。

图 2-25 新建空白文件

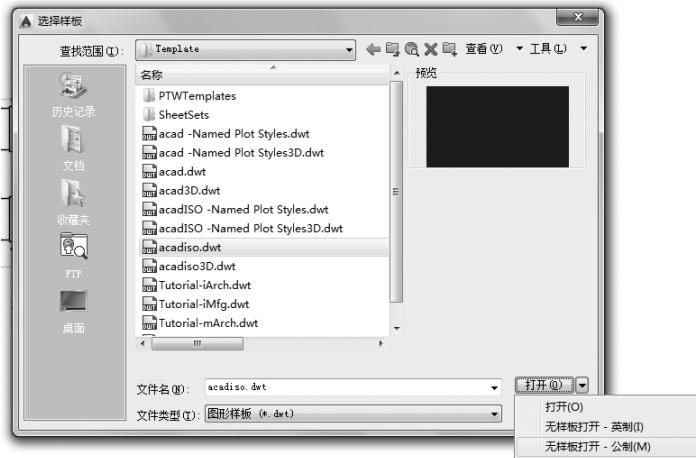

在弹出的窗口中，单击【打开】下拉菜单，选择“无样板打开 - 公制(M)”（如果是用英制设计的 DXF 则选择“无样板打开 - 英制(M)”），如图 2-26 所示。

在新的图形文件中，单击鼠标右键执行菜单命令【剪贴板】 - 【粘贴为块】，如图 2-27 所示。

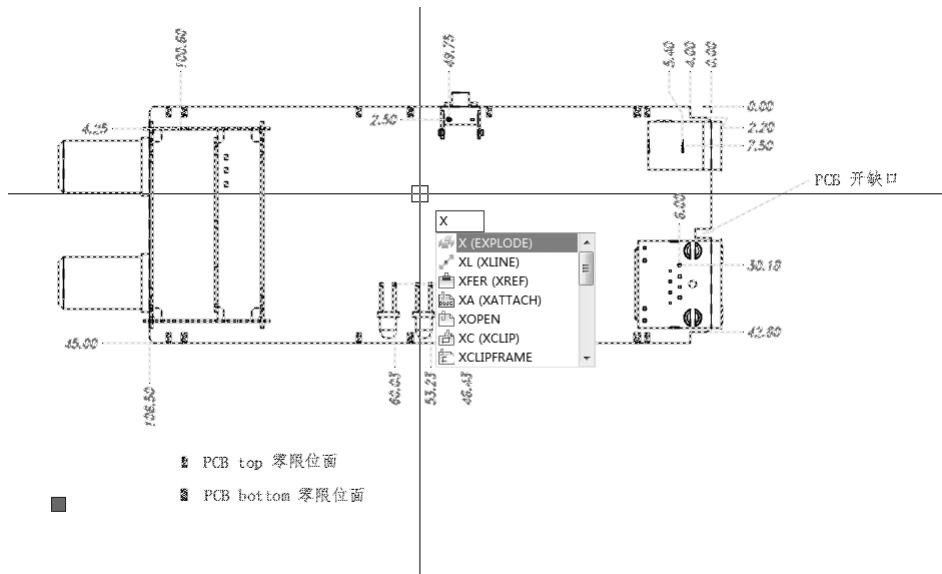

框选粘贴后的块，按下键盘上的【X】键，如图 2-28 所示，单击【Enter】键，键入命令炸开块。

执行菜单命令【文件】 - 【保存】，在弹出的窗口中打开文件类型的下拉菜单，选择保存成“AutoCAD R12/LT2 DXF (\*.dxf)”文件，如图 2-29 所示。

用 PADS Layout 导入刚刚保存的 DXF 文件即可。

图 2-26 设定设计环境的单位

图 2-27 将图形粘贴为块

图 2-28 炸开 (Explode) 块

图 2-29 保存成 AutoCAD R12/LT2 DXF 文件

## 2.7 使用 2.6 节的方法导入后还是空白

在有些情况下，我们在使用 2.6 节的方法导入结构图后，PADS Layout 的工作区域还是一片空白，或者导入的结构图不完整，这时候很多人会误以为结构图没有导入成功。造成这种现象的原因是，结构图在 AutoCAD 里绘制的时候放在了除第 0、1、2 层的其他层上，导入 PADS Layout 后被背景色掩盖了。

我们来看以下这个例子：图 2-30 是 AutoCAD 里的原图，我们用以上方法导入结构图后，PADS Layout 没有任何反应，工作区域也还是一片空白。

图 2-30 AutoCAD 结构原图

### 1. 方法一，PADS Layout 中更改

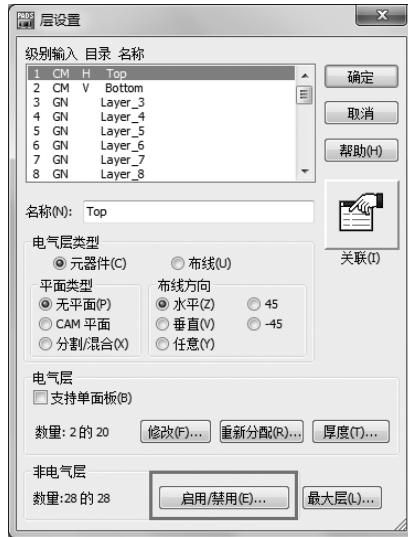

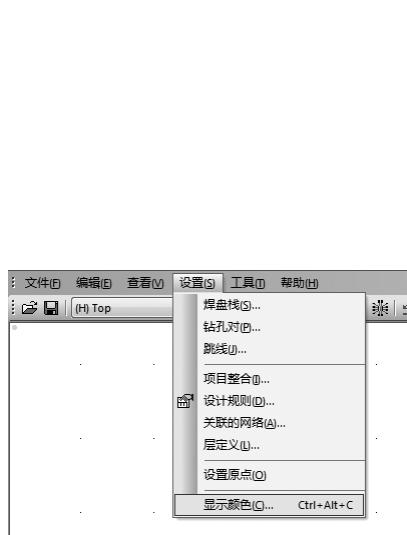

执行菜单命令【设置】 - 【层定义】，如图 2-31 所示。

弹出的“层设置”对话框中，单击【启用/禁用】按钮，如图 2-32 所示。

图 2-31 执行菜单命令【设置】 - 【层定义】

图 2-32 “层设置”窗口

弹出的“启用/禁用层”窗口中，我们可以看到第 16 层是有数据存在的，如图 2-33 所示。

| #  | 启用                                  | 有数据 | 名称       | 类型 |  |

|----|-------------------------------------|-----|----------|----|--|

| 6  | <input checked="" type="checkbox"/> | 否   | Layer_6  | 常规 |  |

| 7  | <input checked="" type="checkbox"/> | 否   | Layer_7  | 常规 |  |

| 8  | <input checked="" type="checkbox"/> | 否   | Layer_8  | 常规 |  |

| 9  | <input checked="" type="checkbox"/> | 否   | Layer_9  | 常规 |  |

| 10 | <input checked="" type="checkbox"/> | 否   | Layer_10 | 常规 |  |

| 11 | <input checked="" type="checkbox"/> | 否   | Layer_11 | 常规 |  |

| 12 | <input checked="" type="checkbox"/> | 否   | Layer_12 | 常规 |  |

| 13 | <input checked="" type="checkbox"/> | 否   | Layer_13 | 常规 |  |

| 14 | <input checked="" type="checkbox"/> | 否   | Layer_14 | 常规 |  |

| 15 | <input checked="" type="checkbox"/> | 否   | Layer_15 | 常规 |  |

| 16 | <input checked="" type="checkbox"/> | 是   | Layer_16 | 常规 |  |

| 17 | <input checked="" type="checkbox"/> | 否   | Layer_17 | 常规 |  |

| 18 | <input checked="" type="checkbox"/> | 否   | Layer_18 | 常规 |  |

| 19 | <input checked="" type="checkbox"/> | 否   | Layer_19 | 常规 |  |

| 20 | <input checked="" type="checkbox"/> | 否   | Layer_20 | 常规 |  |

图 2-33 “启用/禁用层”窗口查看层数据

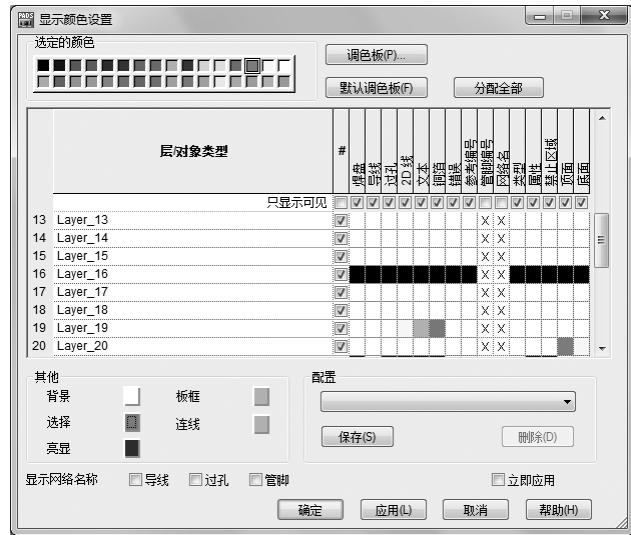

单击【确定】按钮，退出“层定义设置”。执行菜单命令【设置】 - 【显示颜色】，如图 2-34 所示。

将第 16 层的颜色设置为和背景不相同的颜色，如图 2-35 所示，设置后单击【确定】按钮应用设置。

图 2-34 执行菜单命令

【设置】 - 【显示颜色】

图 2-35 设置第 16 层的颜色

这时我们就能在 PADS Layout 工作区域中看到导入后的结构图了，如图 2-36 所示。

图 2-36 PADS Layout 工作区域中的结构图

## 2. 方法二，AutoCAD 中更改

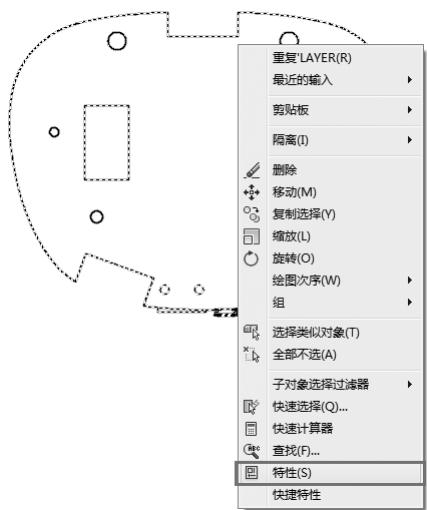

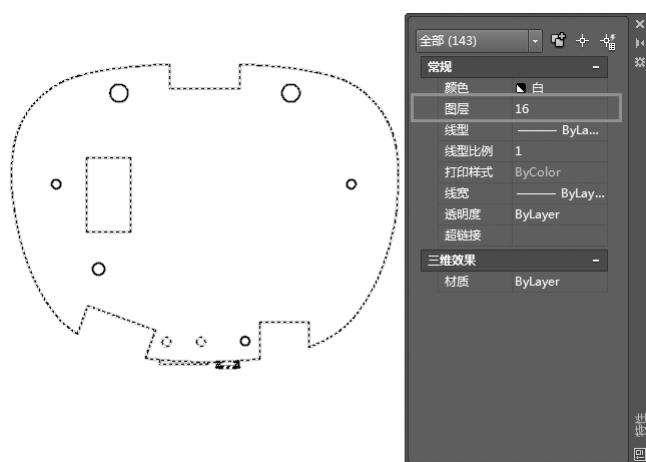

用 AutoCAD 打开 DXF 文件，框选图形，单击鼠标右键执行菜单命令【特性】，如图 2-37 所示。

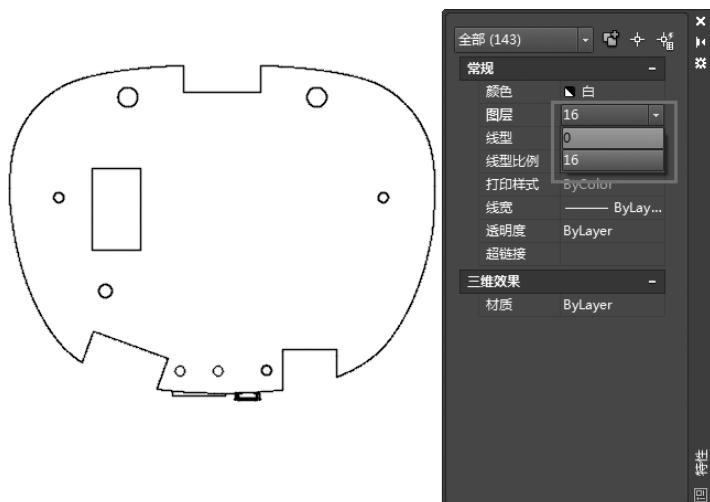

可以看到图形是放在第 16 层的，如图 2-38 所示。

图 2-37 调出图形特性

图 2-38 图形在第 16 层

单击图层下拉按键，选择第 0 层，如图 2-39 所示，保存后用 PADS Layout 导入即可。

图 2-39 将图形放到第 0 层

## 2.8 导入的结构图比实际小

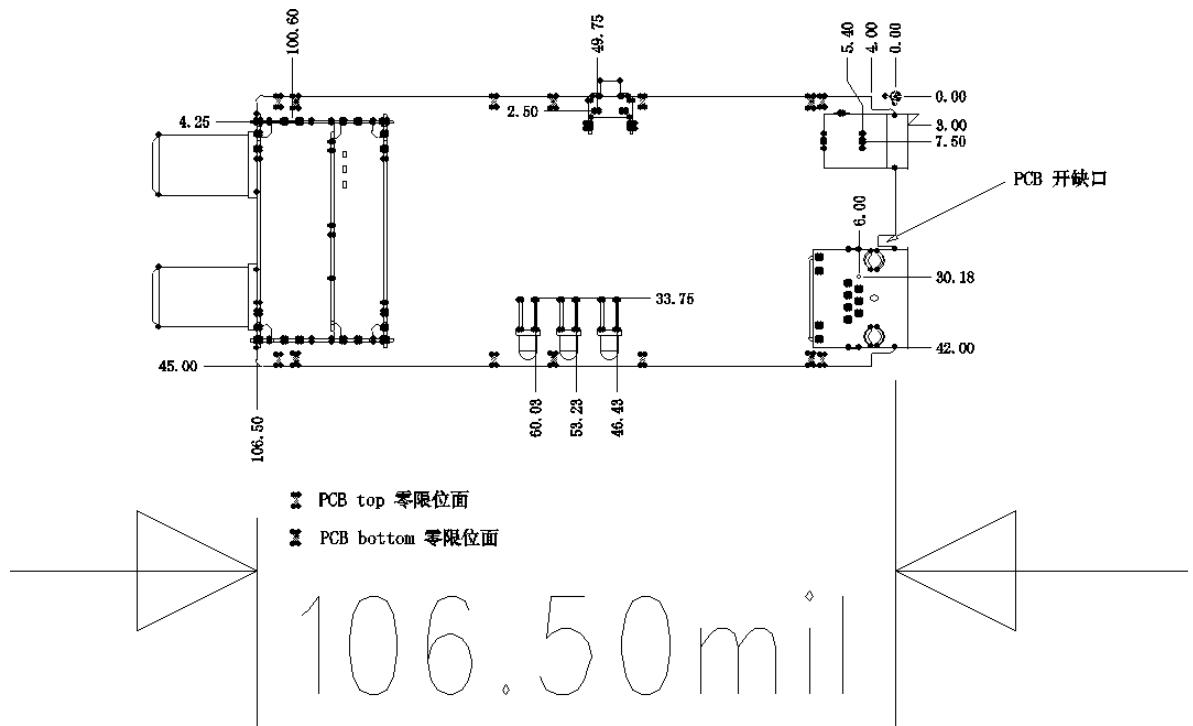

导入的结构图发现比实际小，如图 2-40 所示。

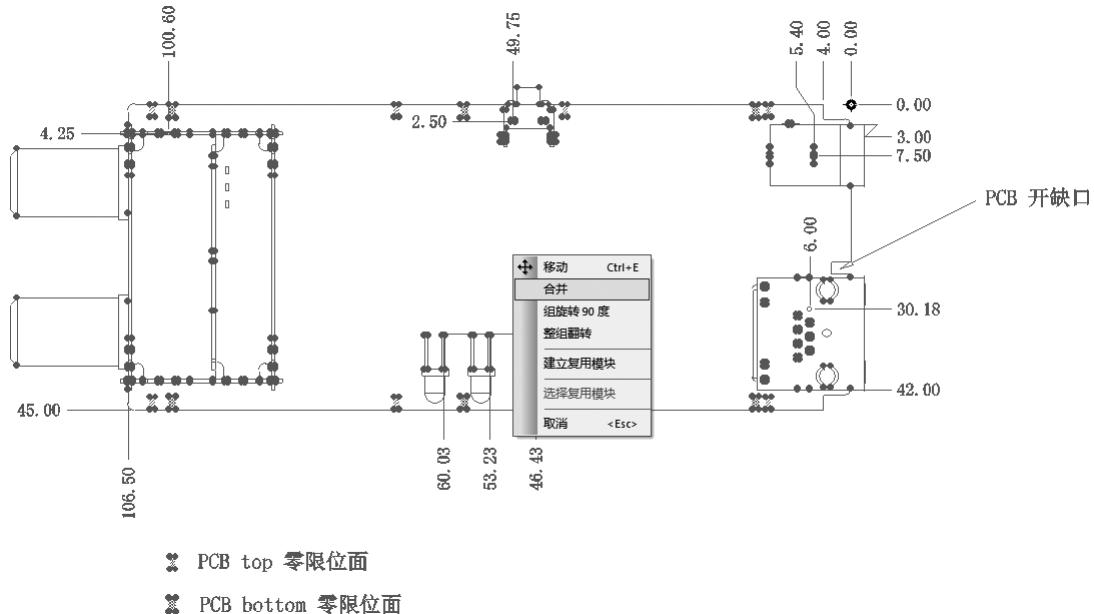

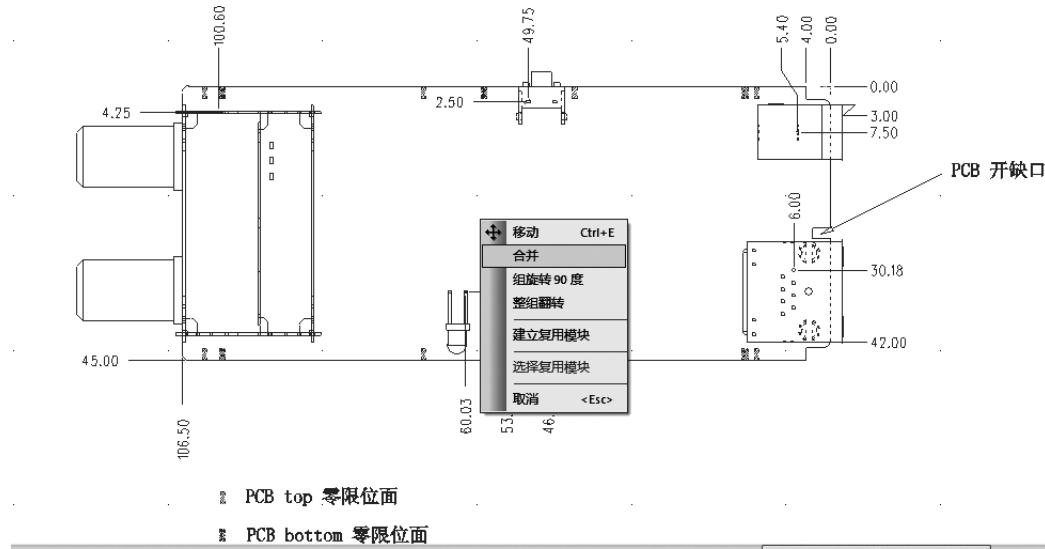

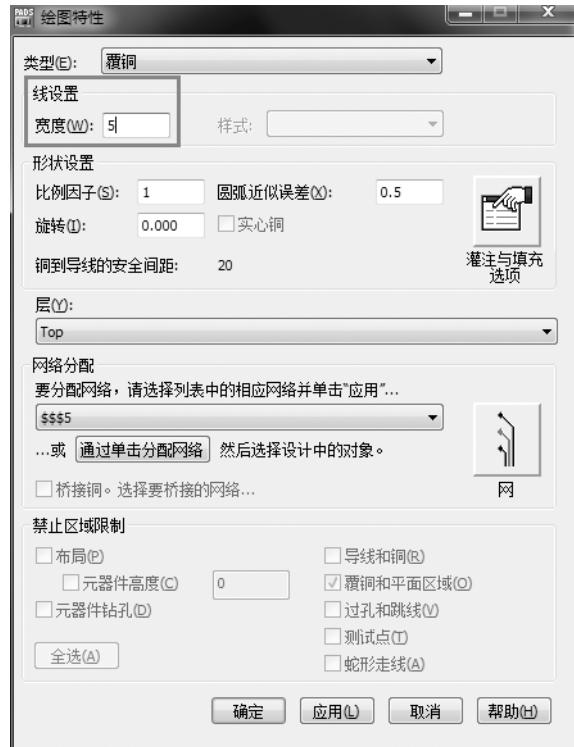

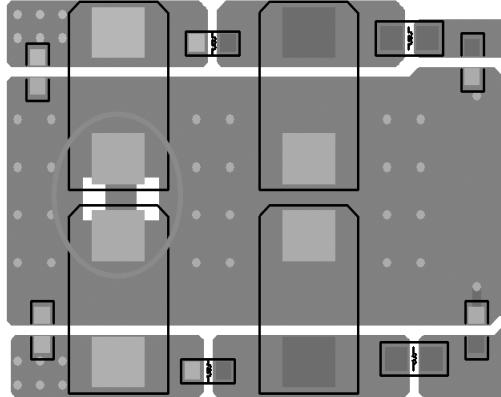

在 PADS Layout 中可以将结构图按比率放大，单击鼠标右键，执行菜单命令【形状】，选择整个图形，单击鼠标右键，执行菜单命令【合并】，如图 2-41 所示。

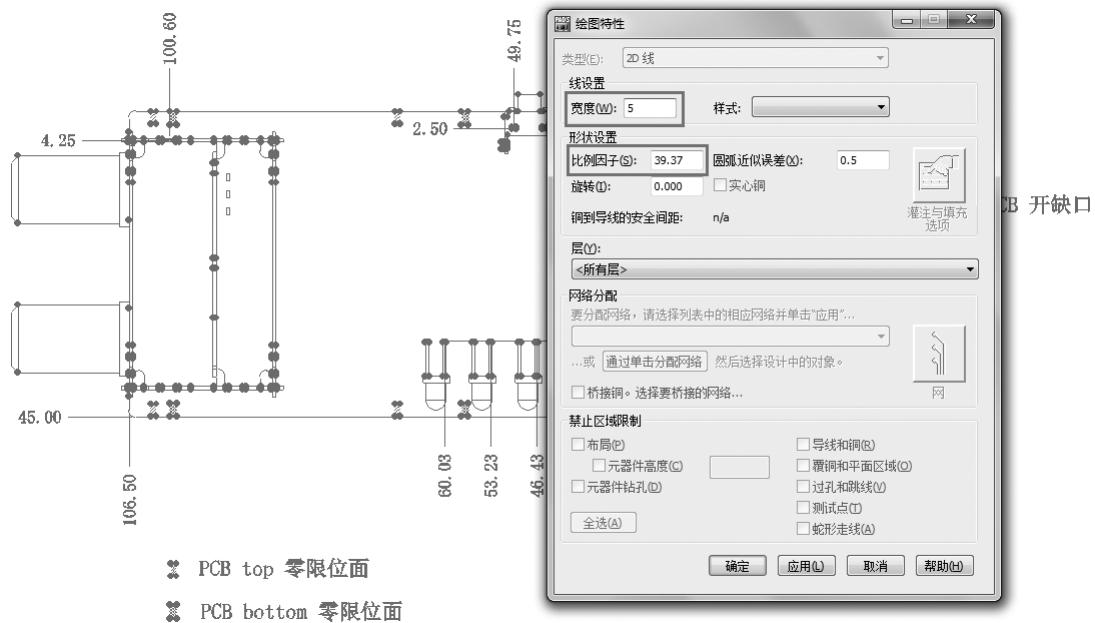

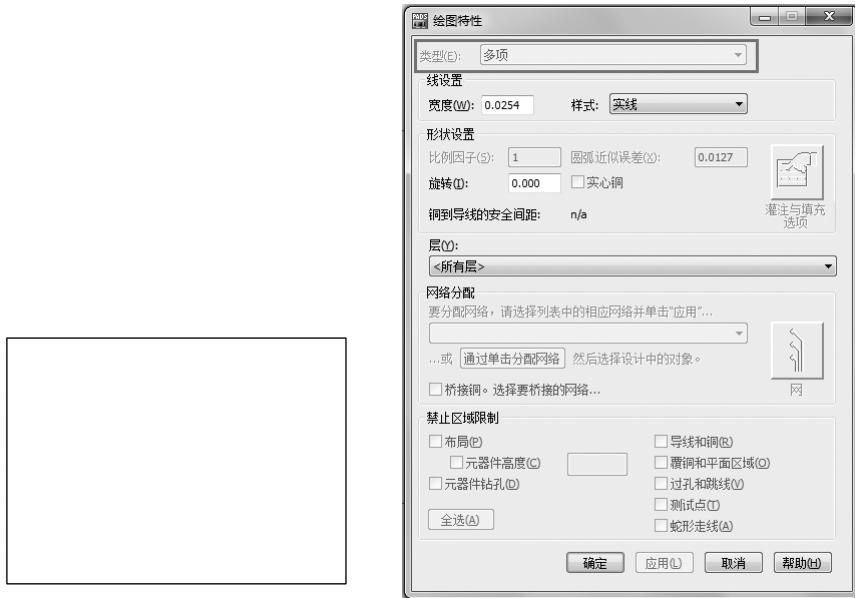

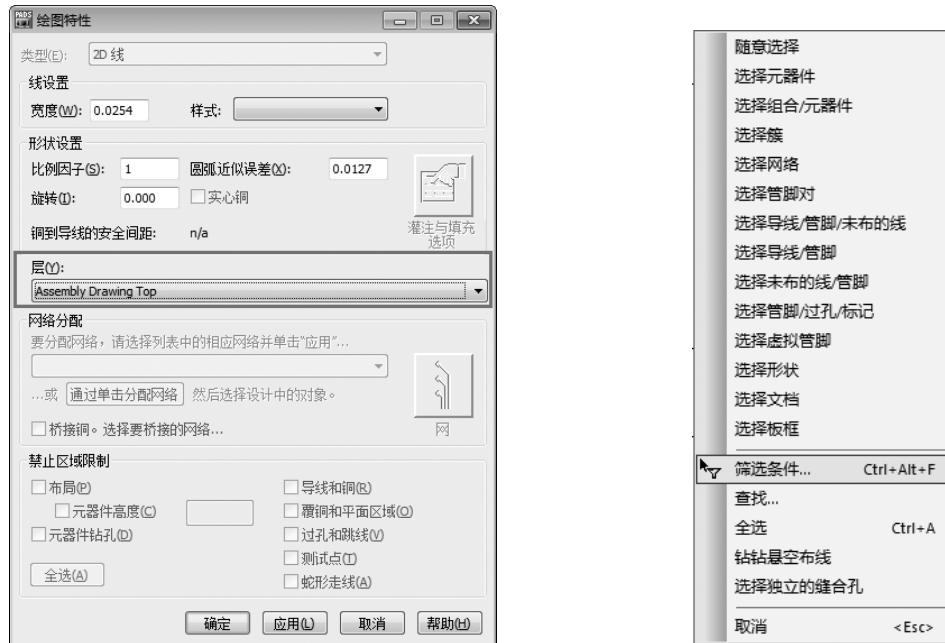

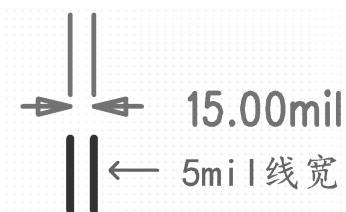

单击鼠标右键，执行菜单命令【特性】。进入“绘图特性”对话框，“宽度”可以改为 5mil，将“比例因子”设成 39.37 ( $1\text{m} \approx 39.37\text{mil}$ )，如图 2-42 所示，单击【确定】按钮。

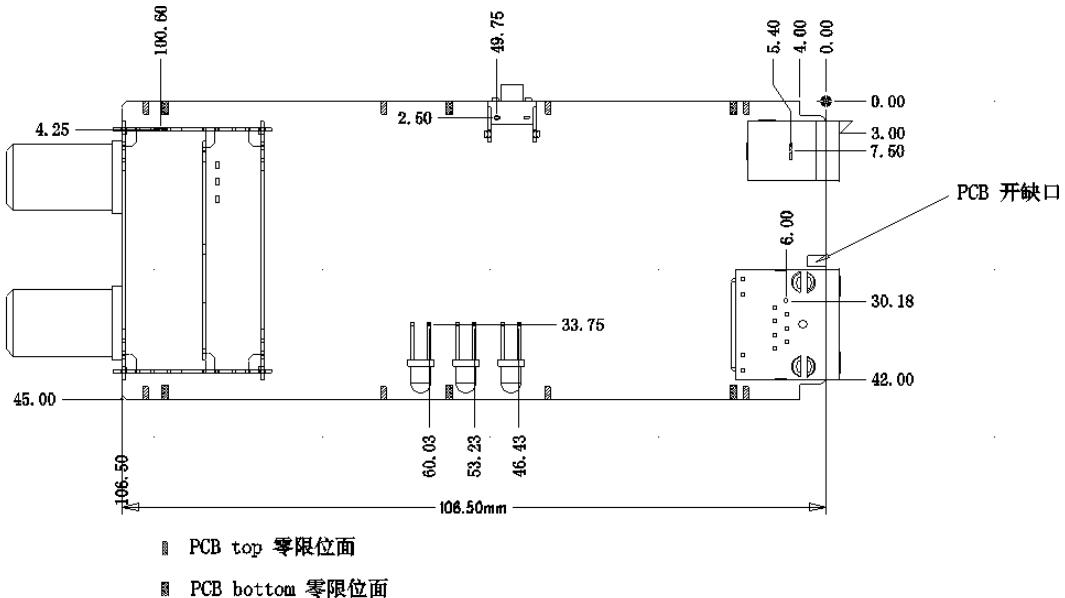

图 2-40 导入操作失误造成公制单位成为英制单位

图 2-41 图形合并操作

用这个方法得到的图形尺寸与原图尺寸相比存在误差，但误差极其微小可以忽略。图 2-43 为已完成应用的效果。

图 2-42 “绘图特性”对话框

图 2-43 完成效果

## 2.9 2D 线转换板框

图 2-44 是刚导入的结构图，是由 4 段 2D 线构成的图形。

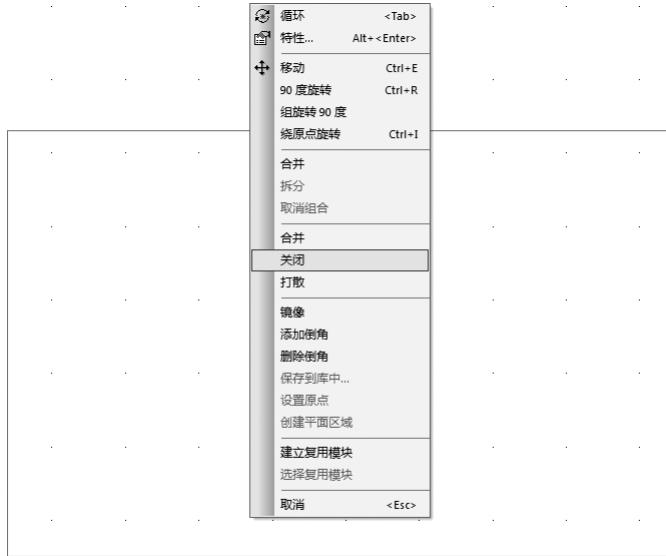

单击鼠标右键，执行菜单命令【形状】，框选整个图形，在右键菜单中进入绘图特性。“类型”那一栏处于灰色不可选的状态，而且显示的是“多项”，如图 2-45 所示。此时这些

2D 线不能转换成板框，在 PADS Layout 中只有闭合的 2D 线才能转换成板框。

图 2-44 结构外形

图 2-45 图形的绘图特性

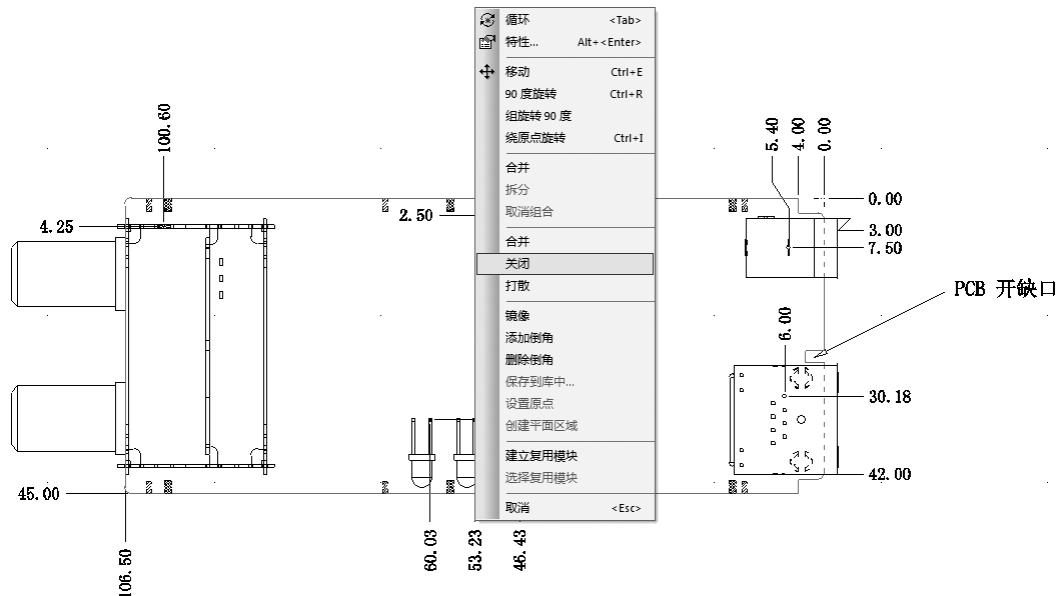

框选整个图形，单击鼠标右键执行菜单命令【关闭】，如图 2-46 所示，将封闭图形闭合连接形成一个整体。

图 2-46 闭合图形

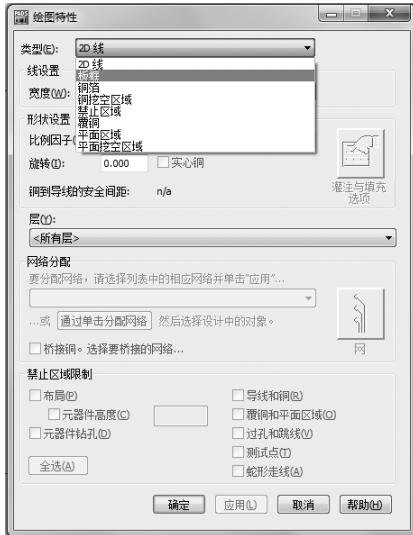

再次选择整个图形，进入绘图特性就可以看到“类型”可以编辑了，点开下拉框，选择“板框”，如图 2-47 所示，再单击【确定】按钮应用设置，2D 线就转换成板框了。

图 2-47 选择绘图的类型

当然以上是最顺利的情况，能使用以上方法的图形需要满足一定的条件。更多的是有重叠线段、线段间缝隙太大等因素造成的不可闭合，这与结构原本的物理构成或者结构绘制者的不良习惯有关。如果只遇到一两处上述问题，我们只要在 PADS 中简单删改、修补一下就可以顺利闭合了。但如果板框外形特别复杂，重叠线段、线段间缝隙大的地方太多，修补起来再生成，板框效率就会低很多。这个方法的局限性比较大。

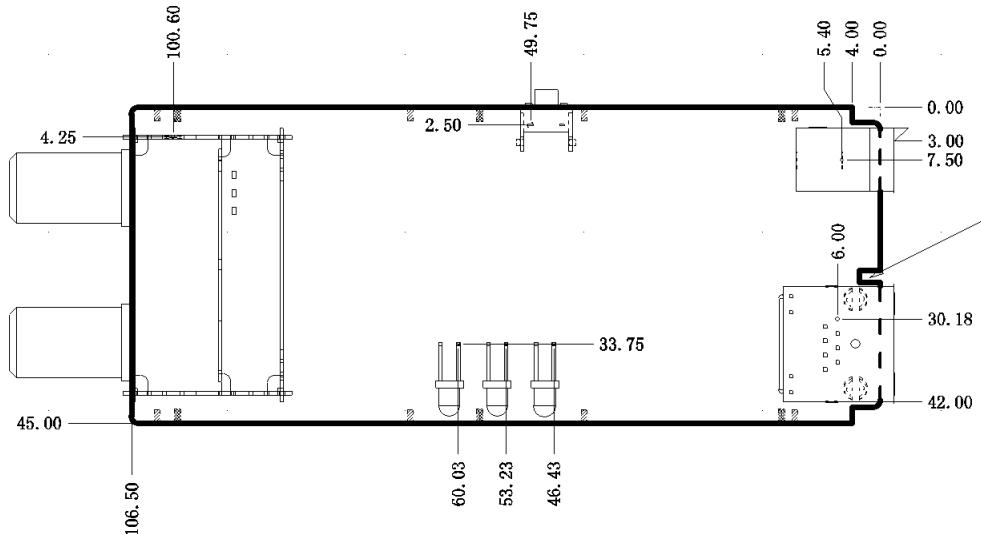

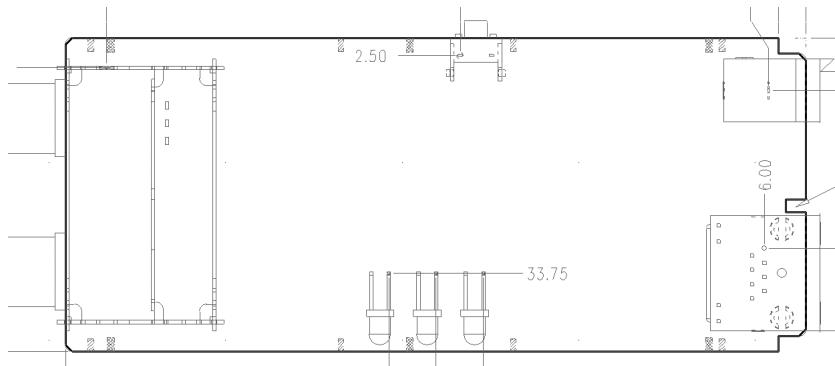

举个例子，PADS Layout 导入结构图后，我们要将它的物理边框（图 2-48 中黑色加粗的边框）转成板框。

图 2-48 PCB 的板框外形

按住键盘上的【Ctrl】键多选，同时用鼠标一条一条地框选边框的线段，直到所有线段（上图黑色加粗的边框）被框选完毕，单击鼠标右键执行菜单命令【关闭】，闭合图形，如

图 2-49 所示。

图 2-49 闭合板框外形

图 2-50 无法闭合图形报错信息一

输出窗口显示如图 2-52 所示的报错信息。

这时候工作区域底部会弹出输出窗口的报错信息，如图 2-50 所示。

单击图中坐标，指针会直接跳到图形中有问题的位置，如图 2-51 所示加粗的线段，底下有短划线。

删除底下的短划线后，再次框选边框，单击鼠标右键，执行菜单命令【关闭】，输

图 2-51 线段重合位置

图 2-52 无法闭合图形报错信息二

具体情况是，按键图形的一边与板框外形的两根 2D 线搭在一块，使得关闭的命令不能继续进行。造成图形不可闭合的原因有很多，但报错信息里往往不会提到具体是什么原因导致的，这也是转换法生成板框的一个缺点。

## 2.10 绘制生成板框

继续以上例来演示如何采用绘制法来完成板框。

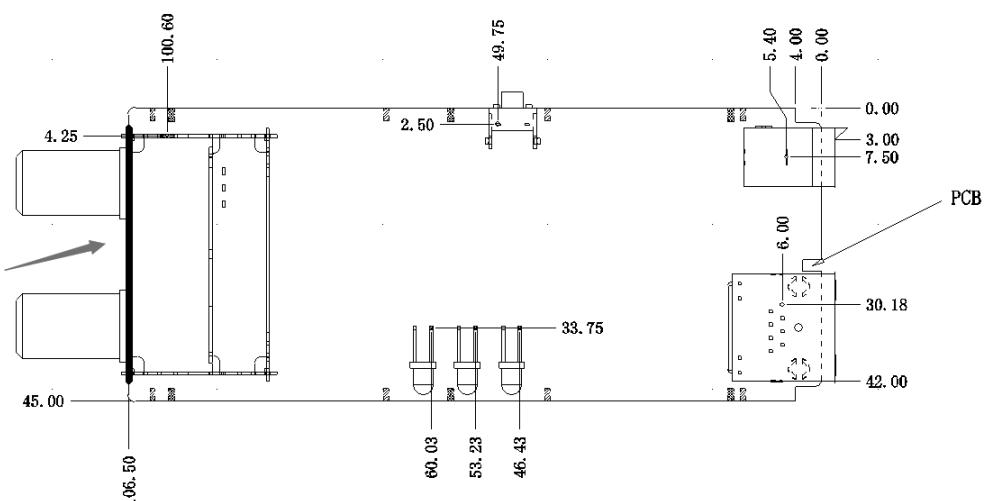

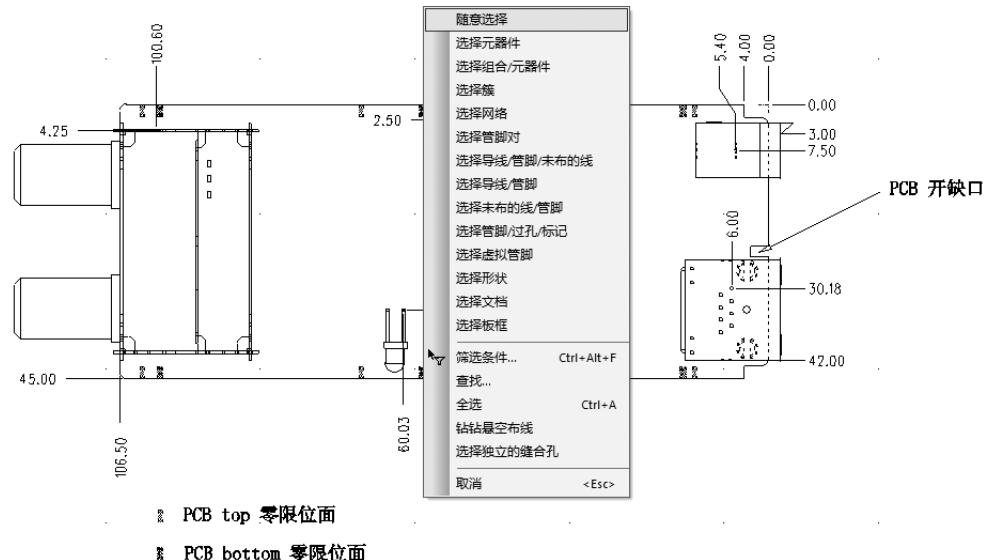

成功导入结构图后，在空白区域单击鼠标右键，执行菜单命令【随意选择】，如图 2-53 所示。

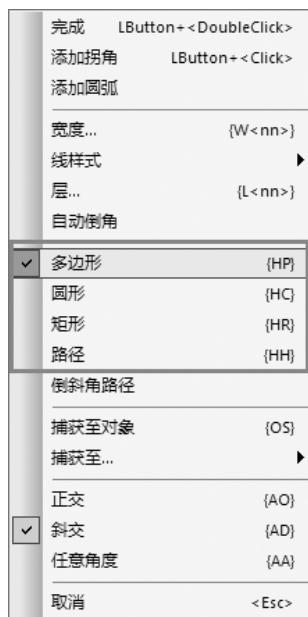

图 2-53 执行菜单命令【随意选择】

单击绘图工具栏的“板框和挖空区域”图标，如图 2-54 所示。

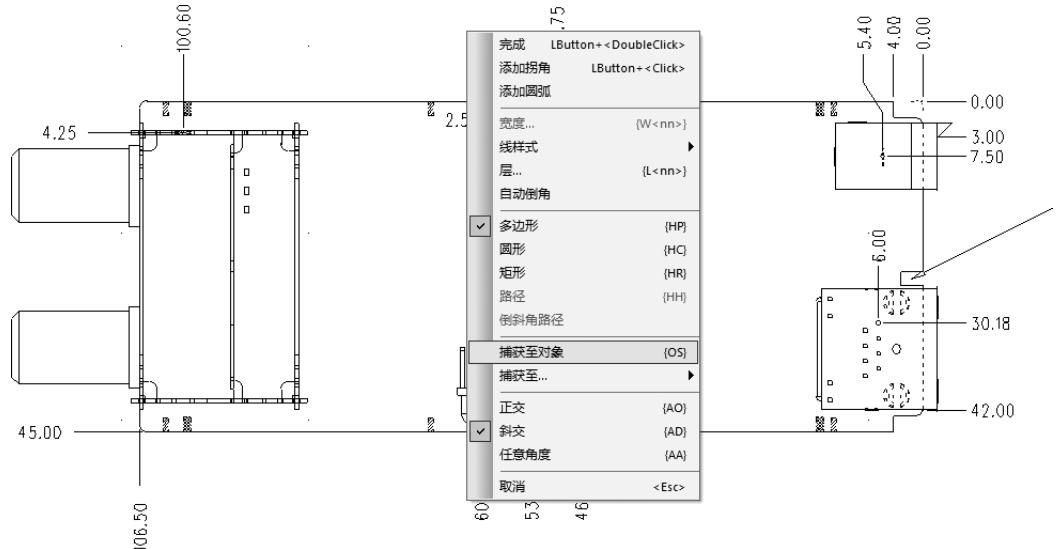

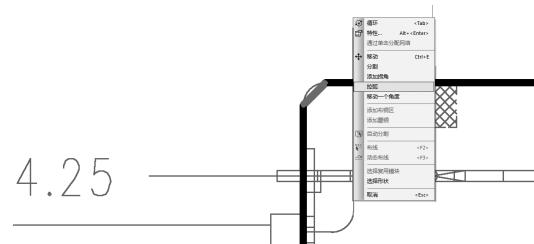

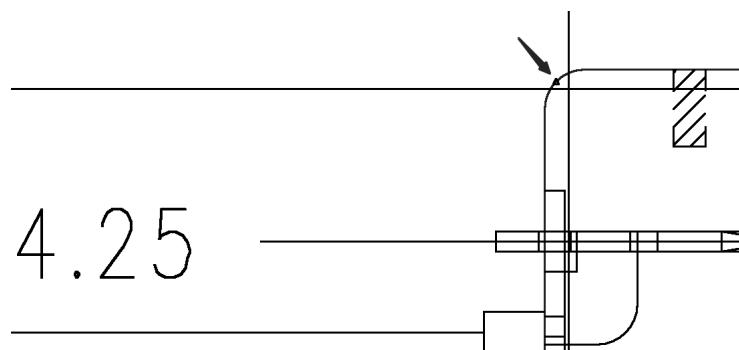

在空白区域单击鼠标右键，执行菜单命令【捕获至对象】，如图 2-55 所示。由于这个板框是由横平竖直和四分之一圆周构成的，所以其他只要勾选“多边形”及“斜交”来绘制就可以了。

图 2-54 “板框和挖空区域”图标

图 2-55 执行菜单命令【捕获至对象】

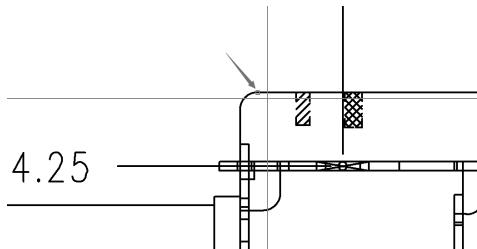

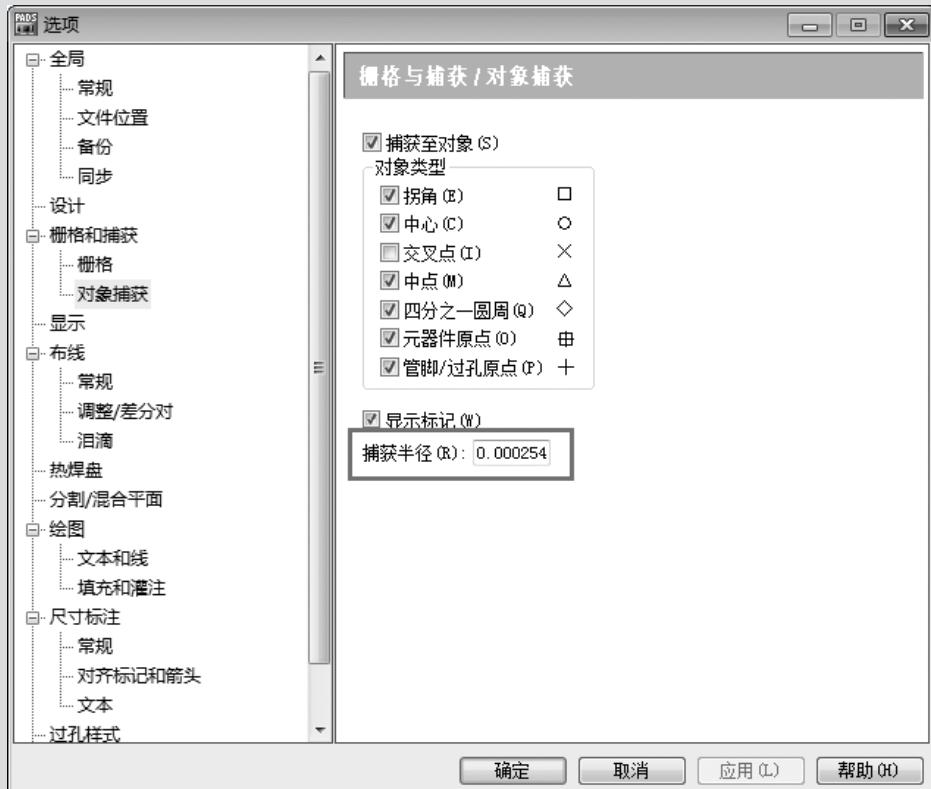

菜单命令【捕获至对象】也可以在选项菜单的“对象捕获”中找到，如图 2-56 所示，这里要确保“显示标记”勾选上，同时这里还列举了这些标记的图形含义。

图 2-56 “对象捕获”选项卡

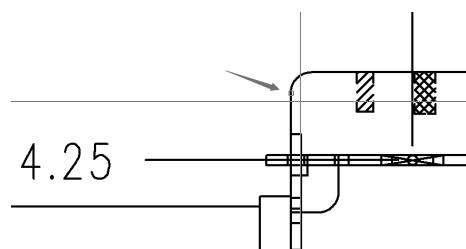

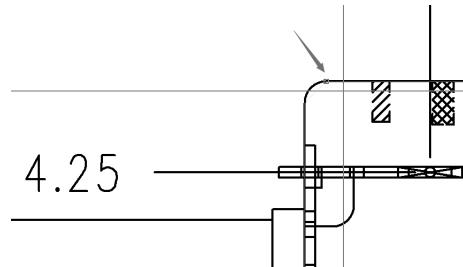

设置完毕后，我们从图形的左上角开始。将鼠标移至图形的左上角，这时候四分之一圆周和线段的结合处会出现小方框，如图 2-57 所示。由图 2-56 可知意为拐角的标记，单击鼠标左键开始画多边形。

移动鼠标至四分之一圆周与另一条线段的结合处，显示小方框图形后单击鼠标左键，如图 2-58 所示。

图 2-57 捕获左上角四分之一圆周与线段的结合处显示小方框标记

图 2-58 捕获左上角四分之一圆周与另一条线段的结合处

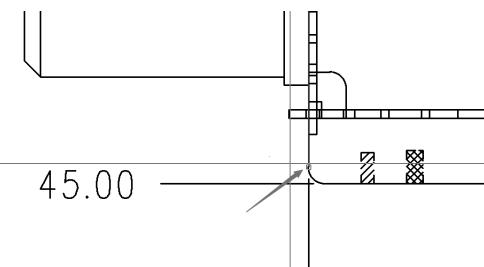

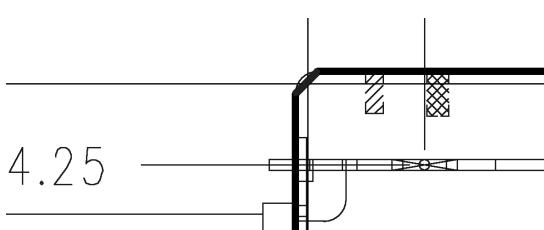

鼠标继续移至左下角四分之一圆周处，在四分之一与线段的结合处出现小方框后单击鼠标左键，如图 2-59 所示。

相同的操作，直到鼠标回至左上角的绘画起始点，如图 2-60 所示。

图 2-59 捕获左下角四分之一圆周与线段的结合处

图 2-60 回到起点完成多边形绘制

双击鼠标左键，完成多边形的绘制，绘制完的多边形如图 2-61 所示，所有的四分之一圆周都由弦替代了。

图 2-61 四分之一圆周都由弦替代的板框

在空白区域单击鼠标右键，执行菜单命令【选择板框】，如图 2-62 所示。

图 2-62 执行菜单命令【选择板框】

单击选择左上角四分之一圆周的弦，如图 2-63 所示。

单击鼠标右键，执行菜单命令【拉弧】，如图 2-64 所示。

图 2-63 选中其中一根弦

图 2-64 执行菜单命令【拉弧】

移动鼠标出现如图 2-65 所示的小三角形，单击鼠标左键，完成拉弧。

图 2-65 拉弧直至显示小三角形标记

同样的方法完成其他三个四分之一圆周的拉弧，这样整个板框就完成了。

用绘制法画板框就回避了图形闭合不成功的种种问题。实际工作中，转换法和绘制法这两种方法常常结合使用。

**注意：**执行菜单命令【捕获至对象】的时候，对于比较复杂的结构图操作起来会比较卡。有些工程师会遇到勾选上“显示标记”也没有标记图形出现的情况，这时要确认选项菜单中“捕获半径”是不是设置得非常小，图 2-66 中的单位为 mm，这里值设置得越小，鼠标就要移动到越精确的位置标记才能出现。

图 2-66 “捕获半径”的设置

## 2.11 设置原点

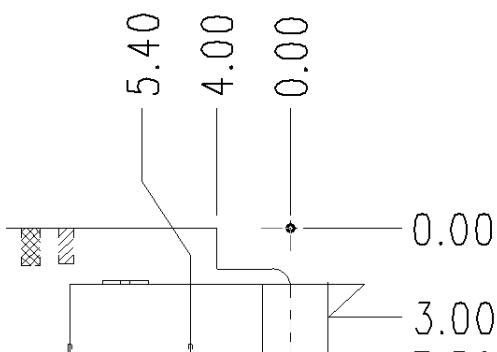

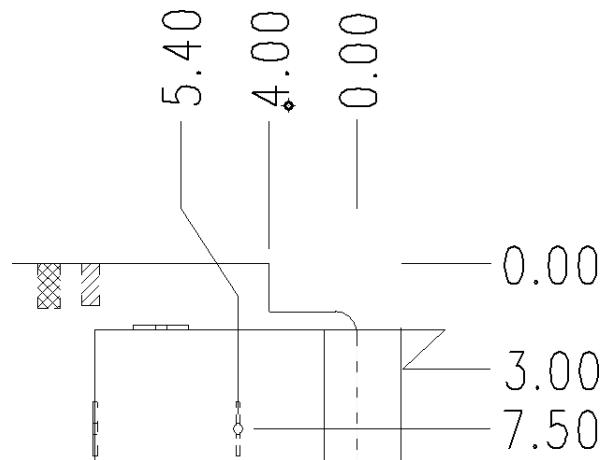

设置好原点能够让放置的固定器件有一个精确的坐标参照。上例中应设置结构图右上角的(0, 0)点为原点。这个结构图的(0, 0)点正好是两根线段相交的点，框选如图 2-67 所示的这两根线段。

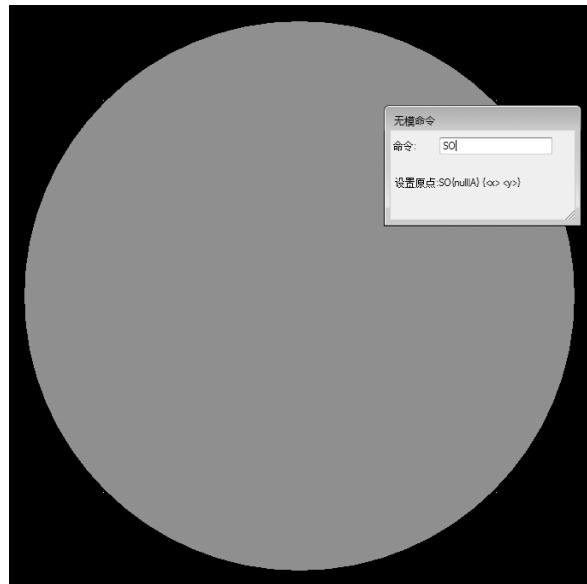

输入无模命令【SO】，原点就会自动设置在两根线段相交的点上，如图 2-68 所示。

图 2-67 选中两根相交的线段

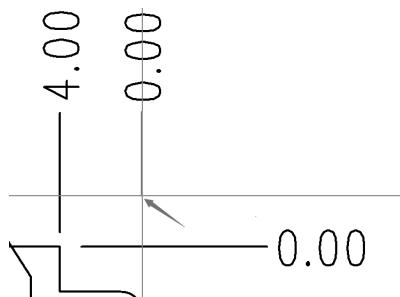

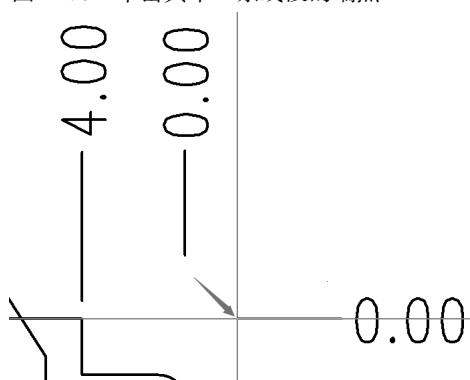

如图 2-69 所示, 结构图的 (0, 0) 位置没有相交的线该怎么办呢?

图 2-68 原点设置在两根线段相交的点上

图 2-69 (0, 0) 指示位置没有相交的线段

图 2-70 单击其中一条线段的端点

用鼠标单击其中一条线段的端点, 如图 2-70 中箭头所指的位置, 按下组合键【Ctrl + E】，向左移动鼠标, 线段会延长, 延长到适当位置单击鼠标左键放置。

用鼠标单击另一条线段的端点, 如图 2-71 中箭头所指的位置, 使用同样的方法延长另一根线段, 使它们相交。

同时框选这两根相交线段, 如图 2-72 所示, 输入无模命令【SO】设置原点即可。

图 2-71 单击另一条线段的端点

图 2-72 框选两根相交线段设置原点

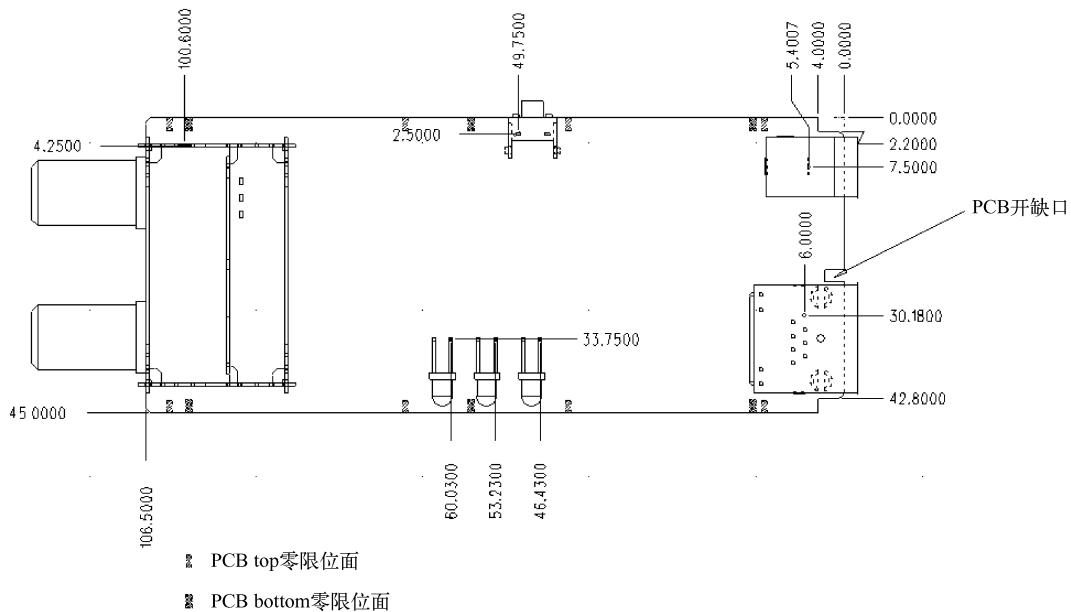

## 2.12 摆放结构器件

设置好原点后, 要先摆放有结构要求的元器件。

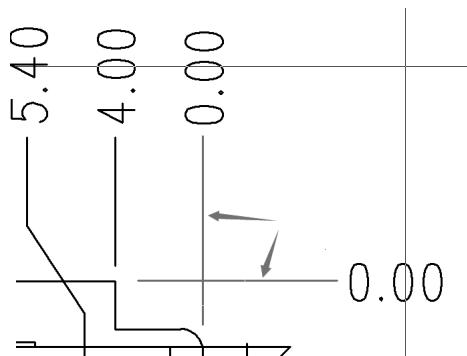

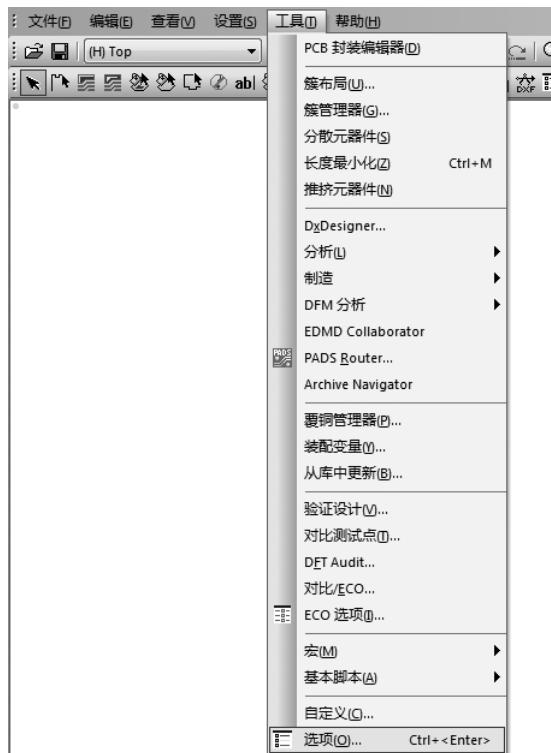

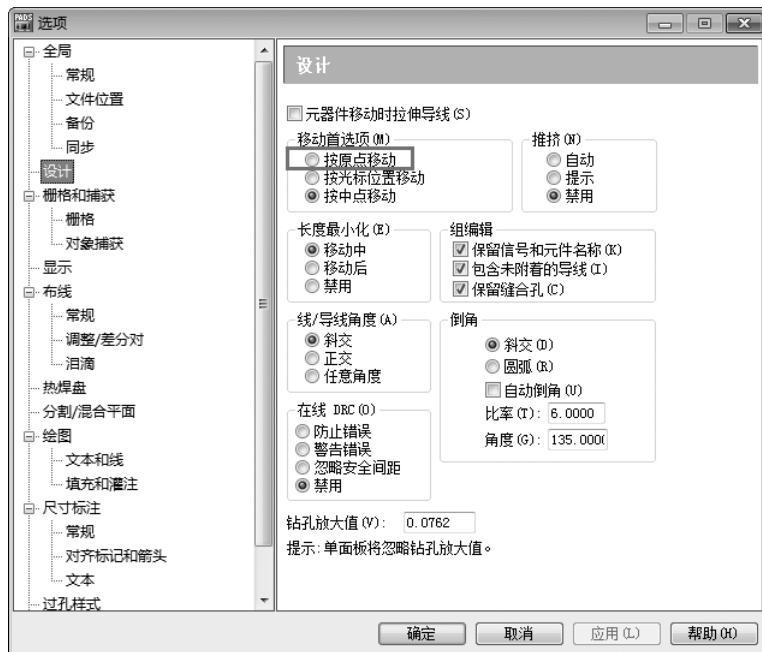

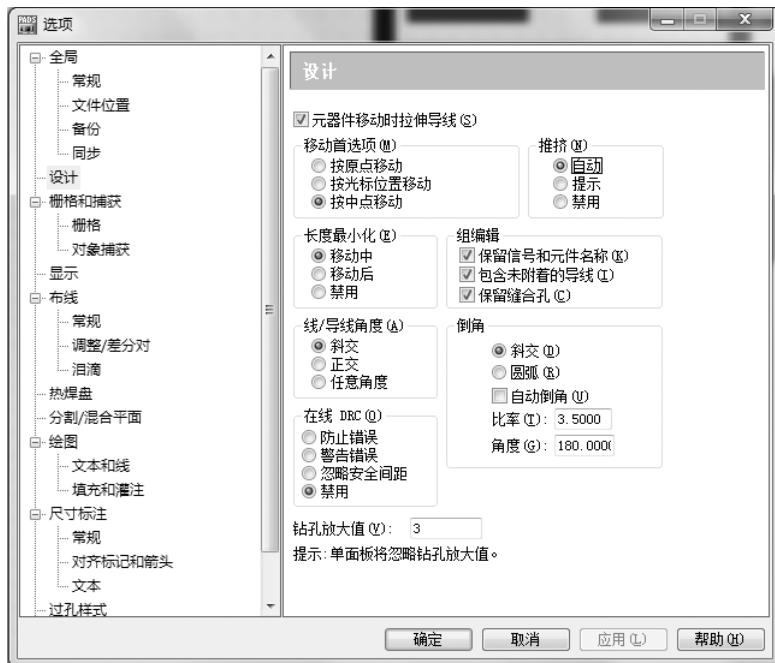

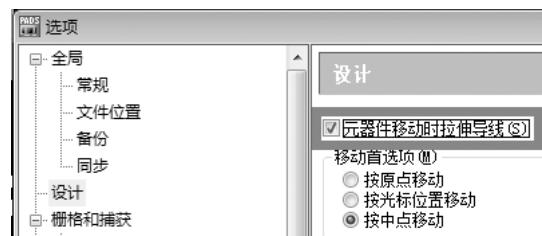

执行菜单命令【工具】 - 【选项】，在“设计”选项卡中将“移动首选项”改为“按原点移动”，单击【确定】按钮应用设置，如图 2-73 和图 2-74 所示。

图 2-73 执行菜单命令【工具】 - 【选项】

图 2-74 移动方式改为“按原点移动”

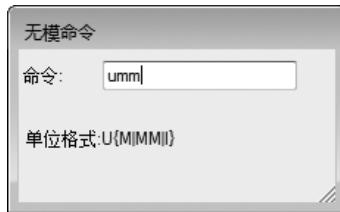

输入无模命令“umm”将设计单位设成毫米（结构图的坐标是按 mm 画的），如图 2-75 所示。

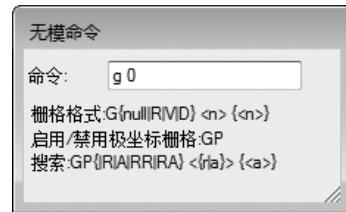

再输入无模命令“g0”将栅格设置成最小，如图 2-76 所示，以免移动元件时受栅格影响不能精确定位。

图 2-75 键入无模命令“umm”

图 2-76 键入无模命令“g0”

在空白处单击鼠标右键，执行菜单命令【选择元器件】，如图 2-77 所示。

图 2-77 执行菜单命令【选择元器件】

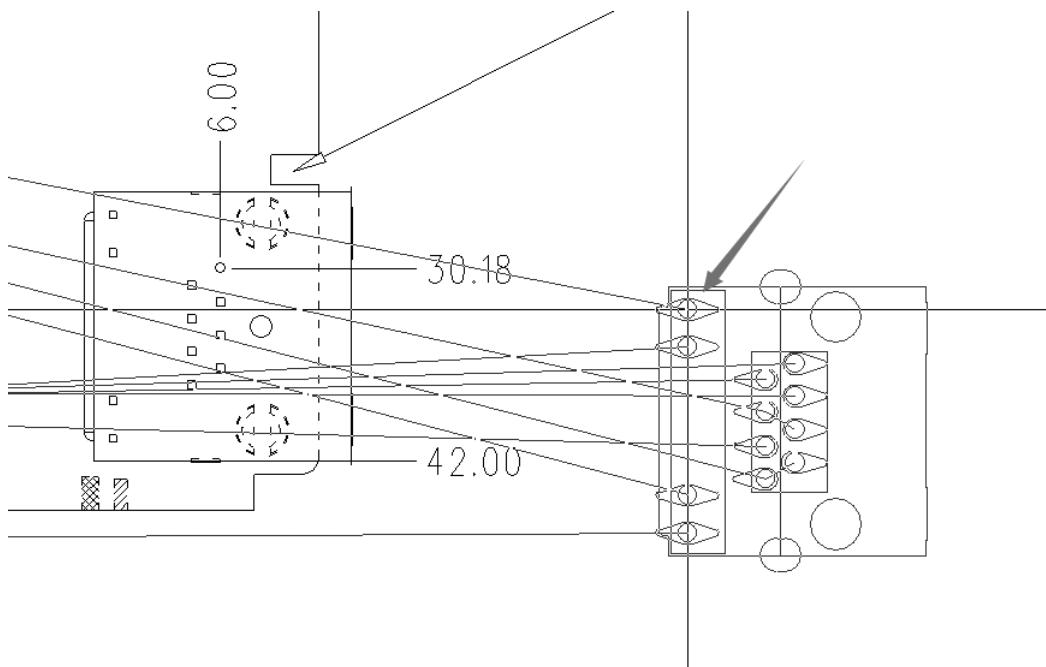

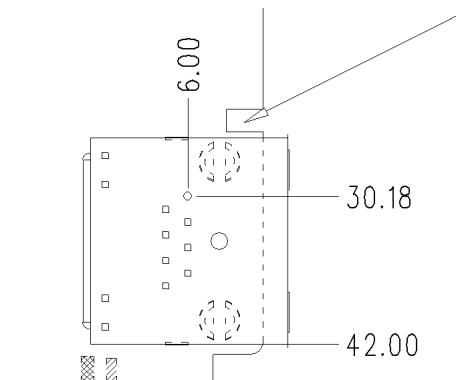

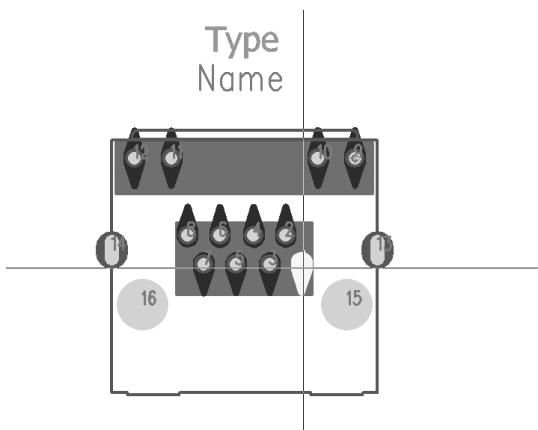

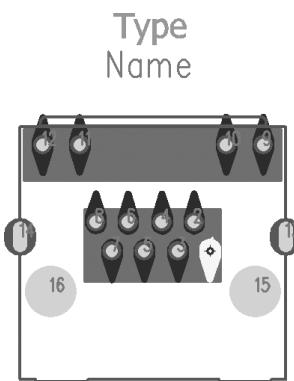

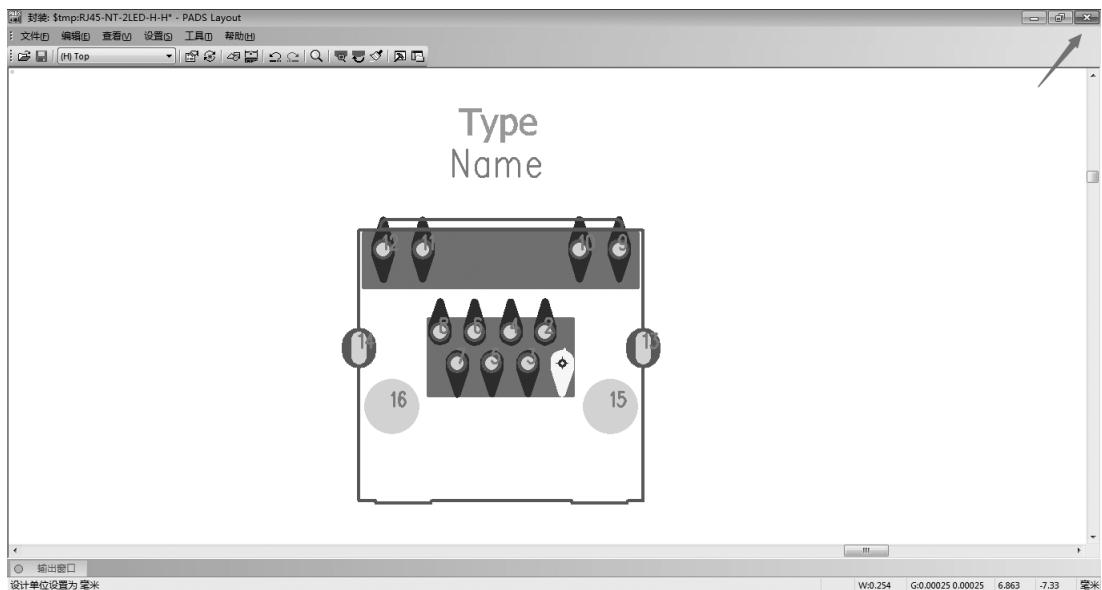

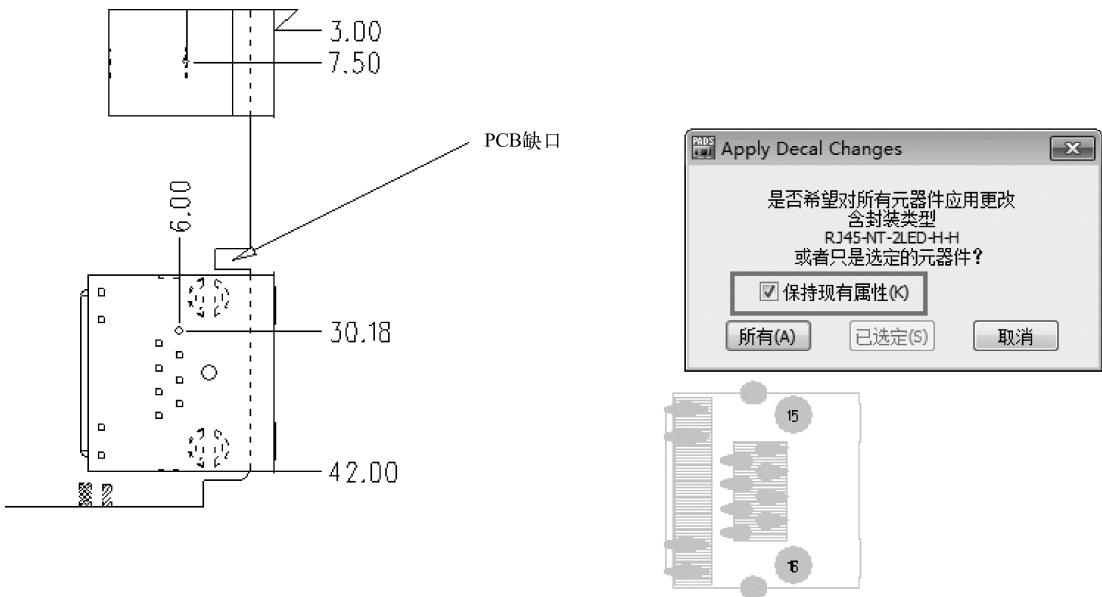

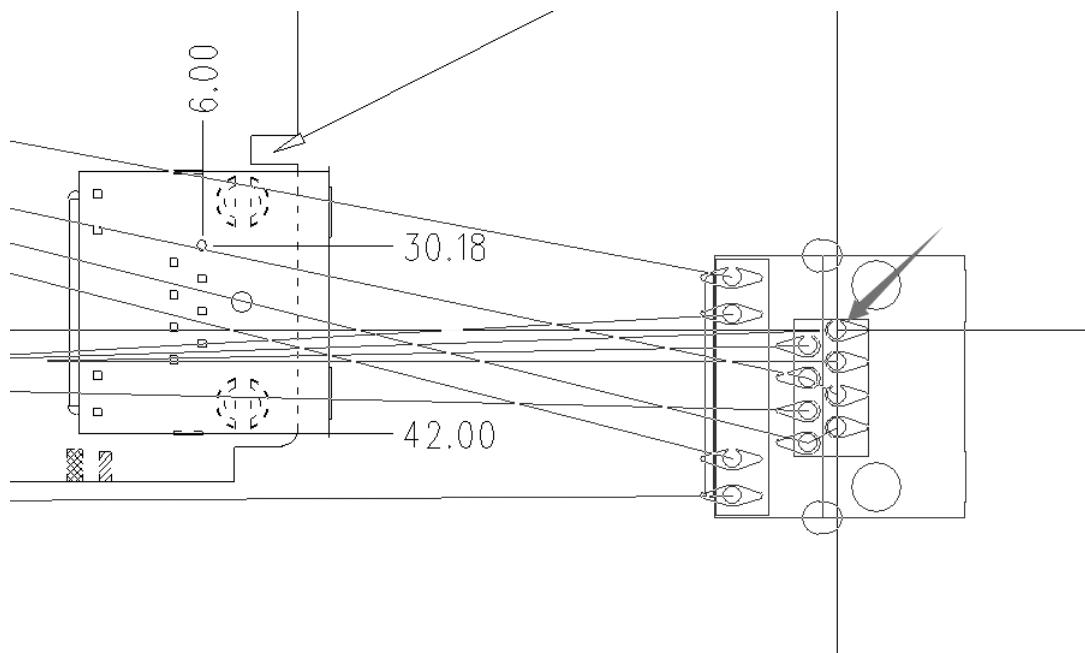

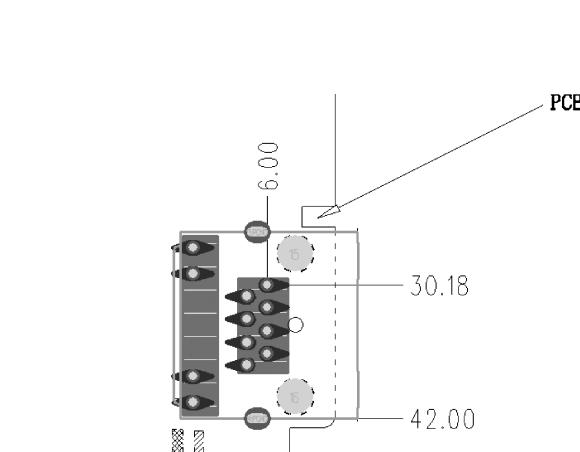

拖动要定位的元器件 RJ45 端口，如图 2-78 所示，这时候元器件会跟随它的原点位置附着在鼠标上，由图可知元器件的 9 号脚是元件的原点。

但我们看结构图上元件的原点应该定在 1 号脚，即图 2-79 中坐标指示的位置。

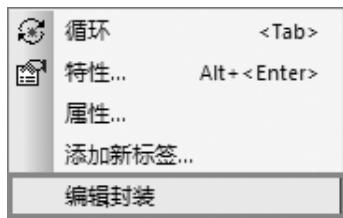

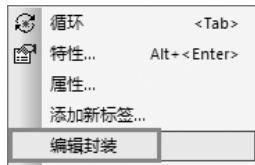

放弃移动器件，单击鼠标，右键执行菜单命令【编辑封装】进入 PCB 封装编辑器的界面，如图 2-80 所示。

选择元器件的第一引脚，输入无模命令“SO”将原点设定在此处，如图 2-81 和图 2-82 所示。

图 2-78 拖动需定位的元器件

图 2-79 结构图中 RJ45 的定位原点

设置完毕后，单击窗口右上方的关闭图标，退出编辑，如图 2-83 所示。

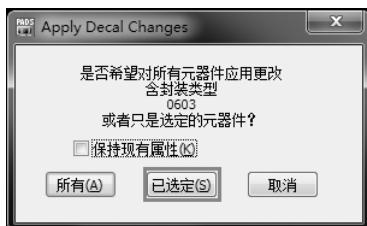

这时会跳回 PCB 设计界面，并弹出元器件应用更改的窗口，勾选“保持现有属性”，再单击【所有】按钮应用（如果整个 PCB 有许多这种器件，【已选定】按钮会处于激活的状态），如图 2-84 所示。

这时候我们再移动这个元器件，就会以 1 号引脚作为元器件移动的原点了，如图 2-85 所示。

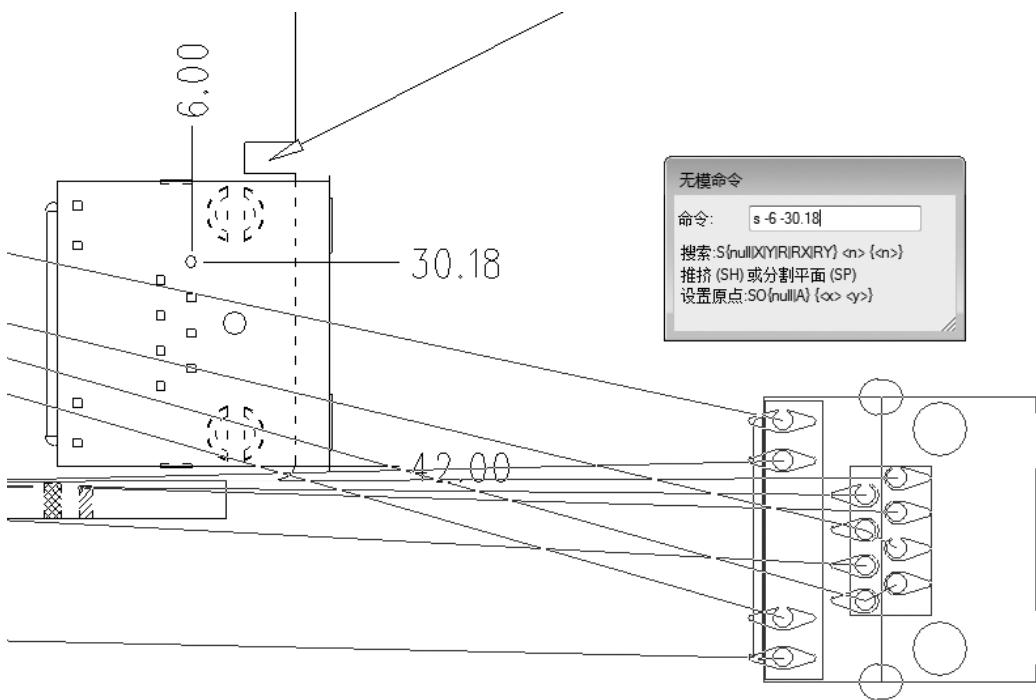

这时候根据坐标输入无模命令“s -6 -30.18”，如图 2-86 所示，按下键盘【Enter】键查找坐标位置，鼠标指针会移动至该点，单击鼠标左键放置器件即可，图 2-87 为放置后的元件。

图 2-80 进入 RJ45 PCB 封装的编辑窗口

图 2-81 选择 RJ45 的 1 号引脚

图 2-82 将 1 号引脚的位置设置成元器件原点

图 2-83 退出 PCB 封装编辑器界面

图 2-84 应用更改

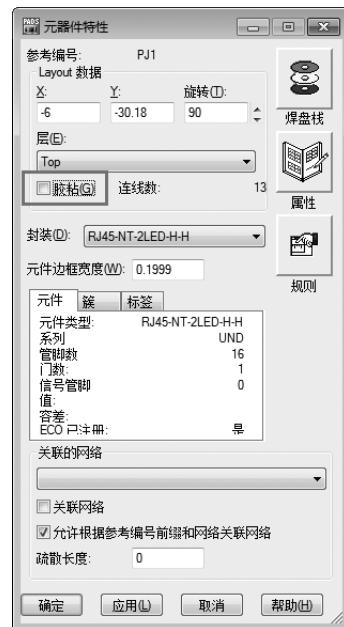

器件摆放好后，为了防止在设计中不小心更改它的位置，要对它进行胶粘的操作。

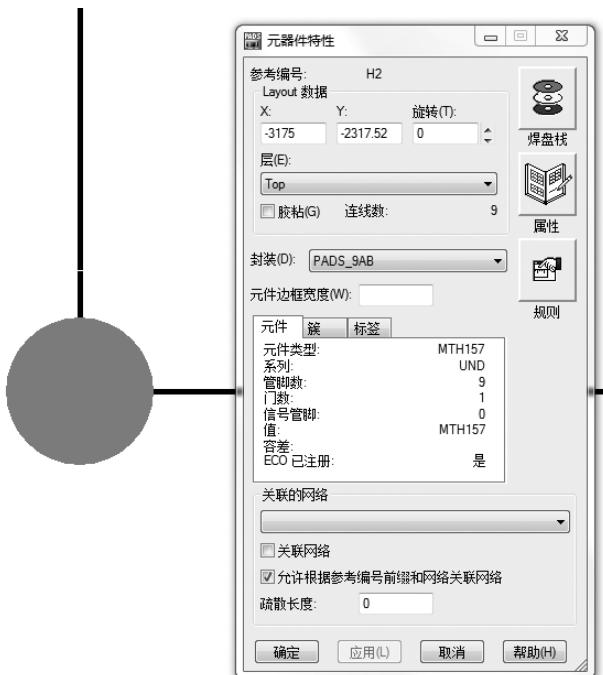

选择放置好的器件，单击鼠标右键，进入“元器件特性”对话框，勾选“胶粘”选项，如图 2-88 所示，并按【确定】按钮应用设置。用同样的方法定位并固定其他结构器件。

图 2-85 元器件“移动的原点”更改为所设引脚

图 2-86 移动中输入无模命令查找坐标

图 2-87 【Enter】键后元器件放置在相应位置

图 2-88 胶粘元器件

## 2.13 将结构图放置到其他层

将结构器件都摆放固定之后，我们要把结构图放到其他不使用的层，以免影响 PCB 绘制和文件输出。

单击鼠标右键，执行菜单命令【随意选择】，如图 2-89 所示。

图 2-89 菜单命令【随意选择】

框选整个图形，单击鼠标右键，执行菜单命令【合并】，如图 2-90 所示。

图 2-90 菜单命令【合并】

合并之后，单击鼠标右键，调出“绘图特性”，打开“层”下拉菜单，选择“Assembly Drawing Top”装配顶层（底层放置在 Assembly Drawing Bottom），单击【确定】按钮应用设置，如图 2-91 所示。

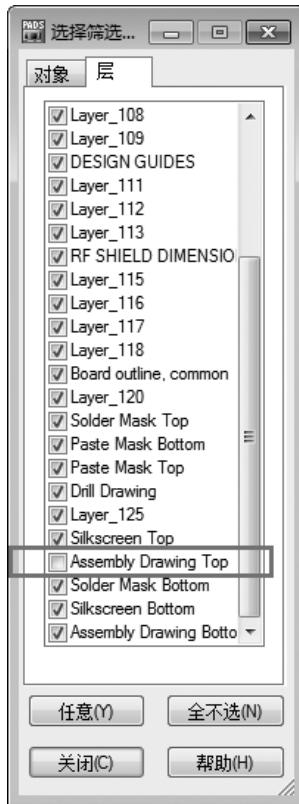

鼠标在空白区域单击鼠标右键，执行菜单命令【筛选条件】，如图 2-92 所示。

图 2-91 将图形放置到装配顶层

图 2-92 菜单命令【筛选条件】

跳出的窗口中选择“层”选项卡，将“Assembly Drawing Top”那层的勾选取消，如图 2-93 所示，这样结构图就不能轻易更改了。

图 2-93 取消勾选“Assembly Drawing Top”

## 2.14 覆铜时提示尝试减小平滑半径和覆铜边框宽度

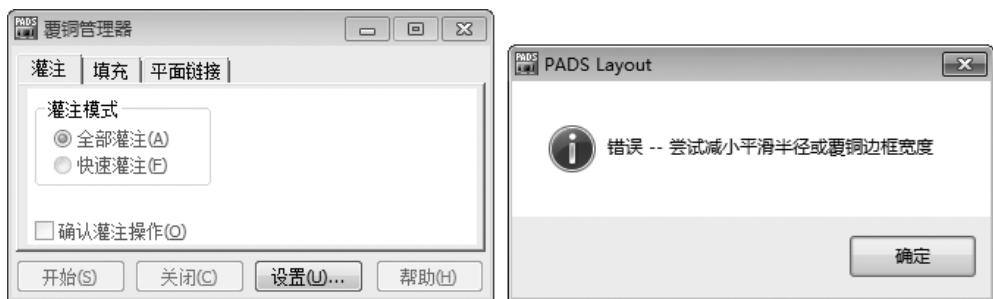

画完 PCB，最后覆铜时弹出错误，提示要减小平滑半径和覆铜边框的宽度，但是无论数值减到多小，覆铜时还是会报相同的错误，如图 2-94 所示。

图 2-94 覆铜灌注时要求减小平滑半径和覆铜边框的宽度的错误提示

这是由板框引起的错误。导入板框后图形虽然可以正常闭合并转换为板框，但覆铜时会报这个错误。解决办法是用 PADS 重新描画一个板框。

图 2-95 所示的例子就是出现这种问题的板框，这样弧度的图形描画起来比较麻烦，还是使用上面的绘制法来绘制。最后删除原板框，将绘制的图形转换成板框即可。

## 2.15 板框被选中却不能移动

有时框选板框后，使用移动命令却移动不了板框。框选板框时，鼠标要扫过整个板框这样框选，如果扫过的区域只是板框的一部分，整个板框虽然处于高亮的状态，看上去似乎已经选择上了，但是实现不了移动。

第3章 软件参数与规则设置

### 3.1 鼠标光标设置

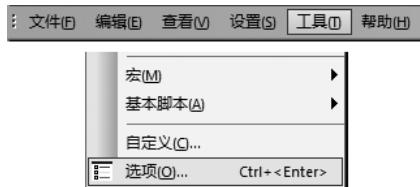

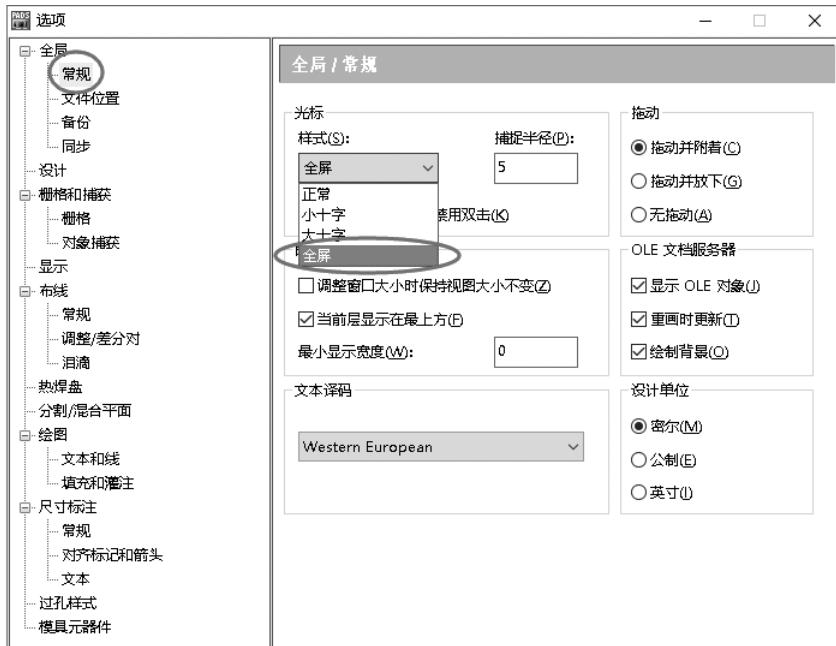

鼠标光标推荐使用全屏，在设计美观和效率方面有一定的提升。

执行菜单命令【工具】-【选项】，如图 3-1 所示。

图 3-1 进入软件参数设置

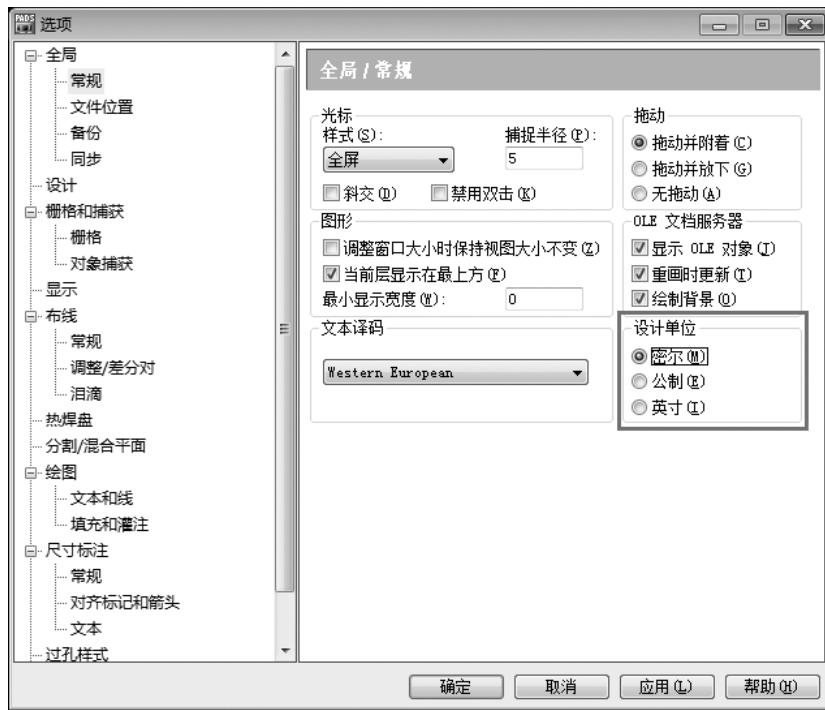

单击“全局”选项中的“常规”，在“光标的样式”标签中选择“全屏”，如图 3-2 所示。

图 3-2 更改光标样式

光标效果如图 3-3 所示。

图 3-3 光标效果

### 3.2 更改设计单位

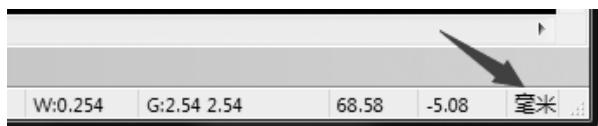

执行菜单命令【工具】-【选项】，单击“全局”选项中的“常规”，在设计单位标签中有3种设计单位选择：密尔、公制、英寸，如图3-4所示。

图 3-4 更改设计单位

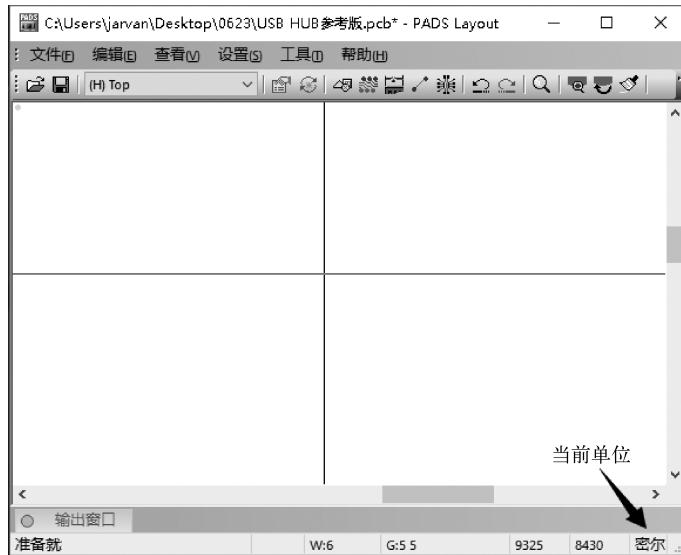

切换密尔的快捷键是 um，公制是 umm，输入后按【Enter】键切换单位。在 PADS Layout 软件的右下角处，有当前单位的显示，如图 3-5 所示。

图 3-5 当前单位显示

### 3.3 走线显示不正常

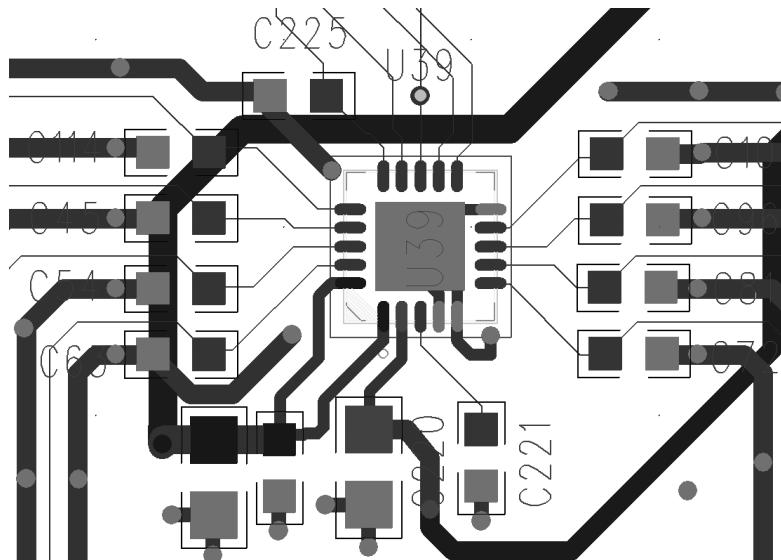

走线宽度设置的为 6mil，走出来变得极细，如图 3-6 所示。

图 3-6 走线显示不正常

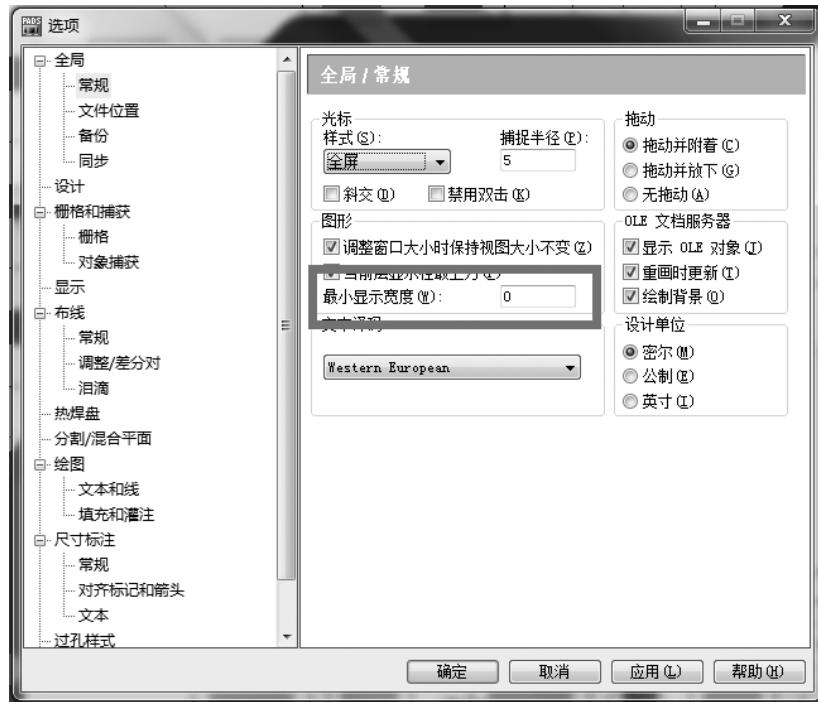

当最小显示宽度大于走线宽度时，走线将按极细的宽度显示。进入设置，将最小显示宽度修改为 0，如图 3-7 所示。

走线将能按正常宽度显示，如图 3-8 所示。

图 3-7 修改最小显示宽度

图 3-8 正常显示走线宽度

### 3.4 备份文件设置

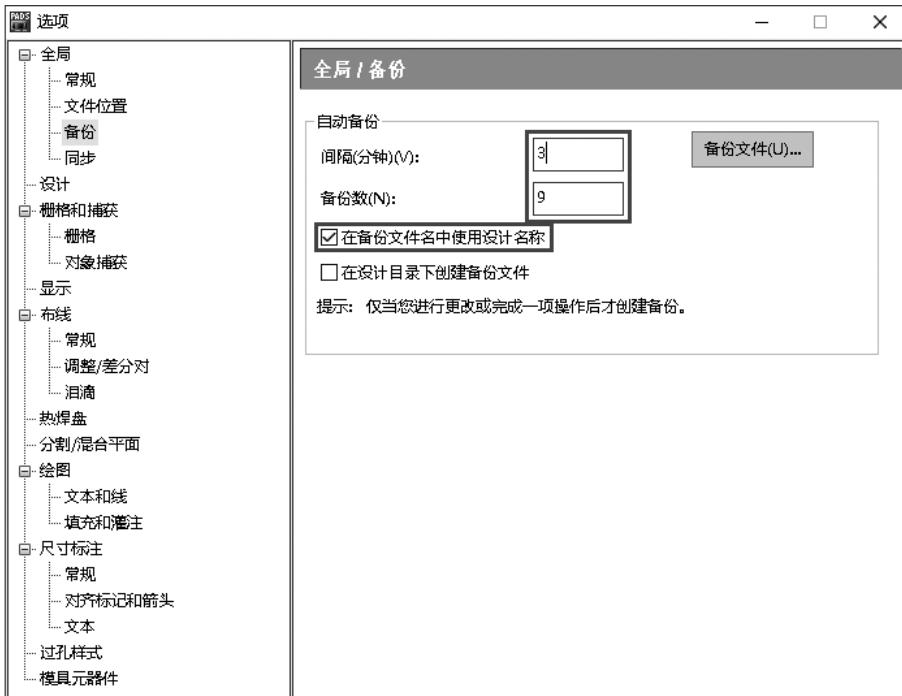

执行菜单命令【工具】-【选项】，选择“全局”选项中的“备份”，推荐设置如图 3-9 所示。

图 3-9 备份文件推荐设置

系统或软件崩溃，通过查找备份文件能找到接近最新设计的文件，减少从新设计的工作量。不出异常，无须使用备份文件，因此不建议勾选“在设计目录下创建备份文件”，会生成很多备份文件在设计目录下。如果勾选“在设计目录下创建备份文件”，效果如图 3-10 所示。

| 名称                                           | 修改日期           | 类型                | 大小       |

|----------------------------------------------|----------------|-------------------|----------|

| LY20-Y7242-all.pcb                           | 2016/5/7 21:52 | PADS Layout De... | 4,248 KB |

| LY20-Y7242-all_Layout -16_05_07_19_43_01.pcb | 2016/5/7 21:43 | PADS Layout De... | 4,248 KB |

| LY20-Y7242-all_Layout -16_05_07_20_43_01.pcb | 2016/5/7 21:43 | PADS Layout De... | 4,248 KB |

| LY20-Y7242-all_Layout -16_05_07_21_43_01.pcb | 2016/5/7 21:43 | PADS Layout De... | 4,248 KB |

| LY20-Y7242-all_Layout -16_05_07_22_43_01.pcb | 2016/5/7 21:43 | PADS Layout De... | 4,248 KB |

| LY20-Y7242-all_Layout.pcb                    | 2016/5/7 21:43 | PADS Layout De... | 4,248 KB |

图 3-10 勾选“在设计目录下创建备份文件”的效果

### 3.5 绘图或走线时改变线的角度

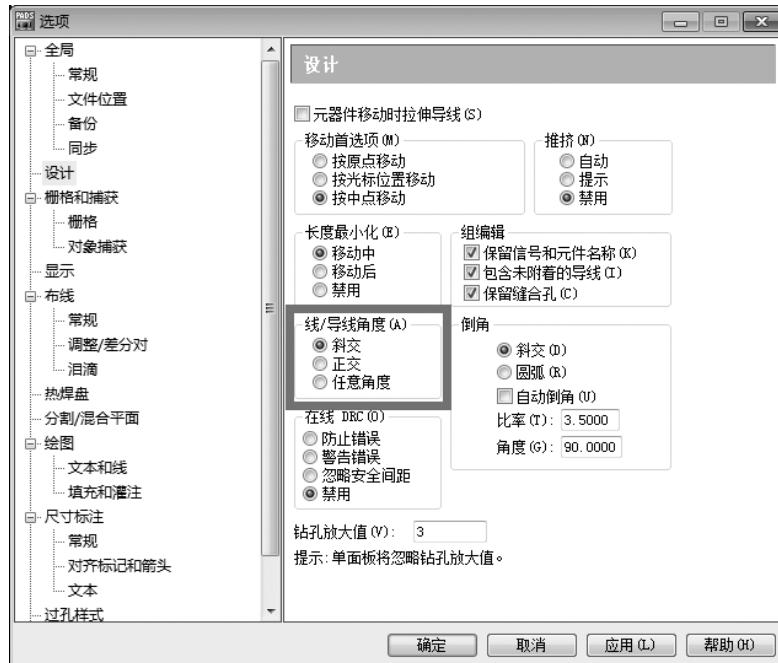

执行菜单命令【工具】-【选项】，选择“全局选项”中的“设计”，在“线/导线角度”中可以对线/导线角度进行改变。也可以输入无模命令“AA”（任意角度），“AD”（斜交）、“正交”（AO）来切换布线角度，如图 3-11 所示。

图 3-11 更改线/导线角度

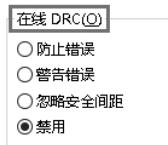

### 3.6 DRC 设置

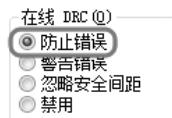

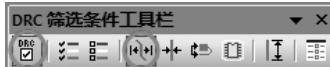

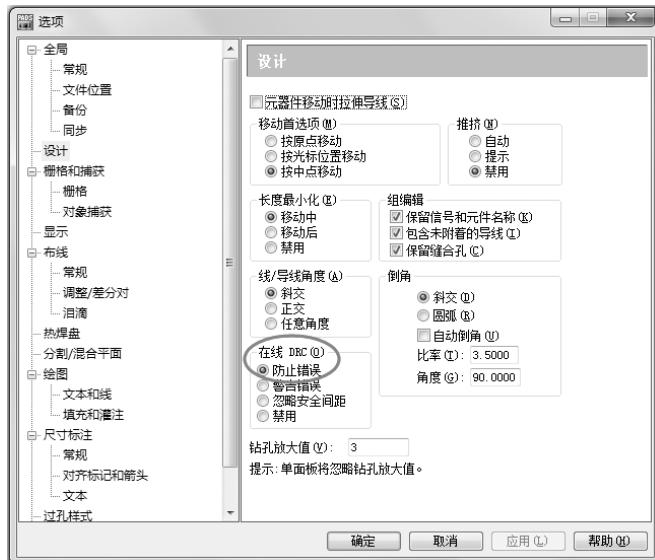

在 PADS layout 上, 推荐禁用 DRC:

- (1) 如果选择“防止错误”, 则不允许瞬间性的错误发生。

- (2) 如果选择“警告错误”, 则有错误时一直弹窗, 也不允许瞬间性的错误发生。

执行菜单命令【工具】-【选项】, 选择“全局”选项中的“设计”, 可以对在线 DRC 根据实际需要进行设置, 如图 3-12 所示。

图 3-12 在线 DRC 设置

### 3.7 长度最小化

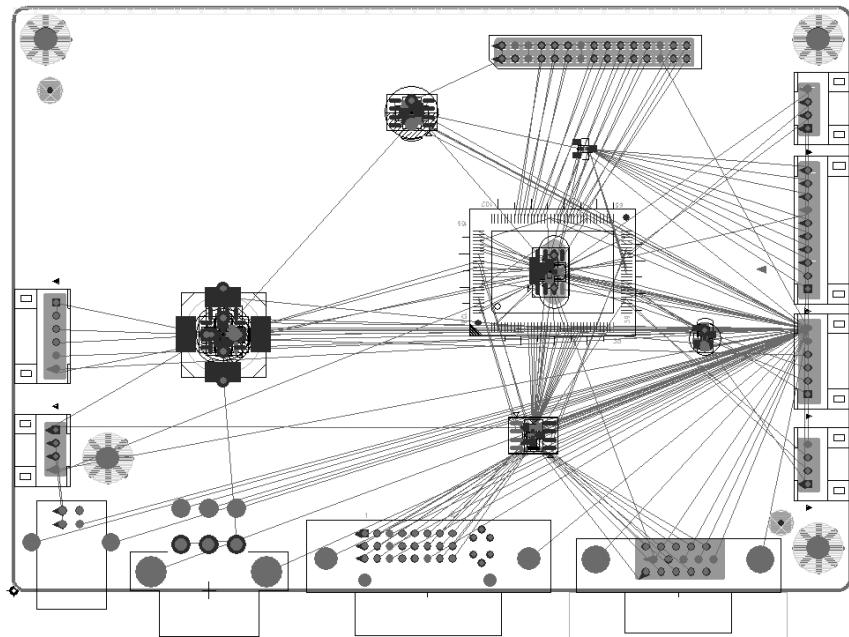

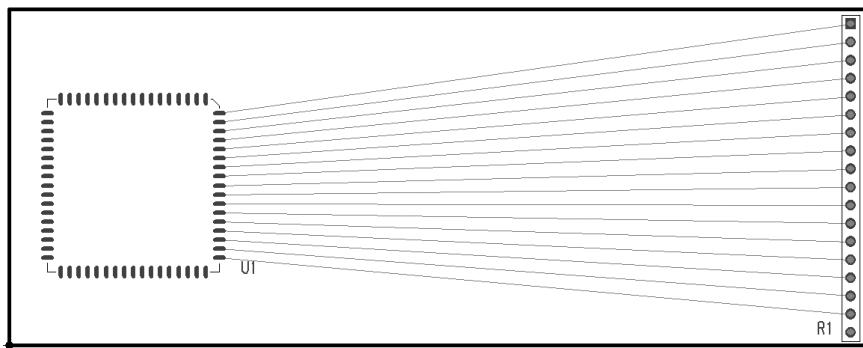

所有的飞线都集中某一个点上, 如图 3-13 所示。

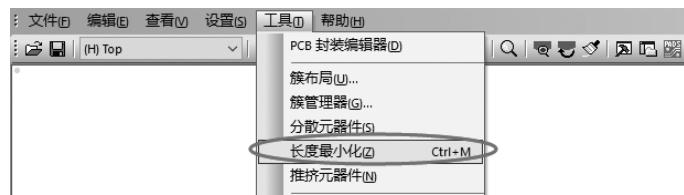

执行菜单命令【工具】-【长度最小化】，使用飞线最小化功能，如图 3-14 所示。

如果还没有反应, 执行菜单命令【设置】-【设计规则】-【默认】-【布线】，需要将“拓扑类型”改为最小化，如图 3-15 所示，再次进行长度最小化操作。

图 3-13 飞线集中在一个点上

图 3-14 长度最小化

图 3-15 更改拓扑类型

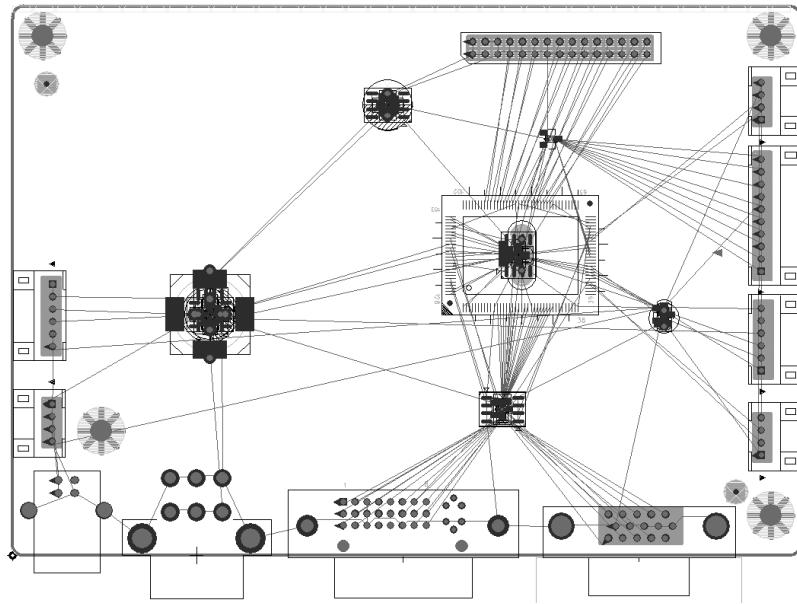

飞线最小化后的效果如图 3-16 所示。

图 3-16 飞线最小化效果

### 3.8 棚格设置

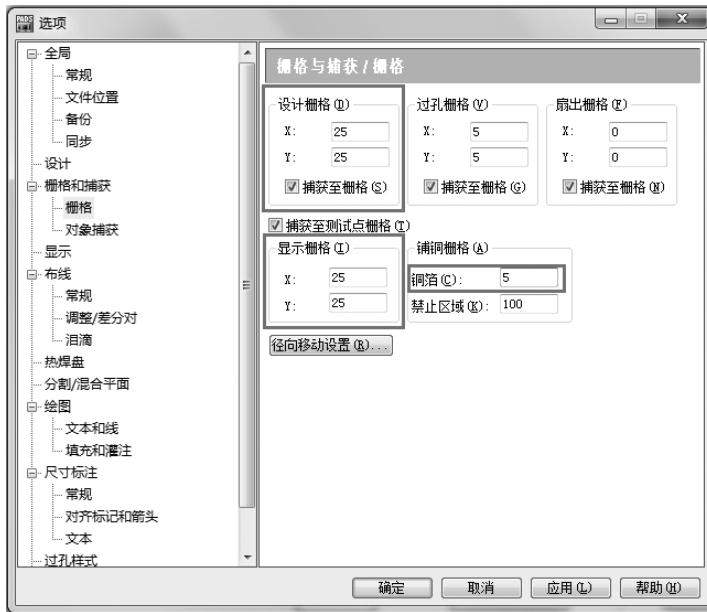

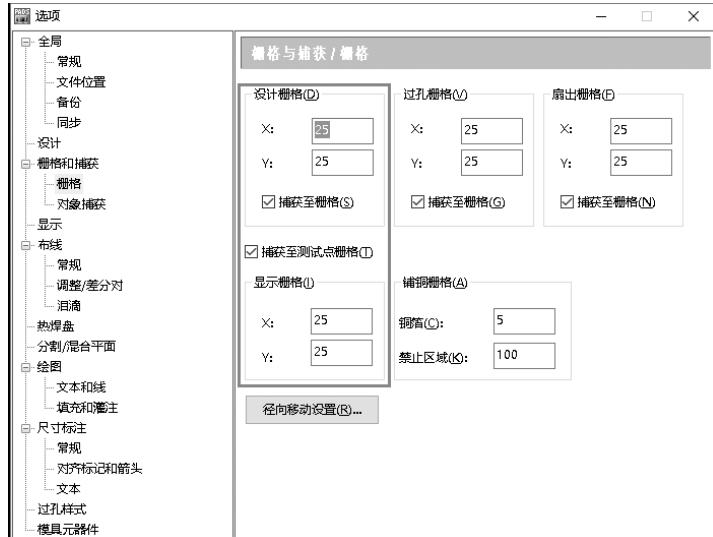

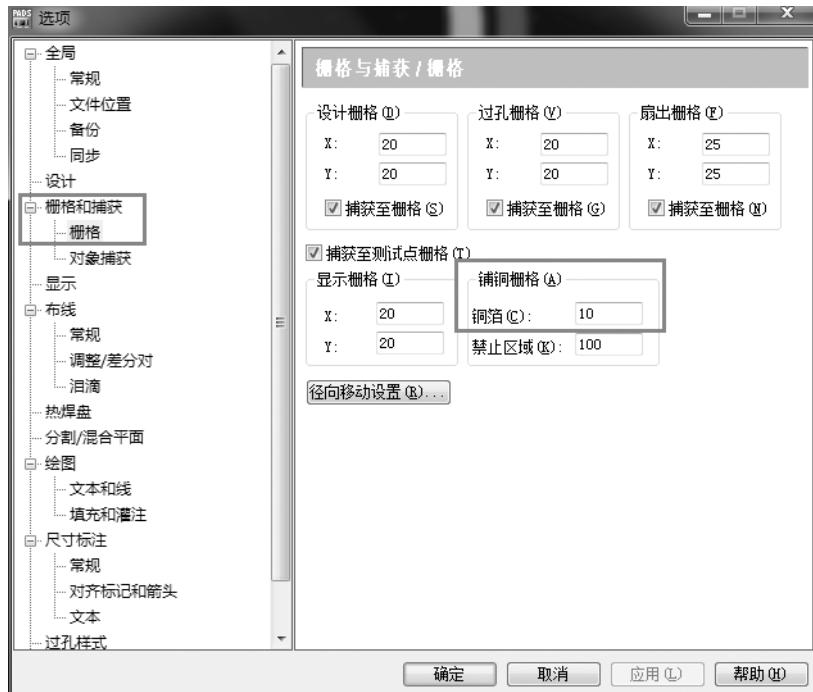

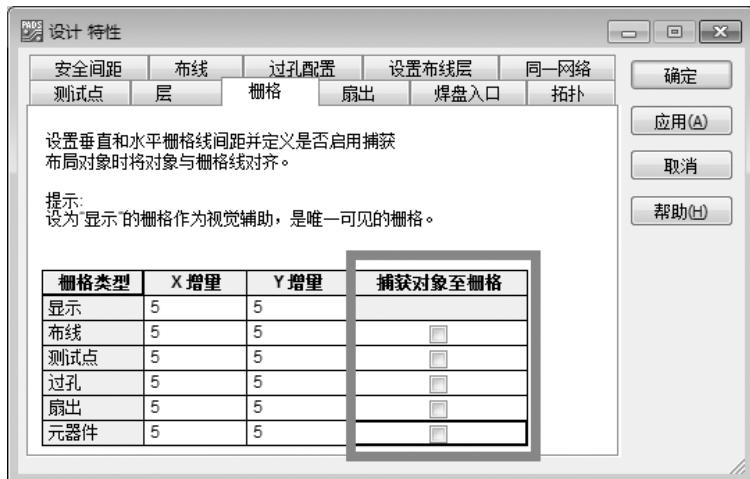

执行菜单命令【工具】-【选项】，选择“栅格与捕获”选项中的“栅格”，布局时推荐栅格的设置如图 3-17 所示。

图 3-17 布局时推荐栅格的设置

- (1) 设计栅格：移动时递增递减的距离。

- (2) 显示栅格：所显示栅格点与相邻点间的距离。

- 铜箔栅格：默认设置与线宽一样的宽度。

## 3.9 对象捕获

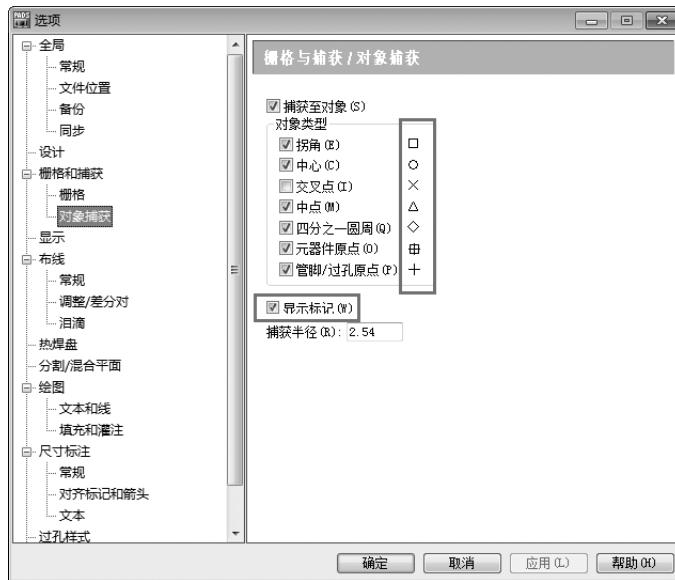

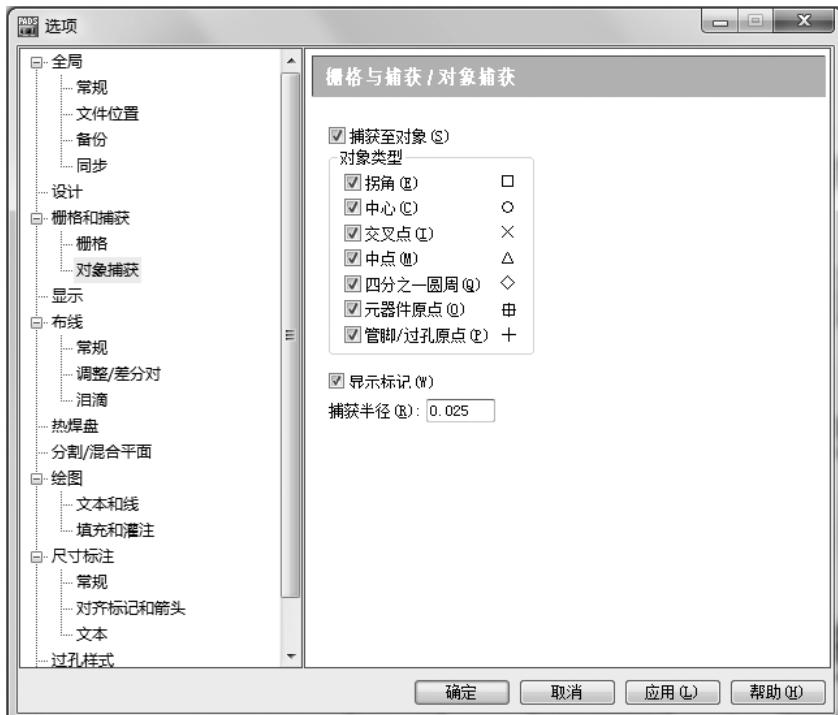

执行菜单命令【工具】-【选项】，选择“栅格与捕获”选项中的“对象捕获”，勾选“捕获至对象”，选定好捕捉对象，在结构定位或设定原点等使用起来能提高效率，如图 3-18 所示。

图 3-18 捕获至对象

## 3.10 添加泪滴

添加泪滴有利于加固焊盘，焊盘多次焊接时减少脱落的几率。

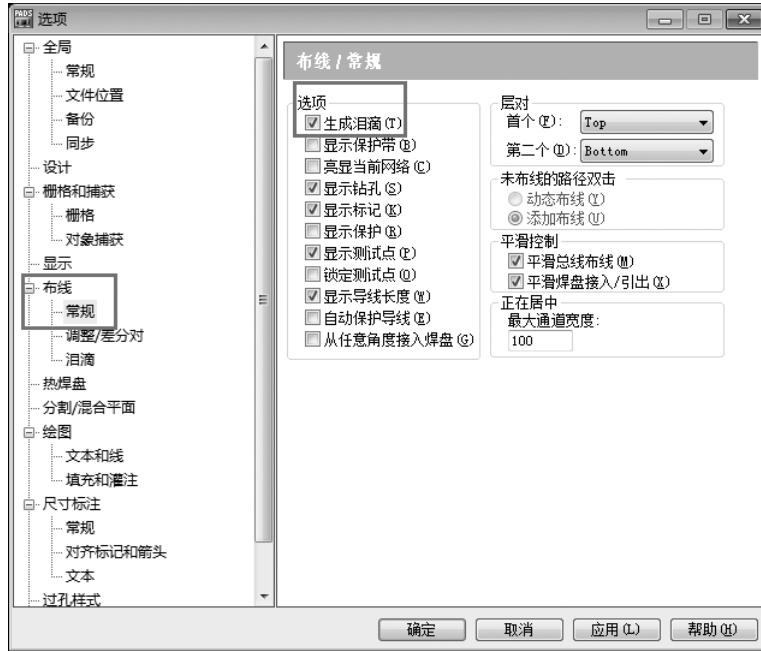

执行菜单命令【工具】-【选项】，选择“布线”选项中的“常规”，勾选“生成泪滴”，如图 3-19 所示。

在“布线”的“泪滴”选项中可选择泪滴的形状或自定义形状，如图 3-20 所示。

图 3-19 生成泪滴

图 3-20 自定义泪滴形状

### 3.11 转化为空心过孔

过孔没有孔径，如图 3-21 所示。

图 3-21 过孔没有孔径

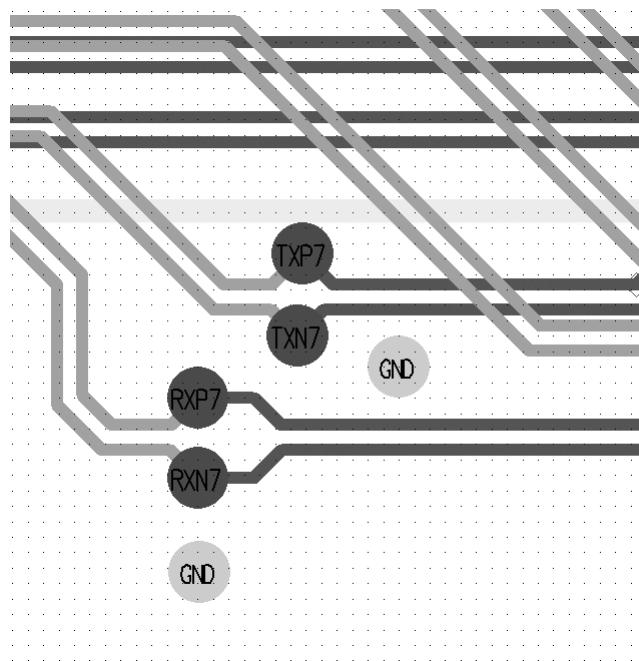

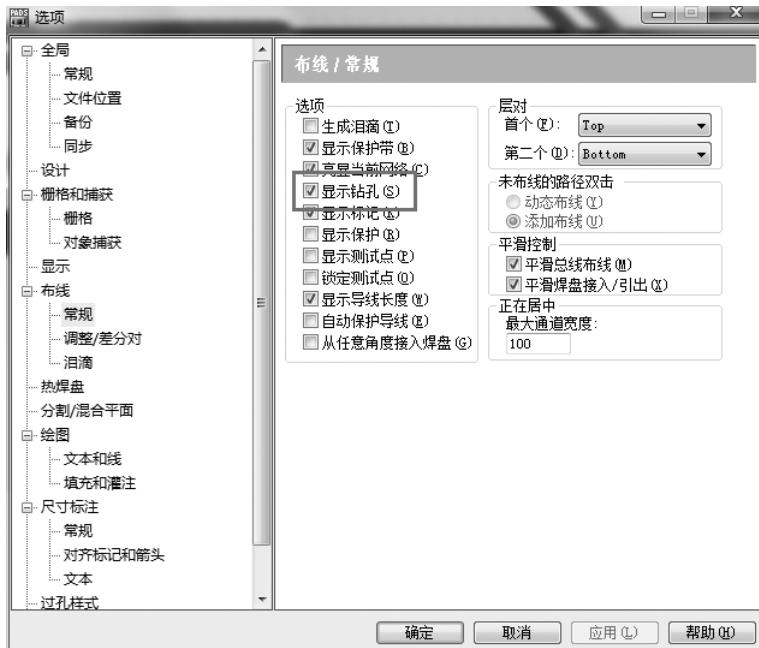

在“布线/常规”设置中勾选“显示钻孔”，如图 3-22 所示。

图 3-22 勾选显示钻孔

实心过孔将以空心过孔显示，如图 3-23 所示。

图 3-23 空心过孔显示

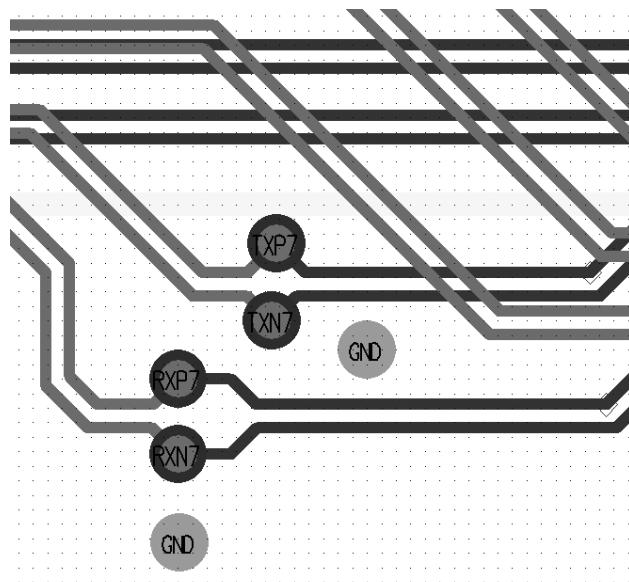

### 3.12 显示保护的导线

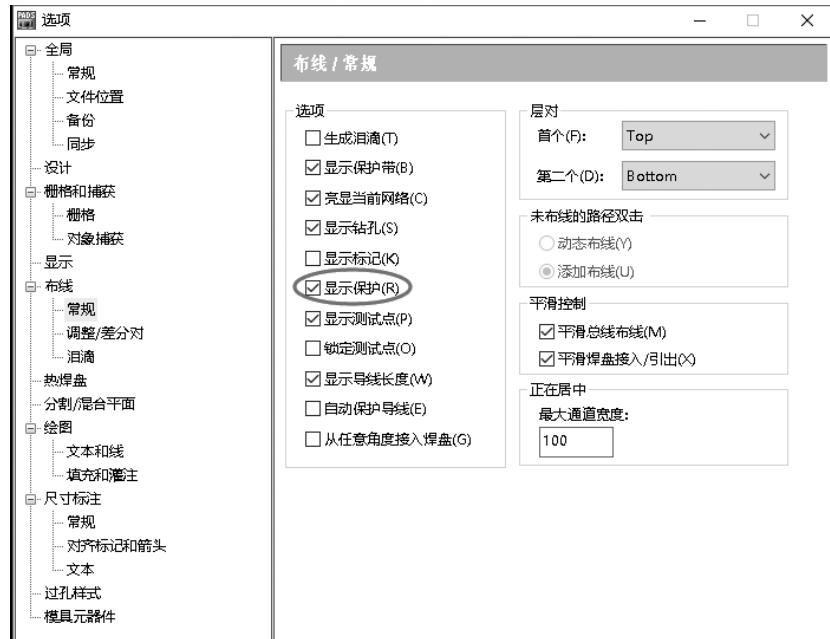

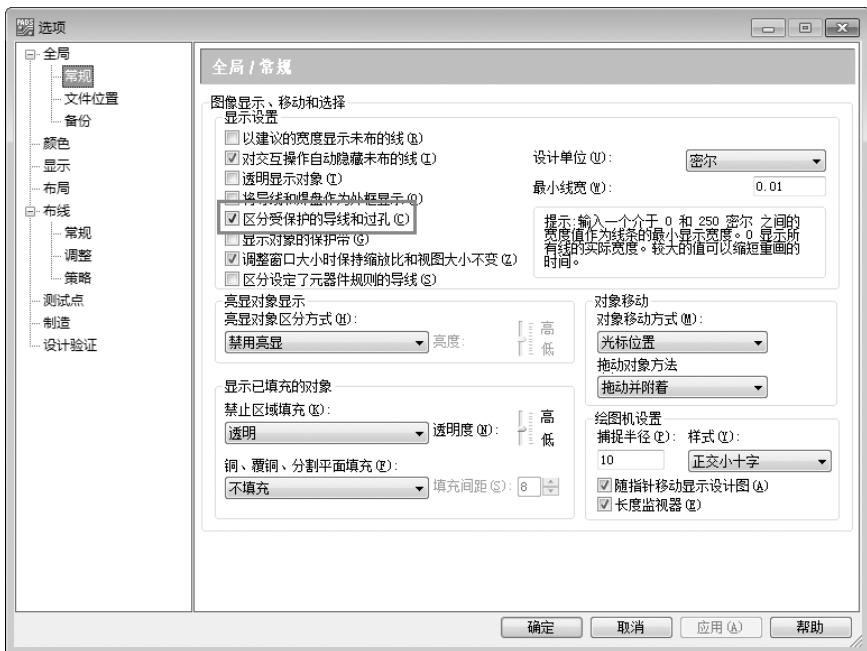

执行菜单命令【工具】-【选项】，选择“布线”选项中的“常规”，勾选“显示保护”，如图 3-24 所示。

图 3-24 勾选“显示保护”

被保护的导线变成透明的，以此区分保护和未保护，如图 3-25 所示。

图 3-25 保护和未保护导线的区别

### 3.13 热焊盘中正交，斜交，过孔覆盖的区别

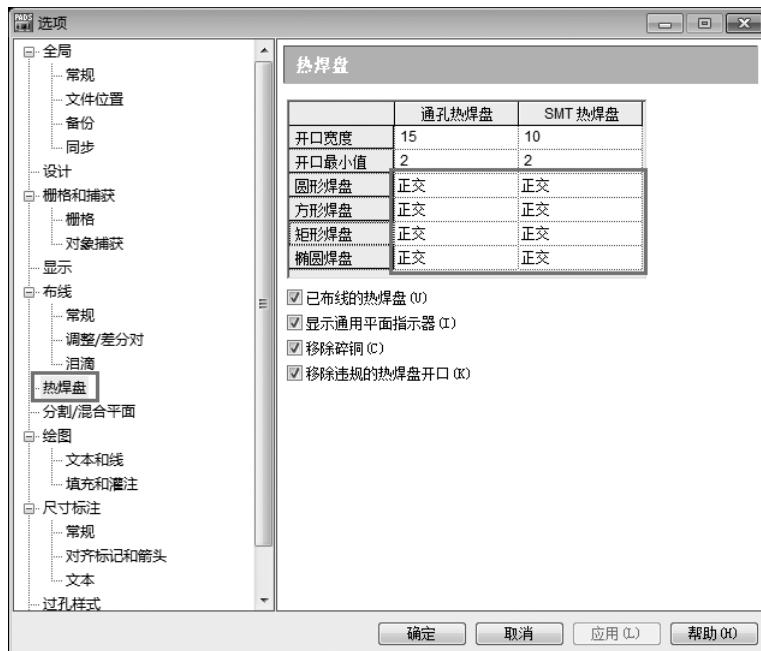

针对电源、地和一些特殊要求的网络经常需要敷铜处理，热焊盘连接的选择在生产加工和返修上显得尤为重要。

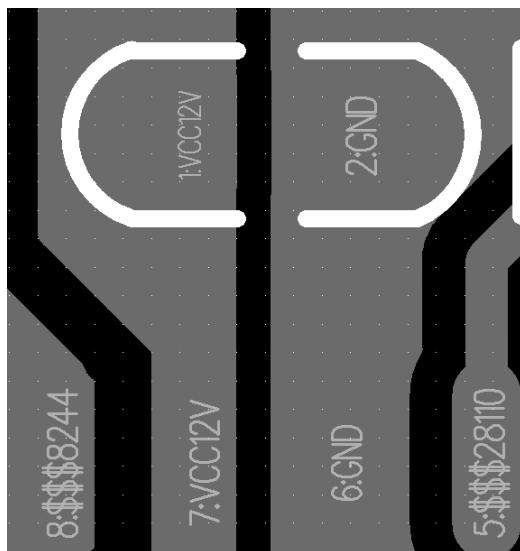

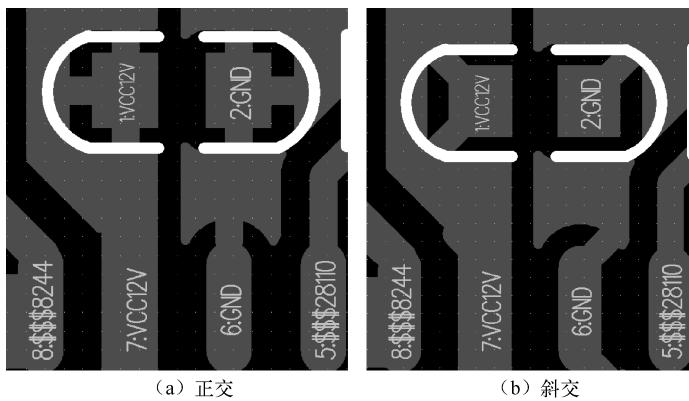

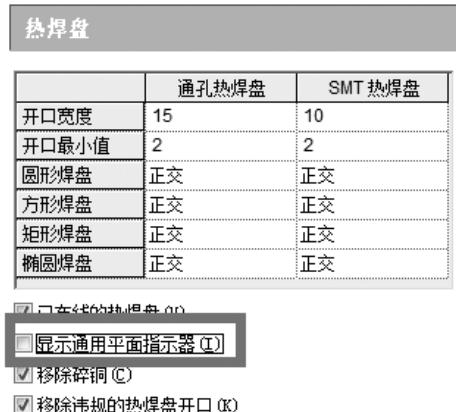

执行菜单命令【工具】-【选项】，选择“布线”选项中的“热焊盘”，通孔热焊盘/SMT 热焊盘推挤使用正交，如图 3-26 所示。

图 3-26 热焊盘推挤设置

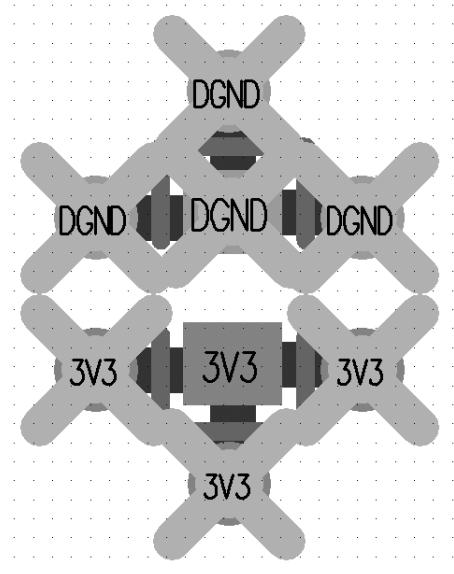

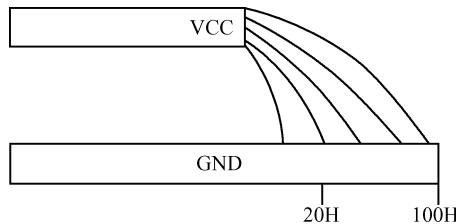

敷铜时连接得要尽可能多，但不要使用全连接。全连接焊接时会因过分散热而导致虚焊和不容易拆卸，过孔全覆盖如图 3-27 所示。

图 3-27 过孔全覆盖

从图 3-28 中可以看出，正交连接的铜皮更多，推荐花焊盘都使用正交。

图 3-28 正交和斜交的区别

### 3.14 隐藏过孔 X 的图像

PCB 板的过孔处会出现很多“X”图像，如图 3-29 所示。

出现这种现象是因为使用了混合/分割平面，取消勾选“显示通用平面指示器”，如图 3-30 所示。

图 3-29 有过孔 X 的图像

图 3-30 取消勾选“显示通用平面指示器”

取消后的效果如图 3-31 所示。

图 3-31 取消后效果

### 3.15 移除碎铜

碎铜是 PCB 敷铜时由于有空白面积生成的孤立铜箔，并不与板内的网络相连，在设计中应避免碎铜的出现，碎铜如图 3-32 所示。

图 3-32 碎铜

执行菜单命令【工具】-【选项】，选择“布线”选项中的“热焊盘”，勾选“移除碎铜”，如图 3-33 所示。

- 已布线的热焊盘 (U)

- 显示通用平面指示器 (I)

- 移除碎铜 (C)

- 移除违规的热焊盘开口 (O)

图 3-33 勾选“移除碎铜”

勾选“移除碎铜”后的效果如图 3-34 所示。

图 3-34 勾选“移除碎铜”后的效果

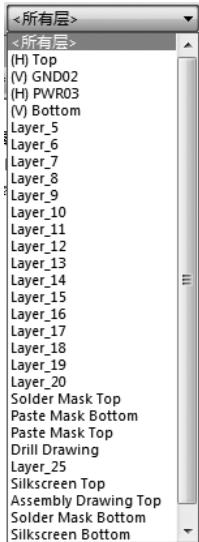

### 3.16 PADS 各层的用途和作用

PADS 各层如图 3-35 所示。

图 3-35 PADS 各层

PADS 各层的定义和作用如图 3-36 所示。

| 层                       | 层定义   | 作用               |

|-------------------------|-------|------------------|

| TOP                     | 顶层电气层 | 放置元器件和走线         |

| ...                     | 内层电气层 | 走线               |

| BOTTOM                  | 底层电气层 | 放置元器件和走线         |

| Silkscreen Top          | 顶层丝印层 | PCB表面印刷字符、图案、标识等 |

| Silkscreen Bottom       | 底层丝印层 |                  |

| Solder Mask Top         | 顶层阻焊层 | 没有绿油覆盖，露铜        |

| Solder Mask Bottom      | 底层阻焊层 |                  |

| Paste Mask Top          | 顶层助焊层 | 制作钢网             |

| Paste Mask Bottom       | 底层助焊层 |                  |

| Assembly Drawing Top    | 顶层装配图 | 装配文件             |

| Assembly Drawing Bottom | 底层装配图 |                  |

| Drill Drawing           | 钻孔图   | PCB外形处理          |

| Layer-xxx ~ Layer-xxx   | 非电气层  | 用作标识作用，不用于走线     |

图 3-36 PADS 各层的定义和作用

### 3.17 Layer25 层的作用

Layer25 层是插装的器件才有的，只是在出负片的时候才有用，一般只有当电源层定义为 CAM Plane 的时候 Gerber 文件才会出负片（分割/混合层输出是正片），如果不加这一层，在出负片的时候这一层的引脚容易短路。

PADS 中对电源层和地层的选择有 3 种选择，无平面、CAM 平面和分割/混合平面。分割/混合平面主要用于多个电源或地共用一个层的情况，但只有一个电源和地时也可以用。它的主要优点是输出时的图和光绘的一致，便于检查。

CAM Plane 用于单个的电源或地，这种方式是负片输出，要注意输出时需加上第 25 层。

第 25 层包含了电源和地的信息，主要指电层的焊盘要比正常的焊盘大 20mil 左右的安全距离，保证金属化过孔之后不会有信号与电源和地平面相连。这就需要在创建封装时焊盘上添加 Layer25 层的信息。而我们自己建库时往往会忽略这个问题。

Layer25 层的替代设置：在 PADS 的焊盘设置中，有一个 AntiPad 的设置，选择这一项（选择焊盘类型即可），其焊盘的初始设置值即为普通焊盘 +24mil 或 0.6mm。

不管是用 Layer25 还是 Antipad，其最终的目标有两个：一是上面提到的金属化过孔时防止短路；二是减小过孔的感生电容电感。

另外，不建议使用负片进行设计。

### 3.18 无平面、CAM 平面和分割/混合平面的区别

(1) 无平面：一个新设计的文件的层设置默认为无平面，无平面可以先绘制覆铜框，然后再给其分配任意网络，有较大的灵活性。

(2) CAM 平面：不建议使用。

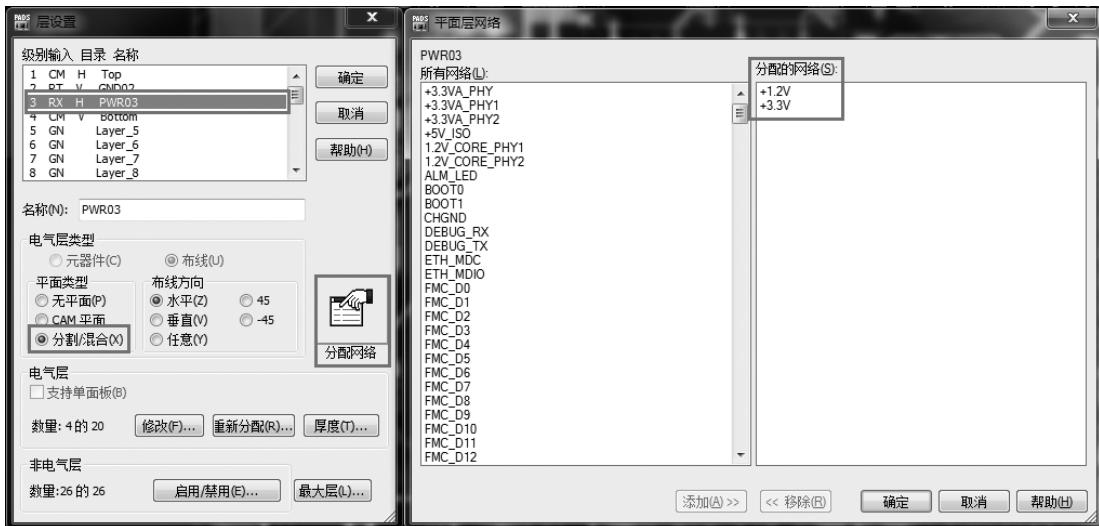

(3) 分割/混合平面：需要先定义这个层的网络，如图 3-37 所示。

图 3-37 定义分割/混合平面网络

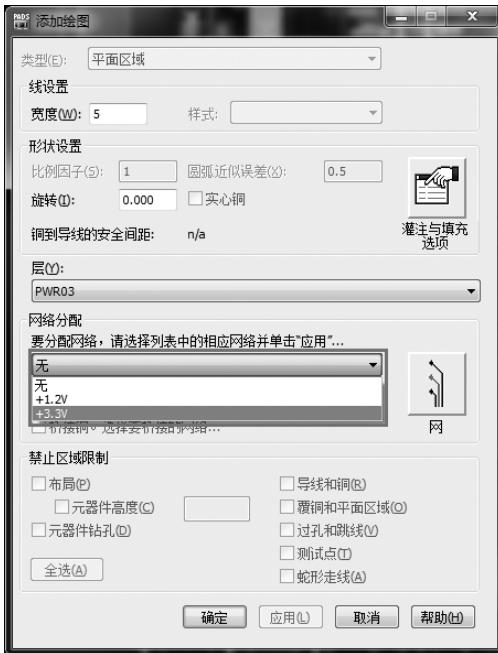

用平面区域图标 绘制，绘制完成后，在弹出的对话框的“网络分配”标签中选择下拉菜单中选择网络（仅限层定义里面已经分配的网络），如图 3-38 所示。

在覆铜管理器上无平面（见图 3-39）和分割混合平面（见图 3-40）使用着不同的灌注方法。

图 3-38 分配分割/混合平面网络

图 3-39 无平面灌注

图 3-40 分割/混合平面链接

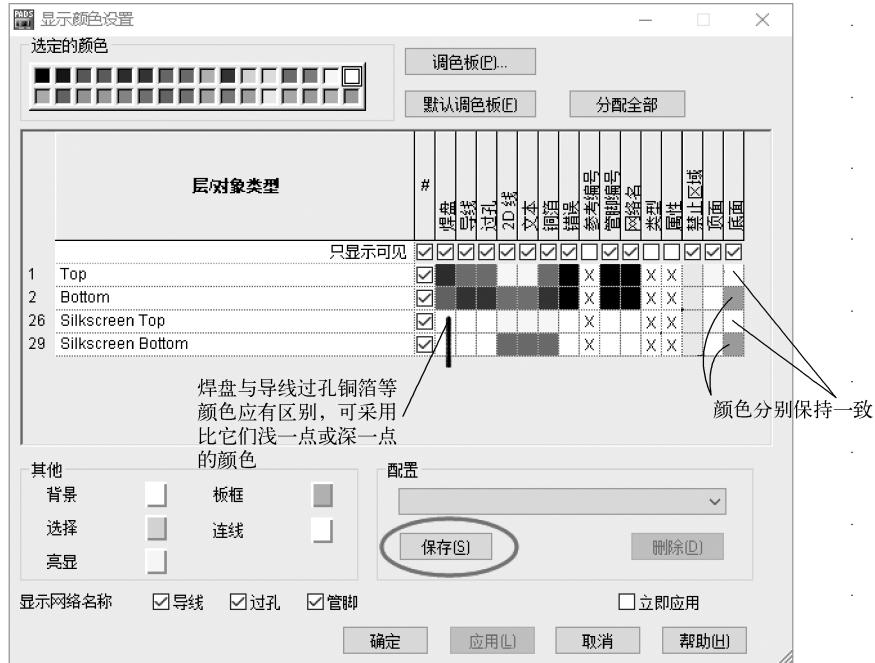

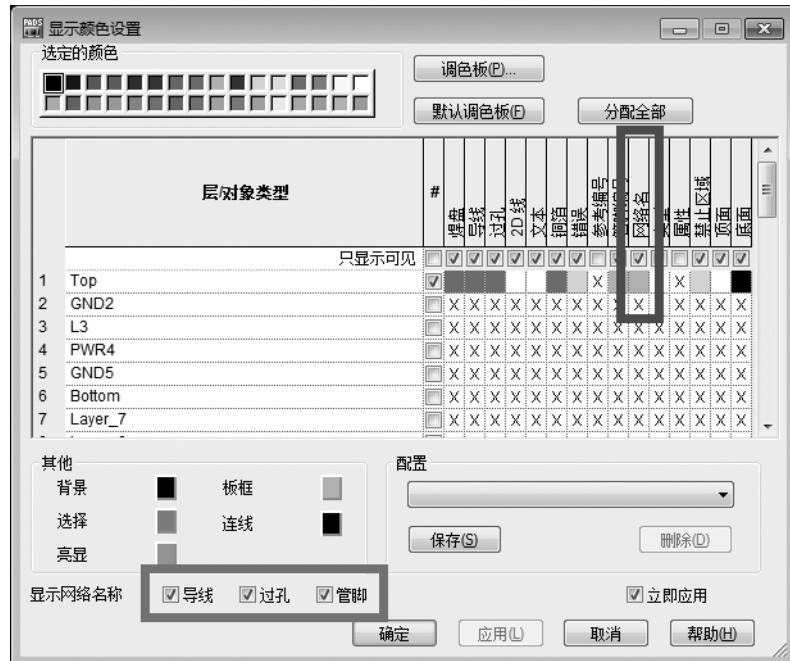

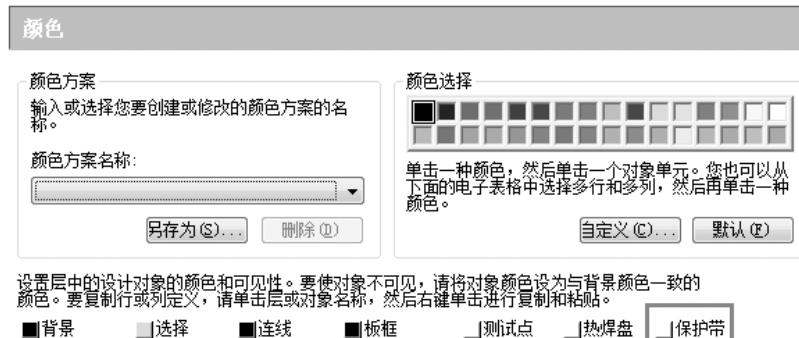

### 3.19 颜色设置

执行菜单命令【设置】-【显示颜色】，进入“显示颜色设置”对话框。

顶层顶面和丝印顶层顶面的颜色建议保持一致，因为不同设计师的设计习惯不一样，有些人喜欢把元器件丝印放在顶层，有些人喜欢放在丝印顶面，如果选择不一样的颜色，可能会造成误判断等情况。

焊盘的颜色应与导线、过孔和铜箔的颜色有所区别，能够更直观地进行走线打孔、绘制铜箔等操作。

设置颜色可根据个人习惯进行设置，需注意避免设置的颜色影响整个 PCB 的设计进度和设计质量。

配色方案可以保存，在后续的设计中可以调用，如图 3-41 所示。

图 3-41 “显示颜色设置”对话框

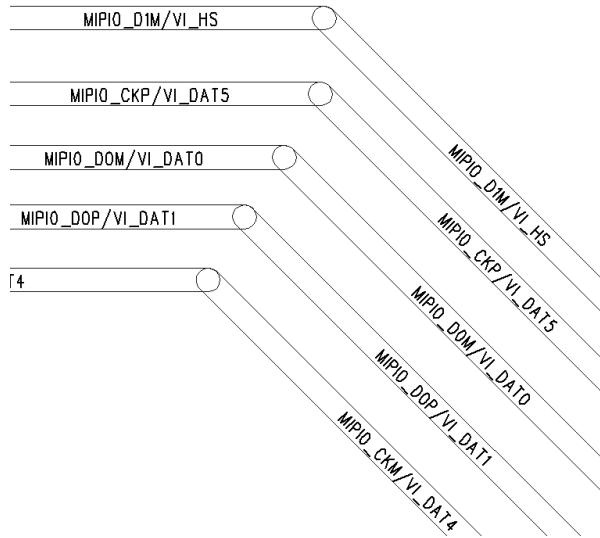

在设计中显示网络名能够一定程度上提高我们的设计效率，在“显示颜色设置”对话框中，勾选“网络名”、“导线”、“过孔”、“管脚”。注意网络名的颜色应与其他颜色区分开，以免颜色一致而导致隐藏，如图 3-42 所示。

图 3-42 网络名显示设置

设置完成后查看导线网络名，如图 3-43 所示。

图 3-43 导线显示网络名

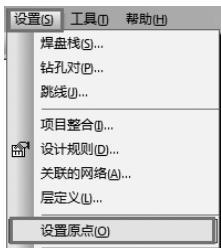

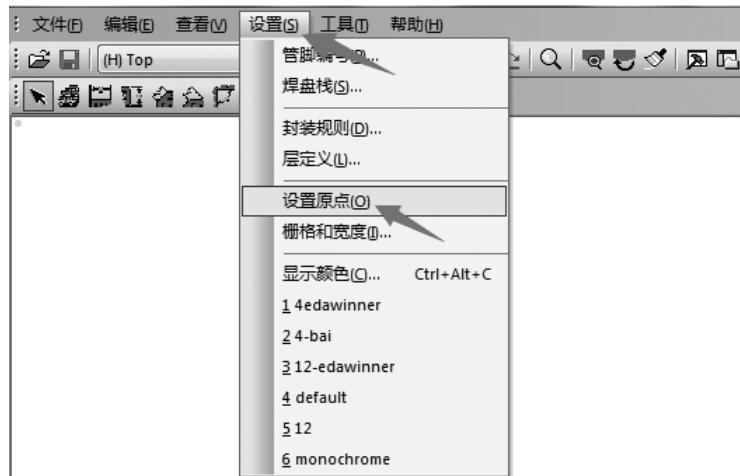

### 3.20 原点设置

执行菜单命令【设置】-【设置原点】，如图 3-44 所示。

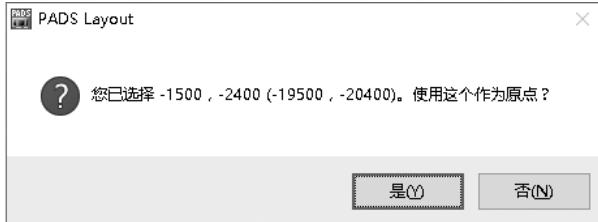

可以在工作区的任意位置单击鼠标左键，会弹出一个对话框，询问是否将相应的点设置为原点，如图 3-45 所示。

图 3-44 设置原点

图 3-45 确认原点位置

### 3.21 设置原点——元器件中心

执行菜单命令【设置】-【设置原点】，如果需要将原点设置在元件中心，则选中该元件后，输入无模命令“SO”，按下【Enter】键即可将原点设置在元件中心，如图 3-46 所示（此方法适用于创建封装时原点设置在元件中心的元件）。

图 3-46 设置原点在元件中心

### 3.22 设置原点——斜交拐角

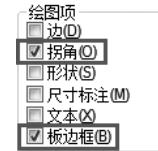

如果要将原点设置在板框直角的拐角处，如图 3-47 所示。

单击鼠标右键，进入筛选条件，勾选“绘图项”的“拐角”和“板边框”，单击【确认】按钮，如图 3-48 所示。

图 3-47 设置拐角处原点

图 3-48 筛选条件选择

选中该拐角，输入无模命令“SO”，按下【Enter】键即可将原点设置在拐角处。

### 3.23 设置原点——圆弧拐角

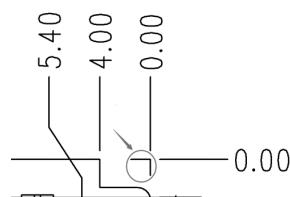

如果要将原点设置在板框弧线的拐角处，可借助螺丝孔或 MARK 等器件来设置原点，如图 3-49 所示。

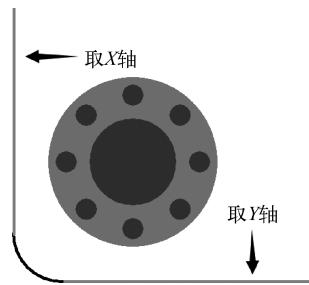

查看与弧线相接的两根线的特性，其中竖线取 X 轴坐标，横线取 Y 轴坐标，如图 3-50 所示。

选中螺丝孔，进入特性，输入 X、Y 轴坐标，如图 3-51 所示。

图 3-49 设置原点在拐角

图 3-50 取值思路

图 3-51 设置完成

螺丝孔将移动到拐角中心位置，这时又可使用将原点设置在元件中心的方法，将原点设置在元件中心（即板框弧线的拐角处）。

### 3.24 板层层数设置

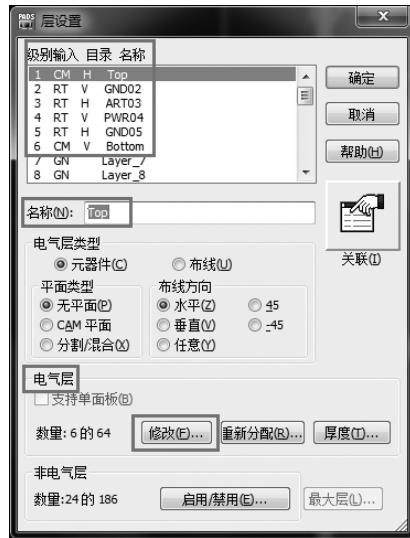

执行菜单命令【设置】-【层定义】，在“电气层”标签中单击【修改】按钮，可设置成需要的层数（奇数层只限于单面板）。

在名称处，可以修改层的名字。

走线层推荐名称使用：ART \*\*。

地层推荐名称使用：GND \*\*。

电源层推荐名称使用：PWR \*\*。

如图 3-52 所示。

图 3-52 层定义

### 3.25 默认线宽间距设置

执行菜单命令【设置】-【设计规则】，单击“默认”，如图 3-53 所示。

图 3-53 “规则”对话框

弹出的对话框如图 3-54 所示，单击“安全间距”。

图 3-54 “默认规则”对话框

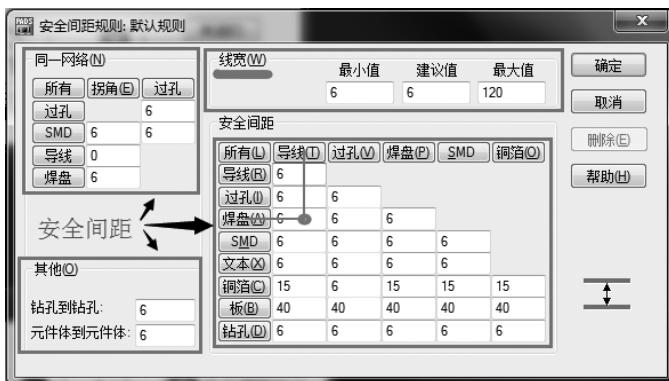

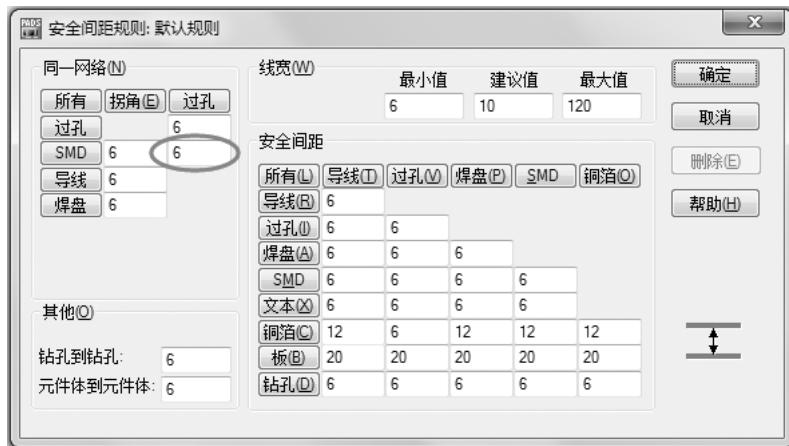

在弹出的对话框中可以针对各种元素之间的距离和线宽进行设置，如图 3-55 所示。线宽设置的建议值应在最小值和最大值的范围内，否则设置会出现类似对话框，如图 3-56 所示。

图 3-55 安全间距和线宽设置

图 3-56 报错窗口

推荐的安全间距设置如下。

- (1) 普通低速板：8mil。

- (2) 普通高速板：6mil。

- (3) 普通 BGA 的高密度板：4~5mil。

- (4) “板框”与所有元素：40mil。

- (5) “铜箔”与所有元素：12~20mil。

- (6) “铜箔”与过孔：4~8mil。

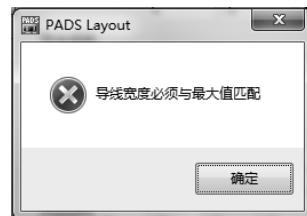

## 3.26 建立类规则

通常包括整板的电源和接地网络、各个模块的并行总线，关键信号线等。

执行菜单命令【设置】-【设计规则】，单击“类”，如图 3-57 所示。

图 3-57 进入类规则

输入类名称后单击【添加】按钮，之后在可用网络上选择网络添加至已选定，如图 3-58 所示。可以对类里面的网络进行安全间距、布线限制的设定。

图 3-58 “类规则”对话框

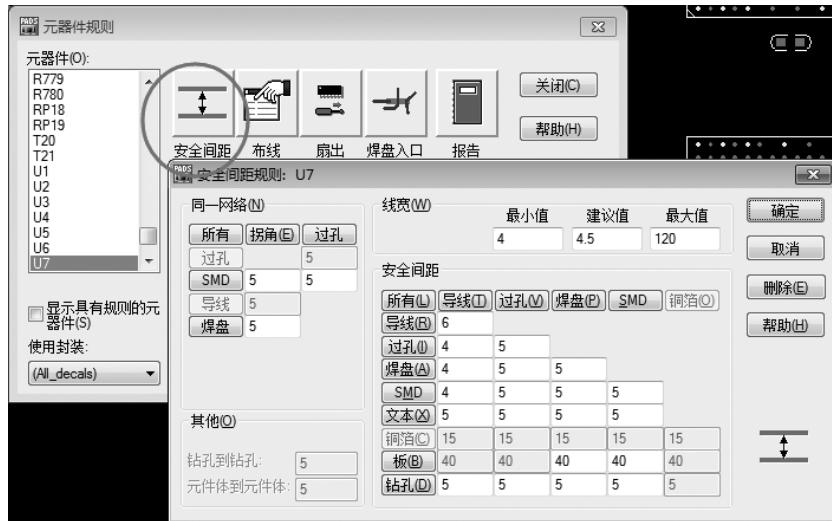

### 3.27 BGA 元器件规则设置

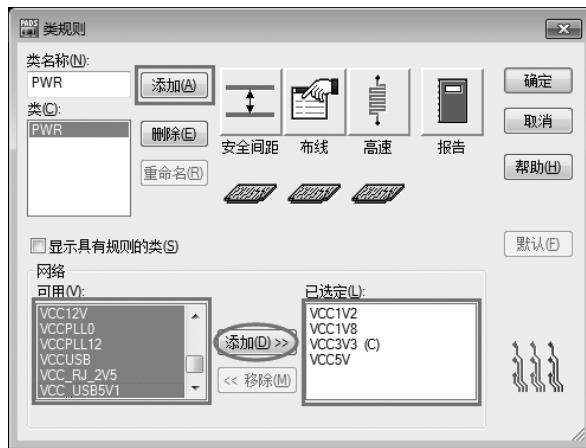

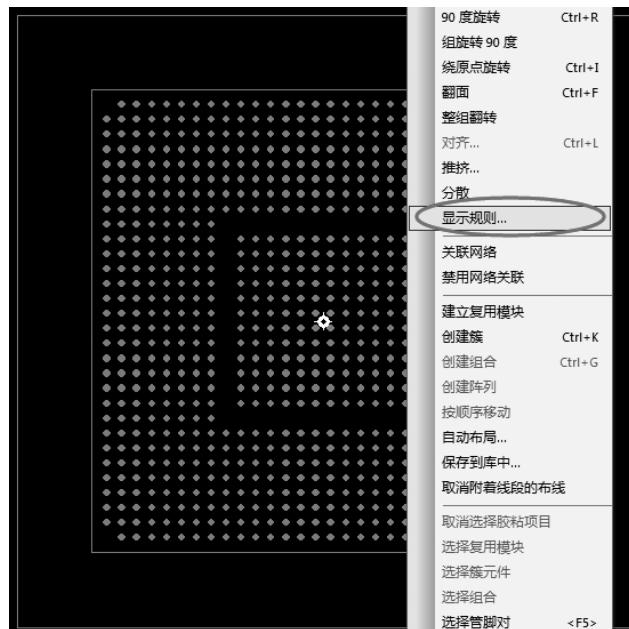

为便于 BGA 出线，BGA 部分常采用比其他位置稍小的线宽线距进行设计，选中要设置规则的元器件，单击鼠标右键，执行菜单命令【显示规则】，如图 3-59 所示。

图 3-59 元器件显示规则

在弹出的对话框中单击“安全间距”，进行修改线宽线距，如图 3-60 所示。

图 3-60 “元器件规则”对话框

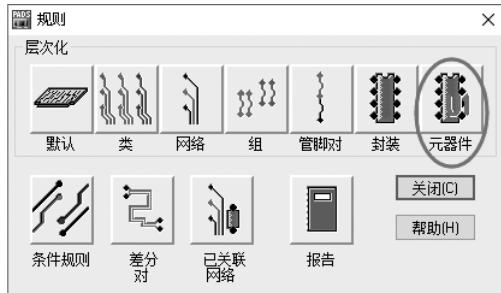

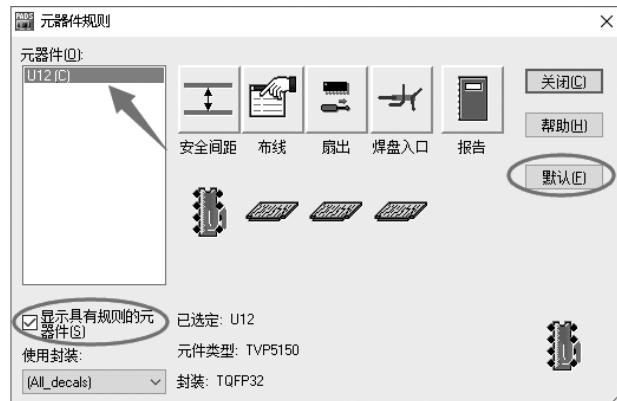

如果要取消元器件规则，在规则里面单击“元器件”，如图 3-61 所示。

图 3-61 单击“元器件”

勾选“显示具有规则的元器件”，元器件列表中将只出现存在规则设置的元器件，选中需要取消规则的，单击【默认】按钮，原有的规则会恢复至默认规则，如图 3-62 所示。

图 3-62 删除元器件规则

### 3.28 网络规则设置

为控制某个网络的线宽或与其他网络的距离，选中要设置规则的网络，单击鼠标右键，执行菜单命令【显示规则】，在弹出的对话框中单击“安全间距”，进行修改线宽线距，其操作与设置元器件规则类似。

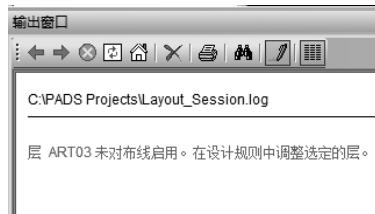

### 3.29 层未对布线启用

在 TOP 层布线时，输出窗口弹出以下报错，如图 3-63 所示。

该错误原因是“层 TOP 未对布线启用”，执行菜单命令【设置】-【设计规则】-【默认】-【布线】，将需要的层添加到选定的层后，就可以在 TOP 层走线了，如图 3-64 所示。

图 3-63 错误类型

图 3-64 设置布线层

### 3.30 布线中过孔设置

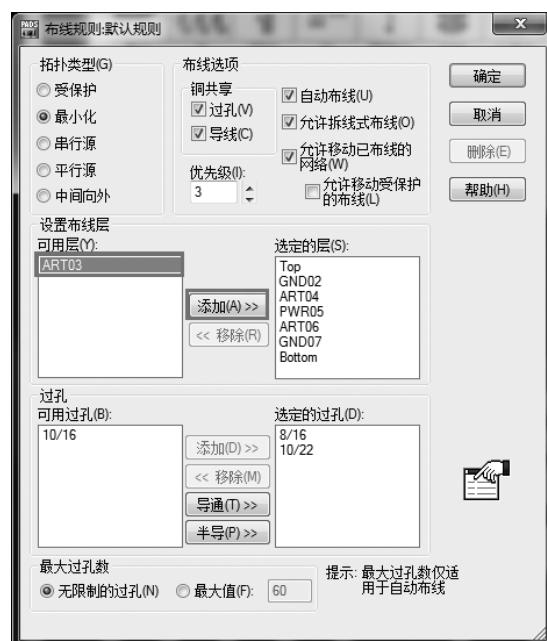

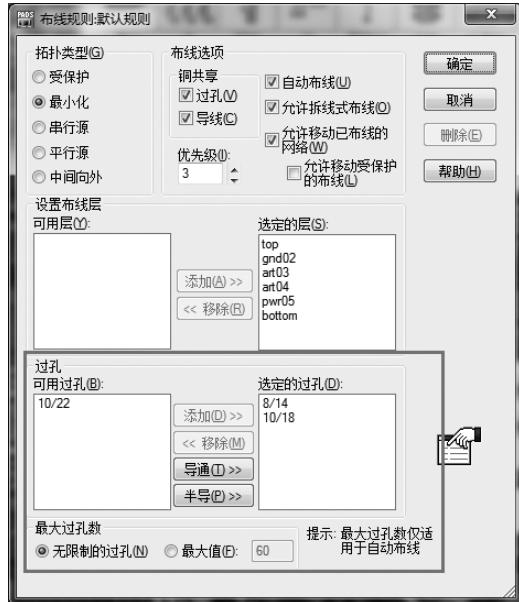

执行菜单命令【设置】-【设计规则】-【默认】-【布线】，弹出以下对话框，如图 3-65 所示。

**可用过孔：**意思是当前设计状态下未采用的过孔（可能之前已经使用，但目前不想使用）。

**选定的过孔：**代表可以在设计中添加的过孔。

**最大过孔数：**一般不用限制。

图 3-65 “布线规则：默认规则”对话框

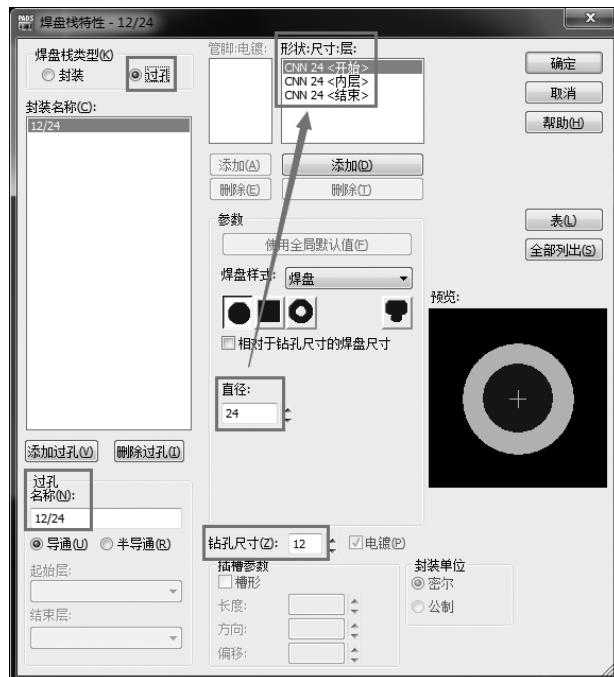

### 3.31 新建过孔的设置

执行菜单命令【设置】-【焊盘栈】，在“焊盘栈类型”中选择“过孔”，如图 3-66 所示。

图 3-66 过孔设置

输入钻孔的尺寸和直径（直径需要在开始层、内层、结束层各设置一次），过孔名称的格式为：钻孔尺寸/直径。

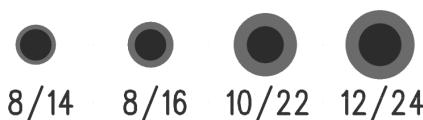

### 3.32 常用的过孔大小

PCB 中的过孔类型过多无疑会增加加工程序和价格，选用合适过孔显得尤为重要。

通孔 PCB 设计通常使用 3 种过孔：

- (1) 对于密度较高的区域采用局部小孔；

- (2) 除密度较高的区域外的常规过孔；

- (3) 电源过孔，稍大，以满足载流能力。

图 3-67 机械通孔

以下为常用的过孔大小：

- (1) 激光盲孔：4/8、4/10；

- (2) 激光埋孔：8/16；

- (3) 机械通孔：8/14、8/16、10/22、12/24。

图 3-67 为机械通孔。

### 3.33 修改元件边框宽度

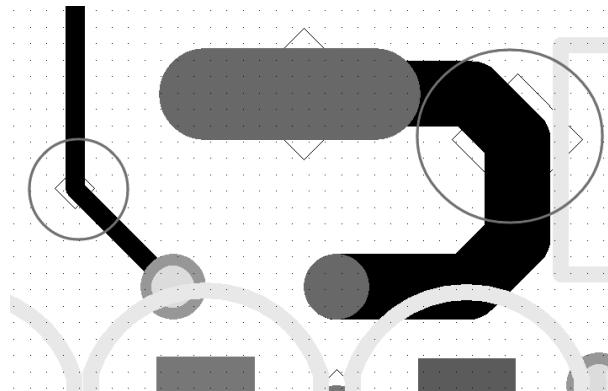

在选择元件的情况下，通过【Ctrl + A】组合键选中所有元件，通过右键菜单进入“元器件特性”对话框，在“元件边框宽度”标签中，可以统一修改元件边框的宽度，如图 3-68 所示。

图 3-68 修改元件边框宽度

### 3.34 消除拐角处的方框

“拐角处的方框”如图3-69所示。形成的位置多在每一次拐角处，不会对生产造成影响。

图 3-69 拐角处的方框

执行菜单命令【工具】-【选项】，在“布线/常规”的对话框中取消勾选“显示标记”，如图3-70所示。

图 3-70 取消“显示标记”

### 3.35 新添加的文本有边框

“文本边框”如图3-71所示。

输入无模命令“X”，按下【Enter】后，边框将消失，如图3-72所示。

图 3-71 文本边框

图 3-72 文件边框消失

### 3.36 自动填充

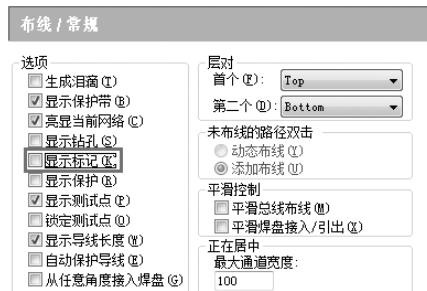

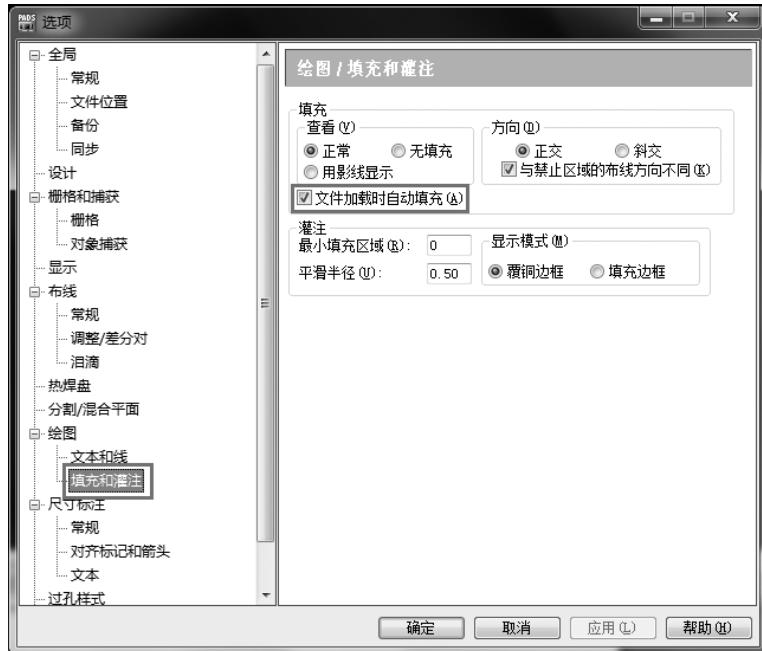

打开新文件，覆铜默认是不填充的，需要重新灌注覆铜，通过设置可以免去这一步骤，执行菜单命令【工具】-【选项】，在“绘图”选项中选择“填充和灌注”，勾选“文件加载时自动填充”，如图 3-73 所示。

图 3-73 文件自动填充

### 3.37 自交叉多边形

在绘图时经常出现自交叉多变形，如图 3-74 所示。

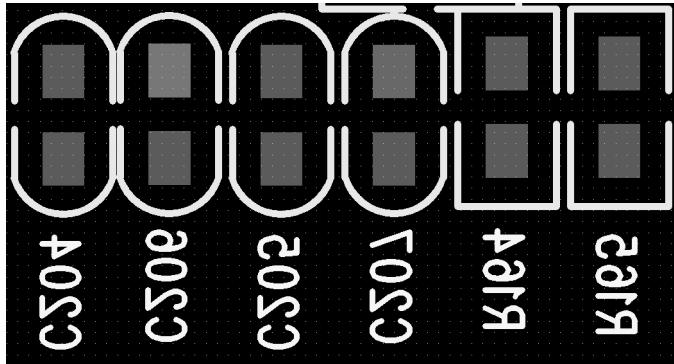

出现该问题的原因是线的宽度大于线拐角的宽度，导致线转不了弯，执行菜单命令【工具】-【选项】，在“绘图”选项中选择“文本和线”，可以修改成合适的默认宽度，如图 3-75 所示。

图 3-74 自交叉多边形

图 3-75 修改文本和线的默认宽度

### 3.38 底面视图的作用

在调节底层丝印时，丝印的方向是反过来的，如图 3-76 所示。

图 3-76 底层丝印

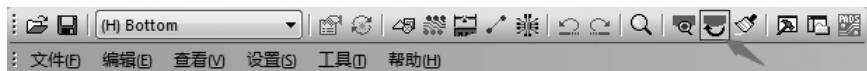

单击“底面视图”图标，如图 3-77 所示。

图 3-77 底面视图图标

以底面视图显示，调节丝印，更方便地调整和查看丝印的方向，如图 3-78 所示。

图 3-78 底层丝印底面视图

### 3.39 快速显示整板

对整板验证安全间距时，单击“板”图标，确保整板都能够被检查到，如图 3-79 所示。

图 3-79 “板”图标

效果如图 3-80 所示。

图 3-80 单击“板”图标后的效果

### 3.40 找不到工具栏

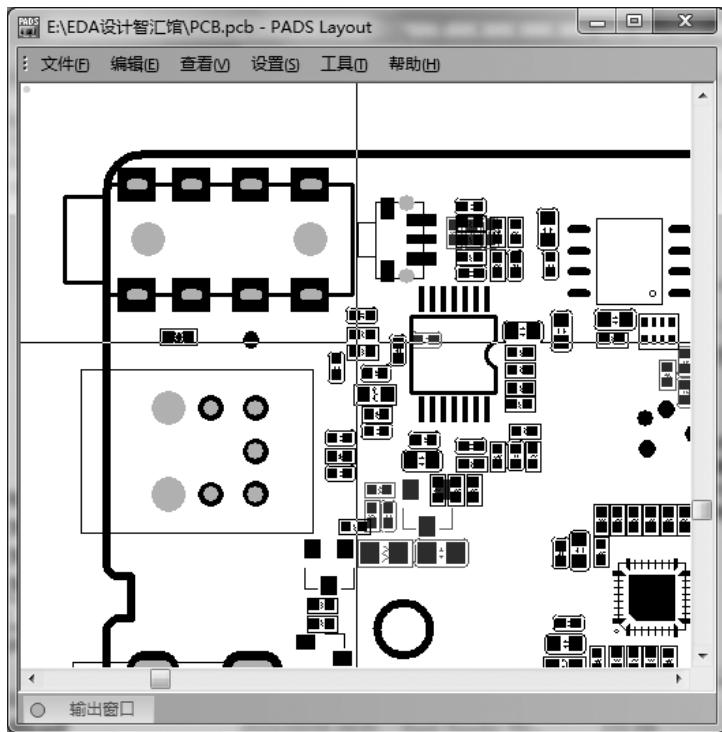

找不到工具栏，如图 3-81 所示。

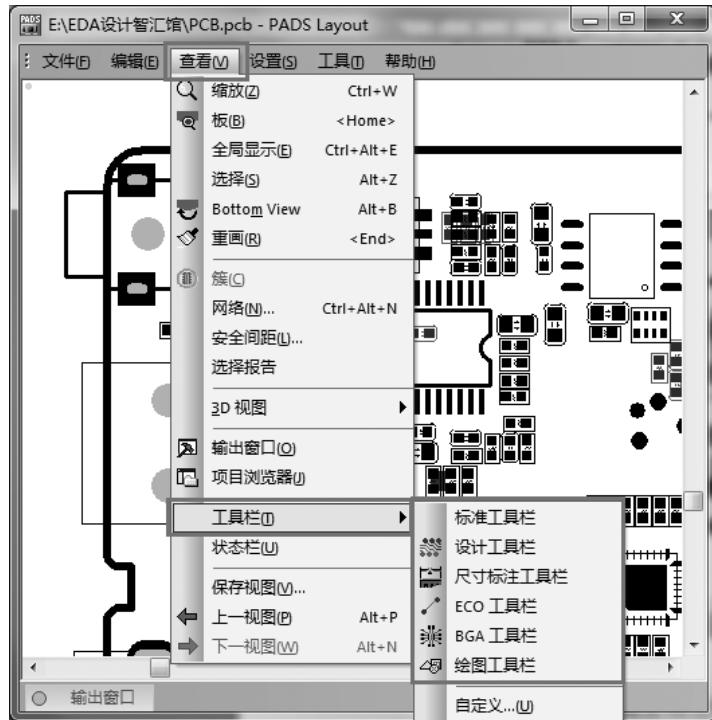

首先应检查有没有被最小化，没有最小化那么就是被关闭了，所有的工具栏可以通过执行菜单命令【查看】-【工具栏】进行开启或关闭，如图 3-82 所示。

图 3-81 找不到工具栏

图 3-82 查看工具栏

### 3.41 鼠标中键缩放失灵和删除自定义快捷键

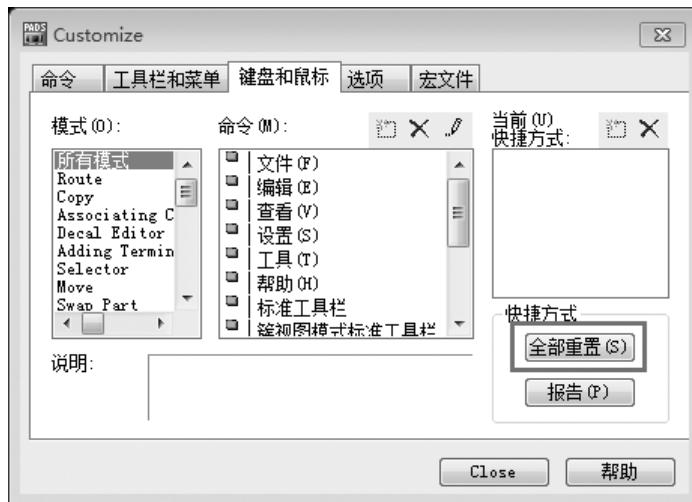

执行菜单命令【工具】-【选项】-【自定义】，在弹出的对话框中单击“键盘和鼠标”标签页，单击【全部重置】按钮，如果还没有反应，可以再将“工具栏和菜单”、“选项”里面的重置选项点一下，如图 3-83 所示。

图 3-83 重置功能

### 3.42 切换中英文界面

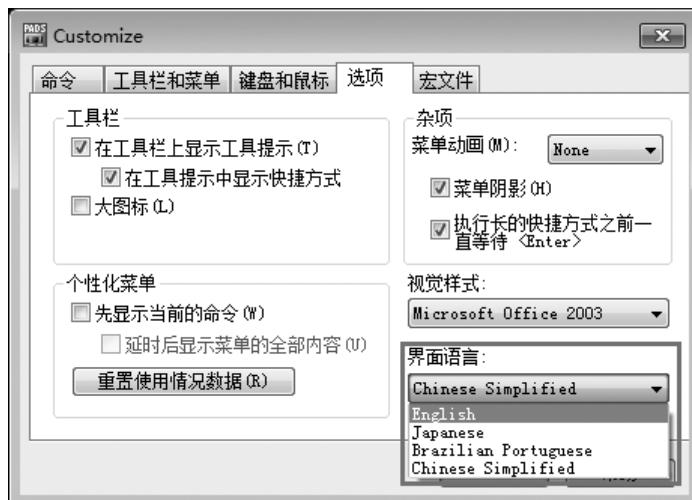

PADS9.5 版本之后的版本中都加入了简体中文，执行菜单命令【工具】-【选项】-【自定义】，在弹出的对话框中单击“选项”标签页，在“界面语言”的下拉菜单中选择语言，更新了界面语言后需要重启软件，如图 3-84 所示。

图 3-84 更新界面语言

### 3.43 笔记本电脑 Fn + 功能键

有些笔记本快捷键必须配合 Fn 才可以使用。例如，在 PADS layout 中，添加连线的快捷键是 F2，Fn + F2 在键盘是不太方便使用的。

建议通过咨询购买电脑的厂家，或通过网上搜索，达到取消 F1 ~ F12 功能键的目的。

### 3.44 启动软件不进入欢迎使用界面

软件启动界面如图 3-85 所示。

图 3-85 软件启动界面

单击“帮助”，取消勾选“启动时显示欢迎屏幕”，如图 3-86 所示。

图 3-86 取消启动时显示欢迎屏幕

99

# 第4章 封装

## 4.1 封装编辑器

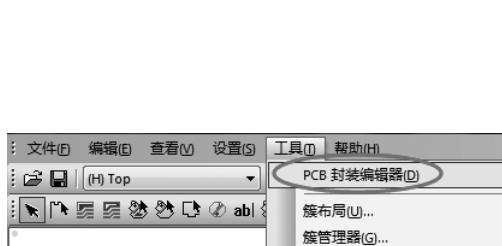

执行菜单命令【工具】-【PCB 封装编辑器】，如图 4-1 所示。

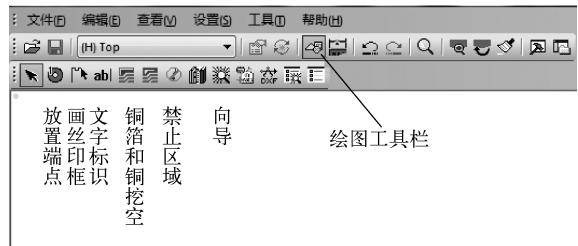

PCB 封装编辑器常用功能如图 4-2 所示。

图 4-1 进入 PCB 封装编辑器

图 4-2 PCB 封装编辑器常用功能

## 4.2 元件中心的热焊盘

对于发热量大的器件，常看到元件中心有个焊盘。

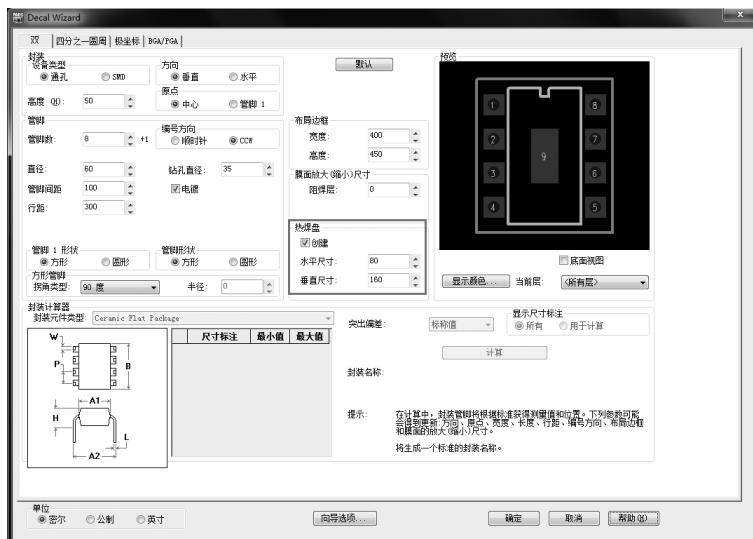

在用封装向导创建，勾选热焊盘将多一个焊盘在元件中心。

改变水平尺寸和垂直尺寸，热焊盘的大小也相应改变，如图 4-3 所示。

图 4-3 热焊盘

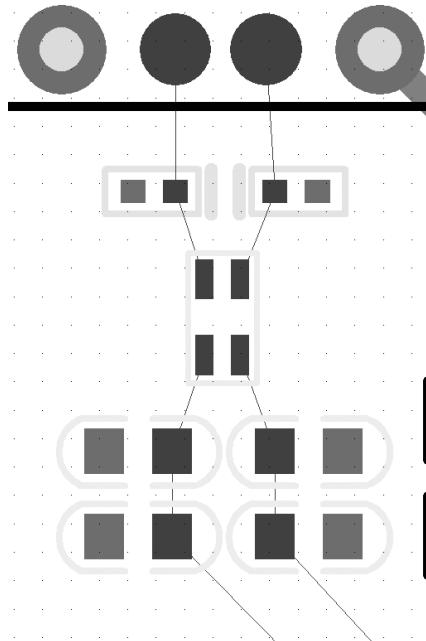

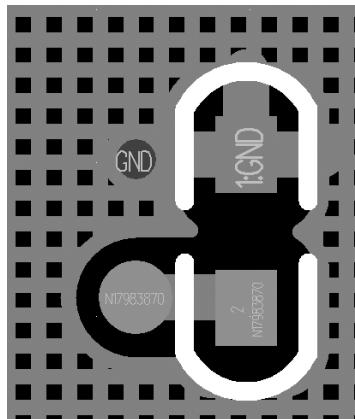

### 4.3 异形封装的创建

异形封装的创建技巧是用端点焊盘关联铜箔，关联后，铜箔具备跟焊盘一样的属性。按键异形封装如图 4-4 所示。

放置两个端点，可以将它修改为较小尺寸的端点，如图 4-5 所示。

图 4-4 按键异形封装

图 4-5 放置端点

根据规格书或实物绘制铜箔，可能会出现“网格铜”，如图 4-6 所示。

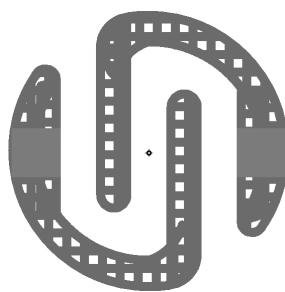

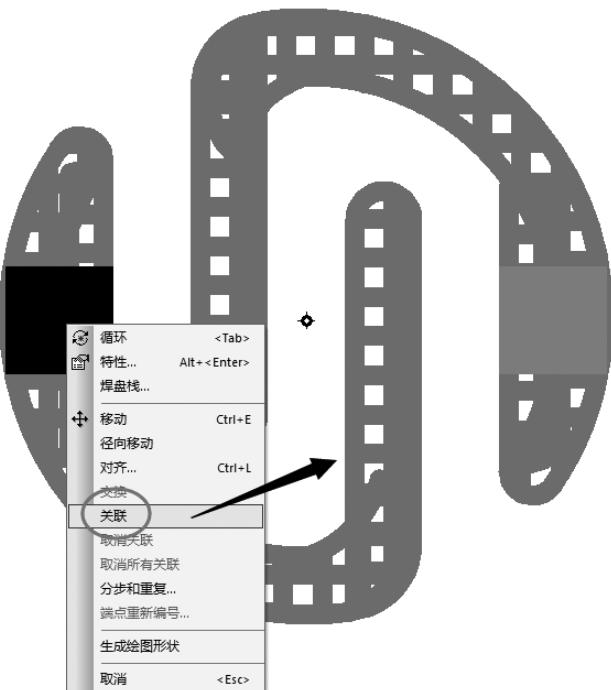

选中端点，单击鼠标右键，执行菜单命令【关联】，再单击“铜箔”，如图 4-7 所示。

图 4-6 绘制铜箔

图 4-7 关联网络

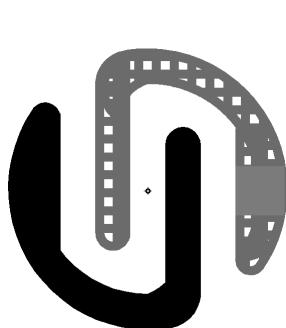

关联成功后，“网格铜”自动消失，铜箔变成“端点”，如图 4-8 所示。

最后绘制丝印框，如图 4-9 所示。

图 4-8 成功关联网络

图 4-9 异形封装创建完成

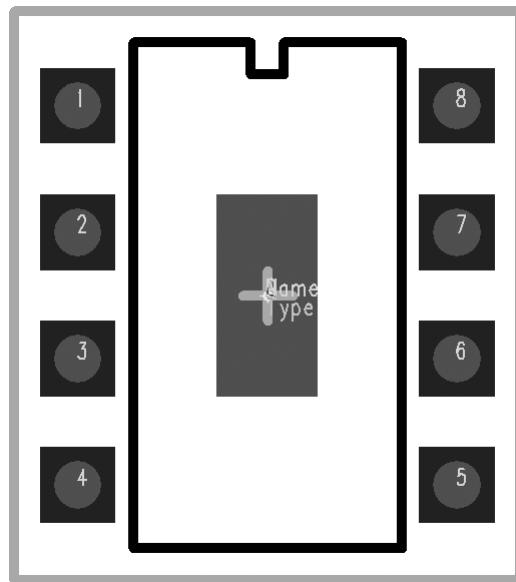

#### 4.4 用封装向导创建封装

封装外框如图 4-10 所示。

图 4-10 封装外框

在封装制作的绘图工具栏中，进入向导选项，如图 4-11 所示。

图 4-11 进入封装向导

取消勾选“创建”布局边框，如图 4-12 所示。

图 4-12 取消“创建”布局边框

在下次制作封装时，布局边框将取消创建。

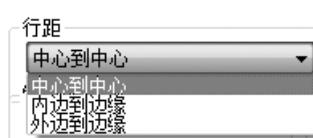

## 4.5 封装向导中行距三个“选项”的区别

三个“选项”如图 4-13 所示。

行距的参数是非常重要的，它们的行距区别如图 4-14 所示。

图 4-13 三个“选项”

图 4-14 行距区别

## 4.6 连续放置相同间距的焊盘

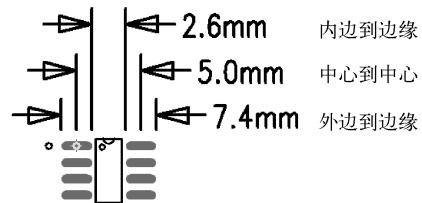

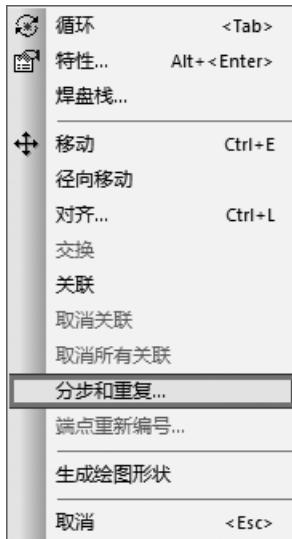

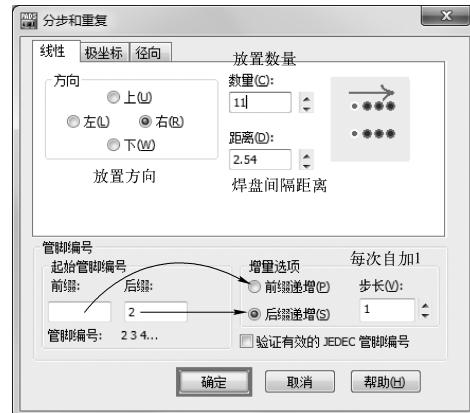

在放置一个焊盘之后，单击鼠标右键，执行菜单命令【分步和重复】，如图 4-15 所示。

弹出“分步和重复”对话框，前缀后缀可分别用字母或数字代替，增量选项中前缀递增代表前缀自加步长，如前缀为 A 时，步长为 1，递增则是 B、C、D...如图 4-16 所示。

图 4-15 执行菜单命令【分步和重复】

图 4-16 “分步和重复”对话框

使用的效果如图 4-17 所示。

图 4-17 利用分步和重复放置多个焊盘

## 4.7 定原点于元器件中心

以 SO8 封装为例，目前原点设置在 1 号引脚，如图 4-18 所示。

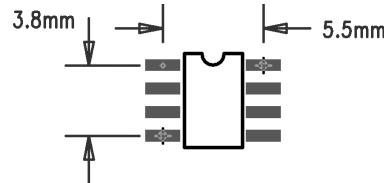

通过尺寸标注工具栏测的 1 脚 ~ 5 脚和 8 脚的中心距离，通过计算能够算出该元件的中心坐标为 (2.75, -1.9)，如图 4-19 所示。

图 4-18 SO8 封装

图 4-19 测量距离

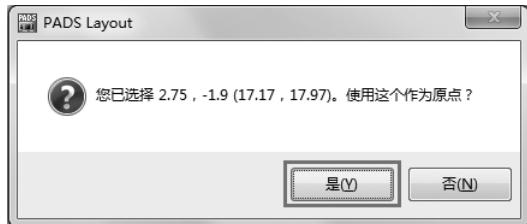

执行菜单命令【设计】-【设置原点】，如图 4-20 所示。

输出“S2.75, -1.9”，按下键盘【Enter】键，光标将跳到输入坐标的位置，再按一下空格键，在弹出的对话框中单击【是】按钮，如图 4-21 所示。

图 4-20 设置原点

原点设置完成，如图 4-22 所示。

图 4-21 确认原点位置

图 4-22 原点设置完成

## 4.8 元件丝印标识

制作的封装时，注明 1 脚标识和引脚编号，更有利于焊接和后期调试，如图 4-23 所示。

图 4-23 元件丝印标识

1 脚位置，可选用小圆点或小多边形代替。

5 脚用短线，10 脚用长线代替。

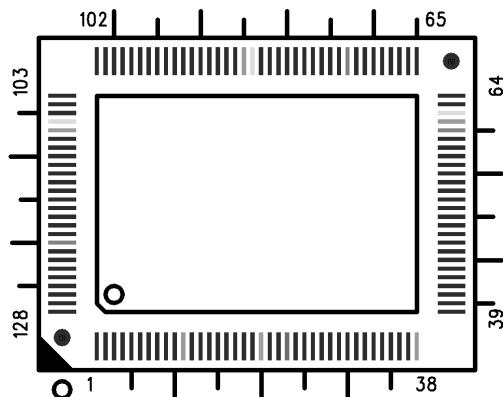

## 4.9 修改 BGA 封装上端点编号大小

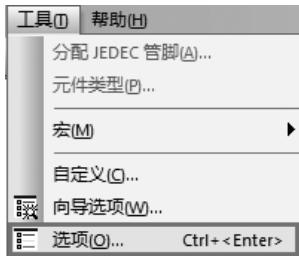

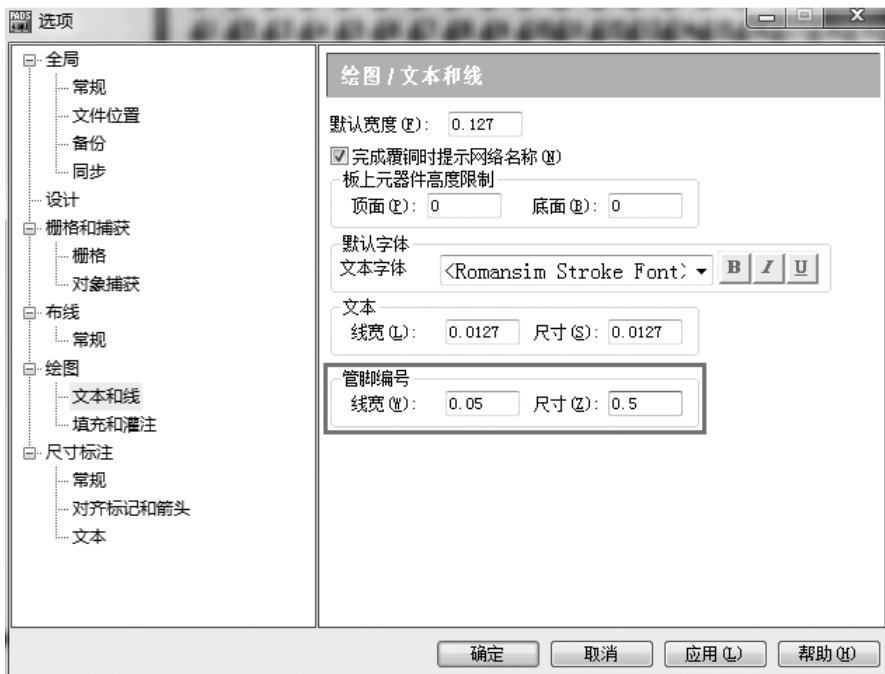

BGA 封装打开封装编辑器找某个焊盘时，如果端点编号过大，眼花缭乱不便于寻找。执行菜单命令【工具】-【选项】，如图 4-24 所示。

图 4-24 进入选项

在“文本和线”的“管脚编号”中修改参数，如图 4-25 所示。

图 4-25 修改“管脚编号”参数

“管脚编号”参数改小后的效果如图 4-26 所示。

图 4-26 “管脚编号”参数改小后的效果

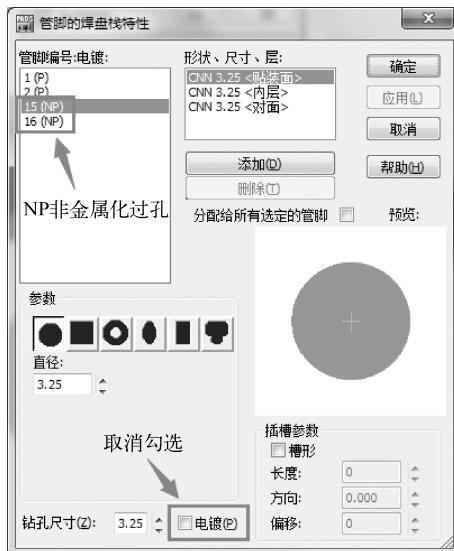

## 4.10 金属化过孔和非金属化过孔

金属化过孔指钻孔后，孔的内壁会用铜连接顶层、内层、底层、非金属化过孔，单纯钻一个孔而已，孔的内壁是没有铜的。在制作封装时，取消勾选“电镀”的通孔焊盘即为非金属化过孔。

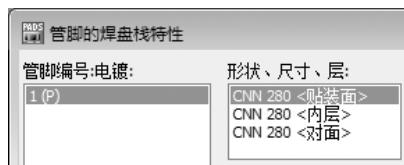

“管脚的焊盘栈特性”对话框如图 4-27 所示。

图 4-27 “管脚的焊盘栈特性”对话框

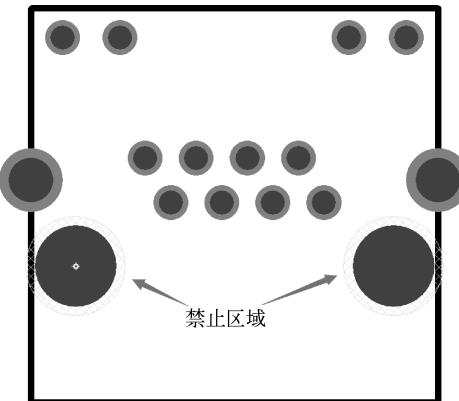

注意，如果是非金属化过孔，那么需要在所有层添加禁止区域，如图 4-28 所示。

图 4-28 非金属化过孔加禁止区域

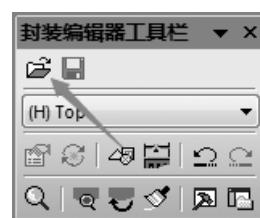

## 4.11 单独修改元器件 PCB 封装

选中元器件后，单击鼠标右键，执行菜单命令【编辑封装】，如图 4-29 所示。单击“打开”（打开封装）图标，如图 4-30 所示。

图 4-29 进入编辑封装

图 4-30 打开封装

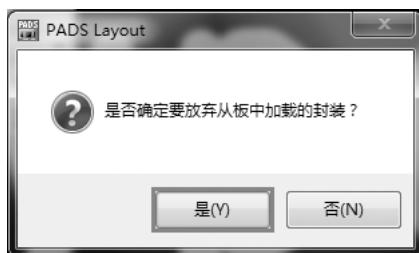

在弹出的对话框中单击【是】按钮，如图 4-31 所示。

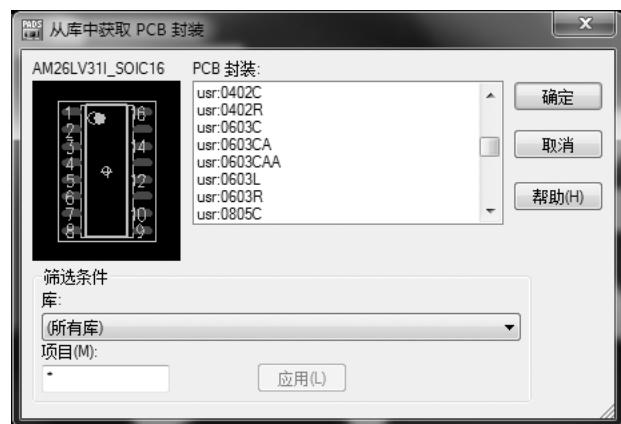

自动进入“库”，选择合适的封装，单击【确定】按钮，如图 4-32 所示。

图 4-31 单击【是】

图 4-32 从库中获取 PCB 封装

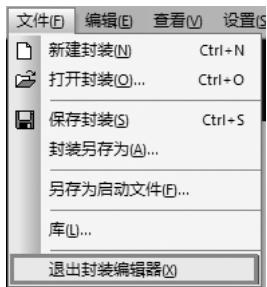

退出封装编辑器，如图 4-33 所示。

在弹出如图 4-34 所示的对话框中单击【确定】按钮。

图 4-33 退出封装编辑器

图 4-34 新封装用于元件类型

单击【已选定】按钮更改单个 PCB 封装，如果单击【所有】按钮，则此元件类型的 PCB 封装都将改变，如图 4-35 所示。

图 4-35 针对对象选择

## 4.12 如何把自己的封装给别人

(1) 进入库管理器，选中封装，单击【导出】按钮，如图 4-36 所示。

图 4-36 库中选中封装导出

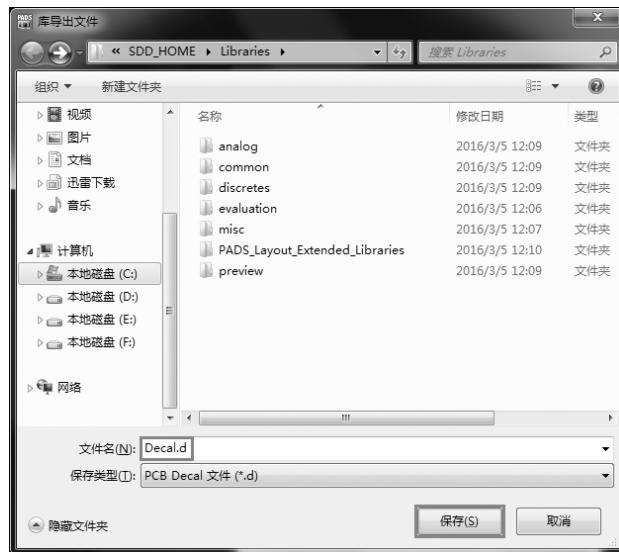

弹出“库导出文件”对话框，可以对导出的封装选择保存路径和重命名（后缀为“.d”的文件），如图 4-37 所示。使用时进入库管理器，导入该“.d”文件即可。

图 4-37 选择路径和重命名

(2) 如果是已建元件类型的封装，可以通过 ECO 功能直接添加元器件到 PCB 上，如图 4-38 所示。

图 4-38 ECO 功能添加元器件

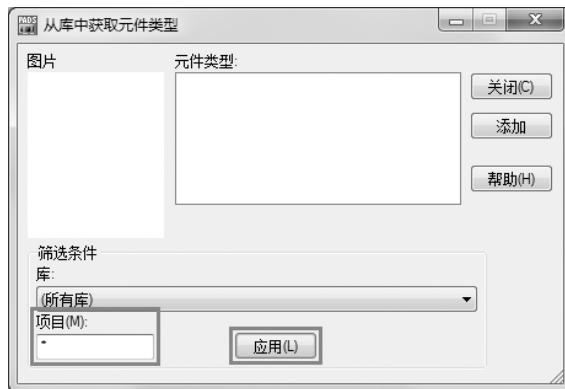

进行上面的操作之后，在弹出的对话框中，在项目标签中输入关键字进行搜索，找到需要封装对应的元件类型，如图 4-39 所示。

图 4-39 从库中获取元件类型

添加后将 PCB 文件发给别人，然后再提取里面的 PCB 封装。

# 第5章 布局

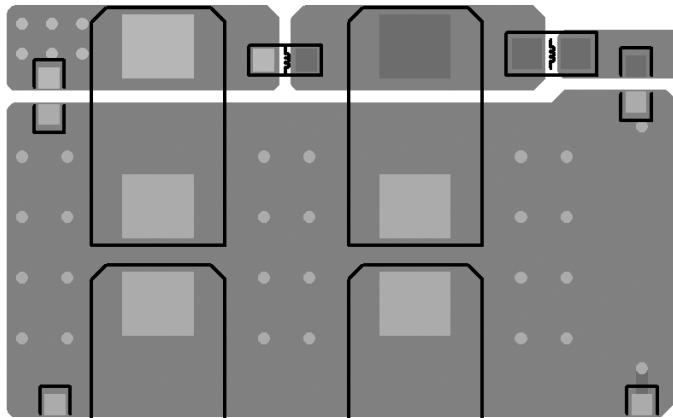

## 5.1 栅格布局法

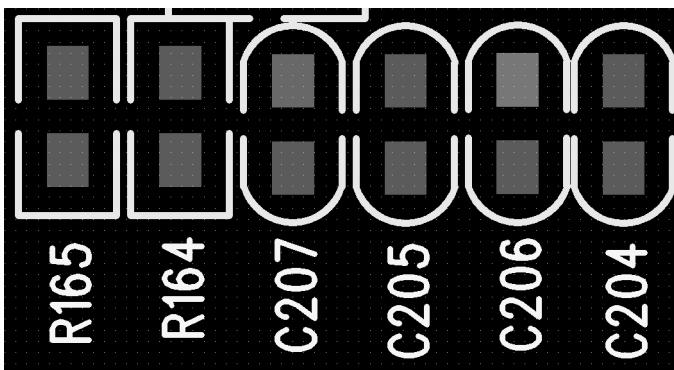

元器件布局整齐是衡量电路板美观的一个重要标准，运用栅格法能够控制整行或整排相同封装元器件间距的一致，整行元器件的X坐标一致或Y坐标一致。

使用大格点有利于器件的对齐和布局的美观。

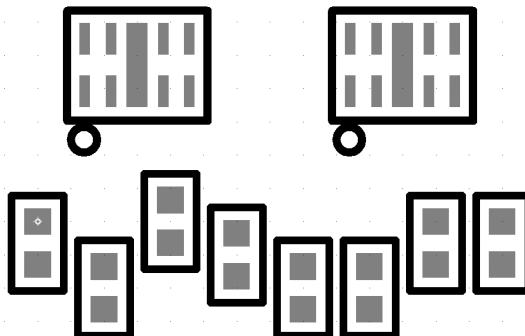

图5-1中的电容部分使用25mil的设计栅格进行布局。

图5-1 电容布局

修改设计栅格，执行菜单命令【工具】-【选项】，选择“栅格和捕获”选项中的“栅格”，输入参数进行更改栅格，如图5-2所示。

图5-2 栅格设置

## 5.2 对齐命令布局

对于图 5-3 的一列电阻，可以使用对齐命令进行 Y 坐标的对齐。

图 5-3 需要优化布局的电阻

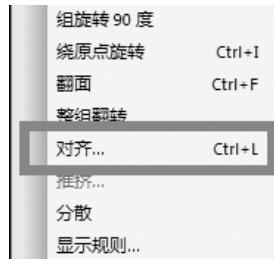

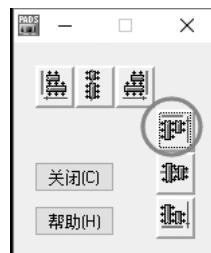

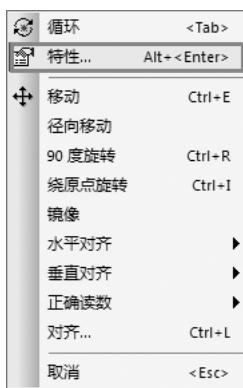

首先选中需要对齐的电阻，单击鼠标右键，在弹出的对话框中选择“对齐”命令，如图 5-4 所示。

根据需要进行选择合适的操作命令，本例中我们选择的是“Y 轴上对齐”，如图 5-5 所示。

图 5-4 “对齐”命令

图 5-5 “Y 轴上对齐”命令

对齐后的效果如图 5-6 所示。

图 5-6 对齐后的效果

### 5.3 Net 标注法布局

利用 NET 标注法对网络进行飞线的开启和颜色设置，直观地区分不同的网络进行布局。

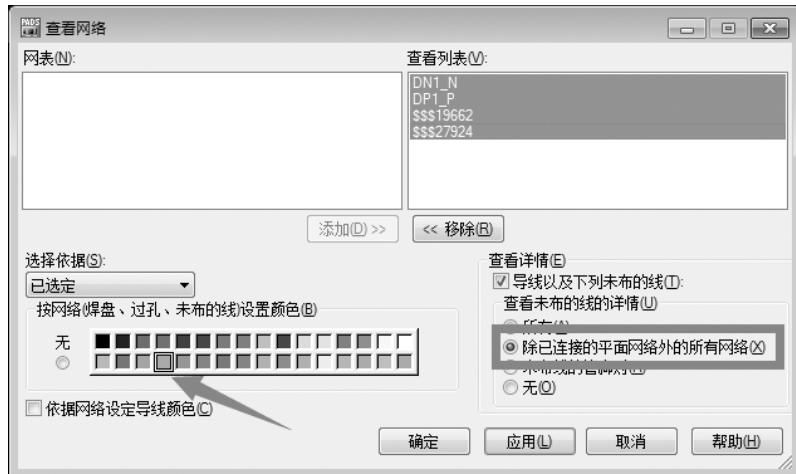

执行菜单命令【查看】-【网络】，进入“查看网络”对话框，选定“网表”上需要开启飞线或设置颜色的网络，单击【添加】按钮，添加到查看列表中。

在查看列表中，可以对选中网络的飞线和颜色进行编辑，如图 5-7 所示。

图 5-7 “查看网络”对话框

经过了分配颜色和开启飞线后的效果如图 5-8 所示。

图 5-8 NET 标注法布局的效果图

## 5.4 飞线引导法布局

应用飞线引导法布局，将原理图连接 PCB，在原理图上分模块抓取，切换至 PCB 部分，将模块按飞线的位置进行规划大致布局区域。

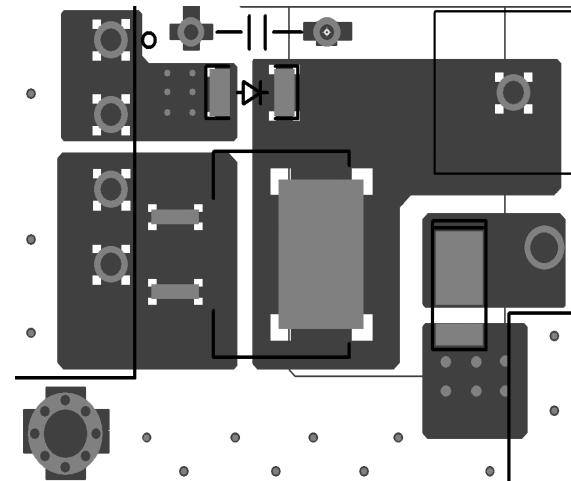

某个 PCB 大致布局后的效果如图 5-9 所示。

图 5-9 飞线引导法布局的效果图

## 5.5 输入坐标布局

具有结构要求的器件在布局时，将原点设置在板子左下角的相交处，将单位设置成毫米，在移动元件 S51 时输入“S719”，定位后再胶粘，确保器件不再被移动，结构如图 5-10 所示。

图 5-10 结构

## 5.6 组合布局

几个模块布局好后，位置还需要进行调整时，为避免多次移动时漏选元器件，将几个模块分别创建组合。

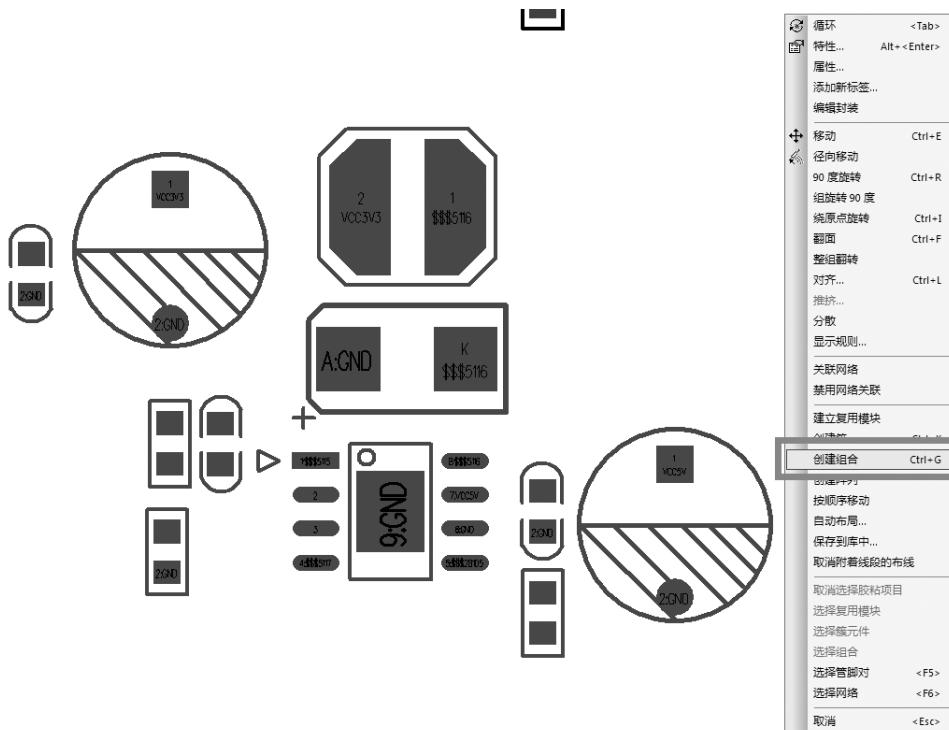

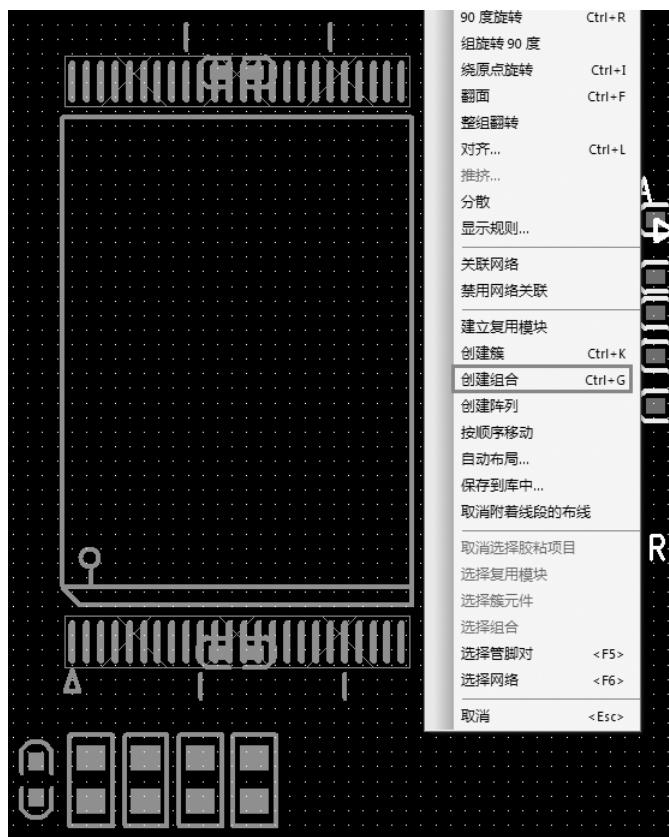

选择模块中所有的元器件后，单击鼠标右键，执行菜单命令【创建组合】，如图 5-11 所示。

图 5-11 创建组合

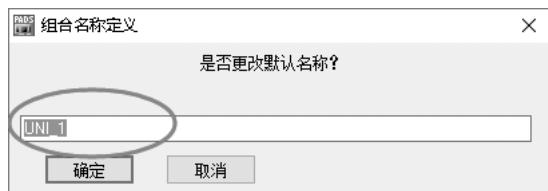

弹出“组合名称定义”对话框，可使用默认的名称创建组合，如图 5-12 所示。

图 5-12 组合名称定义

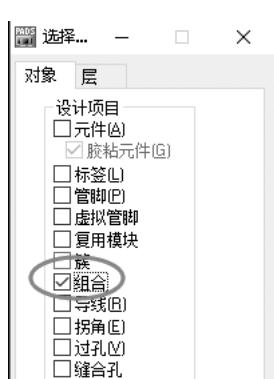

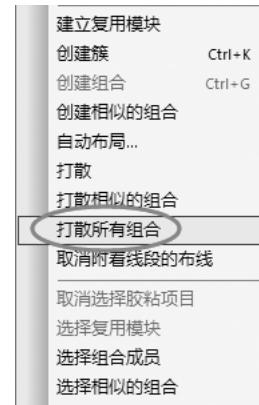

调整完成后，单击鼠标右键，执行菜单命令【筛选条件】，进入筛选条件，勾选“择组合”，如图 5-13 所示。

选中组合，单击鼠标右键，执行菜单命令【打散所有组合】，如图 5-14 所示。

图 5-13 勾选“组合”

图 5-14 打散所有组合

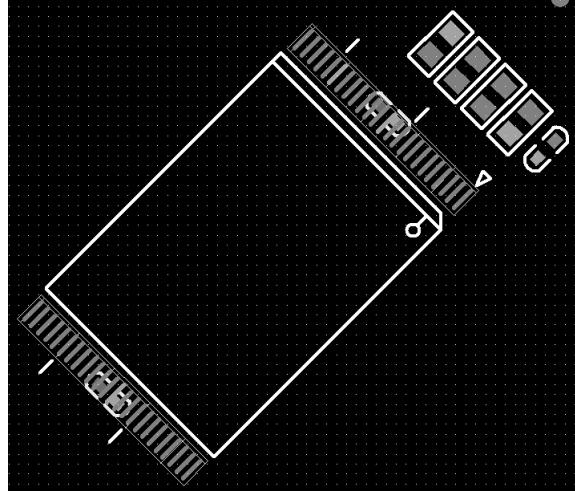

## 5.7 整个模块旋转

选中模块，单击鼠标右键，执行菜单命令【创建组合】，如图 5-15 所示，创建组合的步骤参考 5.6 节内容。

图 5-15 创建组合

创建成功后，选择组合，查看组合特性，在旋转的标签中输入“45”，代表旋转45°，如图5-16所示。

旋转之后再将组合打散，旋转效果如图5-17所示。

图5-16 修改旋转角度

图5-17 整个模块旋转

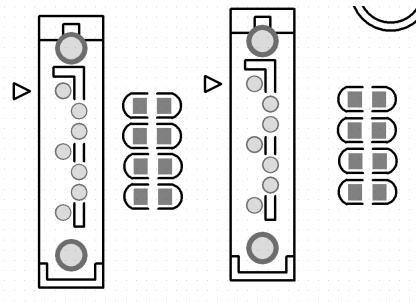

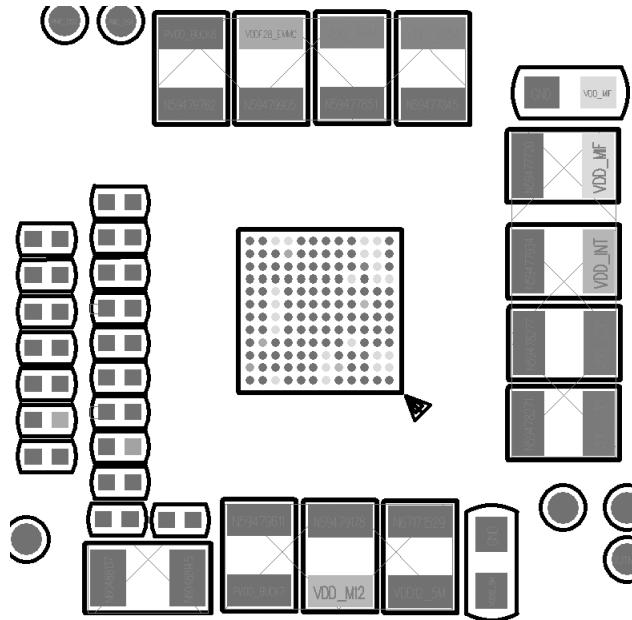

## 5.8 BGA器件布局

布局时，BGA元器件的3mm（极限1mm）内不能放置元器件，元器件放置过近，会导致不好焊接，如图5-18所示。

图5-18 BGA器件与外圈器件的距离

## 5.9 推挤元器件

元器件之间越界重叠不利于生产，开启元器件推挤功能，当元器件的丝印过近时，自动推挤元器件。

执行菜单命令【工具】-【选项】，选择“全局”选项中的“设计”，在“推挤”标签中选择“自动”，自动推挤距离过近的元器件，如图 5-19 所示。

图 5-19 开启自动推挤元器件

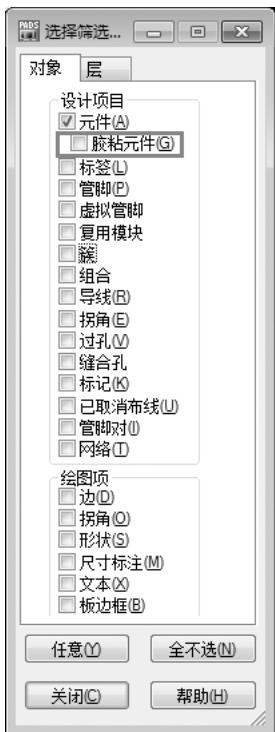

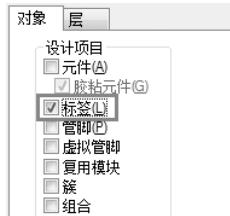

## 5.10 不选中胶粘的元件

单击鼠标右键进入筛选条件，取消勾选“胶粘元件”，如图 5-20 所示。

在后续设计中，将不会选中胶粘的元器件了。

## 5.11 导线随元器件移动

执行菜单命令【工具】-【选项】，选择“全局”选项中的“设计”，弹出的对话框如图 5-21 所示。

不建议勾选“元器件移动时拉伸导线”，元器件非直线移动拉伸的导线都无法使用，还要多删除一次，不拉伸导线，能更好地保留线头，图 5-22 为勾选“元器件移动时拉伸导线”移动元器件后的效果。

图 5-20 取消勾选“胶粘元件”

图 5-21 元器件移动时拉伸导线

图 5-22 元器件移动时拉伸导线

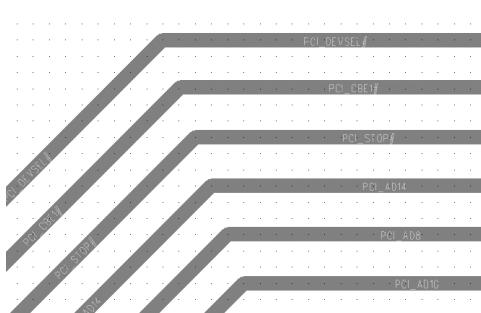

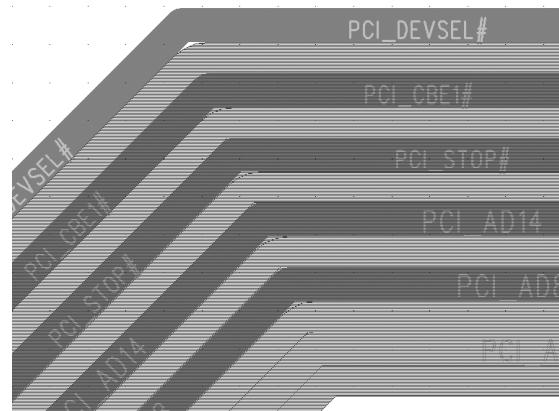

# 第6章 布线

## 6.1 走线的基本操作

按下键盘【F2】键，鼠标光标出现个“v”，在具有电气属性连接的焊盘处单击鼠标左键，线将引出，如图6-1所示。

需要拐弯的时候单击鼠标左键，导线能重新选择走线的角度，常规模式下，推荐使用斜交(45°)，如图6-2所示。

图 6-1 从焊盘上引线

图 6-2 线转角度

到达目标位置时，鼠标光标出现两个小圆圈，单击鼠标左键完成走线，如图6-3所示。

图 6-3 走线结束

## 6.2 打孔换层走线

走线状态下，同时按下【Shift + 鼠标左键】，打孔后换层，可以继续走线，如图 6-4 所示。

图 6-4 打孔换层继续走线

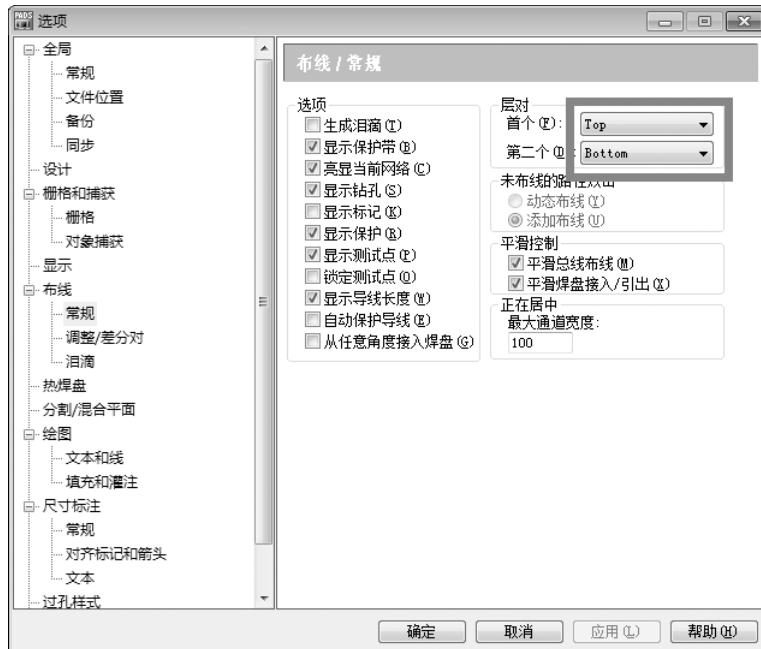

继续走线所在的层是依据层对设置来决定的，执行菜单命令【工具】-【选项】，选择“常规”选项，查看层对，如图 6-5 所示。

图 6-5 查看层对

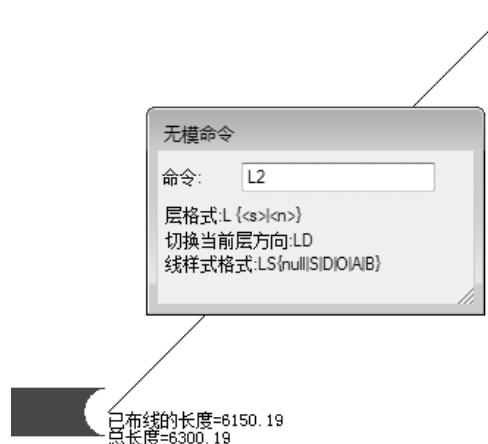

如果要换至任意电气层，可输入 L 层数，将在打孔后在相应的层开始走线，如图 6-6 所示。

图 6-6 换至任意层走线

### 6.3 走线暂停或结束

设计过程中，走线经常需要结束走线或暂时停止在某一个位置。

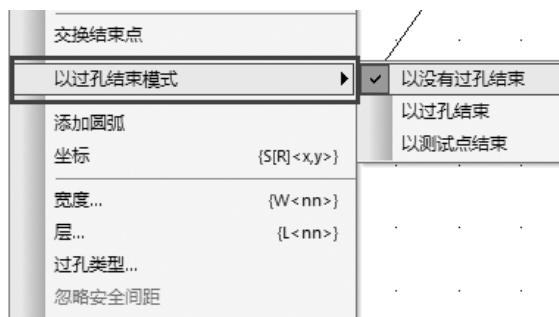

菜单命令中【以过孔结束模式】有 3 种模式可供选择，如图 6-7 所示。

- (1) 第一种：以线结束，结束时以线头结束；

- (2) 第二种：以孔结束，结束时将自动添加一个过孔；

- (3) 第三种：以测试点结束，结束时将自动添加测试点（通常不选用这种方式）。

图 6-7 结束 3 种模式

### 6.4 走线过程中导线加粗

走线时输入无模命令“W \*”（\* 代表线宽，线宽要求在规则设置中最小值与最大值之间），即可更改“这一次”的走线宽度，如图 6-8 所示。

图 6-8 走线时加粗导线

## 6.5 走线时改变线宽没反应

注意查看当前单位是不是毫米，输入的参数过大大会导致无模命令失效，如图 6-9 所示。

图 6-9 状态栏查看单位

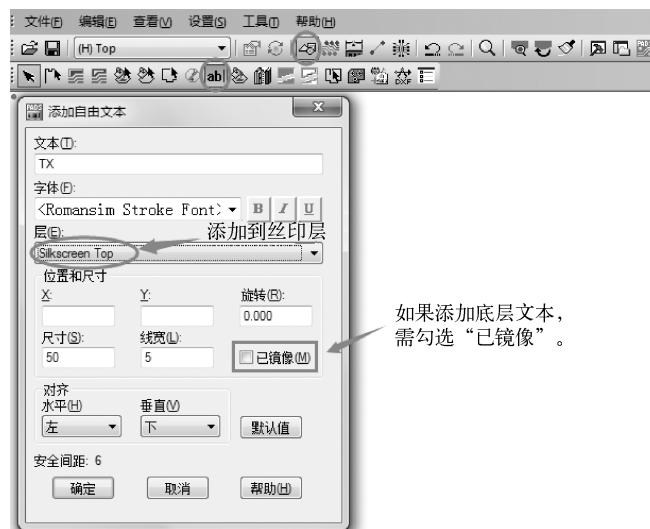

## 6.6 走线完成后导线加粗

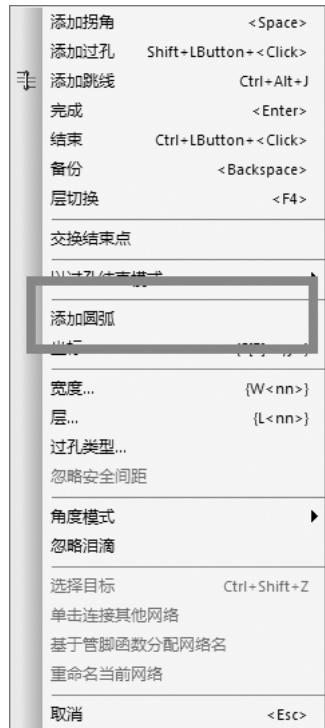

单击鼠标右键，执行菜单命令【筛选条件】，如图 6-10 所示。

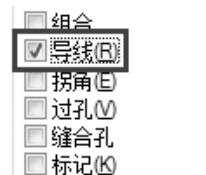

如果需要导线的某一段加粗，则只勾选“导线”，如图 6-11 所示。

图 6-10 进入筛选条件

图 6-11 勾选“导线”

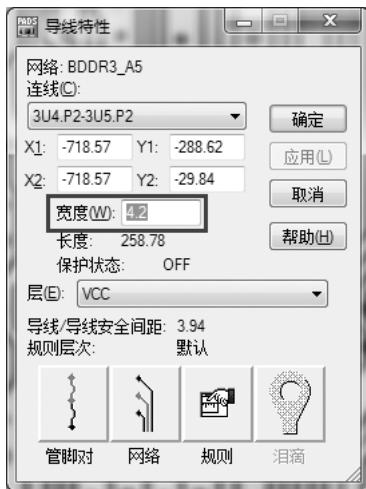

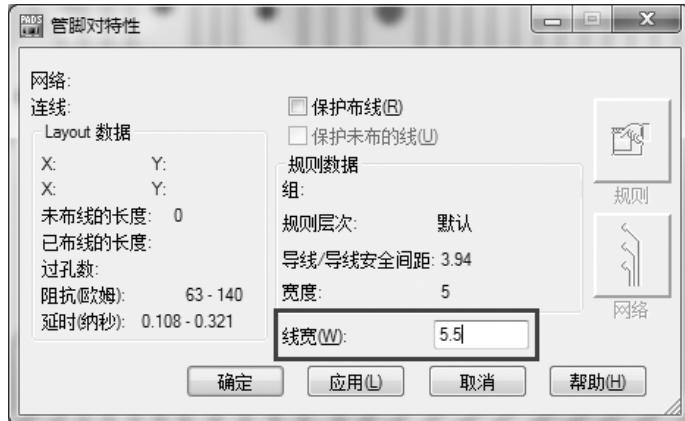

选择需要加粗的导线后，通过右键菜单，进入其特性，在未保护导线的情况下可以对其宽度进行编辑，如图 6-12 所示。输入合适的值单击【确定】按钮，线宽随即改变。

如果需要导线的某一层加粗，则只勾选“管脚对”，选中的效果如图 6-13 所示。

选择需要加粗的“管脚对”后，通过右键菜单，进入其特性，在未保护导线的情况下

可以对其宽度进行编辑，如图 6-14 所示。输入合适的值单击【确定】按钮，线宽随即改变。

图 6-12 “导线特性”对话框

图 6-13 勾选“管脚对”

图 6-14 “管脚对特性”对话框

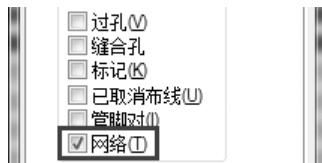

如果需要整个网络加粗，则只勾选“网络”，如图 6-15 所示。

图 6-15 勾选“网络”

选择需要加粗的网络后，通过右键菜单，进入其特性，在未保护网络的情况下可以对其宽度进行编辑，如图 6-16 所示。输入合适的值单击【确定】按钮，线宽随即改变。

图 6-16 “网络特性”对话框

## 6.7 走线时怎么走弧线

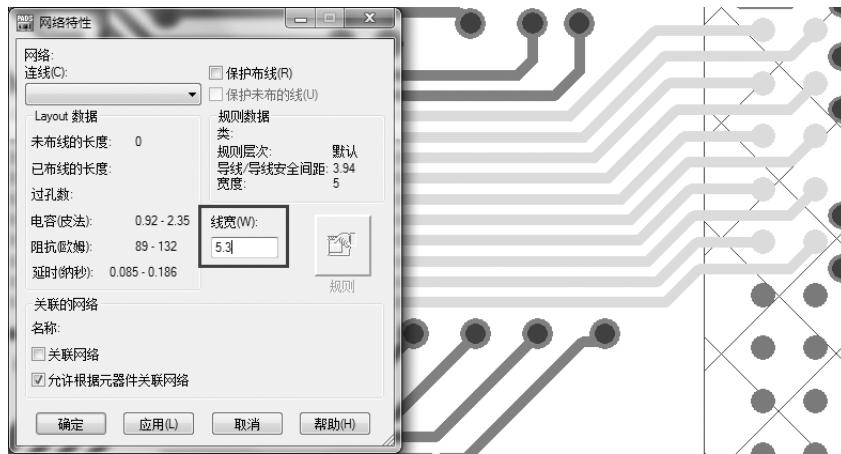

在走线过程中单击鼠标右键，执行菜单命令【添加圆弧】，如图 6-17 所示。添加圆弧的走线效果如图 6-18 所示。

图 6-17 添加圆弧

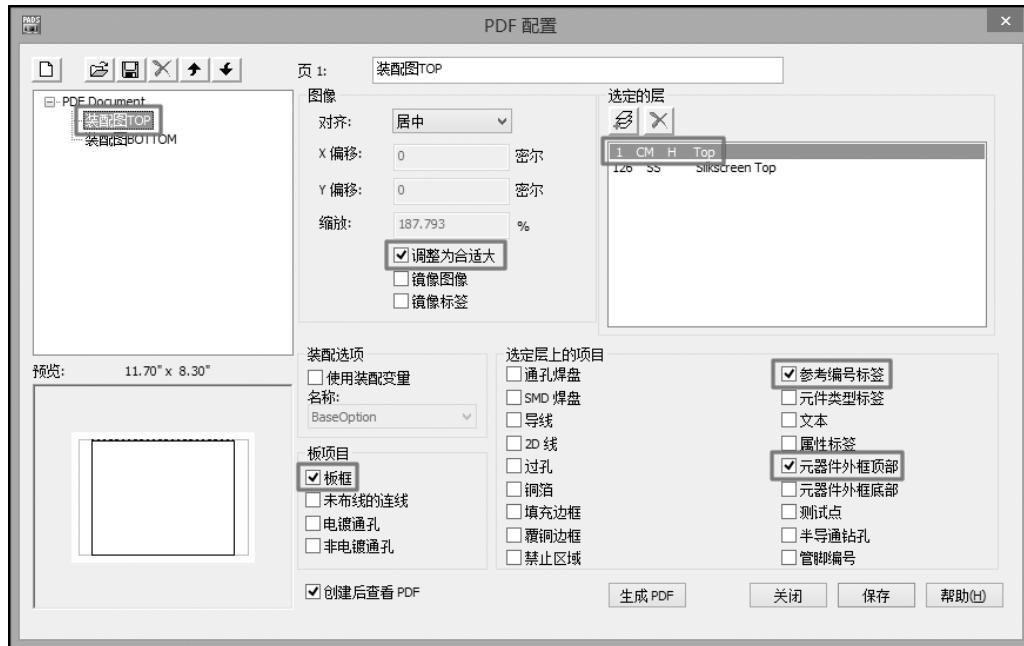

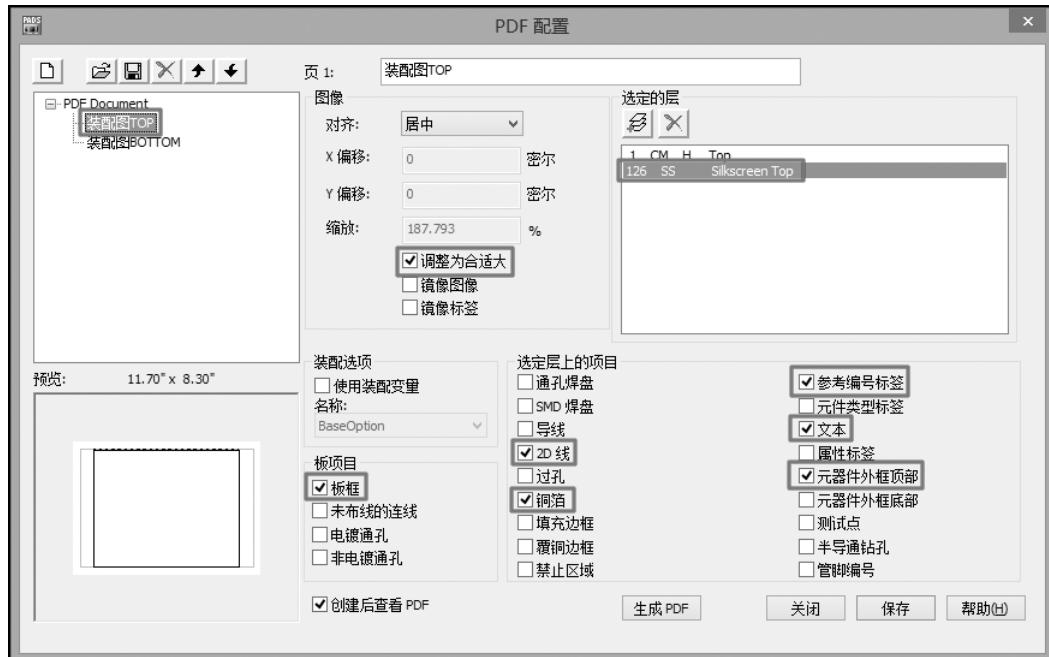

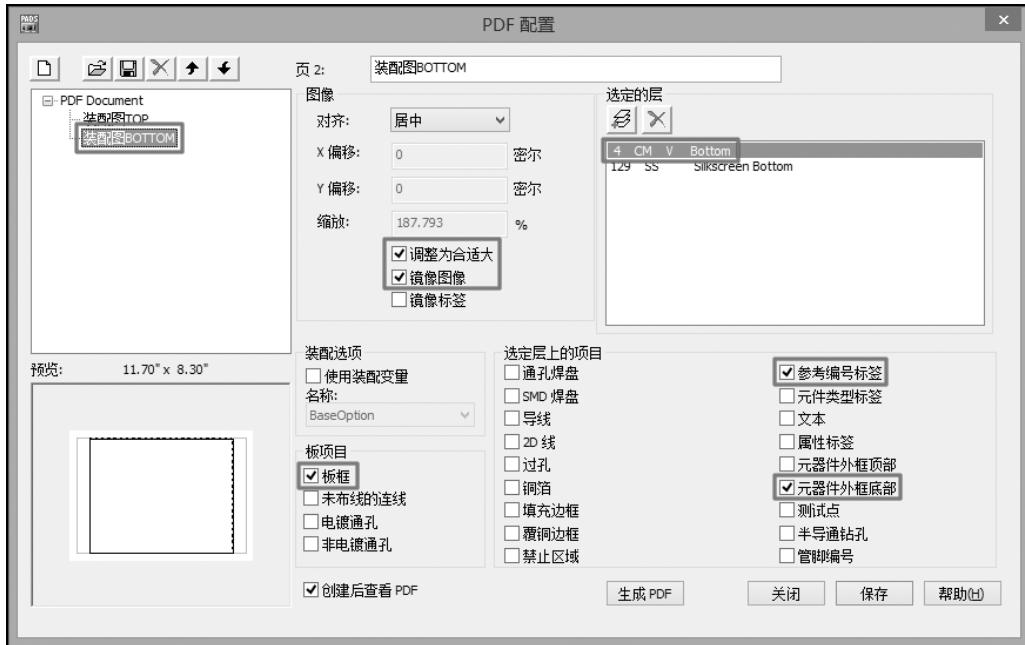

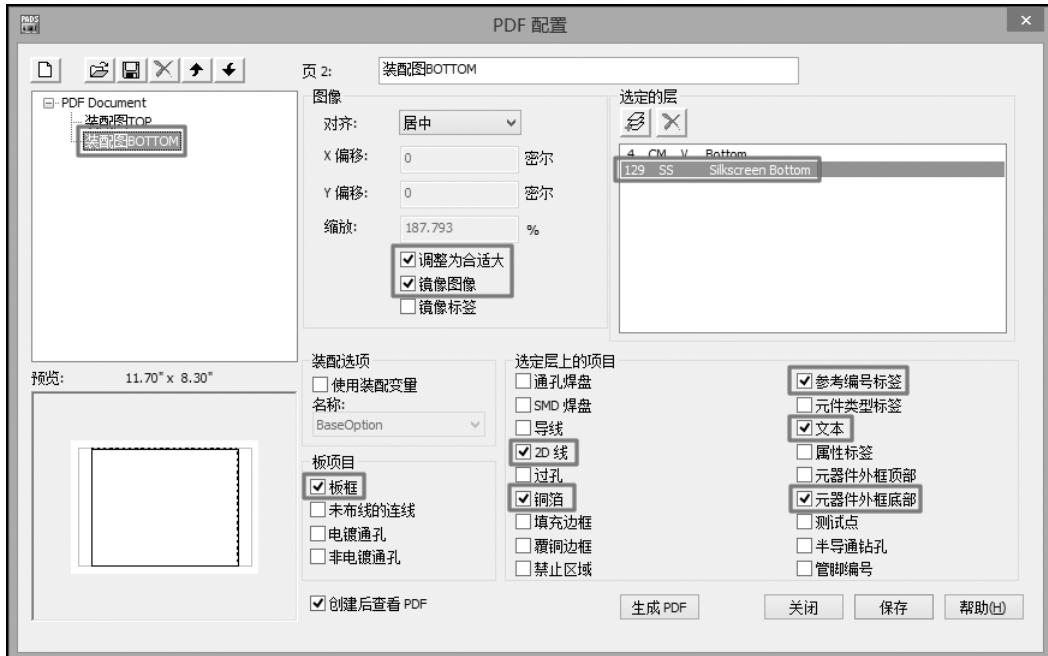

图 6-18 添加圆弧走线

PADS Router 软件走线时添加圆弧的方法也类似。

## 6.8 走线完成后转换为弧线

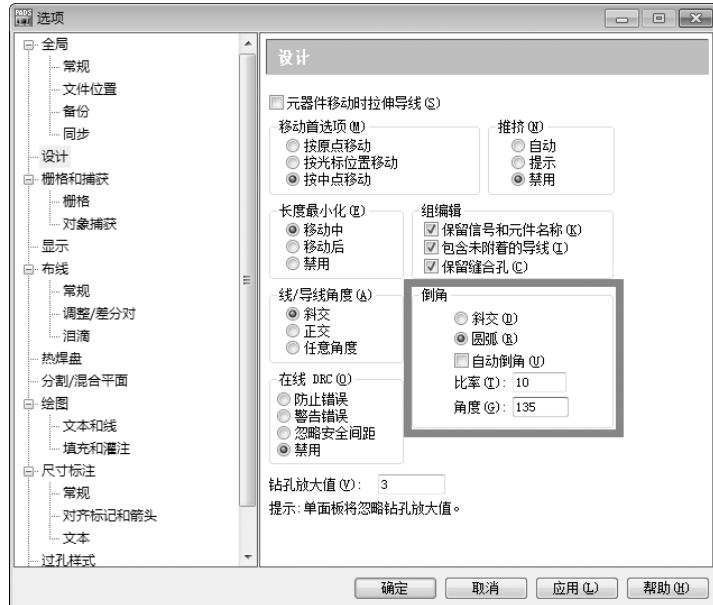

### 1. PADS Layout 软件

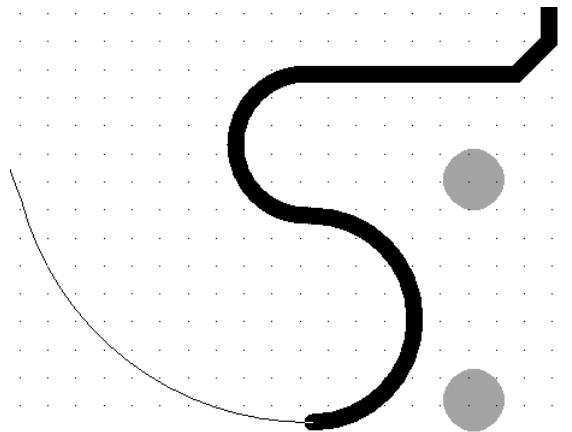

(1) 可以先进行倒角设置，执行菜单命令【工具】-【选项】，在“设计”选项的“倒角”中，选择“圆弧”，可以对圆弧倒角的比率和角度进行编辑，如图 6-19 所示。

图 6-19 倒角设置

- (2) 通过筛选条件，选中需要转换为圆弧的拐角。

- (3) 单击鼠标右键，添加倒角，就能得到一个拐角处的弧线处理，如图 6-20 所示。

图 6-20 圆弧走线

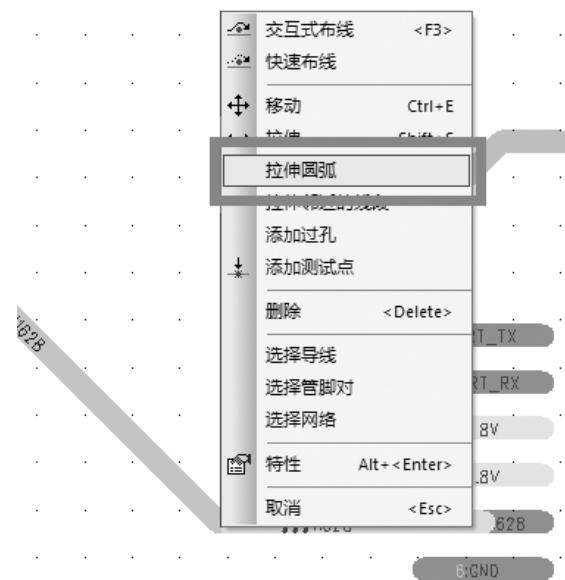

### 2. PADS Router 软件

#### 1) 方法一

选中 46°拐角，单击鼠标右键，执行菜单命令【拉伸圆弧】，如图 6-21 所示。

## 2) 方法二

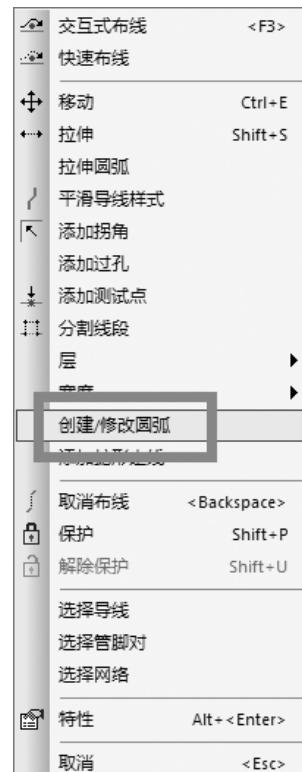

选中单根导线，单击鼠标右键选择“创建/修改圆弧”，如图 6-22 所示。

图 6-21 拉伸圆弧

图 6-22 创建/修改圆弧

## 6.9 走线时选择过孔

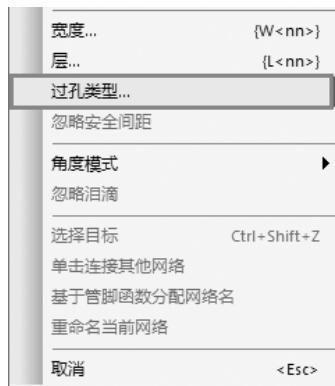

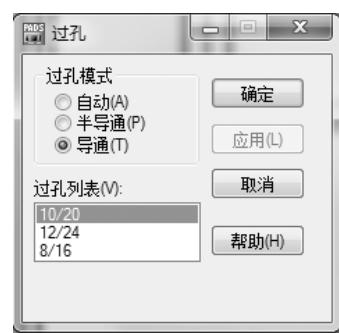

在走线状态下单击鼠标右键，执行菜单命令【过孔类型】，如图 6-23 所示。

在过孔列表中选用过孔，在之后的过孔中都会默认采用选用的过孔，如图 6-24 所示。

图 6-23 进入过孔类型

图 6-24 选择过孔

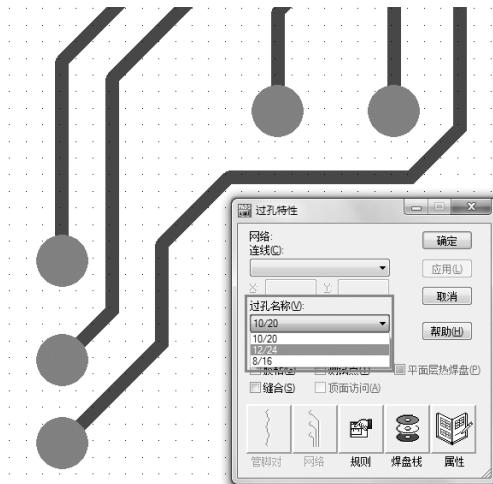

## 6.10 走线结束后更改过孔

选中需要更改的过孔，单击鼠标右键，进入特性，在过孔名称中选用合适的过孔，如图 6-25 所示。

图 6-25 更改过孔

## 6.11 过孔删除不了

过孔删除不了的原因如果不是导线受到保护，就是过孔胶粘了。

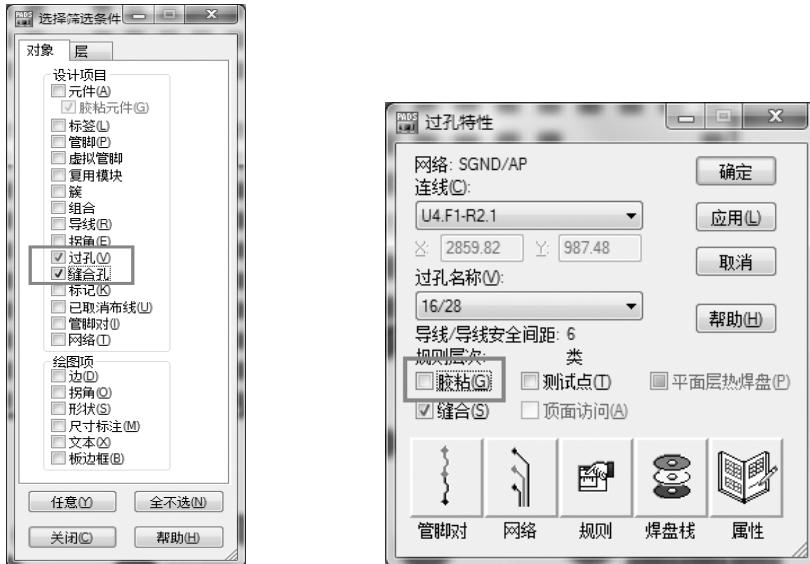

单击鼠标右键，执行菜单命令【筛选条件】，勾选“过孔”和“缝合孔”，如图 6-26 所示。选中需要删除的过孔，单击鼠标右键，进入特性，取消勾选“胶粘”，如图 6-27 所示。

图 6-26 勾选“过孔”和“缝合孔”

图 6-27 取消勾选“胶粘”

确定后，再次选中，按下【Delete】键后就能删除。

## 6.12 虚拟过孔

虚拟过孔生产出来跟真的过孔是一样的，主要使用在 T 点，方便 CPU 与 T 点间做等长。

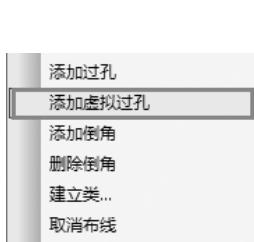

单击鼠标右键，执行菜单命令【选择网络】，选中需要添加虚拟过孔的网络。再次单击鼠标右键。执行菜单命令【添加虚拟过孔】，如图 6-28 所示。

虚拟过孔的中心有两个三角形，如图 6-29 所示。

图 6-28 添加虚拟过孔

图 6-29 虚拟过孔

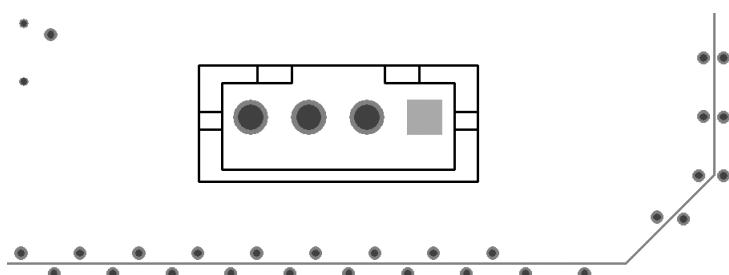

## 6.13 自动增加过孔

PCB 设计后期，在板上空白区域增加地过孔，能降低地线阻抗，增强电源或信号的回流能力，使不同层的地更紧密结合在一起。

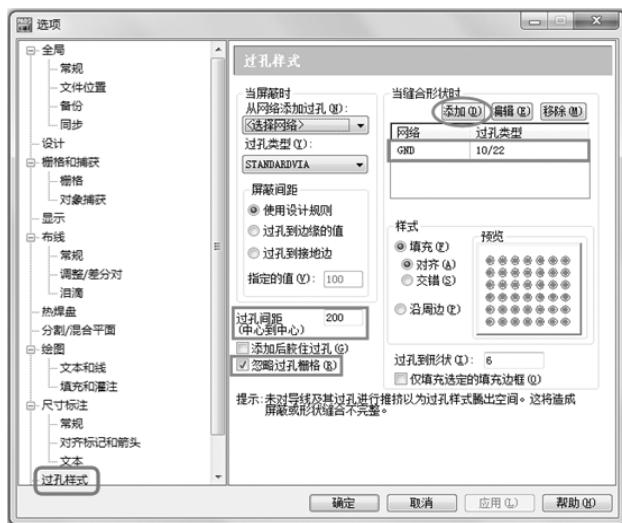

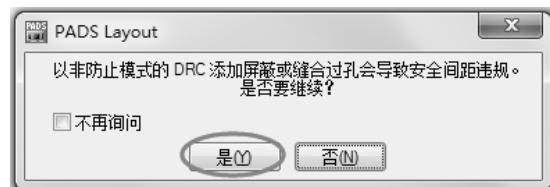

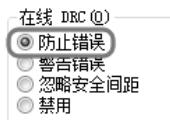

输入无模命令“DRP”，在线 DRC 自动设置为“防止错误”，如图 6-30 所示。

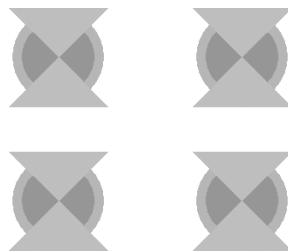

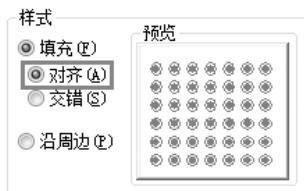

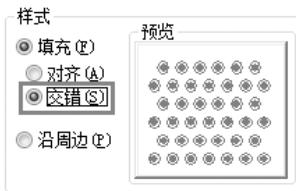

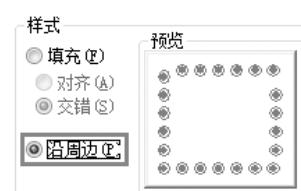

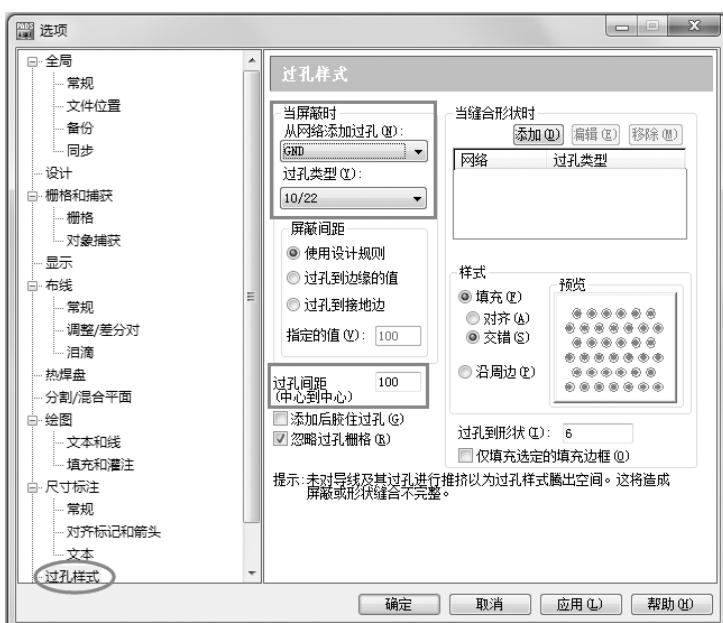

执行菜单命令【工具】-【选项】，选择“过孔样式”选项，在“当缝合形状”时单击【添加】按钮，添加需要自动加过孔的网络及使用的过孔；

过孔间距指每隔多远放置一个过孔，勾选“忽略过孔栅格”，如图 6-31 所示。

图 6-31 自动添加过孔设置

自动添加过孔的三种样式，根据实际需要进行选择，如图 6-32、图 6-33 和图 6-34 所示。

图 6-32 对齐

图 6-33 交错

图 6-34 沿周边

设置完成后，单击【确定】按钮。

对 PCB 进行灌铜后，单击鼠标右键执行菜单命令【选择形状】。

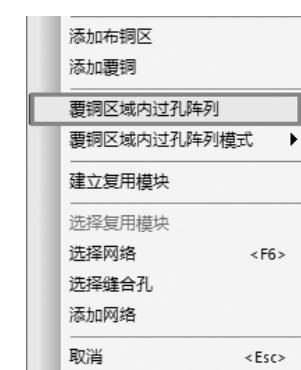

选中地平面（形状），单击鼠标右键，执行菜单命令【覆铜区域内过孔阵列】，如图 6-35 所示。

图 6-35 覆铜区域内过孔阵列

图 6-36 确认继续

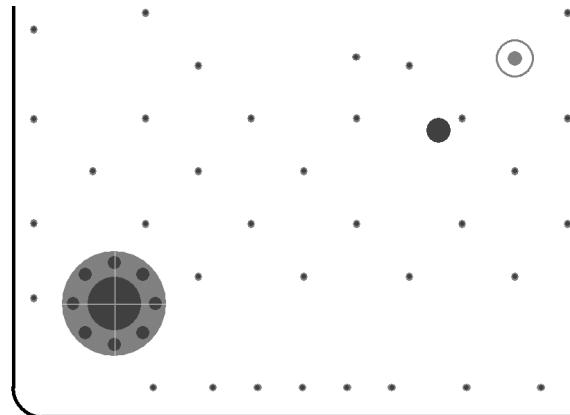

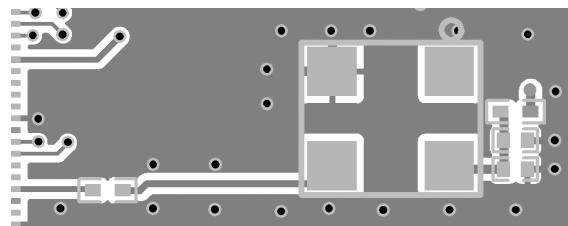

整板将自动在空白处添加地过孔，新增加的孔不会造成安全间距违规错误，如图 6-37 所示。

图 6-37 空白处添加过孔

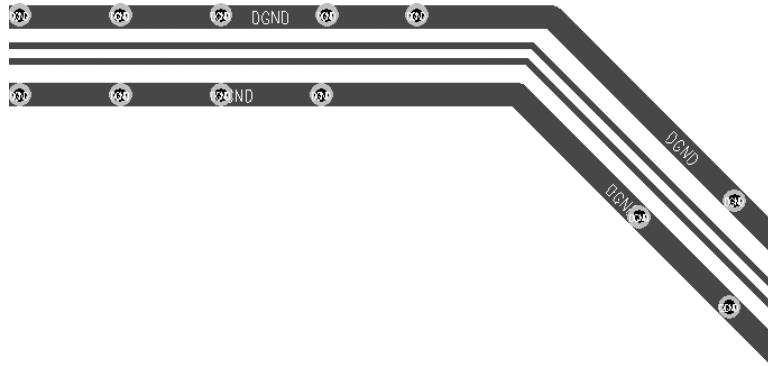

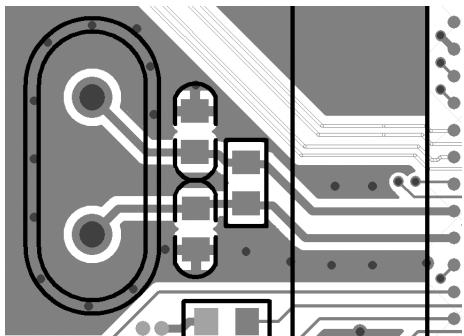

## 6.14 自动包地

输入无模命令“DRP”，在线 DRC 自动设置为防止错误，如图 6-38 所示。

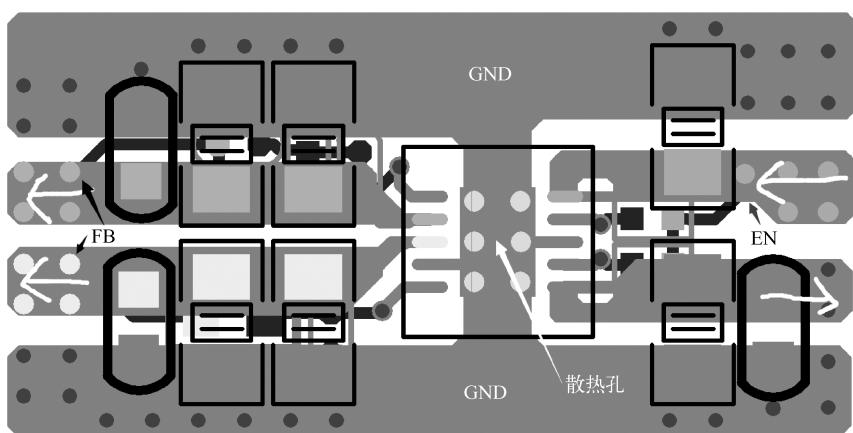

执行菜单命令【工具】-【选项】，选择“过孔样式”选项，在“当屏蔽时”从网络添加过孔处选择“地网络”，过孔类型中选择使用的过孔，如图 6-39 所示。

当屏蔽时指被包时，从 GND 网络添加 10/22mil 的孔。

设置完成后，单击【确定】按钮。

图 6-38 打开在线 DRC

图 6-39 设置屏蔽过孔

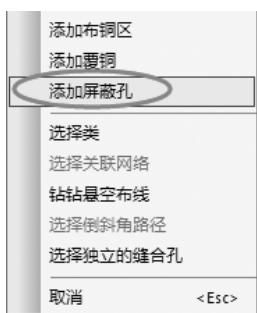

单击鼠标右键，执行菜单命令【网络】，选中需要包地的网络。

单击鼠标右键，执行菜单命令【添加屏蔽孔】，如图 6-40 所示。

被选择的网络将自动添加屏蔽孔，如图 6-41 所示。

图 6-40 添加屏蔽孔

图 6-41 自动添加屏蔽孔

## 6.15 走线立体包地

对于比较重要的信号线常使用立体包地避免其他网络的干扰，立体包地是指在被保护线旁边走地线，并且每隔一段距离加地孔，最好相邻层是地平面，如图 6-42 所示。

图 6-42 立体包地处理

## 6.16 调整走线或形状时移动和拉伸命令的区别

移动命令有些时候会使角度发生变化，出现一些不规则的现象。例如，歪线（锯齿线）。拉伸命令不会改变角度，但存在局限性。

究竟使用哪种操作更合适，需根据具体情况来确定。

歪线如图 6-43 所示。

图 6-43 歪线

## 6.17 走线如何自动保护

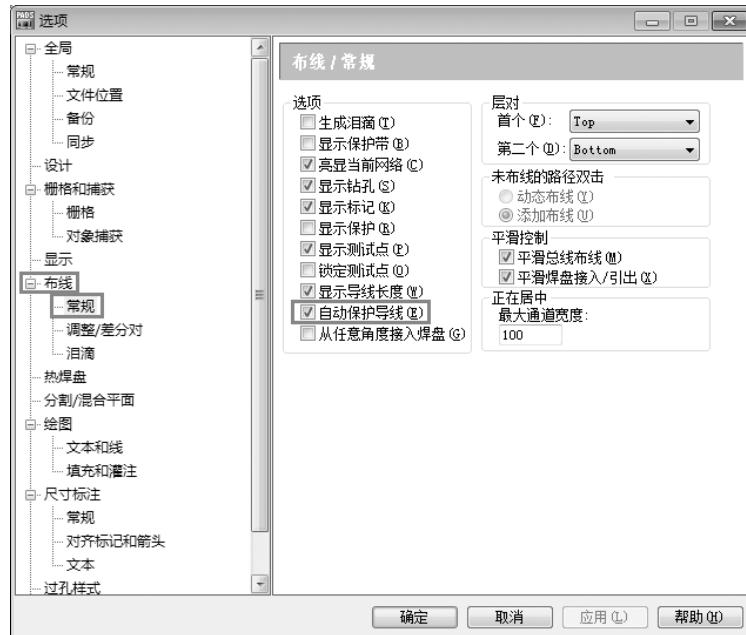

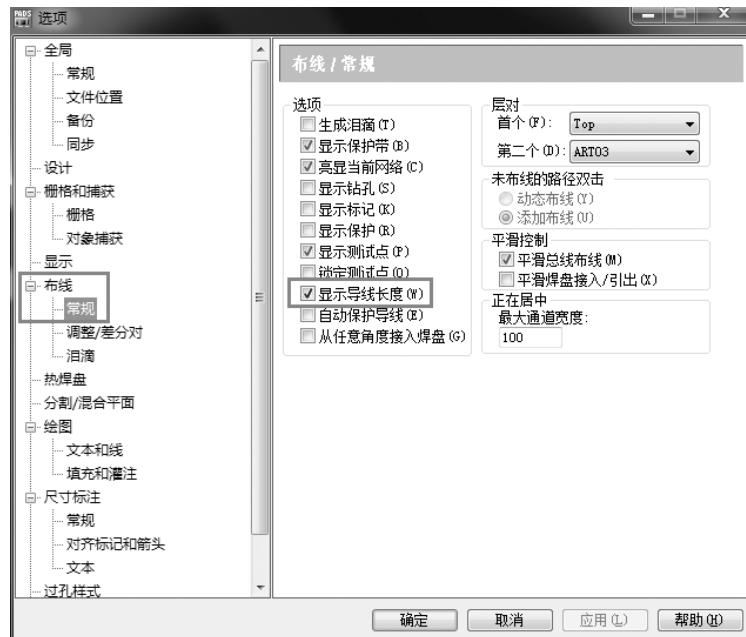

在 Layout 中，执行菜单命令【工具】-【选项】，在弹出的对话框中选择“布线”选项中的“常规”，勾选“自动保护导线”，如图 6-44 所示。

图 6-44 自动保护导线

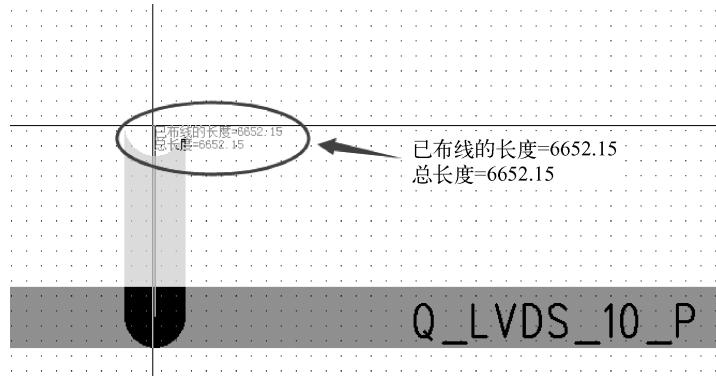

## 6.18 显示走线长度

执行菜单命令【工具】-【选项】，选择“布线”选项中的“常规”，勾选“显示导线长度”，如图 6-45 所示。

图 6-45 显示导线长度

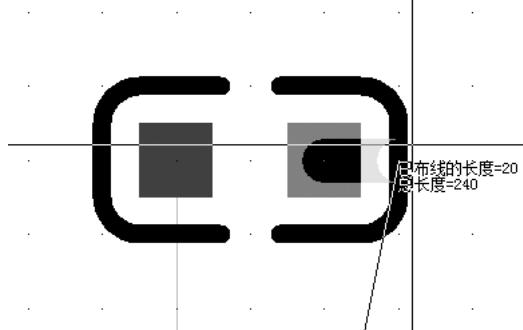

显示效果如图 6-46 所示。

图 6-46 显示导线长度

## 6.19 回路布线

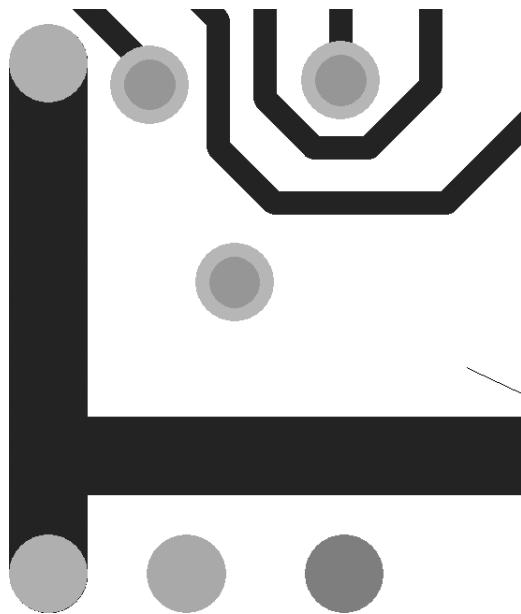

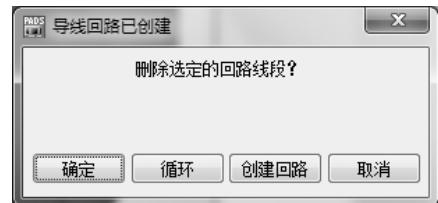

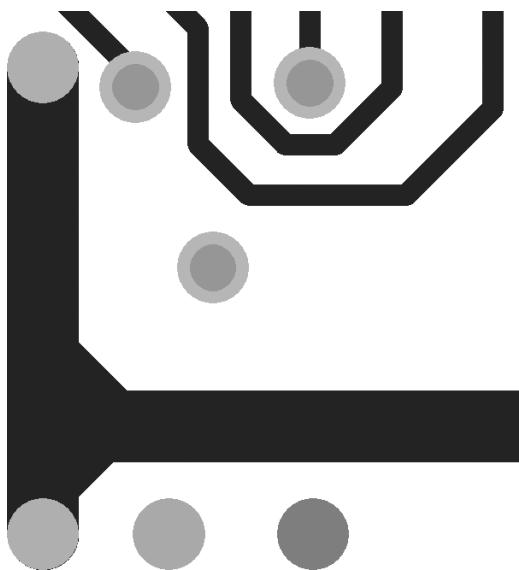

走线时出现直角或锐角，如图 6-47 所示。

常把导线再连一段去优化，当连接到合适位置时，某一位置的线又断开了，也或者出现如图 6-48 所示的窗口。

图 6-47 直角走线

图 6-48 删除选定的回路线段

可直接采用回路布线，选中焊盘、导线或过孔，单击鼠标右键，执行菜单命令【回路布线】，如图 6-49 所示。

回路布线后如图 6-50 所示。

图 6-49 回路布线

图 6-50 回路布线后

## 6.20 无模命令“O”和“T”的区别

无模命令“O”是以图像边框模式进行显示的，在添加散热过孔和检查“碎线头”时经常使用，如图 6-51 所示。

图 6-51 无模命令“O”显示效果

无模命令“T”是以透明图像模式进行显示的，如图 6-52 所示。

图 6-52 无模命令“T”显示效果

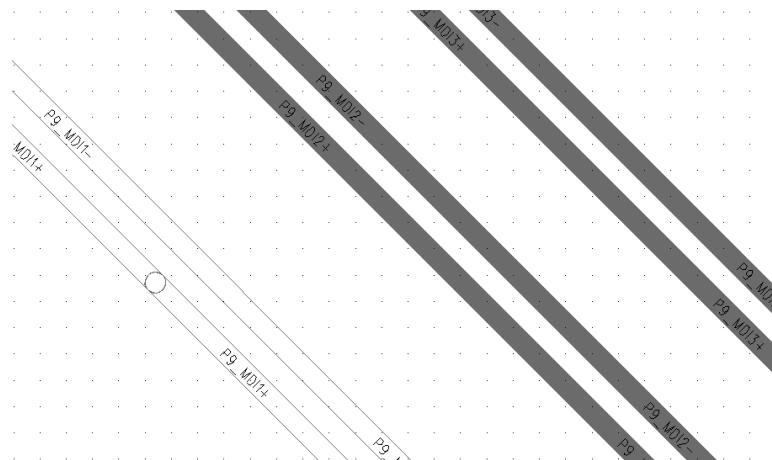

## 6.21 多条平行信号线间的间距如何保持相等

在布线过程将线走在同间距的栅格上，能够控制间距一致，如图 6-53 所示。

也可以在 PADS Router 中布线，开启 DRC 和启动拉线器中的推挤功能，进行保持间距一致，如图 6-54 所示。

图 6-53 利用栅格控制间距

图 6-54 利用 PADS Router 推挤功能

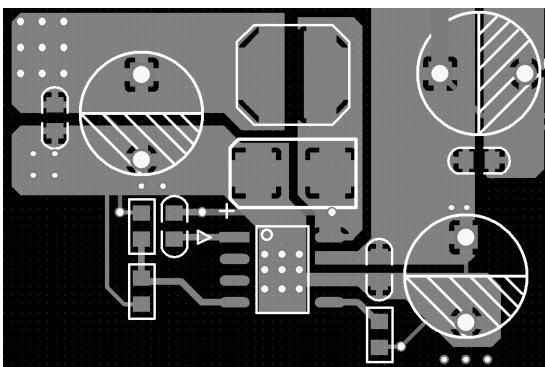

## 6.22 铜箔/覆铜的绘制（后分配网络）

单击绘图工具栏 ，单击铜箔 。此时鼠标光标处出现个“v”，表示进入绘制状态。

单击鼠标右键，有 4 种模式可供选择，如图 6-55 所示。

绘制完成后，弹出“添加绘图”对话框。单击【通过单击分配网络】按钮，单击覆铜的网络，如图 6-56 所示。

图 6-55 绘图的 4 种模式

图 6-56 分配网络

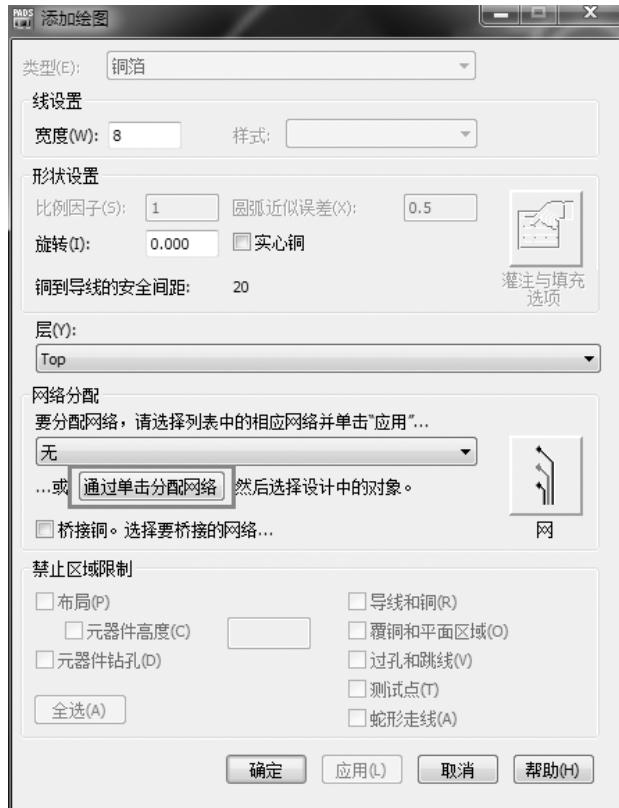

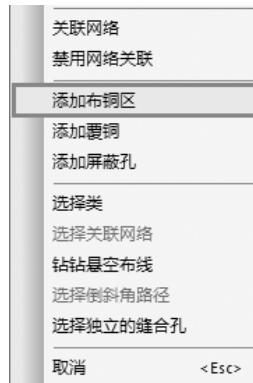

## 6.23 铜箔/覆铜的绘制（先分配网络）

选中需要绘制铜箔的网络后，单击鼠标右键，执行菜单命令【添加布铜区】，如图 6-57 所示。

图 6-57 添加布铜区

绘制铜箔/覆铜完成后自动分配给之前选定的网络。

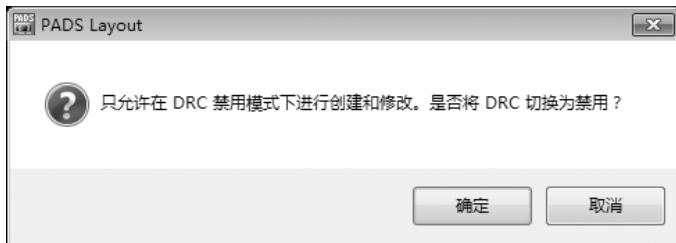

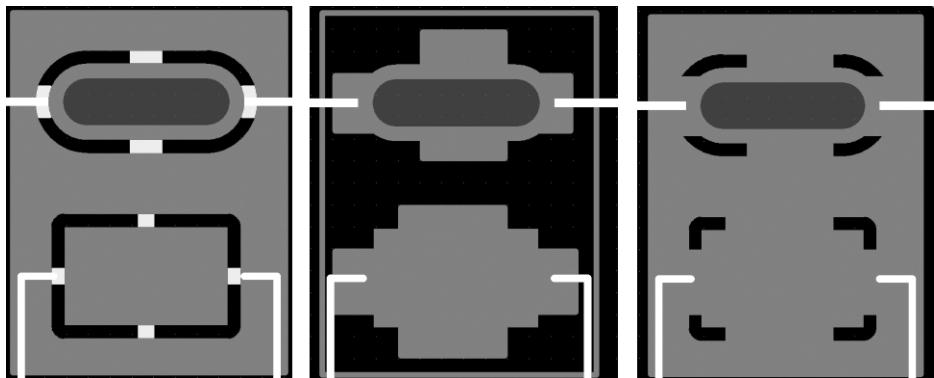

## 6.24 铜箔和覆铜的区别

铜箔和覆铜图标所在的位置如图 6-58 所示。

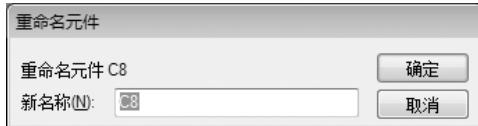

图 6-58 铜箔和覆铜图标

铜箔又称“死铜”，按照绘制的范围生成铜箔，不会避让其他网络，只能在 DRC 禁用的模式下使用；如果在 DRC 开启的情况下进行绘制铜箔，将弹出如图 6-59 所示的窗口。

图 6-59 是否将 DRC 切换为禁用

铜箔可能会造成短路的情况，不过可以通过设计验证检查出来，如图 6-60 所示为铜箔。

覆铜又称“动态铜”、“活铜”。按照绘制的范围生成一个覆铜框，灌注时将避让其他网络，避免出现安全间距的错误，覆铜灌注后的效果如图 6-61 所示。

图 6-60 铜箔

图 6-61 覆铜灌注后

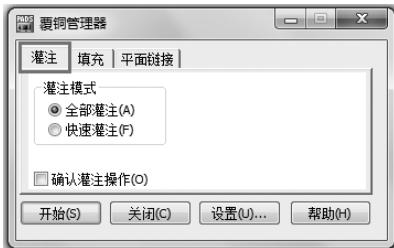

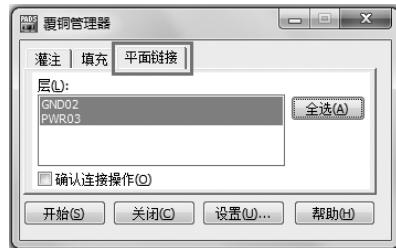

## 6.25 灌注、填充、平面连接的区别

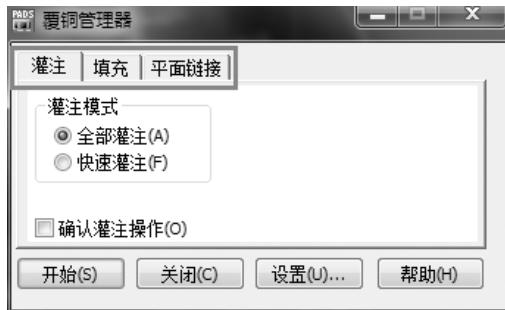

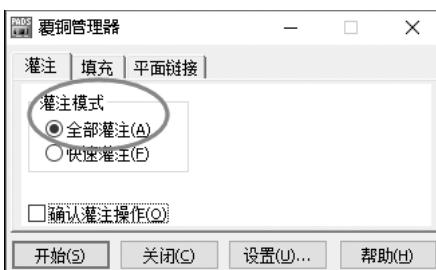

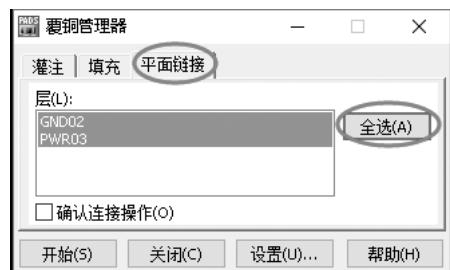

执行菜单命令【工具】-【覆铜管理器】，弹出的对话框如图 6-62 所示。

- (1) “灌注”：无平面的覆铜区域会根据规则设置和目前 PCB 情况进行重新灌注。

- (2) “填充”：不重新灌注，会显示出上一次灌注后的铜箔。

- (3) “平面链接”：分割/混合平面会根据规则设置和目前 PCB 情况进行重新灌注。

图 6-62 “覆铜管理器”对话框

单击“灌注”和“平面链接”时会有一定时间的等待软件灌注才能完成，而填充是马上就好。

## 6.26 铜箔加固焊盘

使用覆铜连接的电源引脚，并没有大面积的连接。使用铜箔进行加强，更大面积的连接。如图 6-63 所示。

图 6-63 铜箔加固焊盘

## 6.27 怎样铺网格状的铜皮

设计软板时，使用的是网格铜，这样能延长软板多次折叠的使用寿命。

绘图特性中的线宽小于铺铜栅格的线宽时，查看覆铜线宽如图 6-64 所示，查看铺铜栅格的线宽如图 6-65 所示。

当满足条件时，实心铜会变成网格铜，如图 6-66 所示。

图 6-64 查看覆铜线宽

图 6-65 查看铺铜栅格线宽

图 6-66 网格铜

## 6.28 铜箔优化全连接

铜箔全连接会造成生产时“虚焊”、“立碑”和调试返修困难等问题，铜箔全连接如图 6-67 所示。

图 6-67 铜箔链接

空区域可以优化全连接问题，单击“绘图工具栏”中的“铜挖空区域”图标，如图 6-68 所示。

图 6-68 单击“铜挖空区域”图标

在铜箔内绘制矩形框，如图 6-69 所示。

单击鼠标右键，执行菜单命令【形状】，选择这 3 个形状（1 个铜箔和 2 个铜箔挖空区域），可以按下键盘【O】键查看是否已经选中。单击鼠标右键，执行菜单命令【合并】，如图 6-70 所示。

图 6-69 绘制铜挖空的矩形框

图 6-70 合并

将铜箔和铜挖空区域合并后如图 6-71 和图 6-72 所示。

图 6-71 优化全连接 A

图 6-72 优化全连接 B

## 6.29 隐藏灌注后的覆铜或连接后的平面

对 PCB 进行填充和灌注后，可以通过无模命令对铜进行显示和不显示。

对于无平面的层输入无模命令“PO”，以覆铜边框或灌注后的覆铜相互切换进行显示；对于分割/混合平面层，输入“SPO”，以平面边框显示，再次输入“SPD”，以连接平面显示。

图 6-73 为以覆铜边框显示，图 6-74 为灌注后的覆铜显示。

图 6-73 以覆铜边框显示

图 6-74 灌注后的覆铜显示

### 6.30 灌注后内部覆铜框覆不了铜

两个覆铜框之间有相切或包裹的情况时，要修改它的优先级来保证都能灌上铜。由于优先级都采用默认设置，导致有网络没灌注，如图 6-75 所示。

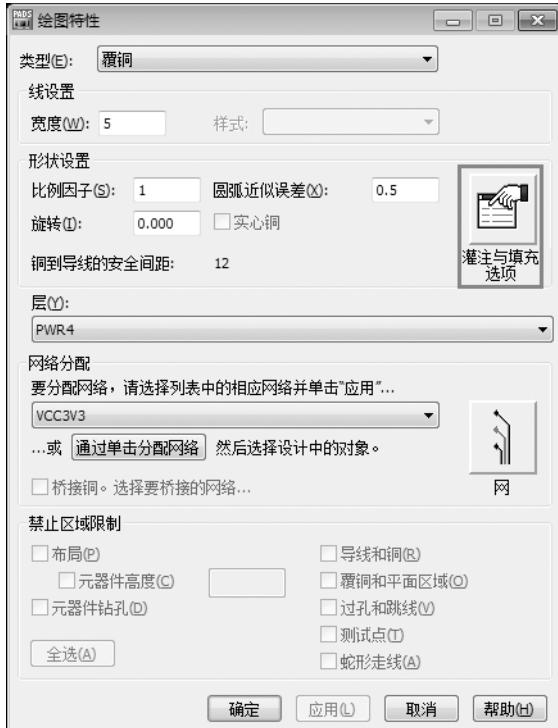

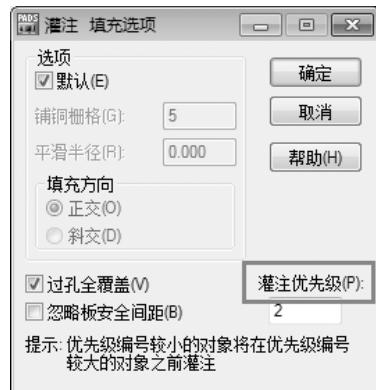

覆铜框的优先级默认是“0”，单击鼠标右键，执行菜单命令【选择形状】，选中外圈的覆铜框，单击鼠标右键，执行菜单命令【特性】，弹出的对话框如图 6-76 所示。

图 6-75 覆铜未灌注

在弹出的“绘图特性”对话框中单击“灌注与填充选项”，修改“灌注优先级”中的参数即可，如图 6-77 所示。

图 6-76 进入灌注与填充选项

图 6-77 修改灌注优先级

### 6.31 单个绘图形状的相互转换

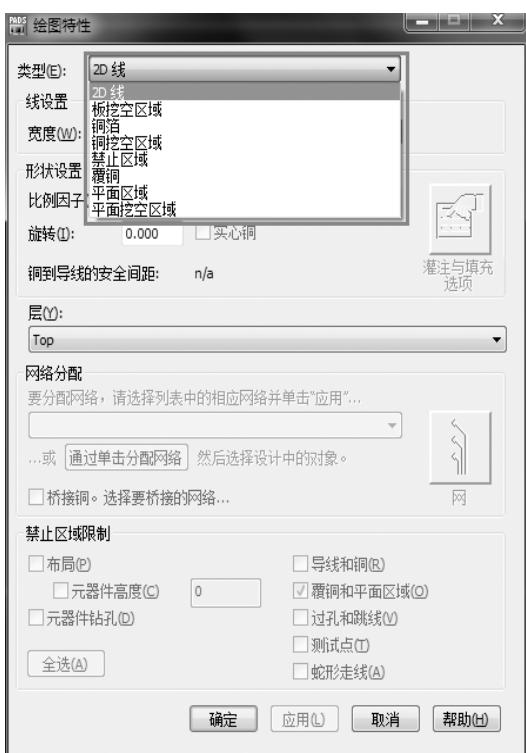

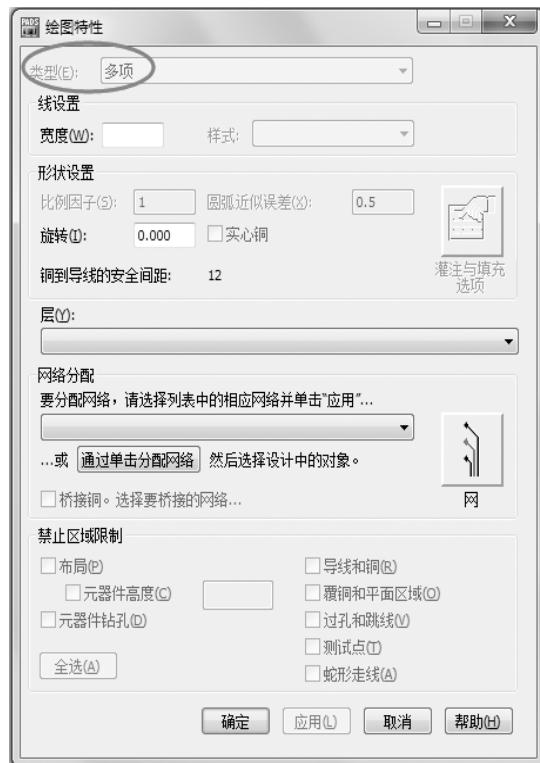

选中单个多边形绘图形状，进入其特性，在类型标签的下拉菜单中可以进行转化，如图 6-78 所示。

不支持多个的转化，如果是多个，那类型标签中则显示为多项，无下拉菜单，如图 6-79 所示。

图 6-78 多边形绘图不同类型的转换

图 6-79 多个绘图类型为多项

### 6.32 如何将已经画好的线段更改为铜箔

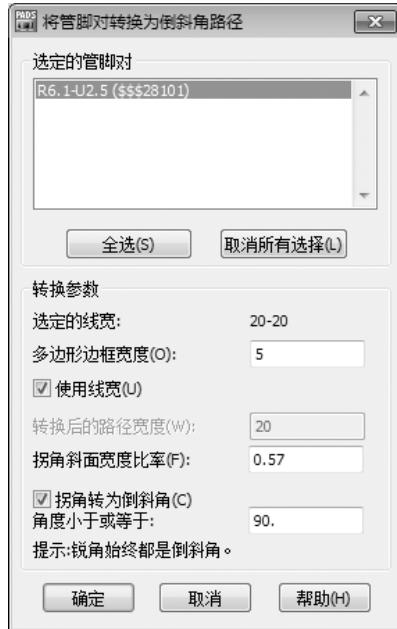

选中“网络/管脚”对，单击鼠标右键，执行菜单命令【转换为倒斜角路径】，在弹出的对话框中修改参数，单击【确定】按钮将转换完成，如图 6-80 所示。

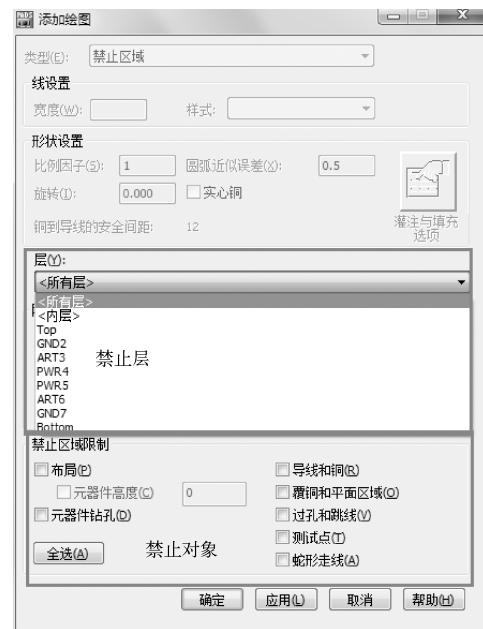

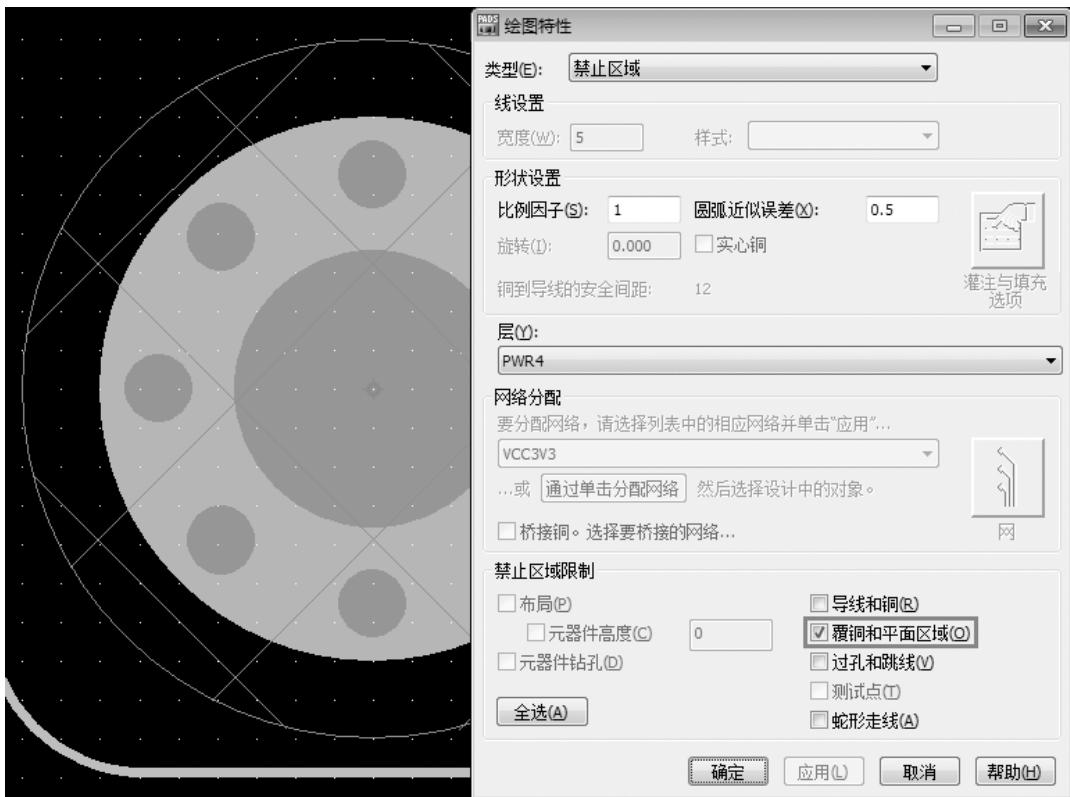

### 6.33 绘制禁止区域

禁布区是为了限制某些区域的某些属性，设计时避开禁止区域进行设计。

在绘图工具栏上选择禁止区域图标 ，绘制完成后弹出“添加绘图”对话框，根据实际需要进行勾选，如图 6-81 所示。

图 6-80 导线转换为铜箔

图 6-81 禁止区域选项

### 6.34 定位孔覆铜怎么避开

绘制禁止覆铜区域，让敷铜离螺丝孔有 1mm 的距离。

选中螺丝孔，使用无模命令“SO”，将原点设置在螺丝孔的正中心，如图 6-82 所示。

图 6-82 选中状态输入无模命令

选中元器件，进入螺丝孔的封装编辑器，如图 6-83 所示。

选择螺丝孔的焊盘，单击鼠标右键，进入“管脚的焊盘栈特性”对话框，如图 6-84 所示。

图 6-83 编辑封装

图 6-84 查看螺丝孔焊盘特性

从螺丝孔特性中能够算出螺丝孔半径为 140mil，要绘制 1mm 的禁止区域，我们直接将栅格设为 160(140+40)，“禁止区域限制”勾选“敷铜和平面区域”，如图 6-85 所示。

图 6-85 绘制禁止区域

## 6.35 复用功能

不同设计项目之间会有拓扑和封装完全相同的电路，在同一个设计中也有重复的电路（多通道电路），利用复用功能，让设计提高一定的效率。

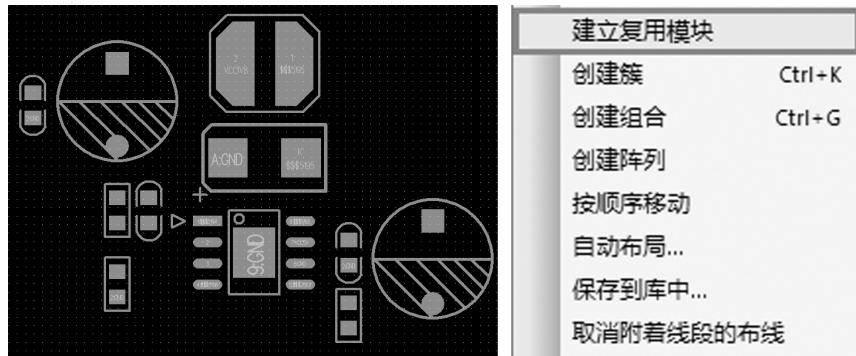

选择需要建立复用的电路，单击鼠标右键，执行菜单命令【建立复用模块】，如图 6-86 所示。

图 6-86 建立复用模块

对复用模块进行命名后单击【确定】保存，如图 6-87 所示。

图 6-87 保存复用模块

要调用复用模块，先选中与复用模块相同的电路，单击“设计工具栏”中“建立相似的复用模块”图标，如图 6-88 所示，选中的将变成与复用模块一致的电路。

图 6-88 建立相似的复用模块

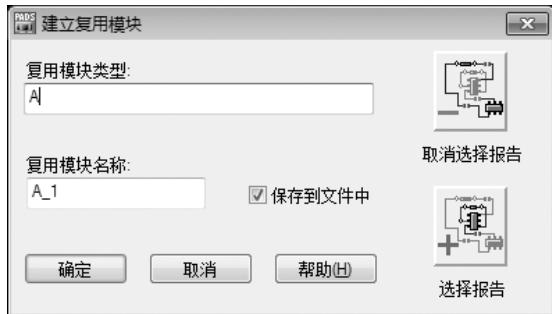

## 6.36 怎么进入 ECO 功能

ECO 功能可以让用户无须更改原理图就可以直接在 PCB 上增减元器件，修改网络。

为了避免误操作导致网络信息的改变，进入 ECO 功能会先让用户进行确认。

单击“ECO 工具栏”，如图 6-89 所示。

图 6-89 ECO 功能入口

弹出的对话框如图 6-90 所示，单击【确定】按钮，进入 ECO 模式。

图 6-90 “ECO 选项”对话框

### 6.37 在 ECO 功能上如何直接添加网络连接

单击 ECO 功能上的“添加连线”图标，如图 6-91 所示。

单击空的引脚后，移开会有飞线，把飞线连接至需要的网络焊盘上单击鼠标左键，编辑弹出的对话框，空的引脚将赋予网络，如图 6-92 所示。

图 6-91 ECO 添加连线

图 6-92 定义网络名

### 6.38 在 ECO 功能上如何直接添加元器件

单击 ECO 功能上的“添加元器件”图标，如图 6-93 所示。

图 6-93 ECO 添加元器件

“从库中获取元件类型”对话框的“项目”标签中，输入关键字进行搜索，找到需要的

元器件后单击【添加】按钮，如图 6-94 所示。

图 6-94 添加元器件

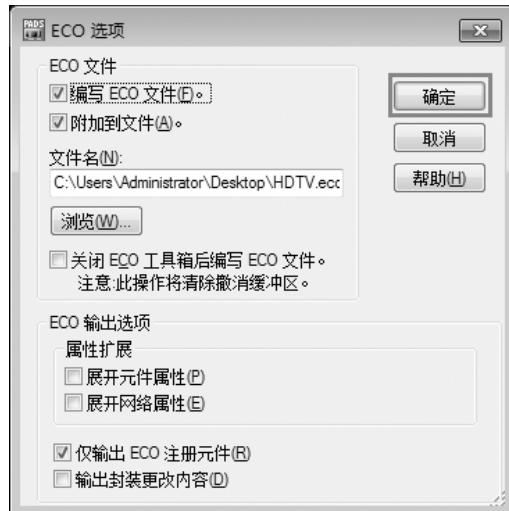

### 6.39 在 ECO 功能上如何直接重命名网络

单击 ECO 功能上的“重命名网络”图标，如图 6-95 所示。

图 6-95 ECO 重命名网络

选中需要重命名的网络，将出现“重命名网络”对话框，输入新的网络名，如图 6-96 所示。

图 6-96 重命名网络

### 6.40 在 ECO 功能上如何直接重命名元器件

单击 ECO 功能上的“添加元器件”图标，如图 6-97 所示。

图 6-97 ECO 重命名元器件

选中需要重命名的元器件，将出现“重命名元件”对话框，输入新的元器件名称，如图 6-98 所示。

图 6-98 重命名元器件

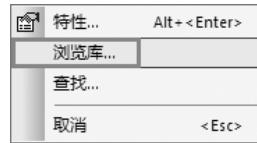

## 6.41 在 ECO 功能上如何直接更改元器件

单击 ECO 功能上的“更改元器件”图标，如图 6-99 所示。

选中需要更改的元器件，单击鼠标右键，执行菜单命令【浏览库】，如图 6-100 所示。

图 6-99 更改元器件

图 6-100 浏览库

在库中查找需要更改的元器件，单击【替换】按钮，如图 6-101 所示。

图 6-101 更改元器件

## 6.42 在 ECO 功能上如何直接删除

在 ECO 功能上可以删除 3 项，分别是删除连线、删除网络、删除元器件，如图 6-102 所示。

图 6-102 ECO 删除

选中需要删除的元素，按下键盘上的【Delete】键将删除。

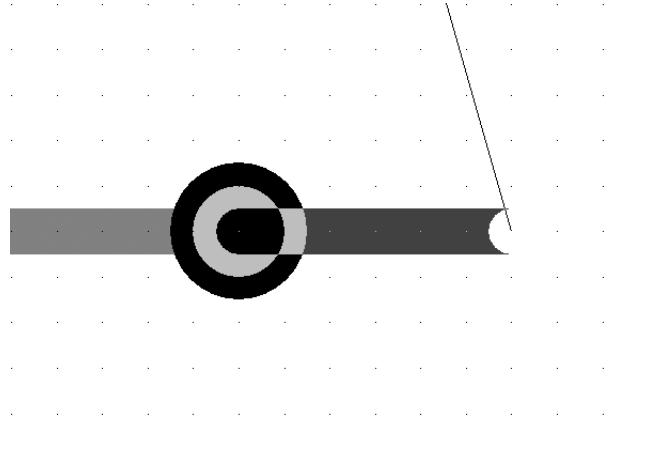

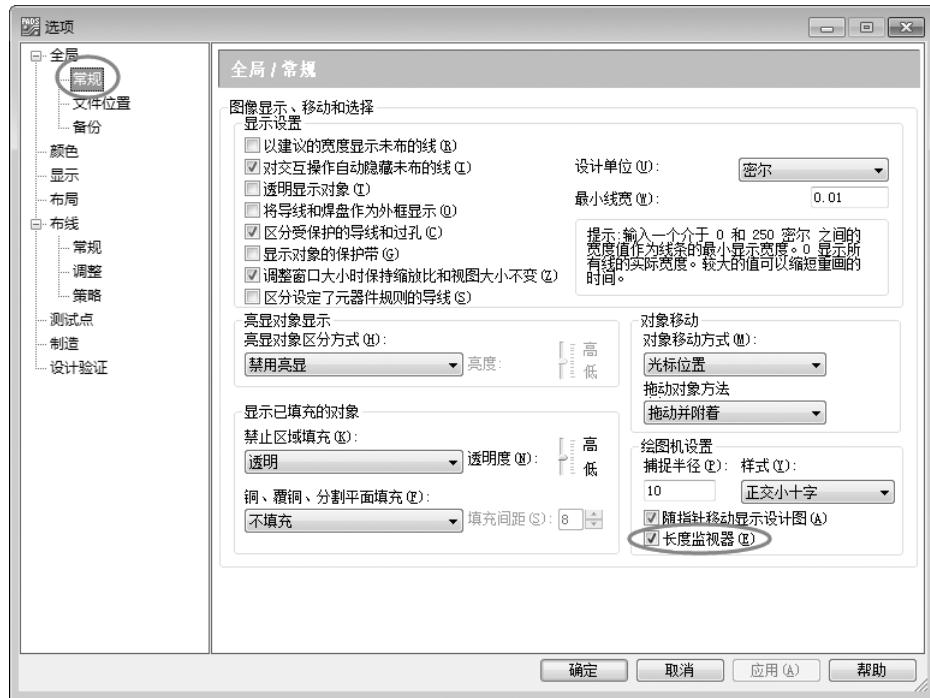

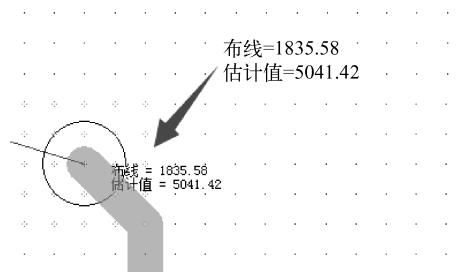

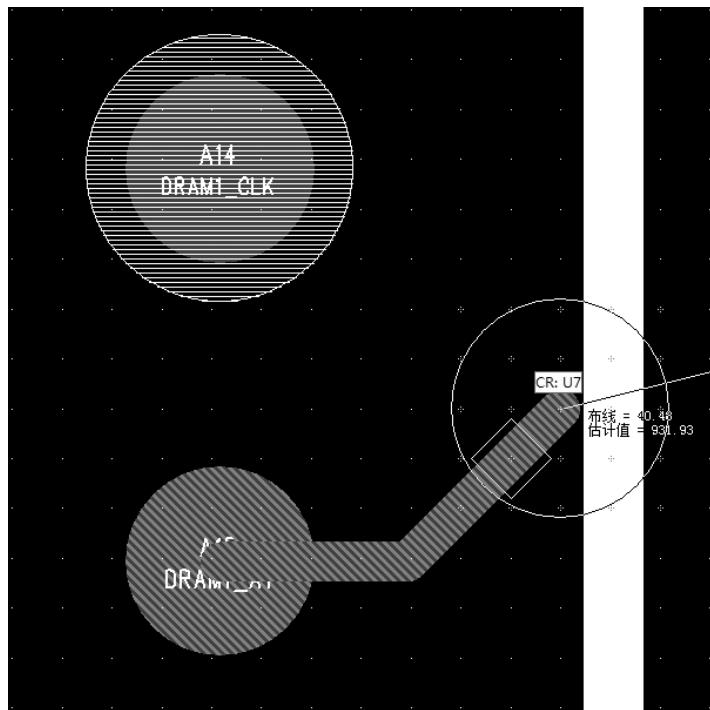

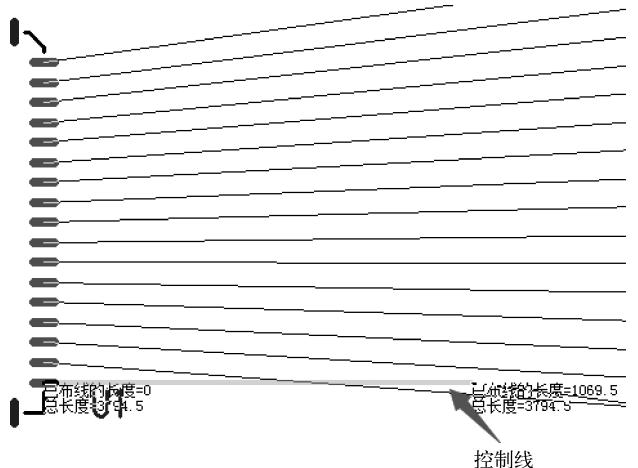

## 6.43 PADS Router 显示走线长度

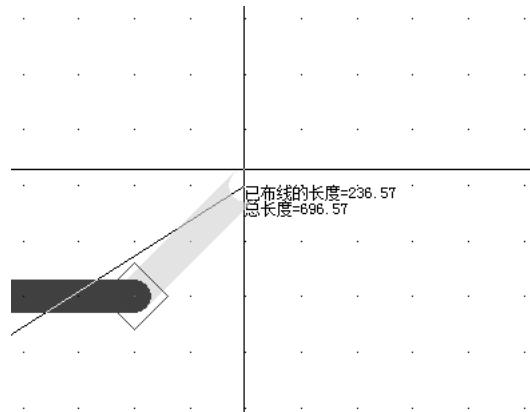

执行菜单命令【工具】-【选项】，在“全局”选项中选择“常规”，勾选“长度监视器”，如图 6-103 所示。

图 6-103 长度监视器

在走线时，鼠标光标下将显示长度。布线长度指从引脚拉线的长度，估计值为整个网络用导线连接的估计长度，如图 6-104 所示。

图 6-104 显示走线长度

## 6.44 区分受保护的导线和过孔

执行菜单命令【工具】-【选项】，在“常规”选项中勾选“区分受保护的导线和过孔”，如图 6-105 所示。

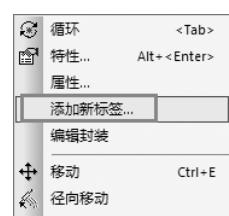

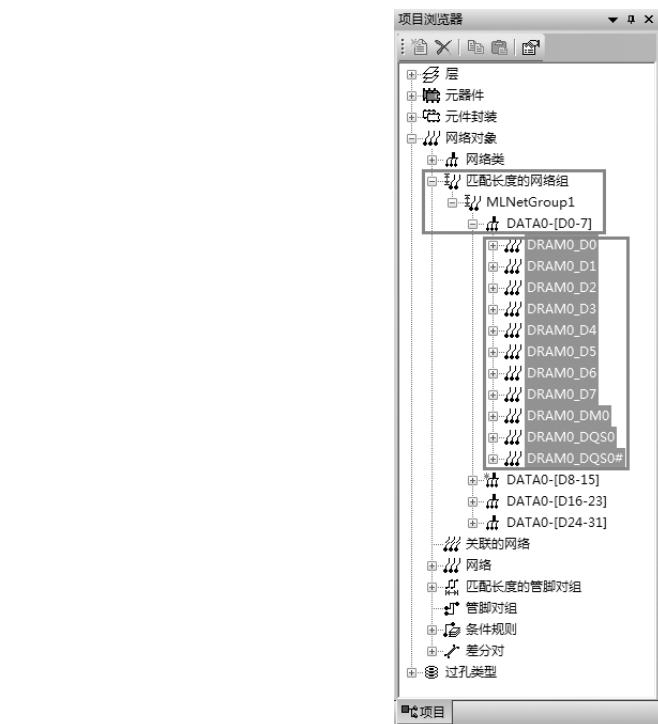

图 6-105 区分受保护的导线和过孔

被保护的导线和过孔将透明，中心为空心，如图 6-106 所示。

图 6-106 保护和未保护的区别

## 6.45 没有保护带显示

PADS Router 里面的保护带在设计 PCB 时做预估非常重要，保护带不显示的原因是没有勾选“显示对象的保护带”，如图 6-107 所示。

图 6-107 勾选“显示对象的保护带”

如果背景颜色和保护带颜色是一样的，保护带将不明显，保护带的颜色推荐使用白色。

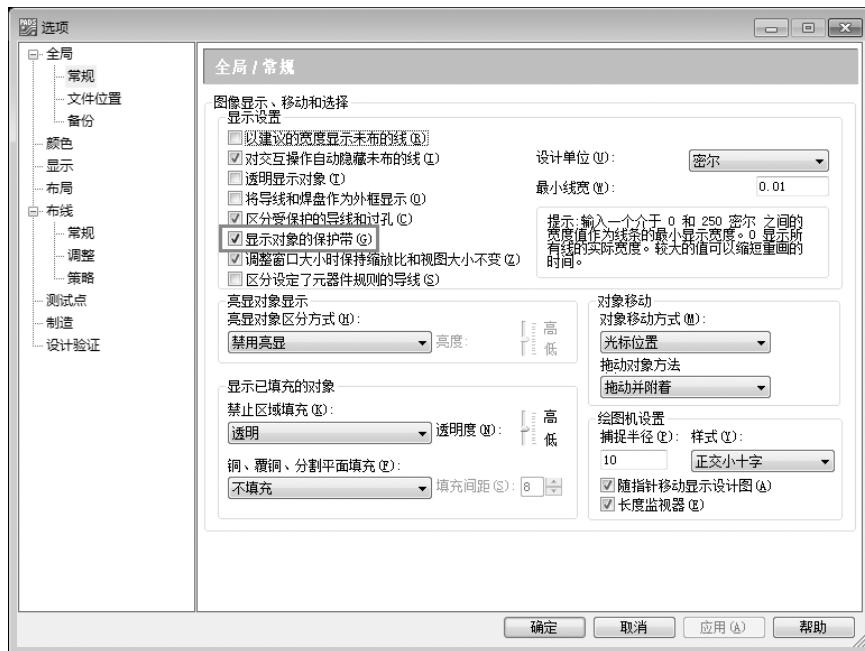

## 6.46 保护带不明显

在 Router 里，默认的保护带的颜色为黑色，设计时默认背景也是黑色，改变保护带的颜色，更便于我们布线时做规划。

执行菜单命令【工具】-【选项】，在“颜色”选项中，在“颜色选择”标签上选中白色后单击保护带，保护带颜色修改为白色，如图 6-108 所示。

图 6-108 修改保护带颜色

白色保护带显示效果如图 6-109 所示。

图 6-109 白色保护带

### 6.47 BGA 封装如何设置才能自动扇出

自动扇出只能在 Router 中使用，执行菜单命令【编辑】-【特性】，“栅格”标签页中取消全部勾选，如图 6-110 所示。

图 6-110 不捕获栅格

“扇出”标签页中只勾选“平面网络”和“信号网络”，如图 6-111 所示。

图 6-111 扇出设置

## 6.48 PADS Router 中走差分线时相同网络连不上

在 Router 中，PADS Router 中走差分线时相同网络连不上，这属于软件 BUG，先暂定走线，切换至 Layout 接通后，再切换 Router 进行优化。

## 6.49 什么时候需要使用关联网络

关联网络是将元器件两端的网络关联起来，变成“同一网络”，对于有等长要求的网络这一功能能够体现出强大的功能。

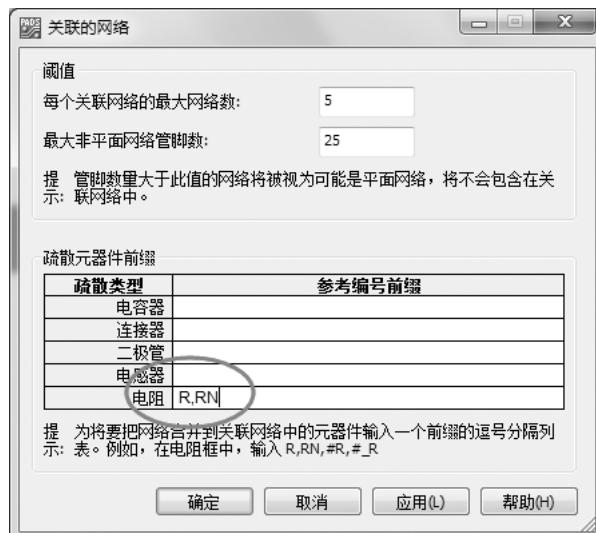

执行菜单命令【设置】-【关联的网络】，在弹出的对话框中，“疏散元器件前缀”中的电阻输入“R,RN”（根据元器件命名的前缀确定输入的参数），如图 6-112 所示，单击【确定】按钮。

图 6-112 关联网络设置

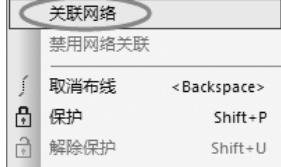

单击鼠标右键，执行菜单命令【选择网络】，选择电阻或排阻两端的需要关联起来的网络，单击鼠标右键，执行菜单命令【关联网络】，如图 6-113 所示。

完成关联网络后，输出窗口会生成一个报告，如图 6-114 所示。

图 6-113 关联网络

图 6-114 输出窗口提示关联网络创建成功

## 6.50 PADS Router 推挤功能

导线推挤，设计中不出现安全间距的错误，根据规则设置推动多根导线。启动该功能有两个必要的条件：

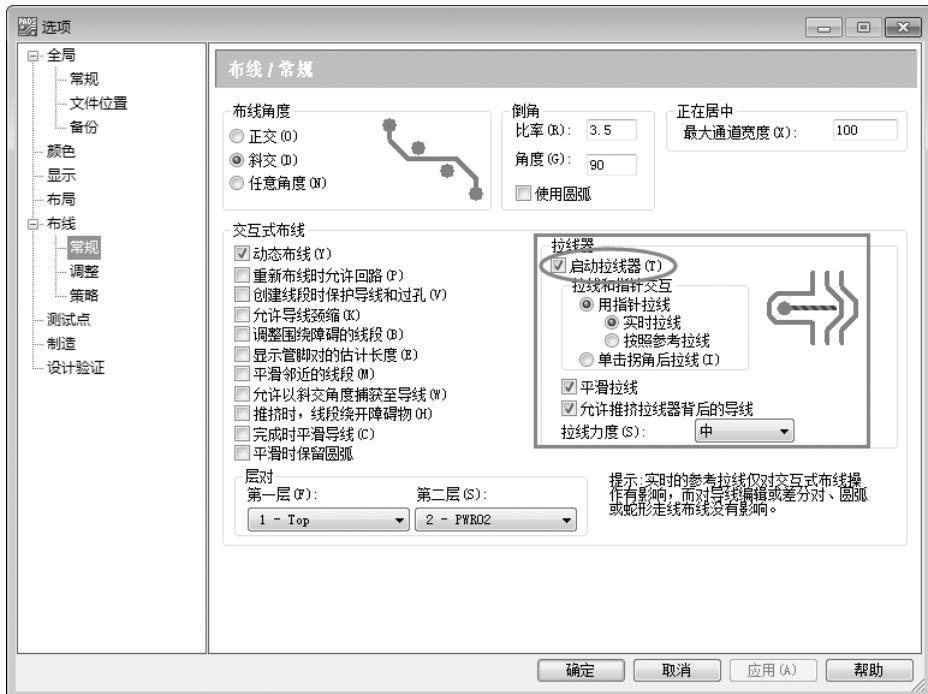

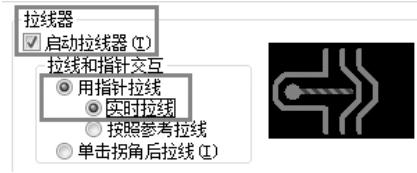

(1) 开启拉线器，其实就是推线器，执行菜单命令【工具】-【选项】，选择“布线”选项中的“常规”，“拉线器”上的推荐设置如图 6-115 所示。

图 6-115 拉线器推荐设置

(2) 开启 DRC 安全间距，所有网络将按照规则设置保持距离，如图 6-116 所示。使用推挤时，拉线与指针交互建议设置如图 6-117 所示。

图 6-116 DRC 设置

图 6-117 拉线与指针交互设置

设置完成后，如果还不能推挤，可能存在的原因是：①这条导线在推挤之前就存在的安全间距错误软件没能优化其安全间距错误；②没有推挤的空间。

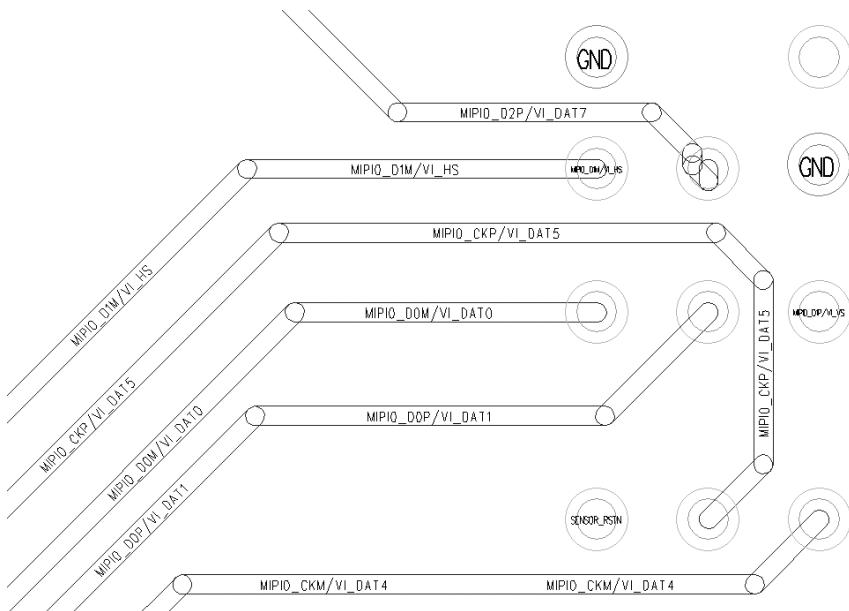

## 6.51 建立差分对及设置

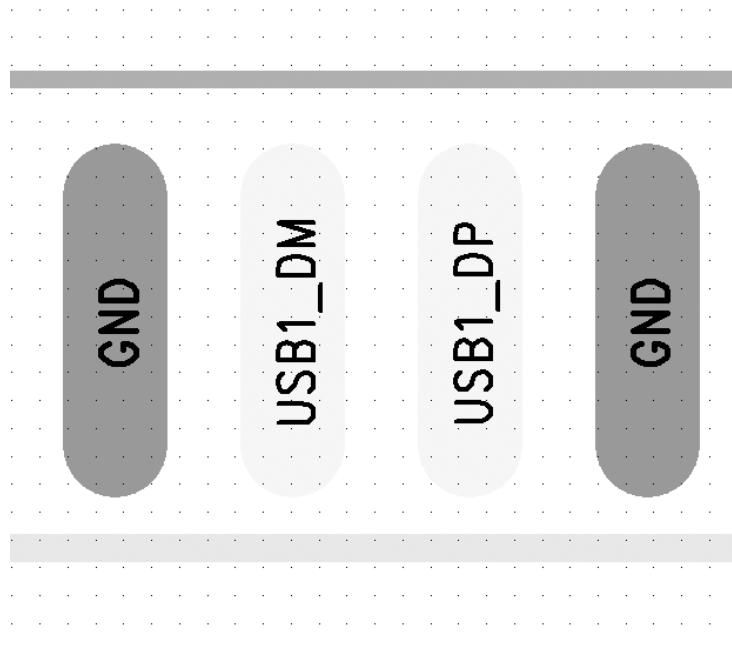

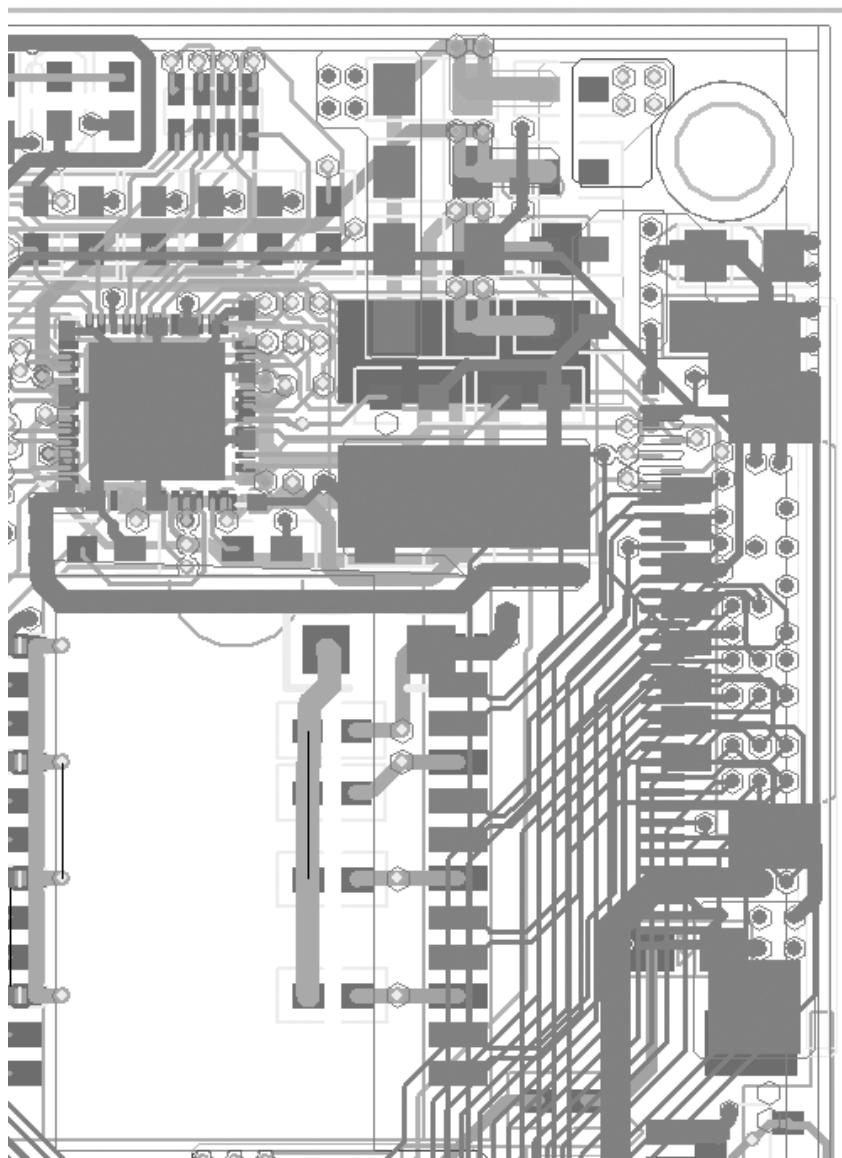

差分网络常见命名为两个网络前缀一致，最后的字节为“+”和“-”、“N”和“P”，USB 接口网络以“M”和“P”结尾，根据这 3 个特征，查找 PCB 上的差分对。

差分对 PADS Layout 上也可以建立，但速度较慢，因此建议在 PADS Router 软件上创建差分对（本节以 PADS Router 软件为例）。

单击鼠标右键，执行菜单命令【网络】。选中需要建立的差分对的两个网络（差分对为两个网络，禁止多组需要建立差分的网络同时选中），如图 6-118 所示。

图 6-118 选中差分网络

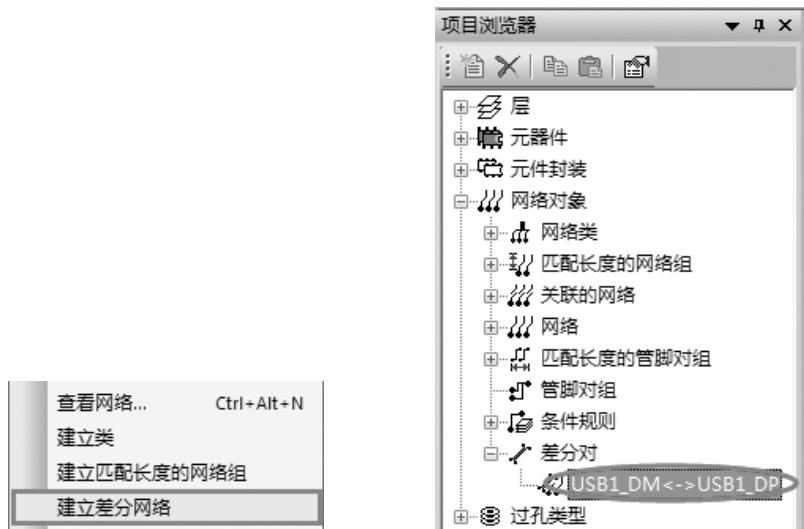

单击鼠标右键，执行菜单命令【差分网络】，如图 6-119 所示。

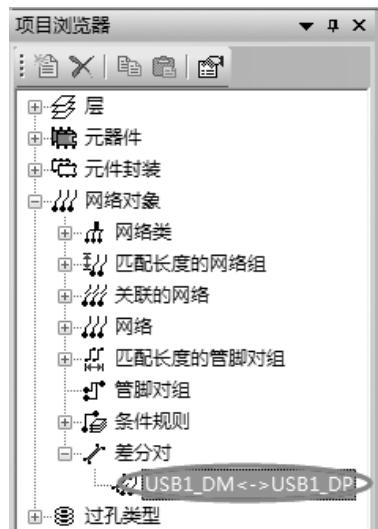

在“项目浏览器”的“差分对”标签中选中建立好的差分网络，如图 6-120 所示。

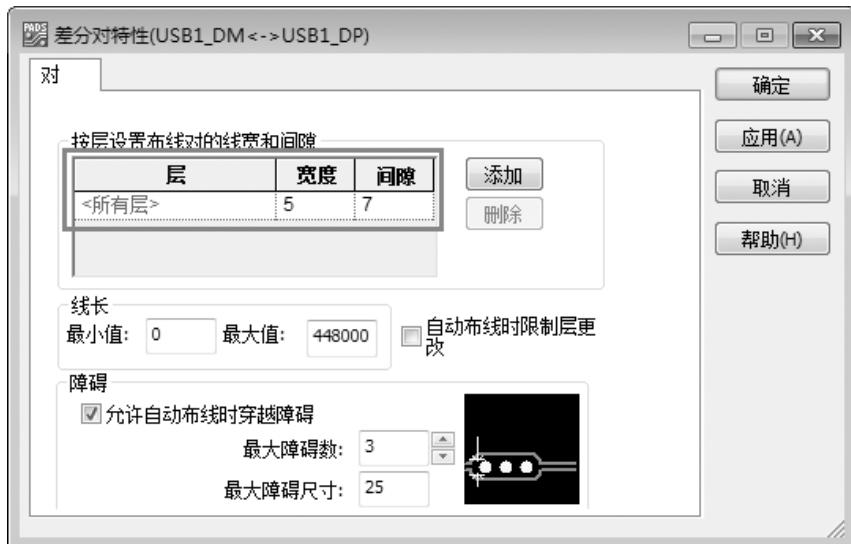

单击鼠标右键，进入其特性，主要对宽度、间隙进行编辑，如图 6-121 所示。

图 6-119 建立差分网络

图 6-120 选择差分对

图 6-121 编辑差分对特性

## 6.52 选中某片区域的差分对

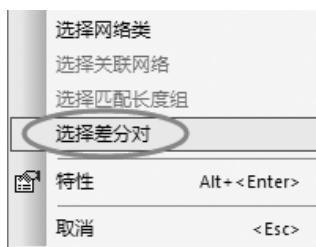

单击鼠标右键，执行菜单命令【选择网络】，选择该片区域的所有网络，如图 6-122 所示。

单击鼠标右键，执行菜单命令【选择差分对】，如图 6-123 所示。

该片区域的差分对都被选中，如图 6-124 所示。

图 6-122 选中该片区域的网络

图 6-123 选择差分对

图 6-124 差分对被选中

### 6.53 无法创建差分对

创建差分对时出现如图 6-125 所示的报错。

图 6-125 创建差分对

报错问题是选中的网络存在铜箔/覆铜/平面层，原因可能是：

- (1) 分配覆铜或平面网络时误分配错误；

- (2) 制作封装时在差分引脚使用了关联铜箔；

- (3) 在 PCB 的元器件上绘制了形状并分配了网络。

解决问题后便可以重新创建差分对。

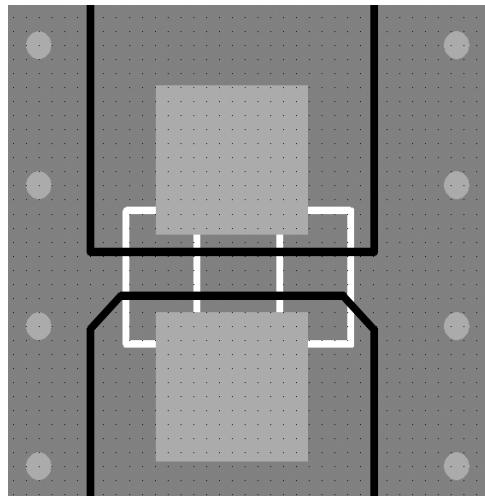

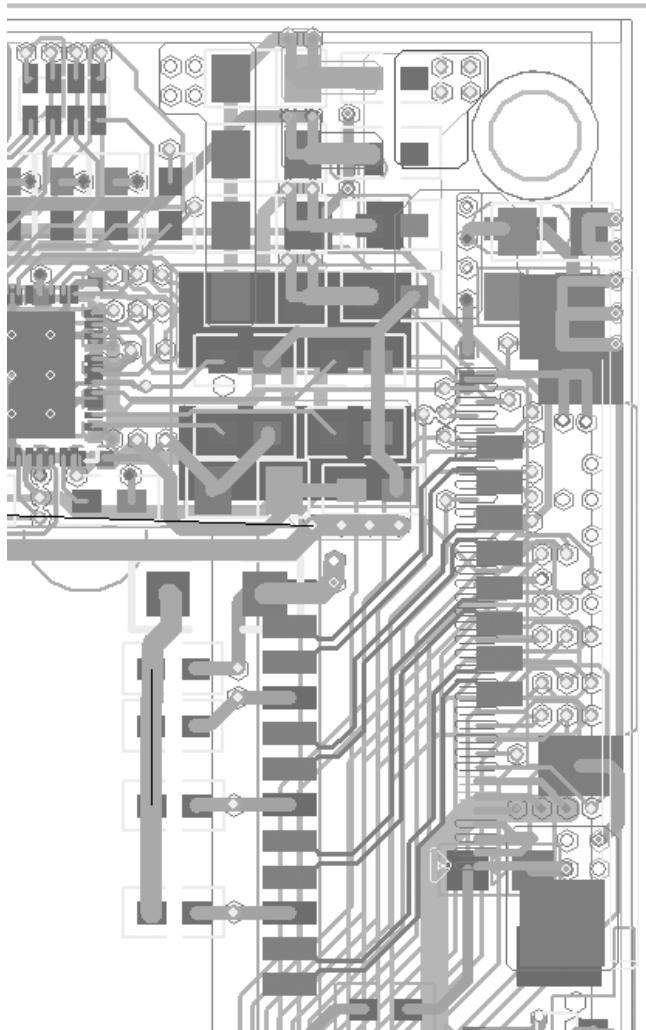

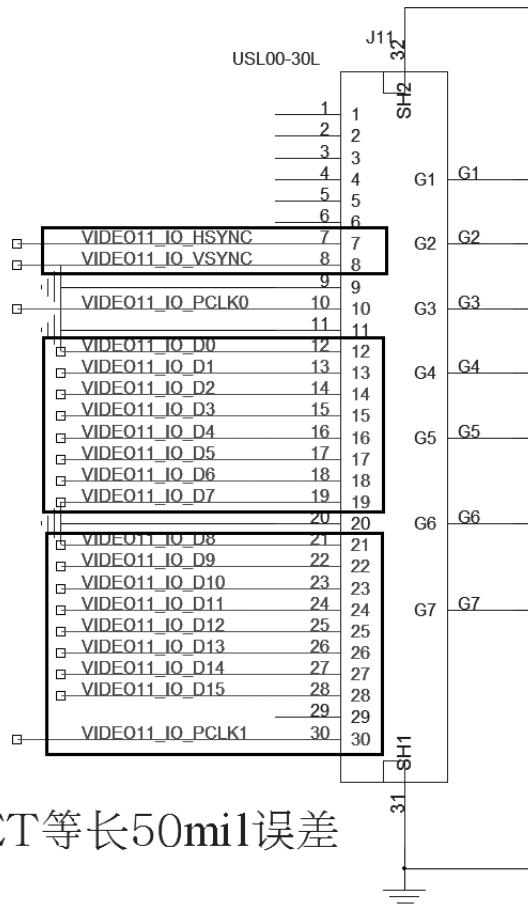

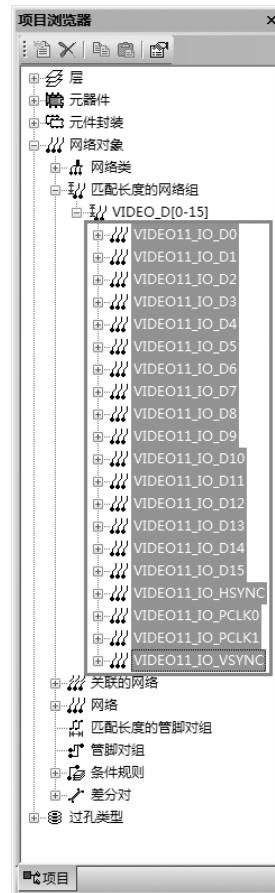

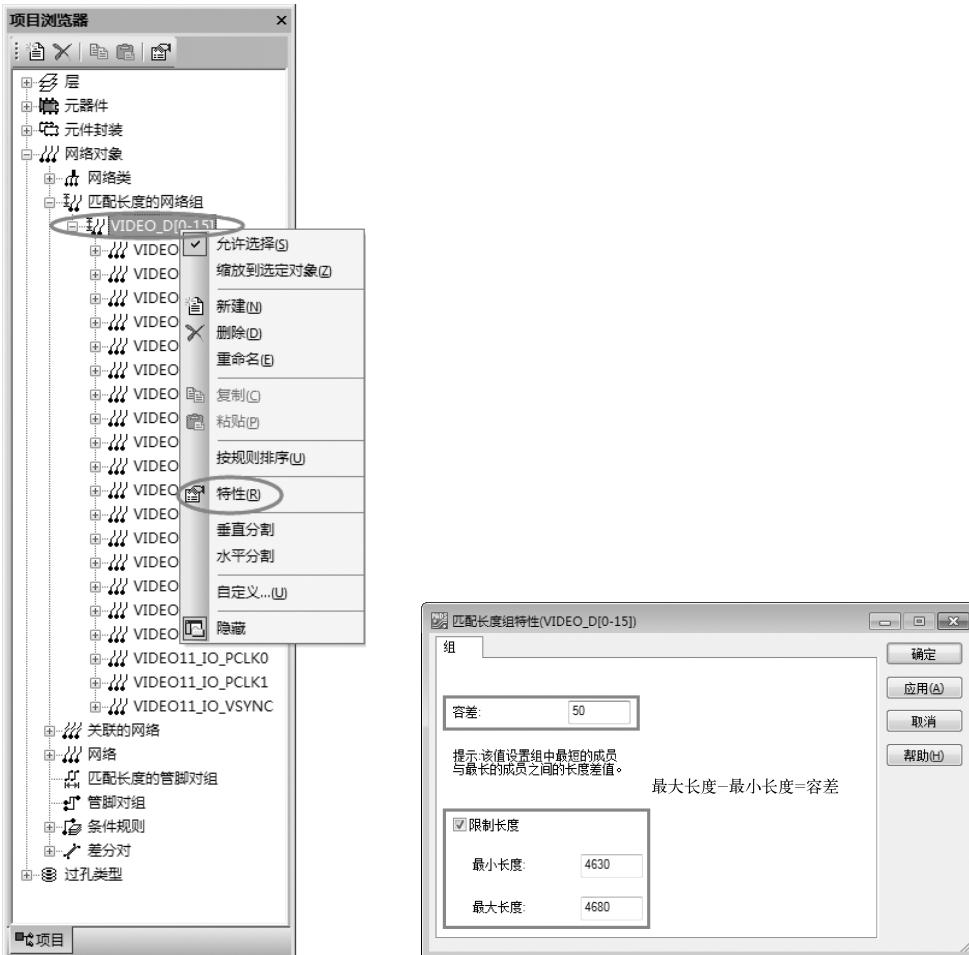

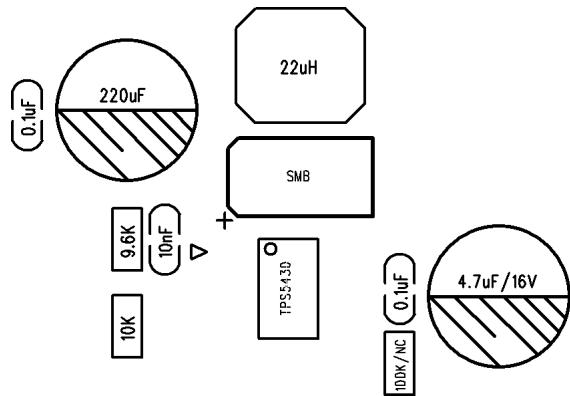

## 6.54 建立等长的网络组

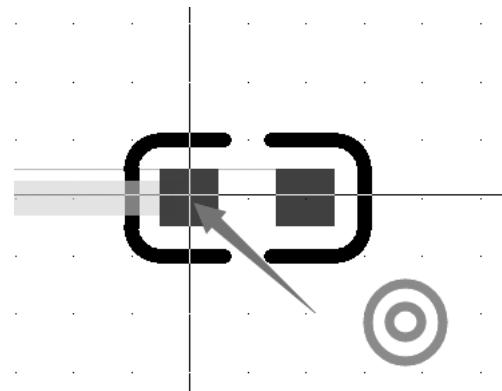

在 PCB 上找需要建立等长的网络较为困难，将 PADS Logic 和 PADS Router 交互起来，在 PADS Logic 上选中要做等长的网络，如图 6-126 所示。

图 6-126 PADS Logic 选中等长网络组

切换至 PADS Router 上单击鼠标右键，执行菜单命令【建立匹配长度的网络组】，如图 6-127 所示。

建立完成后可以在项目浏览器中找到，把等长网络组展开，选中组内网络，如图 6-128 所示。

图 6-127 建立匹配长度的网络组

图 6-128 选中等长网络组内的网络

在标准工具栏中单击“电子表格”图标，如图 6-129 所示。

图 6-129 电子表格图标

弹出“电子表格”对话框，双击已布线的长度，有从大到小和从小到大两个排序。找到最长的网络，记下它的长度，如图 6-130 所示。

选中“项目浏览器”中“匹配长度的网络组”，单击鼠标右键，执行菜单命令【特性】，如图 6-131 所示。

进入匹配长度的网络组特性，对“容差”进行设置，限制长度中，最大长度减去最小长度等于长容差，如图 6-132 所示。

设置完成后，绕等长时将会遇到蛇形走线。

电子表格

网格长度监视器

|    | 名称                | 标记对象 | 估计长度    | 未布线的长度 | 已布线的长度  | 限制长度 | 长度最小值 | 长度最大值  | 网络类 | 长度匹配的组        | 容差  | 边缘     |

|----|-------------------|------|---------|--------|---------|------|-------|--------|-----|---------------|-----|--------|

| 1  | VIDEO011 IO_PCLK1 |      | 4679.66 | 0      | 4679.66 |      | 0     | 448000 |     | VIDEO D[0-15] | 200 | 0      |

| 2  | VIDEO011 IO_D11   |      | 4528.52 | 0      | 4528.52 |      | 0     | 448000 |     | VIDEO D[0-15] | 200 | 0      |

| 3  | VIDEO011 IO_D15   |      | 4514.99 | 0      | 4514.99 |      | 0     | 448000 |     | VIDEO D[0-15] | 200 | 0      |

| 4  | VIDEO011 IO_D10   |      | 4498.57 | 0      | 4498.57 |      | 0     | 448000 |     | VIDEO D[0-15] | 200 | 0      |

| 5  | VIDEO011 IO_D14   |      | 4465.03 | 0      | 4465.03 |      | 0     | 448000 |     | VIDEO D[0-15] | 200 | 0      |

| 6  | VIDEO011 IO_D9    |      | 4472.82 | 0      | 4472.82 |      | 0     | 448000 |     | VIDEO D[0-15] | 200 | 6.84   |

| 7  | VIDEO011 IO_D13   |      | 4455.21 | 0      | 4455.21 |      | 0     | 448000 |     | VIDEO D[0-15] | 200 | 24.45  |

| 8  | VIDEO011 IO_D8    |      | 4449.09 | 0      | 4449.09 |      | 0     | 448000 |     | VIDEO D[0-15] | 200 | 30.57  |

| 9  | VIDEO011 IO_D12   |      | 4432.95 | 0      | 4432.95 |      | 0     | 448000 |     | VIDEO D[0-15] | 200 | 46.71  |

| 10 | VIDEO011 IO_D3    |      | 4262.88 | 0      | 4262.88 |      | 0     | 448000 |     | VIDEO D[0-15] | 200 | 216.78 |

| 11 | VIDEO011 IO_D7    |      | 4251.31 | 0      | 4251.31 |      | 0     | 448000 |     | VIDEO D[0-15] | 200 | 228.35 |

| 12 | VIDEO011 IO_D2    |      | 4233.02 | 0      | 4233.02 |      | 0     | 448000 |     | VIDEO D[0-15] | 200 | 246.64 |

| 13 | VIDEO011 IO_D6    |      | 4222.36 | 0      | 4222.36 |      | 0     | 448000 |     | VIDEO D[0-15] | 200 | 257.3  |

| 14 | VIDEO011 IO_D1    |      | 4207.18 | 0      | 4207.18 |      | 0     | 448000 |     | VIDEO D[0-15] | 200 | 272.48 |

| 15 | VIDEO011 IO_D5    |      | 4192.62 | 0      | 4192.62 |      | 0     | 448000 |     | VIDEO D[0-15] | 200 | 287.04 |

| 16 | VIDEO011 IO_D0    |      | 4181.49 | 0      | 4181.49 |      | 0     | 448000 |     | VIDEO D[0-15] | 200 | 298.17 |

| 17 | VIDEO011 IO_D4    |      | 4163.99 | 0      | 4163.99 |      | 0     | 448000 |     | VIDEO D[0-15] | 200 | 315.67 |

| 18 | VIDEO011 IO_VSYNC |      | 4063.31 | 0      | 4063.31 |      | 0     | 448000 |     | VIDEO D[0-15] | 200 | 416.35 |

| 19 | VIDEO011 IO_PCLK0 |      | 3996.44 | 0      | 3996.44 |      | 0     | 448000 |     | VIDEO D[0-15] | 200 | 483.22 |

| 20 | VIDEO011 IO_HSYNC |      | 3899.74 | 0      | 3899.74 |      | 0     | 448000 |     | VIDEO D[0-15] | 200 | 579.92 |

图 6-130 查看已布线最长网络的长度

图 6-131 进入匹配长度的网络组特性

图 6-132 设置容差

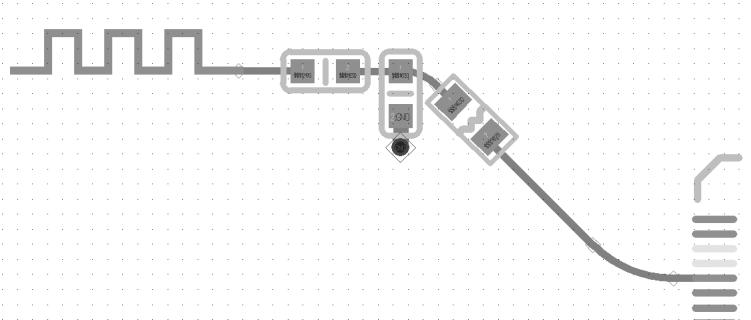

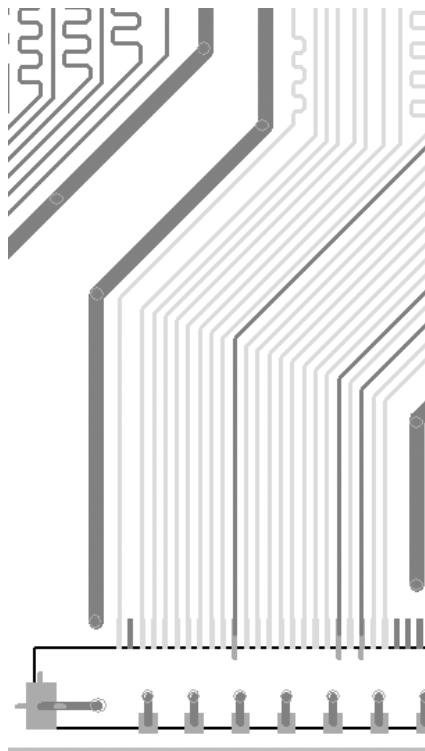

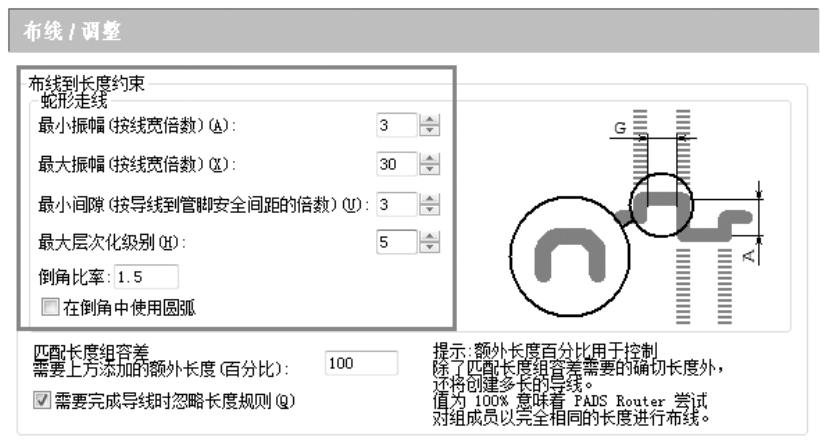

## 6.55 蛇形走线

为调节延时，满足系统时序设计要求，有时又会受到布线空间的限制，这时就需要通过蛇形走线达到设计需要的走线长度。

蛇形走线推荐设置如图 6-133 所示。

图 6-133 蛇形走线推荐设置

如果需要圆弧走线，可以勾选“在倒角中使用圆弧”。

绕等长时，电子表格中对将要绕等长网络选择保留当前对象，如图 6-134 所示。

| 电子表格 |                   |                          |         |        |                      |          |       |       |               |        |        |    |

|------|-------------------|--------------------------|---------|--------|----------------------|----------|-------|-------|---------------|--------|--------|----|

|      | 名称                | 标记对象                     | 估计长度    | 未布线的长度 | 已有<br>保留当前对象         | 与项目浏览器同步 | 长度最小值 | 长度最大值 | 网络类           | 长度匹配的组 | 容差     | 边缘 |

| 1    | VIDEO011 IO_PCLK1 | <input type="checkbox"/> | 4879.65 | 0      | 4879.65<br>保留当前对象    |          | 4830  | 4880  | VIDEO D[0-15] | 50     | 0      |    |

| 2    | VIDEO011 IO_D11   | <input type="checkbox"/> | 4528.52 | 0      | 4528.52<br>无部件       |          | 4830  | 4880  | VIDEO D[0-15] | 50     | 101.48 |    |

| 3    | VIDEO011 IO_D15   | <input type="checkbox"/> | 4514.99 | 0      | 4514.99<br>封装        |          | 4830  | 4880  | VIDEO D[0-15] | 50     | 115.01 |    |

| 4    | VIDEO011 IO_D10   | <input type="checkbox"/> | 4498.57 | 0      | 4498.57<br>层         |          | 4830  | 4880  | VIDEO D[0-15] | 50     | 131.43 |    |

| 5    | VIDEO011 IO_D14   | <input type="checkbox"/> | 4485.03 | 0      | 4485.03<br>网络        |          | 4830  | 4880  | VIDEO D[0-15] | 50     | 144.97 |    |

| 6    | VIDEO011 IO_D9    | <input type="checkbox"/> | 4472.82 | 0      | 4472.82<br>关联的网络     |          | 4830  | 4880  | VIDEO D[0-15] | 50     | 157.18 |    |

| 7    | VIDEO011 IO_D13   | <input type="checkbox"/> | 4455.21 | 0      | 4455.21<br>长度匹配的网络组  |          | 4830  | 4880  | VIDEO D[0-15] | 50     | 174.79 |    |

| 8    | VIDEO011 IO_D8    | <input type="checkbox"/> | 4449.09 | 0      | 4449.09<br>几根长度的管脚对组 |          | 4830  | 4880  | VIDEO D[0-15] | 50     | 180.91 |    |

| 9    | VIDEO011 IO_D12   | <input type="checkbox"/> | 4432.95 | 0      | 4432.95<br>管脚对组      |          | 4830  | 4880  | VIDEO D[0-15] | 50     | 197.05 |    |

| 10   | VIDEO011 IO_D3    | <input type="checkbox"/> | 4262.88 | 0      | 4262.88<br>差分对       |          | 4830  | 4880  | VIDEO D[0-15] | 50     | 367.12 |    |

| 11   | VIDEO011 IO_D7    | <input type="checkbox"/> | 4251.31 | 0      | 4251.31<br>禁止区域      |          | 4830  | 4880  | VIDEO D[0-15] | 50     | 378.69 |    |

| 12   | VIDEO011 IO_D2    | <input type="checkbox"/> | 4233.02 | 0      | 4233.02<br>过孔类型      |          | 4830  | 4880  | VIDEO D[0-15] | 50     | 396.98 |    |

| 13   | VIDEO011 IO_D6    | <input type="checkbox"/> | 4222.36 | 0      | 4222.36<br>铜箔        |          | 4830  | 4880  | VIDEO D[0-15] | 50     | 407.64 |    |

| 14   | VIDEO011 IO_D1    | <input type="checkbox"/> | 4207.18 | 0      | 4207.18<br>跳线        |          | 4830  | 4880  | VIDEO D[0-15] | 50     | 422.82 |    |

| 15   | VIDEO011 IO_D5    | <input type="checkbox"/> | 4192.62 | 0      | 4192.62<br>□         |          | 4830  | 4880  | VIDEO D[0-15] | 50     | 437.38 |    |

| 16   | VIDEO011 IO_D0    | <input type="checkbox"/> | 4181.49 | 0      | 4181.49<br>□         |          | 4830  | 4880  | VIDEO D[0-15] | 50     | 448.51 |    |

| 17   | VIDEO011 IO_D4    | <input type="checkbox"/> | 4163.99 | 0      | 4163.99<br>□         |          | 4830  | 4880  | VIDEO D[0-15] | 50     | 466.01 |    |

| 18   | VIDEO011 IO_VSYNC | <input type="checkbox"/> | 4063.31 | 0      | 4063.31<br>□         |          | 4830  | 4880  | VIDEO D[0-15] | 50     | 566.89 |    |

| 19   | VIDEO011 IO_PCLK0 | <input type="checkbox"/> | 3996.44 | 0      | 3996.44<br>□         |          | 4830  | 4880  | VIDEO D[0-15] | 50     | 633.56 |    |

| 20   | VIDEO011 IO_HSYNC | <input type="checkbox"/> | 3899.74 | 0      | 3899.74<br>□         |          | 4830  | 4880  | VIDEO D[0-15] | 50     | 730.26 |    |

图 6-134 保留当前对象

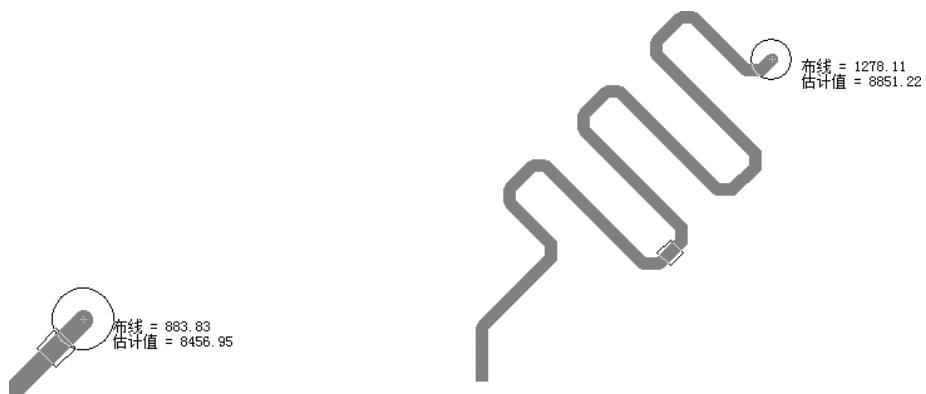

蛇形走线的角度由准备绕等长时走线的角度决定，如图 6-135、图 6-136 和图 6-137 所示。

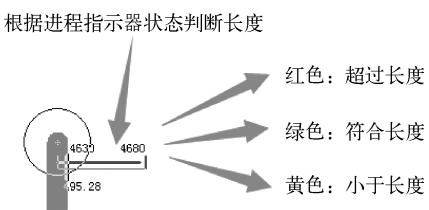

走线长度可以根据进程指示器状态（见图 6-138）和电子表格状态（见图 6-139）的颜色判断长度。

图 6-135 46°走线

图 6-136 垂直走线

图 6-137 平行走线

图 6-138 进程指示器状态

| 电子表格 |                  |                          |         |   |   |         |                                     |                                   |

|------|------------------|--------------------------|---------|---|---|---------|-------------------------------------|-----------------------------------|

|      |                  |                          |         |   |   |         |                                     |                                   |

| 1    | VIDEO11 IO_VSYNC | <input type="checkbox"/> | 5379.31 | 0 | 红 | 5379.31 | <input checked="" type="checkbox"/> | 4630 4680 VIDEO_D[0-15] 50 699.31 |

| 2    | VIDEO11 IO_D2    | <input type="checkbox"/> | 4669.81 | 0 | 绿 | 4669.81 | <input checked="" type="checkbox"/> | 4630 4680 VIDEO_D[0-15] 50 0      |

| 3    | VIDEO11 IO_D11   | <input type="checkbox"/> | 4528.52 | 0 | 黄 | 4528.52 | <input checked="" type="checkbox"/> | 4630 4680 VIDEO_D[0-15] 50 101.48 |

图 6-139 电子表格状态

# 第7章 设计验证

## 7.1 进入验证设计

当设计邻近尾声的时候，需要对设计文件进行检查。

首先需对平面进行重新灌注，执行菜单命令【工具】 - 【覆铜管理器】，如图 7-1 和图 7-2 所示。

图 7-1 对平面进行重新灌注（1）

图 7-2 对平面进行重新灌注（2）

对“无平面”重新灌注，如图 7-3 所示。

对“分割混合平面”进行平面连接，如图 7-4 所示。

图 7-3 灌注无平面

图 7-4 连接分割混合平面

以上操作完成后，正式进入验证设计。

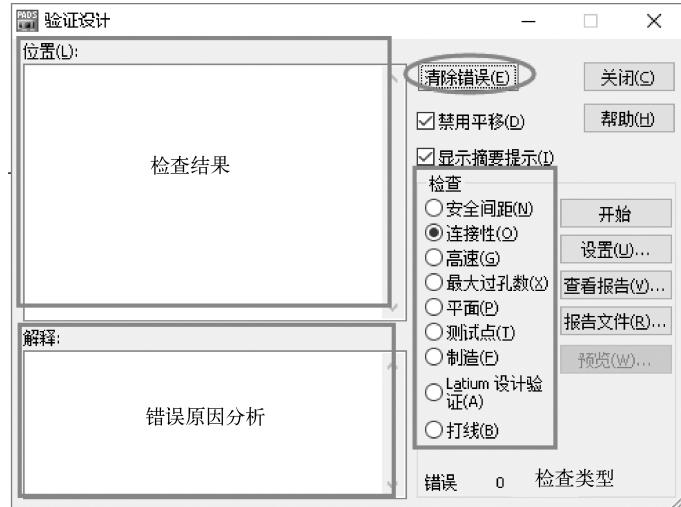

执行菜单命令【工具】 - 【验证设计】，弹出的对话框如图 7-5 所示。

图 7-5 “验证设计”对话框

## 7.2 检查连接性（开路）

检查连接性指具有电气属性连接的网络在设计时有没有连接到一起，如果出现错误，将有连接性错误提示，连接性错误又叫“开路”。

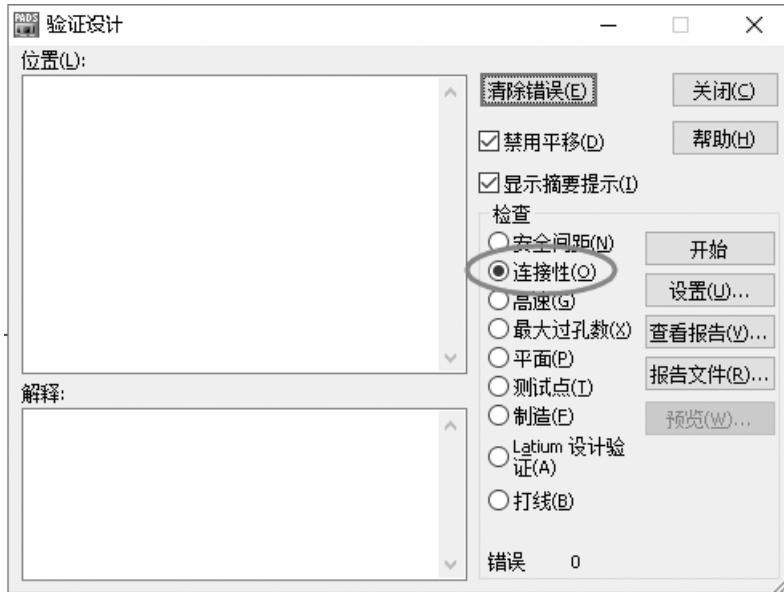

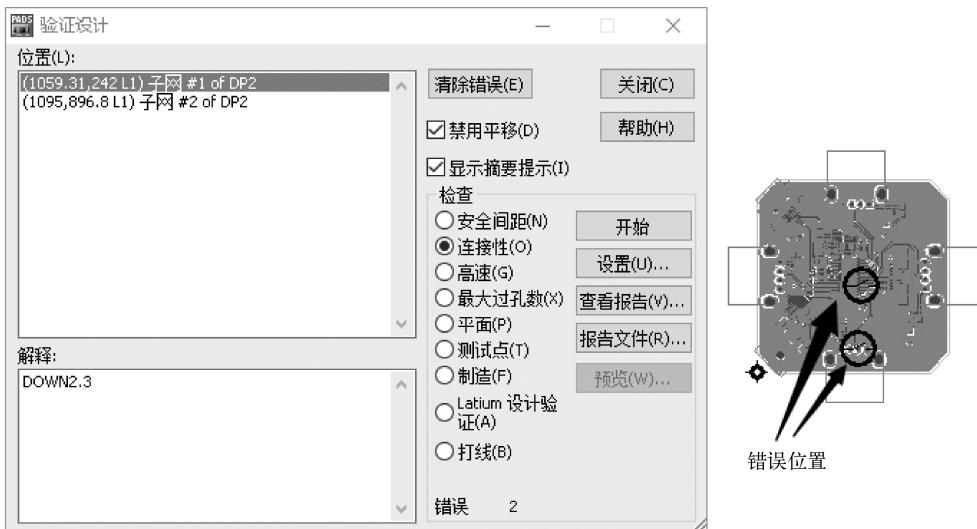

选择检查“连接性”，单击【开始】按钮，如图 7-6 所示。

图 7-6 验证连接性

如果没有连接性错误，将弹出“未发现错误”，如图 7-7 所示。

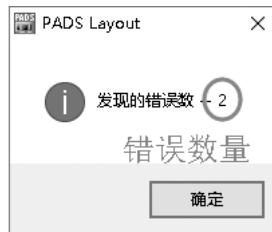

如果有连接性错误，将弹出“错误数量对话框”，如图 7-8 所示。

图 7-7 未发现错误窗口

图 7-8 错误数量对话框

单击【确定】按钮后，弹出“错误提示”窗口，“位置”和“解释”标签将有内容，PCB 上将显示错误所在的位置，如图 7-9 所示。

图 7-9 错误报告

连接性错误至少都是两个或两个以上的出现，代表着至少两个点或以上没连接在一起。连接线错误图标如图 7-10 所示。

图 7-10 连接线错误图标

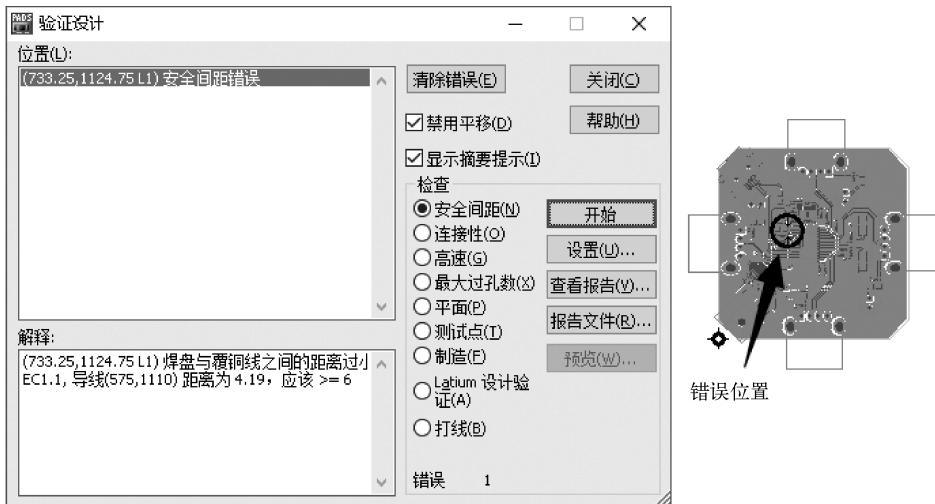

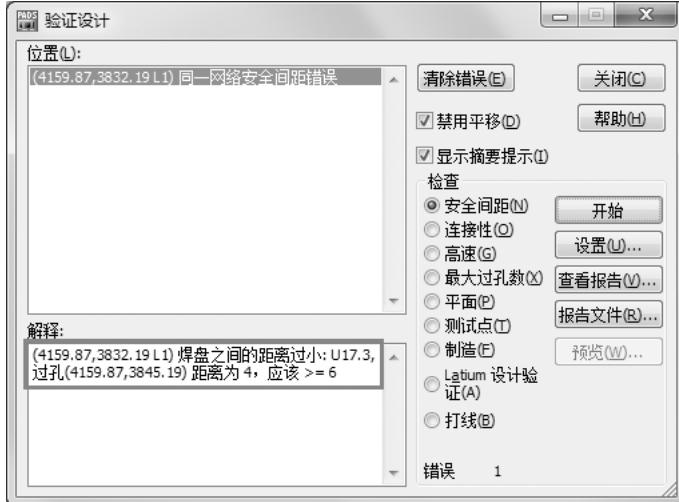

### 7.3 检查安全间距（短路）

安全间距检查通常指超过安全间距的规则设置，不同网络间的距离过近，出现的错误，又称为短路。

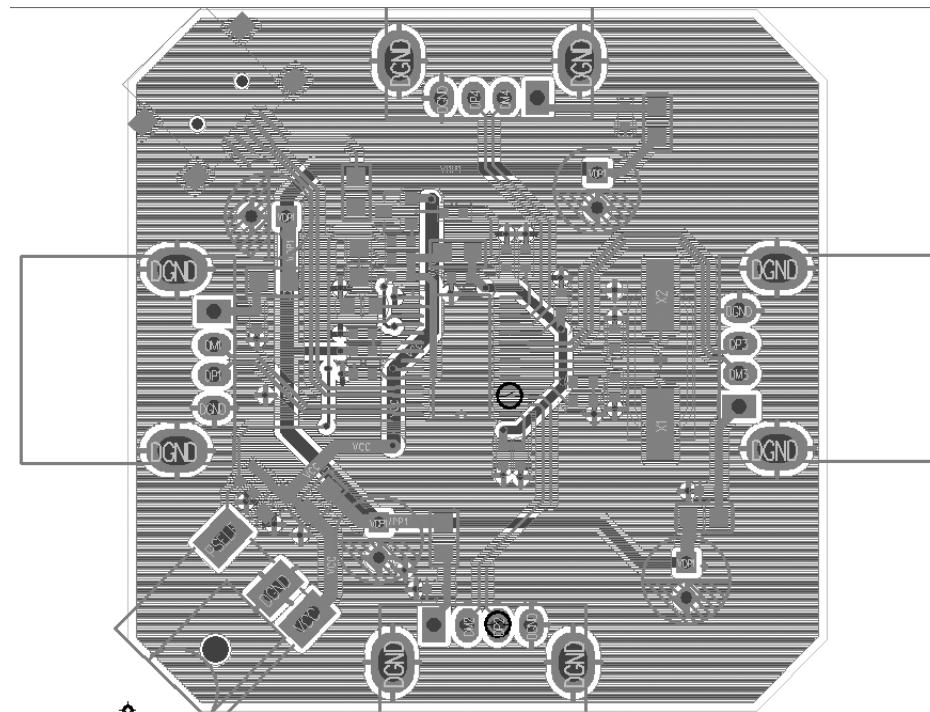

PADS 检查安全间距时只对“当前窗口”进行检查，即对在操作面板中的元素进行检查。

单击“标准工具栏”中的“板”图标，如图 7-11 所示。

单击后，PCB 将最大化显示在操作面板中，如图 7-12 所示。

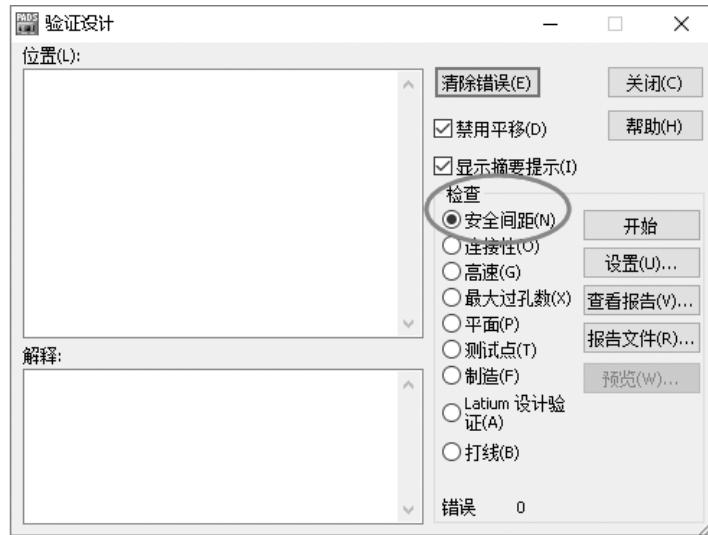

以上操作完成后，选择检查“安全间距”，单击【开始】按钮，如图 7-13 所示。

图 7-11 “板”图标

图 7-12 板视图效果图

图 7-13 验证安全间距

如果没有安全间距错误，将弹出“未发现错误”，如图 7-14 所示。

如果有安全间距错误，将弹出“错误数量对话框”，如图 7-15 所示。

图 7-14 未发现错误窗口

图 7-15 错误数量对话框

单击【确定】按钮后，弹出“错误提示”窗口，“位置”和“解释”标签将有内容，PCB 上将显示错误所在的位置，如图 7-16 所示。安全间距错误图标如图 7-17 所示。

图 7-16 错误报告

图 7-17 安全间距错误图标

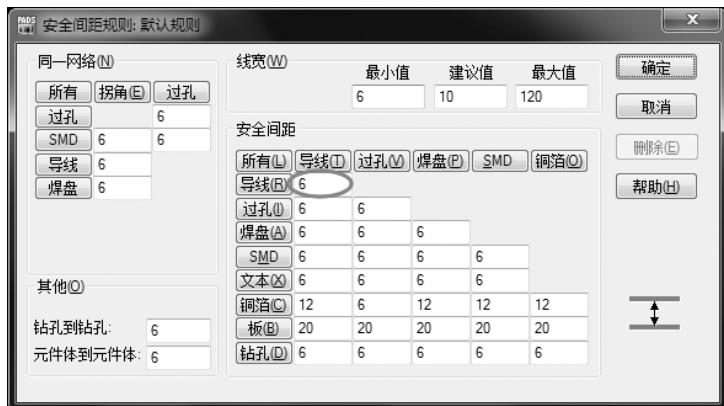

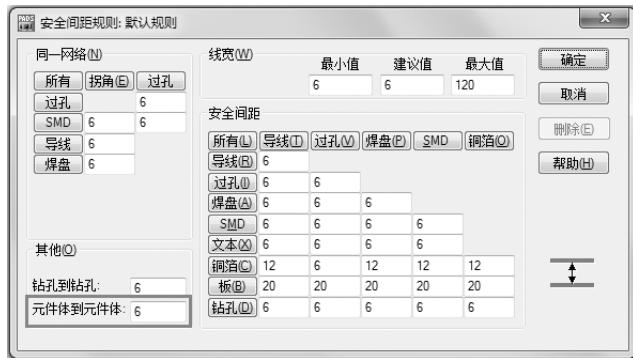

安全间距默认间距设置如图 7-18 所示。

安全间距是根据规则设置进行检查的，如导线与导线的安全间距为 6mil，如图 7-19 所示。

如果导线与导线之间小于 6mil，单击【确定】按钮验证后，PCB 上将会出现错误标识，如图 7-20 所示。

验证设计的窗口中出现错误摘要，单击“位置”处的错误对象，PCB 上对应的点将会亮显，如图 7-21 所示。

图 7-18 安全间距默认间距设置

图 7-19 规则设置

图 7-20 错误提示

图 7-21 验证设计安全间距

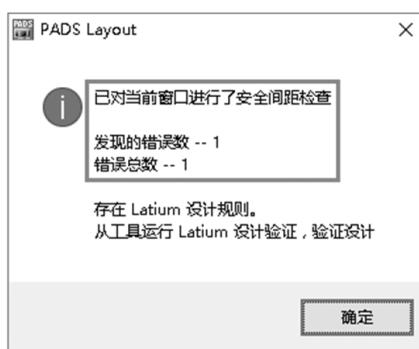

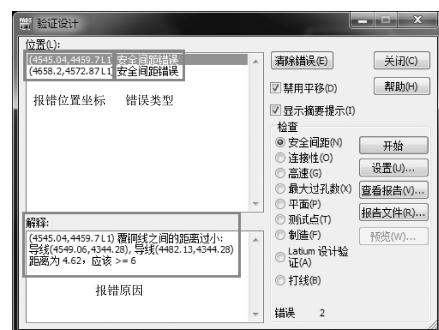

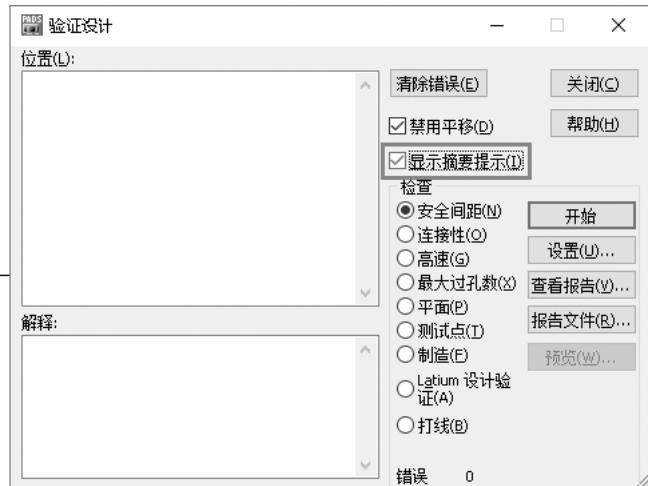

## 7.4 验证设计时没有错误数窗口

没有出现错误窗口，是因为没有勾选“显示摘要提示”，如图 7-22 所示。

图 7-22 勾选显示摘要提示

## 7.5 连接性已经解决还有飞线显示

连接性已经解决还有飞线显示属于正常现象，这种飞线存在于铜箔位置。只要连接性没有错误，飞线的出现可以忽略掉，如图 7-23 所示。

图 7-23 飞线

## 7.6 插件引脚未勾电镀出现连接性错误

插件引脚未勾选“电镀”指该引脚的贴装面/内层/对面将不连接起来，封装制作时就

有连接性错误，在验证整板 PCB 的连接性时，自然而然也会报错，如图 7-24 所示。

图 7-24 未勾选“电镀”选项

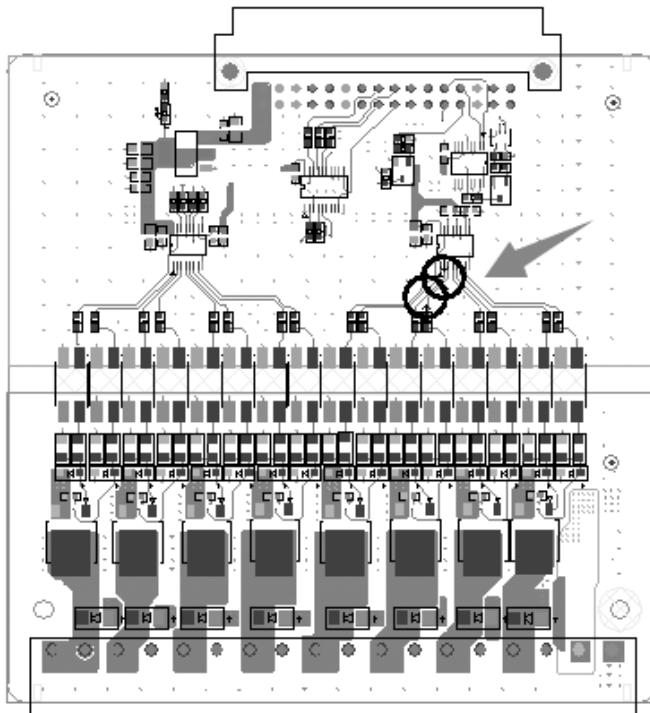

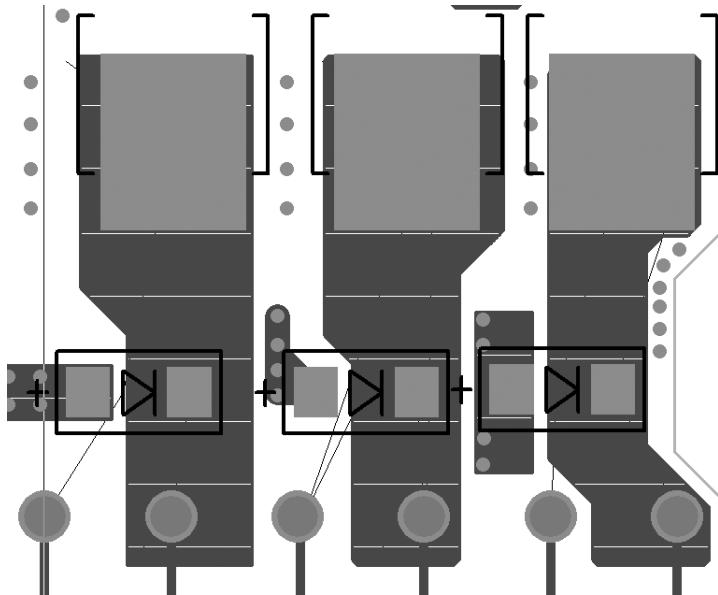

## 7.7 元件体与元件体干涉检查

元件体与元件体干涉检查可能会对生产加工造成隐患。因此，进行元件体干涉检查必不可少，检查元件体干涉（白色背景下）推荐颜色设置如图 7-25 所示。

图 7-25（白色背景下）推荐颜色设置

元件体与元件体的距离会根据设计规则进行检查，规则设置位置如图 7-26 所示。

图 7-26 查看元件体与元件体的距离设置

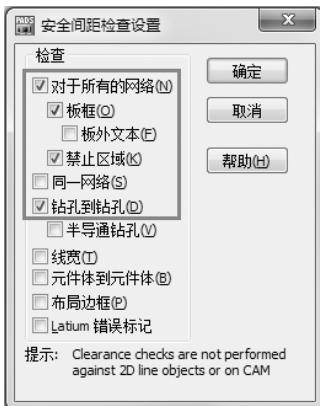

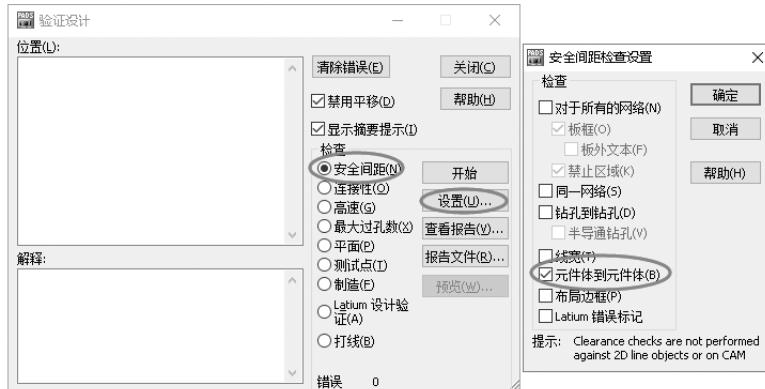

执行菜单命令【工具】 - 【验证设计】，选择“安全间距”，单击【设置】按钮，进入“安全间距检查设置”对话框，只勾选“元件体与元件体”，单击【确定】按钮后开始验证，如图 7-27 所示。

图 7-27 元件体与元件体检查设置

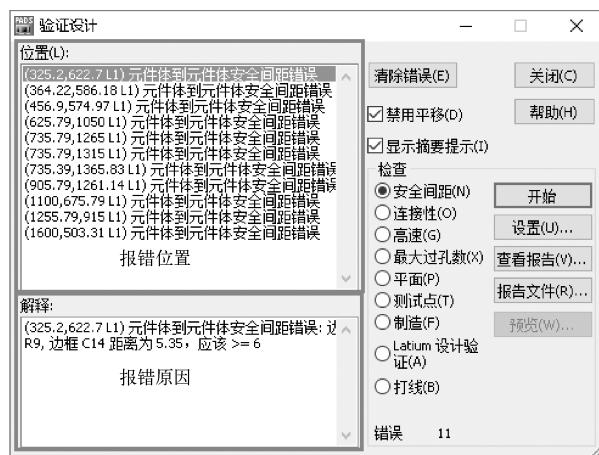

弹出“错误数量”窗口后单击【开始】按钮验证设计中的错误报告，如图 7-28 所示。

图 7-28 验证设计元件体与元件体距离

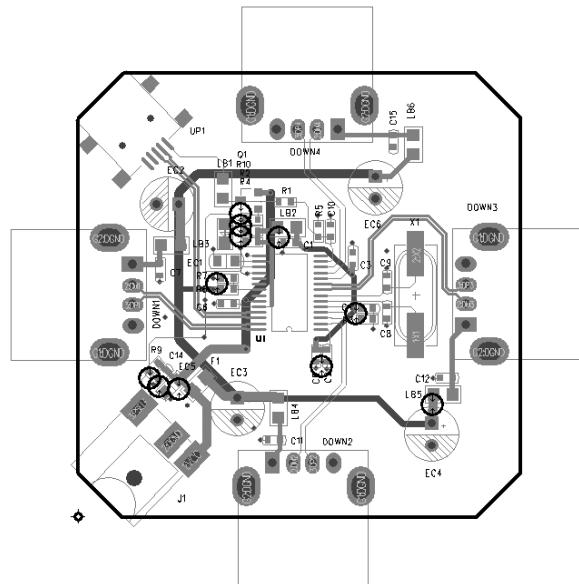

PCB 上的错误提示如图 7-29 所示。

图 7-29 PCB 上的错误提示

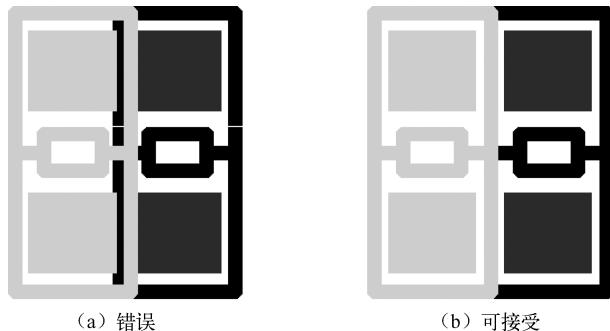

空间比较小的时候可以接受阻容元件体丝印叠丝印，图 7-30 (b) 中出现报错由于空间限制可以忽略错误，但 7-30 (a) 是不能接受的，如图 7-30 所示。

图 7-30 错误类型分析

另外，需注意元件体的 1 脚标识或正负标识不能与其他元件体元件产生干涉，以免影响后期调试或维修。正极与其他原件产生干涉如图 7-31 所示。

图 7-31 元件体干涉

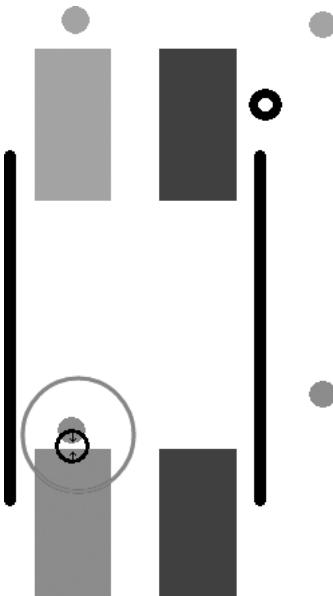

## 7.8 检查过孔有没有打在焊盘上

因为安全间距验证只针对可见的元素进行检查，检查过孔有没有打在焊盘上，推荐颜色设置（白色背景下）如图 7-32 所示。

图 7-32 推荐颜色设置（白色背景下）

设置过孔距离焊盘的安全间距如图 7-33 所示。

图 7-33 设置过孔距离焊盘的安全间距

执行菜单命令【工具】 - 【验证设计】，选择“安全间距”，单击【设置】按钮，进入“安全间距检查设置”对话框只勾选“同一网络”，单击【确定】按钮后单击【开始】按钮验证，如图 7-34 所示。

图 7-34 验证过孔打上焊盘设置

验证设计错误报告如图 7-35 所示。

PCB 上的错误提示如图 7-36 所示。

图 7-35 验证设计错误报告

图 7-36 PCB 上的错误提示

# 第 8 章 PADS logic 文件输出

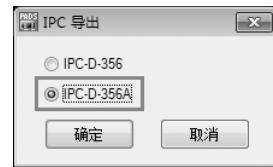

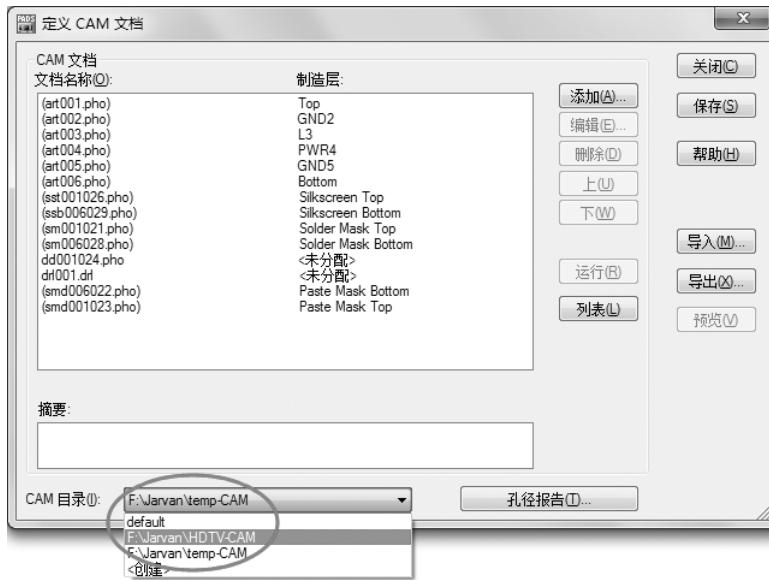

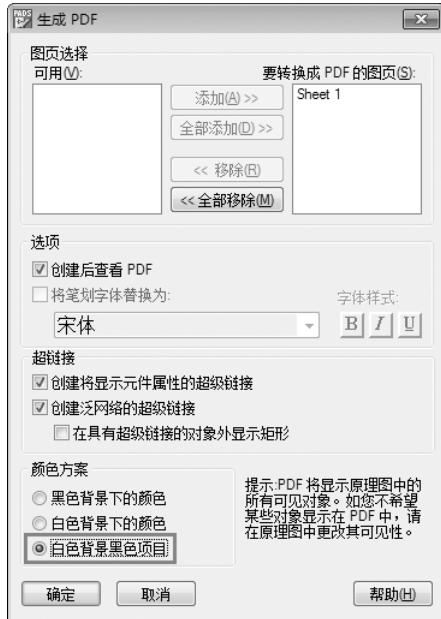

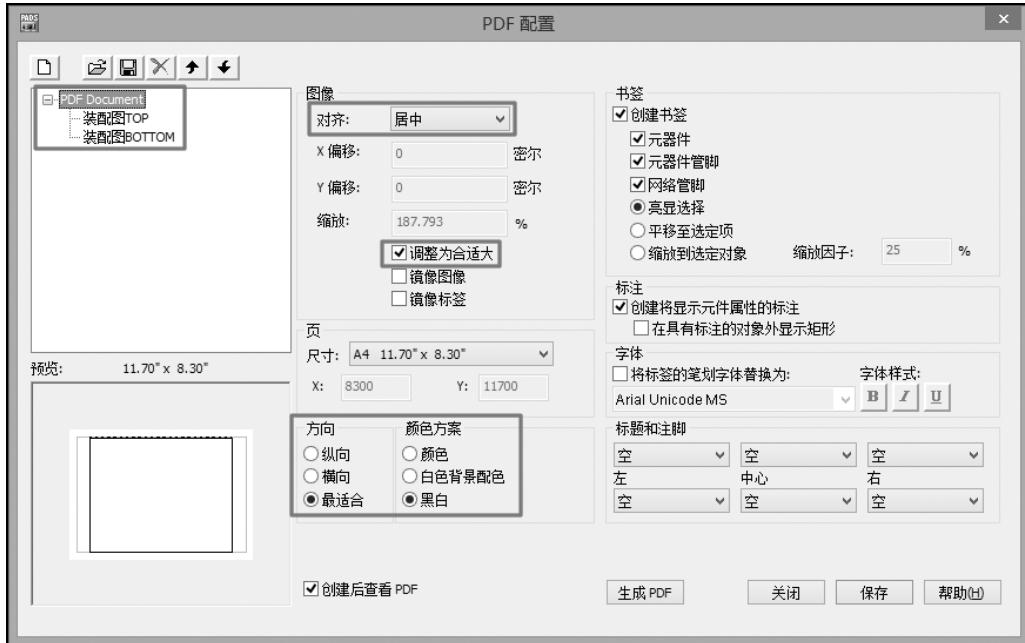

## 8.1 PADS Logic 如何导出低版本

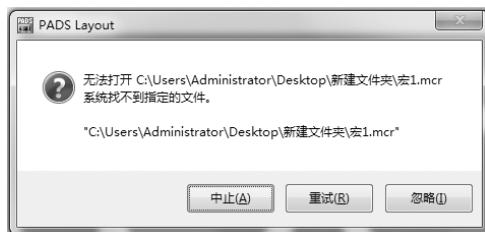

PADS 软件低版本是打不开高版本的设计文件的，这就需要高版本的文件降低版本。执行菜单命令【文件】 - 【导出】，如图 8-1 所示。

图 8-1 PADS Logic 导出

弹出“文件导出”对话框，文件导出的格式为“txt”，可以文件重命名和更改保存的路径，编辑完成后单击【保存】按钮，如图 8-2 所示。

图 8-2 文件导出

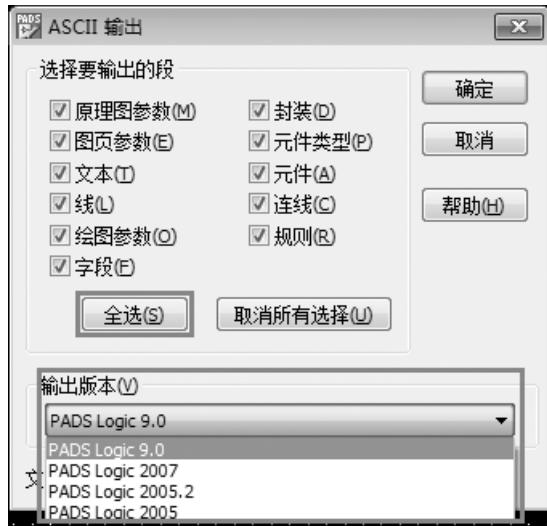

弹出“ASCII 输出”对话框，“选择要输出的段”推荐“全选”，输出版本可根据需要进行选择，如图 8-3 所示。

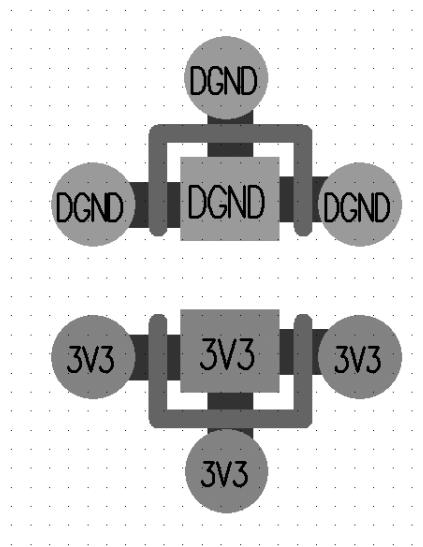

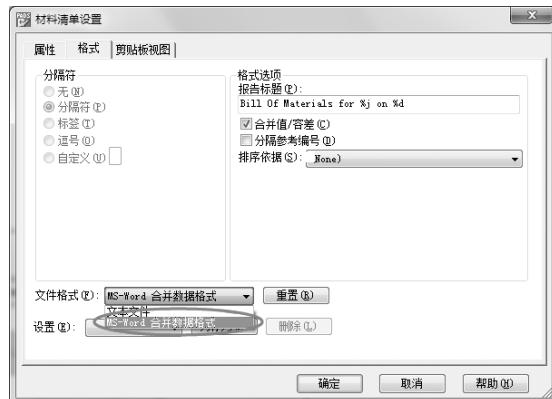

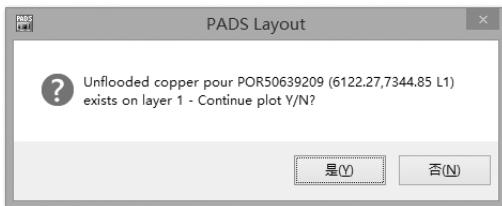

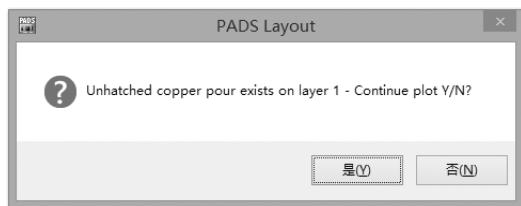

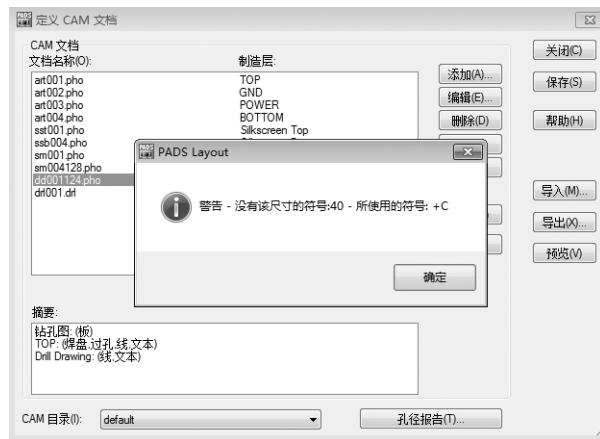

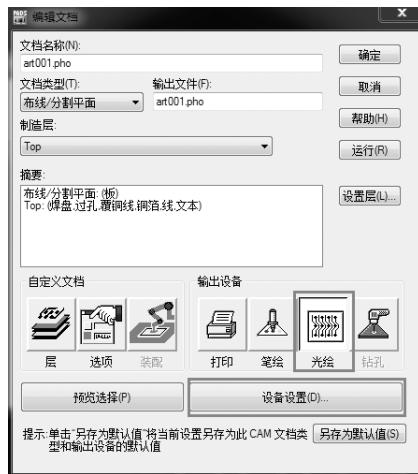

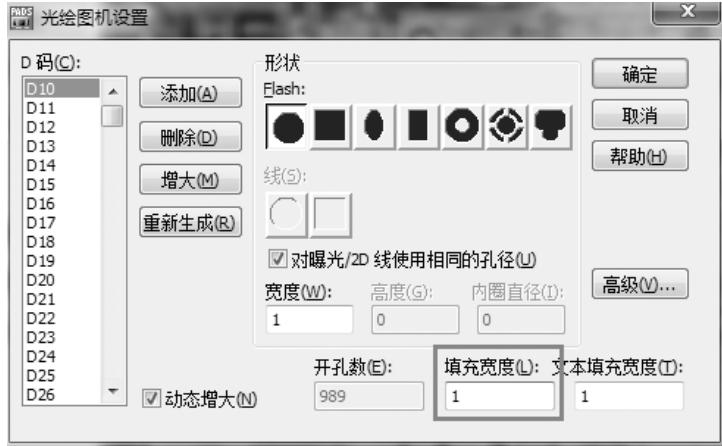

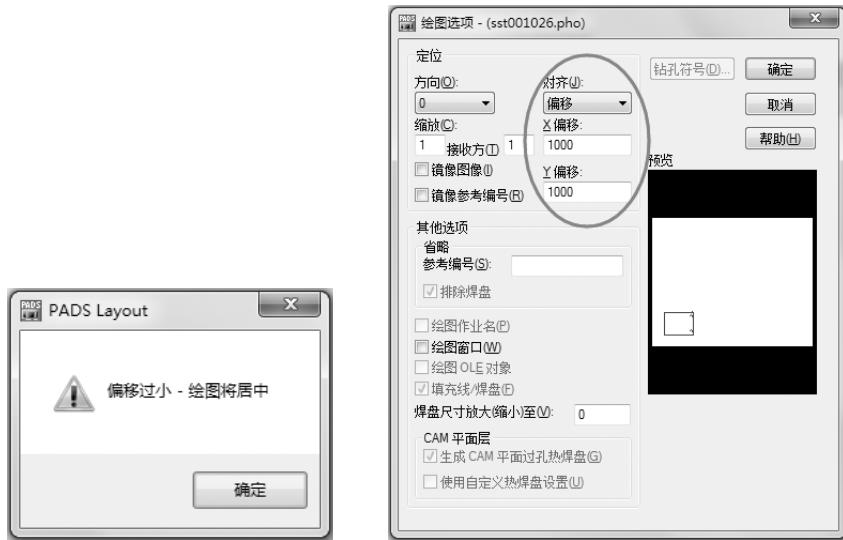

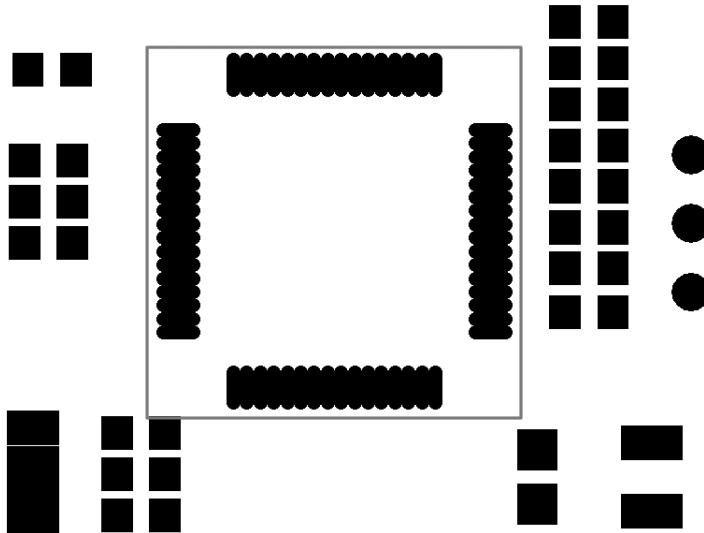

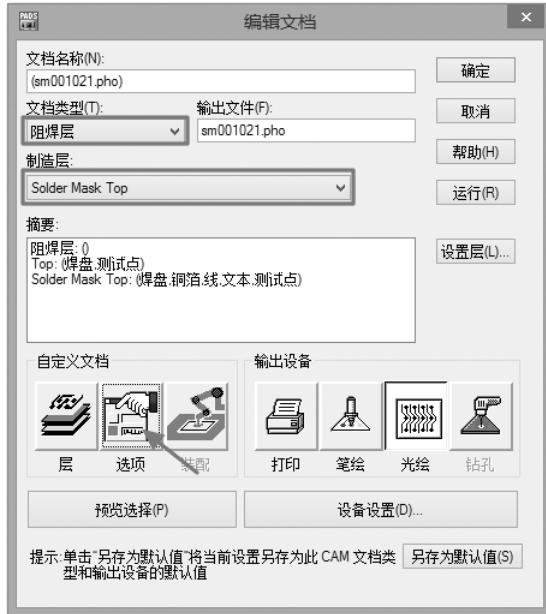

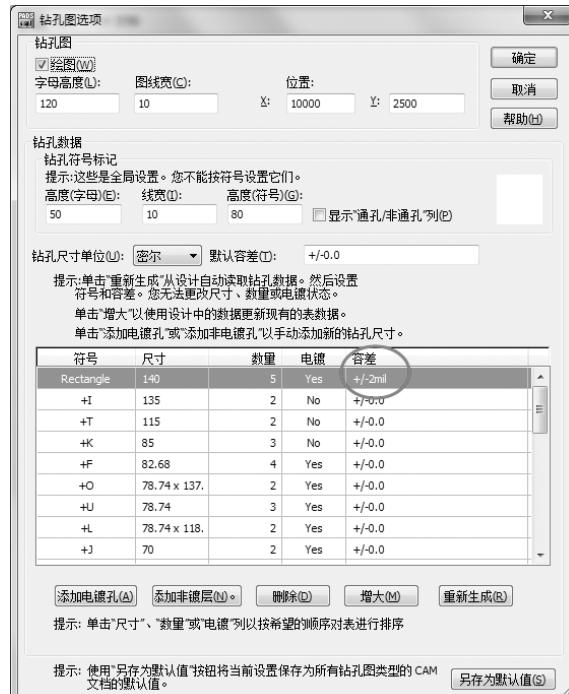

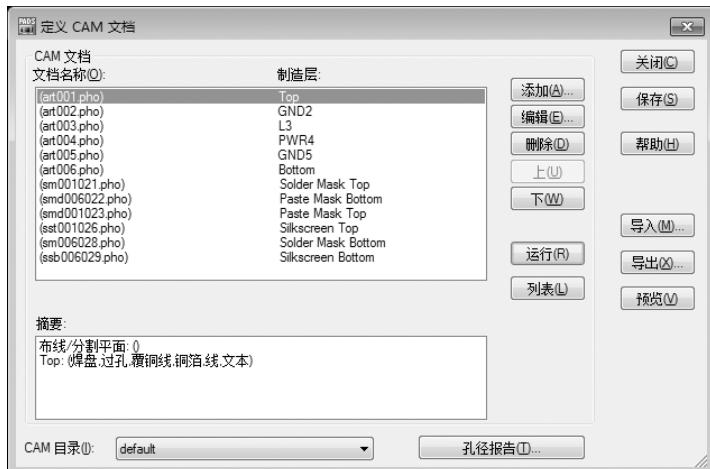

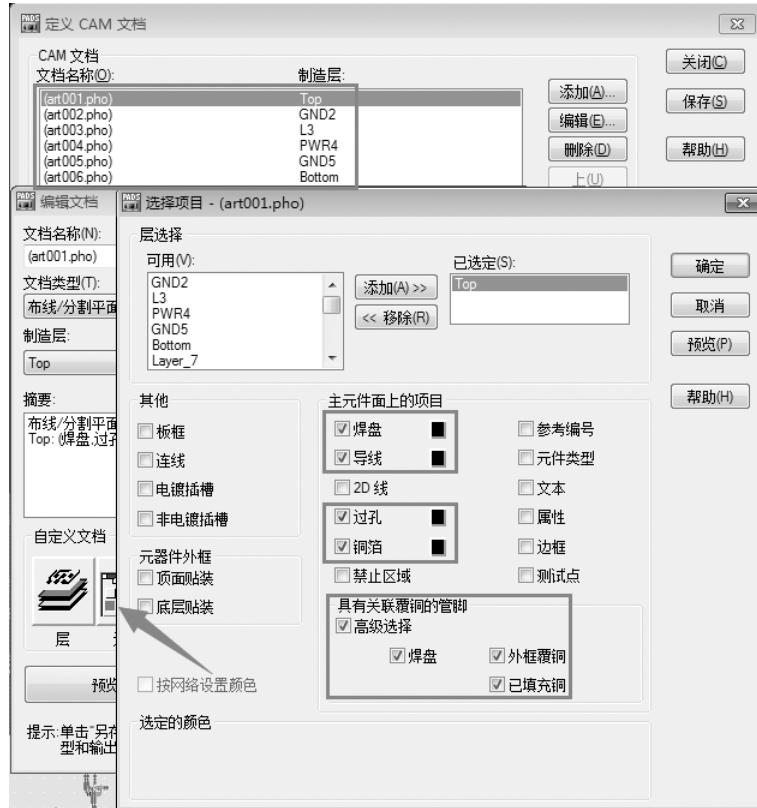

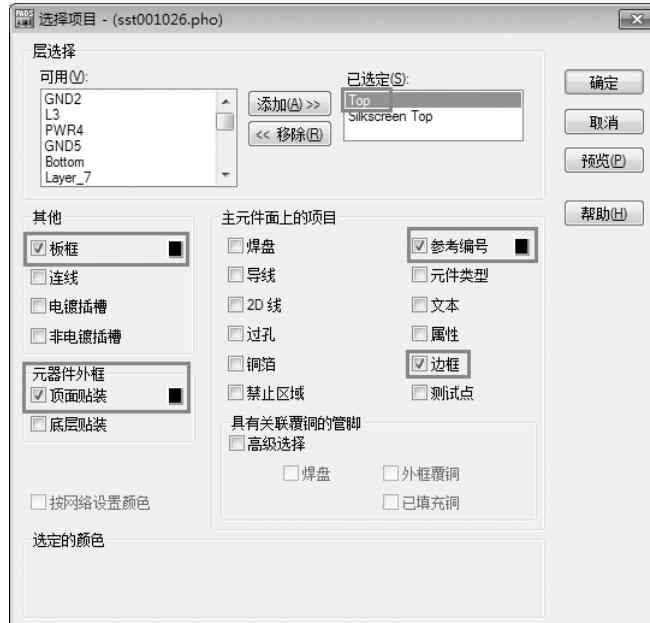

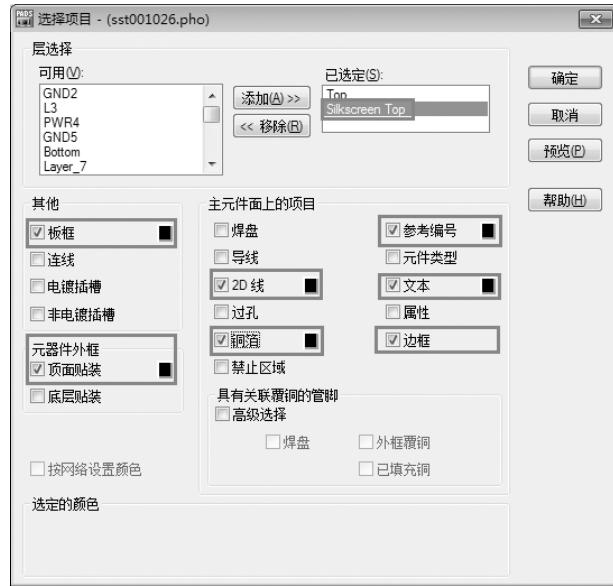

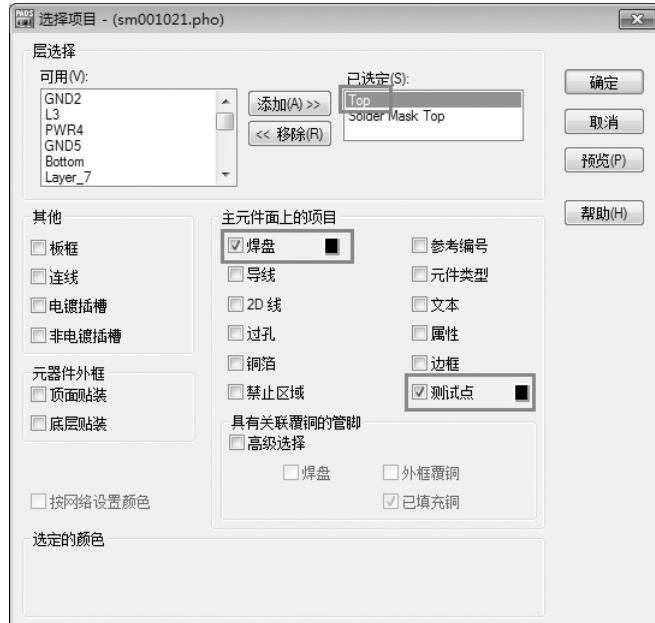

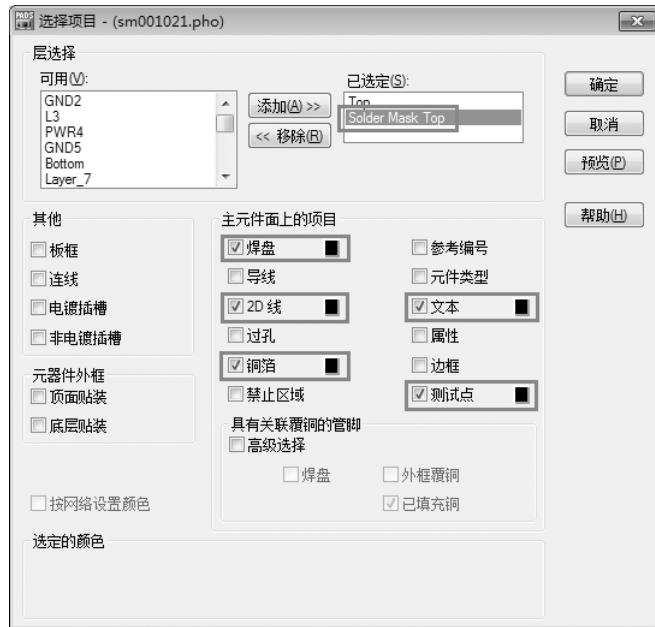

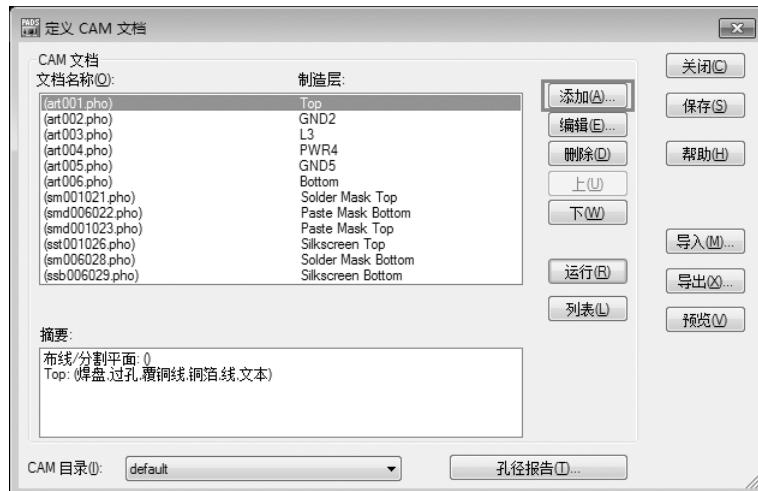

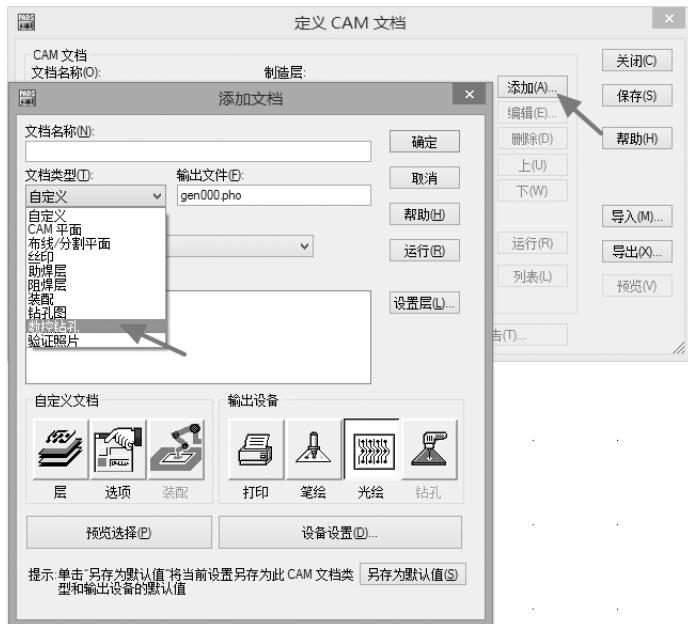

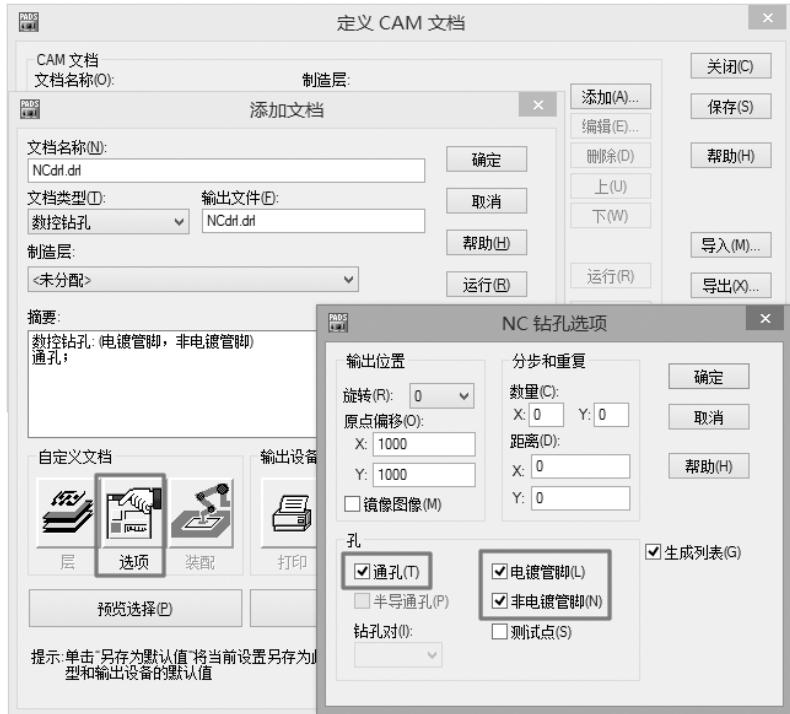

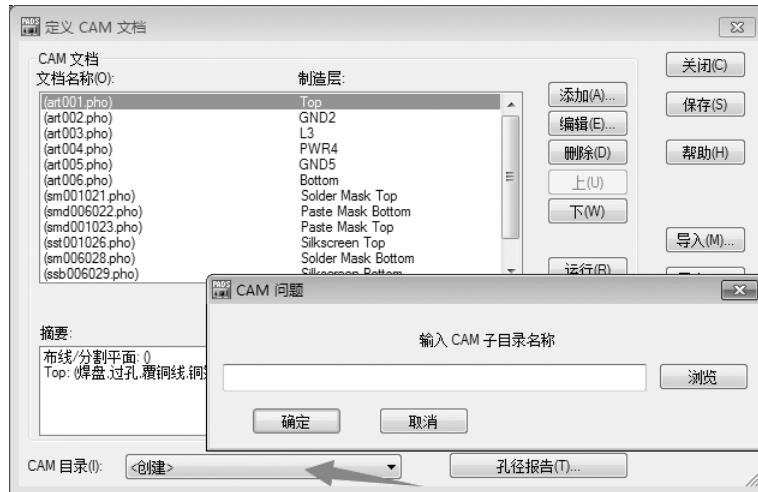

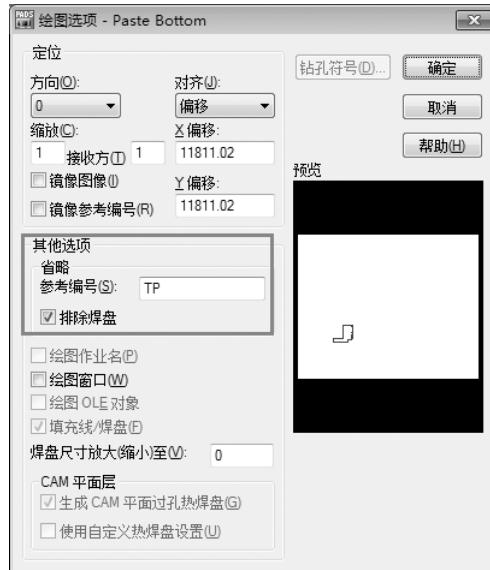

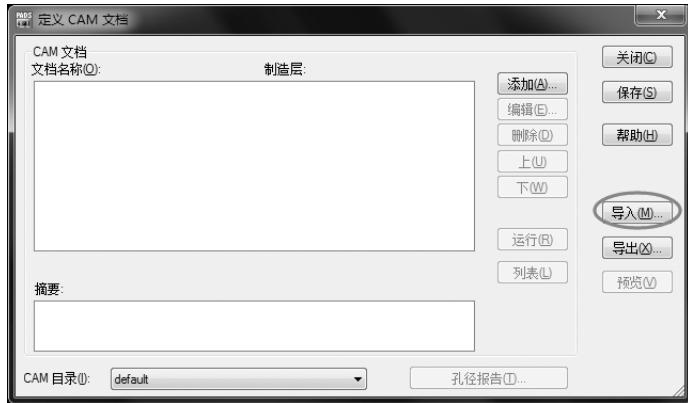

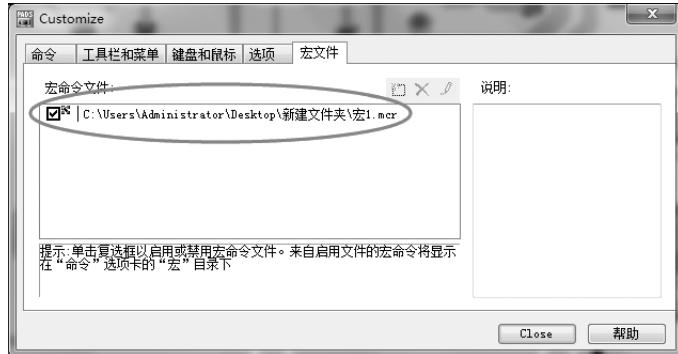

图 8-3 “ASCII 输出”对话框