# 单片机

## 控制技术及应用

李广军 纪娜 ◎ 主编

## 单片机控制技术及应用

主 编 李广军 纪 娜参 编 程晓辉 蒙 娟 宁玉红万 捷 孔 杰 赵海静

机械工业出版社

本书以80C51单片机为例,讲述了单片机控制技术及应用。内容包括单片机基础知识、结构与原理、指令系统、汇编语言设计、中断系统、定时器/计数器、串行通信、单片机的并行扩展技术及单片机 A-D、D-A 转换接口技术等。

本书可作为高职高专电子、通信、电气、机电专业单片机课程教材, 也可供从事单片机应用的工程技术人员参考,非常适合单片机爱好者自学 使用。

#### 图书在版编目 (CIP) 数据

单片机控制技术及应用/李广军等主编. 一北京: 机械工业出版社, 2013.11 北京劳动保障职业学院国家骨干校建设资助项目

ISBN 978-7-111-44921-8

I. ①单··· Ⅱ. ①李··· Ⅲ. ①单片微型计算机 – 计算机控制 – 高等职业教育 – 教材 Ⅳ. ①TP368. 1

中国版本图书馆 CIP 数据核字 (2013) 第 282894 号

机械工业出版社 (北京市百万庄大街 22 号 邮政编码 100037)

策划编辑:罗 莉 责任编辑:罗 莉 版式设计:常天培 责任校对:陈延翔 封面设计:赵颖喆 责任印制:李 洋

北京华正印刷有限公司印刷

2014年1月第1版第1次印刷

184mm×260mm・12 印张・295 千字

0001—3000册

标准书号: ISBN 978-7-111-44921-8

定价:39.00元

凡购本书, 如有缺页、倒页、脱页, 由本社发行部调换

电话服务 网络服务

社服务中心:(010)88361066 教材网:http://www.cmpedu.com

销售一部:(010)68326294 机工官网:http://www.cmpbook.com

销售二部:(010)88379649 机工官博:http://weibo.com/cmp1952

读者购书热线:(010)88379203 封面无防伪标均为盗版

## 前言

本书从社会需要和高等职业教育的特点出发,确定了教学目标:掌握单片机基本结构和原理、MCS-51系列单片机指令系统、汇编语言程序设计方法、单片机存储系统、输入/输出接口电路、定时器/计数器、中断系统、串行通信技术及模拟量输入/输出接口技术等。

本书以80C51单片机为例,讲述了单片机控制技术及应用。内容包括单片机基础知识、结构与原理、指令系统、汇编语言设计、中断系统、定时器/计数器、串行通信、单片机的并行扩展技术及单片机 A-D、D-A 转换接口技术等。

根据高职高专教育注重培养学生实践动手能力的要求,本书以单片机应用为主线,理论与实践紧密结合,注重对单片机资源应用方法的总结,使初学者更容易理解和掌握;每章包含相应的例题,以便使学生更深入学习理论知识,加强实际操作的练习,并安排了一定量的习题与思考题,方便读者练习和提高。

本书可作为高职高专电子、通信、电气、机电专业单片机课程教材,也可供从事单片机应用的工程技术人员参考,非常适合单片机爱好者自学使用。

本书由北京劳动保障职业学院机电工程系教师团队编写。李广军编写第1章和第2章;纪娜编写第3章;程晓辉编写第4章;蒙娟编写第5章;宁玉红编写第6章;万捷编写第7章;孔杰、赵海静编写第8章。全书由李广军统稿。

由于作者水平所限,书中可能会存在某些错误和不妥之处,恳请广大读者批评指正。

作 者

## 目 录

| 前言                                | 2.5 80C51 单片机的并行 I/O 口 24    |

|-----------------------------------|------------------------------|

|                                   | 2.5.1 PO、P2 口的结构 24          |

| 第 <b>1</b> 章 计算机运算基础 1            | 2.5.2 P1、P3 口的结构 26          |

| 1.1 计算机中的数制及数制的转换 1               | 2.5.3 并行口的负载能力 27            |

| 1.1.1 计算机中的数制 1                   | 2.5.4 并行口的应用举例 28            |

| 1.1.2 数制间的转换2                     | 2.6 80C51 单片机的时钟与复位 ····· 29 |

| 1.2 计算机中数的表示方法 4                  | 2.6.1 80C51 单片机的时钟 ····· 29  |

| 1.2.1 定点机中数的表示方法 4                | 2.6.2 80C51 单片机的定时单位 30      |

| 1.2.2 浮点机中数的表示方法 5                | 2.6.3 80C51 单片机的复位方式与        |

| 1.2.3 二进制数的运算6                    | 初始化状态 31                     |

| 1.3 计算机中数的表示形式 7                  | 2.6.4 80C51 单片机的复位电路 32      |

| 1.3.1 机器数的原码、反码和补码 7              | 本章小结                         |

| 1.3.2 计算机中二进制数的单位表示 8             | 习题 34                        |

| 1.3.3 计算机使用二进制数的原因 9              |                              |

| 1.4 计算机中使用的编码 9                   | 第3章 80C51的指令系统 35            |

| 本章小结                              | 3.1 指令概述 35                  |

| 习题 11                             | 3.1.1 汇编语言 35                |

|                                   | 3.1.2 指令格式 36                |

| 第 2 章 80 C51 的结构及原理 ·········· 12 | 3.1.3 常用符号 36                |

| 2.1 单片机的概述 12                     | 3.2 寻址方式 37                  |

| 2.1.1 单片机的定义 12                   | 3.2.1 立即寻址 37                |

| 2.1.2 单片机的特点 12                   | 3.2.2 直接寻址 38                |

| 2.1.3 单片机的发展 13                   | 3.2.3 寄存器寻址 38               |

| 2.1.4 单片机的应用 13                   | 3.2.4 寄存器间接寻址 39             |

| 2.2 80C51 单片机的逻辑结构 14             | 3.2.5 变址寻址 39                |

| 2.2.1 80C51 单片机的组成 14             | 3.2.6 相对寻址 … 40              |

| 2.2.2 中央处理单元 14                   | 3.2.7 位寻址 … 40               |

| 2.2.3 存储器 15                      | 3.2.8 寻址空间 … 41              |

| 2.2.4 输入/输出接口 16                  | 3.3 80C51 的指令系统 … 42         |

| 2.3 80C51 单片机的引脚及功能 16            | 3.3.1 数据传送指令 … 42            |

| 2.3.1 80C51 单片机的引脚封装 16           | 3.3.2 算术运算指令 … 48            |

| 2.3.2 80C51 单片机引脚及功能 17           | 3.3.3 逻辑运算指令 52              |

| 2.4 80C51 单片机的存储器组织 19            | 3.3.4 控制转移指令 55              |

| 2.4.1 80C51 单片机的程序存储器 19          | 3.3.5 位操作指令 61               |

| 2.4.2 80C51 单片机的数据存储器 20          | 本章小结63                       |

| 2.4.3 80C51 单片机的特殊功能              | 习题 68                        |

| 寄存器 21                            |                              |

| 第 <b>4</b> 章 汇编语言程序设计 ············ 71 | 5.5 定时器/计数器的四种工作方式及                      |

|---------------------------------------|------------------------------------------|

| 4.1 程序设计概述 71                         | 其应用 108                                  |

| 4.1.1 程序设计语言 71                       | 5.5.1 定时器/计数器的初始化 108                    |

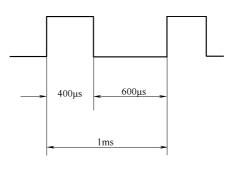

| 4.1.2 汇编语言源程序的编辑与汇编 72                | 5.5.2 方式 0 及应用实例 109                     |

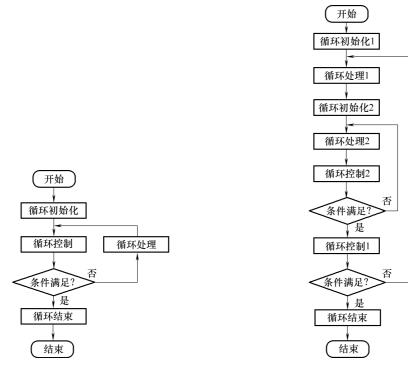

| 4.1.3 汇编语言程序的基本结构 75                  | 5.5.3 方式 1 及应用实例 111                     |

| 4.1.4 程序设计方法和技巧 75                    | 5.5.4 方式2及应用实例 112                       |

| 4.2 顺序程序设计 77                         | 5.5.5 方式3 115                            |

| 4.3 循环程序设计 78                         | 本章小结 116                                 |

| 4.3.1 循环程序设计方法 78                     | 习题116                                    |

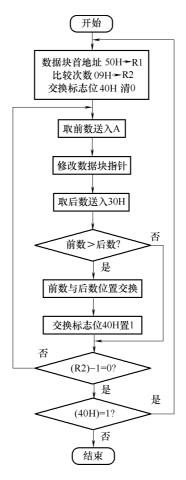

| 4.3.2 循环程序设计实例 79                     |                                          |

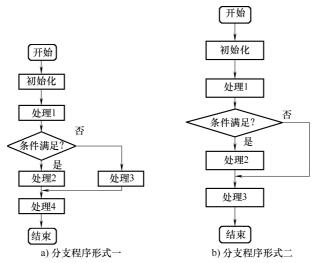

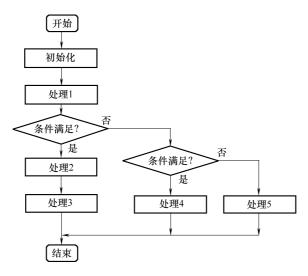

| 4.4 分支程序设计 84                         | 第 6 章 <b>80 C51</b> 单片机的串行通信 ····· 118   |

| 4.4.1 分支程序设计方法 84                     | 6.1 串行通信概述 118                           |

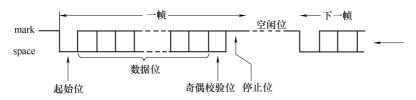

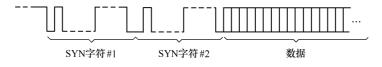

| 4.4.2 分支程序设计实例 85                     | 6.1.1 异步通信和同步通信 118                      |

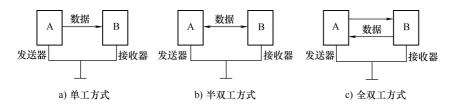

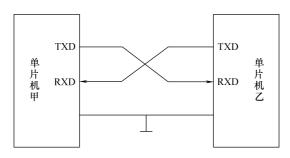

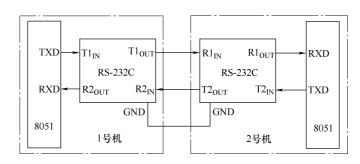

| 4.5 子程序设计 88                          | 6.1.2 串行通信的数据传送方式 120                    |

| 4.5.1 子程序设计方法 88                      | 6.2 80C51 串行通信 121                       |

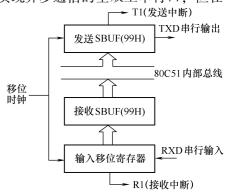

| 4.5.2 子程序设计实例 89                      | 6.2.1 80C51 单片机串行口结构 ······· 121         |

| 4.6 查表程序设计 90                         | 6.2.2 80C51 单片机串行口控制机制 ··· 122           |

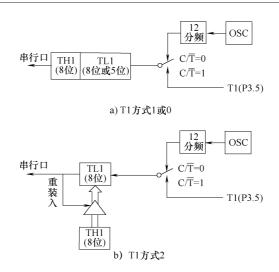

| 4.6.1 查表程序设计方法 90                     | 6.3 80C51 单片机串行口的工作方式 ····· 124          |

| 4.6.2 查表程序设计实例 90                     | 6.3.1 串行工作方式 0 124                       |

| 本章小结 91                               | 6.3.2 串行工作方式 1 125                       |

| 习题 91                                 | 6.3.3 串行工作方式 2 和 3 125                   |

|                                       | 6.4 串行通信数据传输速率                           |

| 第5章 80C51的中断系统及定时器/                   | 6.4.1 传输速率的表示方法 126                      |

| 计数器 93                                | 6.4.2 80C51 单片机波特率的设置 ····· 126          |

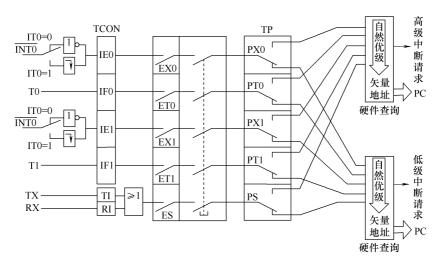

| 5.1 80C51 单片机的中断系统 93                 | 6.5 80C51 单片机串行通信的应用 ······· 127         |

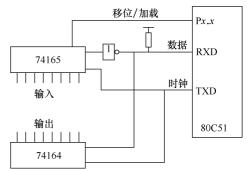

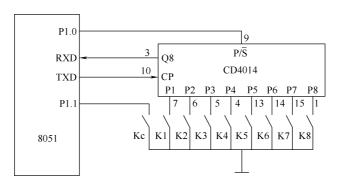

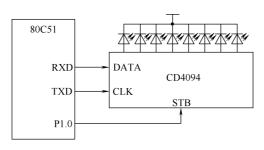

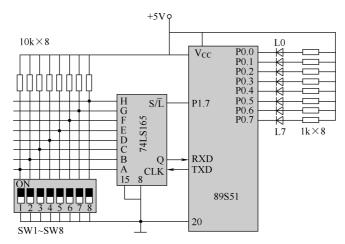

| 5.1.1 80C51 单片机中断的概念 93               | 6.5.1 单片机串行口扩展并行输入<br>输出口的应用 ······· 127 |

| 5.1.2 80C51 单片机的中断源及                  | 6.5.2 单片机与单片机之间的通信 ····· 12.5            |

| 中断向量 94                               | 本章小结                                     |

| 5.2 80C51 单片机中断系统的结构及                 | 习题                                       |

| 控制 95                                 | 13.                                      |

| 5. 2. 1 80C51 单片机中断系统的结构 ····· 95     | 第7章 并行扩展技术                               |

| 5.2.2 80C51 单片机中断系统的控制 95             | 7.1 扩展概述                                 |

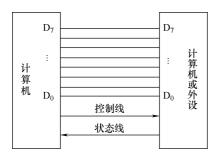

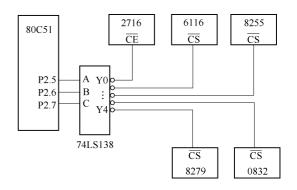

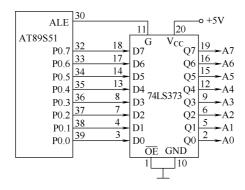

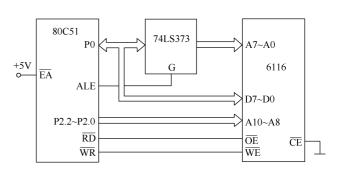

| 5.2.3 80C51 单片机中断系统的                  | 7.1.1 单片机并行扩展总线 135                      |

| 优先级控制 98                              | 7.1.2 并行扩展系统的 I/O 编址和                    |

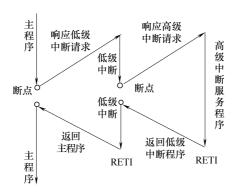

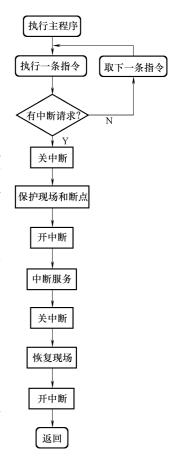

| 5.3 80C51 单片机中断处理过程 99                | 芯片选取 137                                 |

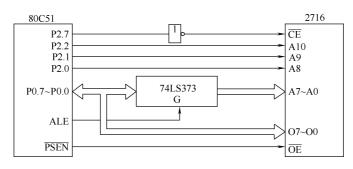

| 5.3.1 中断响应的条件 99                      | 7.2 存储器扩展技术 138                          |

| 5.3.2 中断响应的过程 100                     | 7. 2. 1 存储器的类型 138                       |

| 5.3.3 中断服务程序 101                      | 7.2.2 程序存储器扩展 140                        |

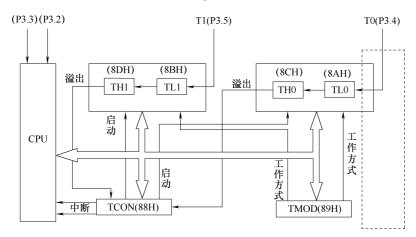

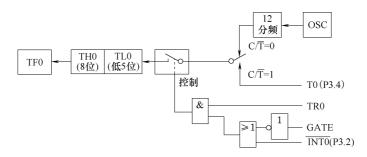

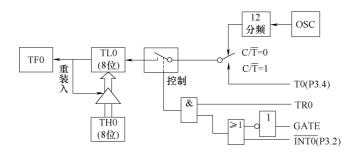

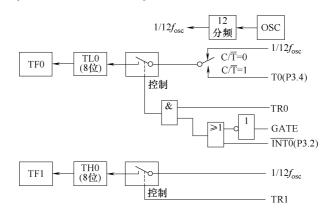

| 5.4 80C51 单片机的定时器/计数器 105             | 7. 2. 3 数据存储器扩展 143                      |

| 5.4.1 定时器/计数器的原理 105                  | 7.3 单片机并行 1/0 接口扩展 145                   |

| 5.4.2 定时器/计数器的应用 106                  | 7.3.1 单片机并行 I/O 接口扩展基础                   |

| 5.4.3 定时器/计数器的控制 106                  | 知识 145                                   |

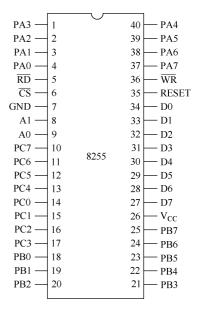

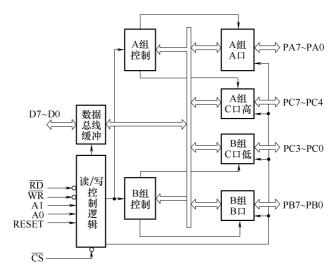

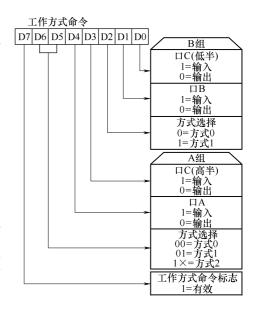

| 7.3.2 8255 可编程并行接口扩展 | 146 | 8.1 模拟  | 以量输入接口 (A-D转换)        | 170 |

|----------------------|-----|---------|-----------------------|-----|

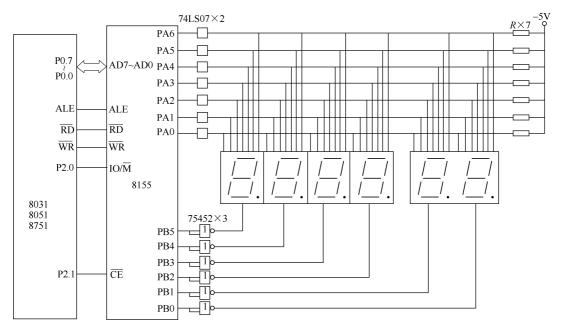

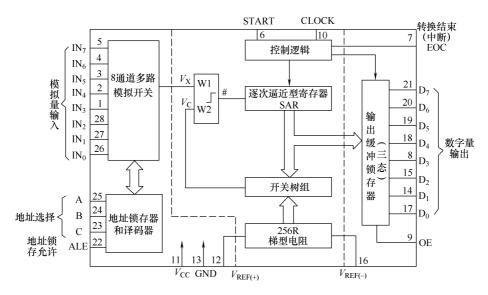

| 7.3.3 8155 可编程并行接口扩展 | 150 | 8. 1. 1 | A-D 转换器概述             | 170 |

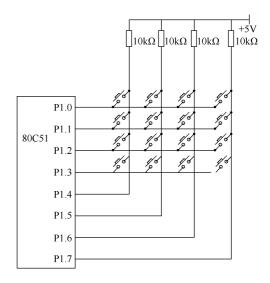

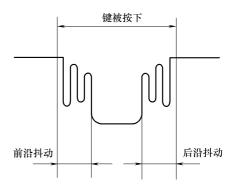

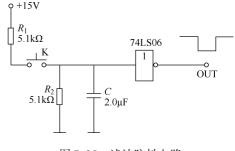

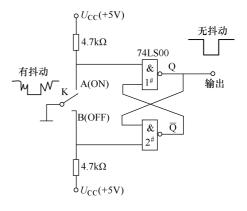

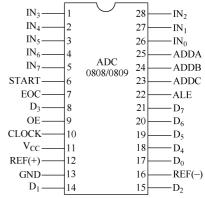

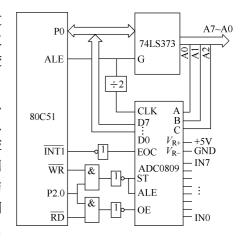

| 7.4 键盘接口技术           | 154 | 8. 1. 2 | 8 位 A-D 转换器芯片及与       |     |

| 7.4.1 键盘的结构          | 155 |         | 80C51 单片机的接口          | 171 |

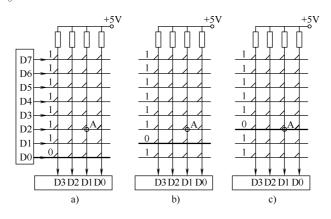

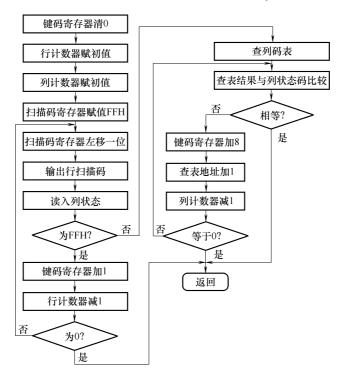

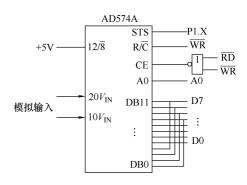

| 7.4.2 键码和键盘的扫描       | 157 | 8. 1. 3 | 高于8位A-D转换器芯片及与        |     |

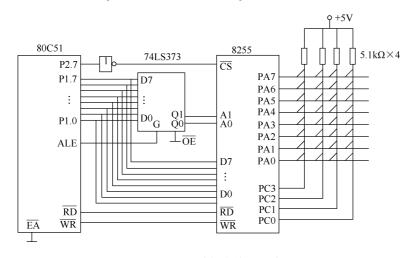

| 7.4.3 用 8255 实现键盘接口  | 160 |         | 80C51 单片机的接口          | 176 |

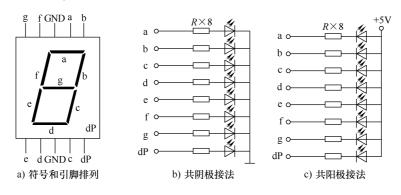

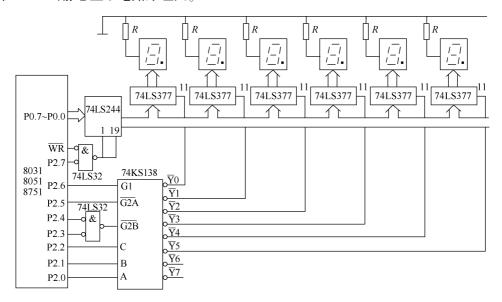

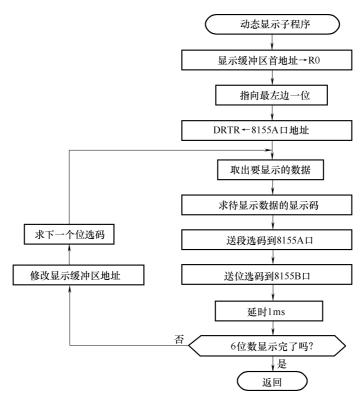

| 7.5 LED 显示接口技术       | 162 | 8.2 模拟  | 以量输出接口 (D-A转换)        | 176 |

| 7.5.1 LED 显示器概述      | 162 | 8. 2. 1 | D- A 转换器概述            | 176 |

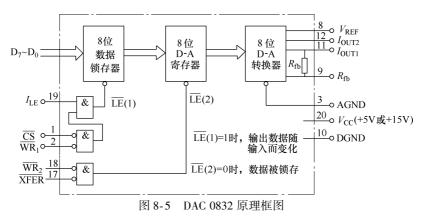

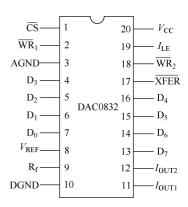

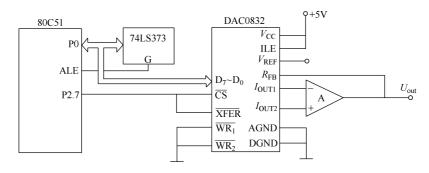

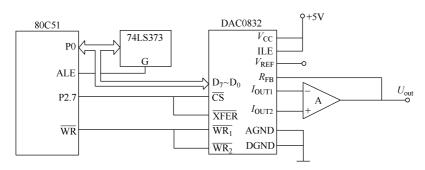

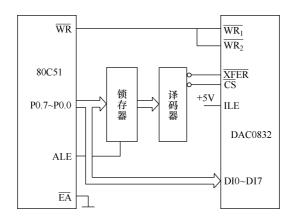

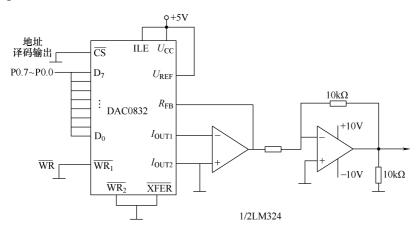

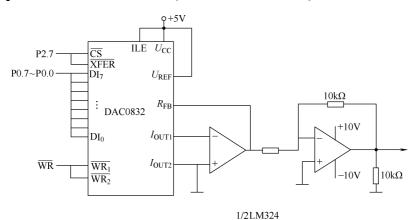

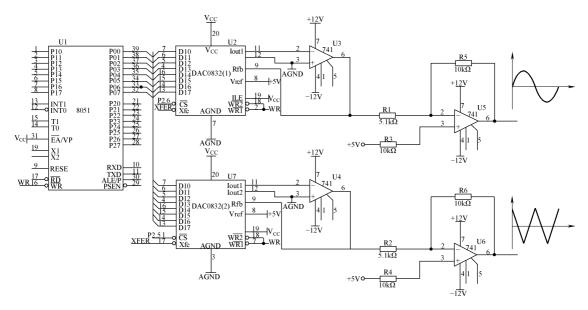

| 7.5.2 LED 显示器接口      | 164 | 8. 2. 2 | 8 位 D-A 转换器芯片及与 80C51 |     |

| 本章小结                 | 168 |         | 单片机的接口                | 177 |

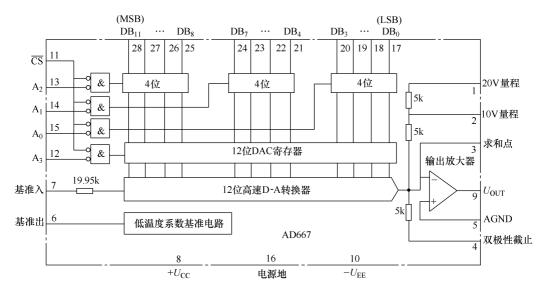

| 习题                   | 169 | 8. 2. 3 | 高于8位D-A转换器芯片及与        |     |

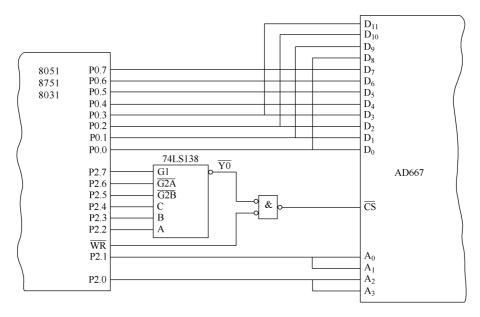

|                      |     |         | 80C51 单片机的接口          | 183 |

| 第 8 章 单片机 A-D 及 D-A  |     | 本章小结    |                       | 185 |

| 转换接口                 | 170 | 习题      |                       | 185 |

|                      |     |         |                       |     |

## 第1章 计算机运算基础

#### 【学习目的】

- 1. 了解计算机中的数制。

- 2. 掌握数制之间的转换。

- 3. 熟悉计算机中数的表示方法及数的表示形式。

电子计算机是一种能对信息加工处理的机器,具有记忆、判断和运算的能力。

#### 1.1 计算机中的数制及数制的转换

十进制是人们生活中普遍使用的计数制,但计算机都是以二进制形式进行算术运算和逻辑运算操作的,微型计算机也不例外。因此,对于用户在键盘上输入的十进制数字和符号命令,微型计算机必须先把它们转换成二进制形式进行识别、运算和处理,然后再把二进制形式的运算结果转换为人们容易识别的十进制数字和符号,并在显示器上显示出来。

上述过程都是由计算机自动完成的,在微型计算机中除了用到二进制和十进制的数制外,经常会用到八进制和十六进制的计数制,为了使读者弄清计算机中数制转换的原理,先对计算机中常用的数制和数制的转换进行讨论。

#### 1.1.1 计算机中的数制

所谓数制是指数的制式,是人们利用符号计数的一种科学方法。数制有很多种,微型计算机中常用的数制有十进制、二进制、八进制和十六进制等。

#### 1. 十进制 (Decimal)

十进制是人们生活中普遍使用的数制,它用0、1、2、…、9 这十个数来描述。十进制数的主要特点如下:

- ① 它有 0~9 十个不同的数,这是构成所有十进制数的基本符号。

- ② 它是逢 10 进位的。十进制数在计数过程中,当它的某位计满 10 时就要向它邻近的高位进 1。

#### 2. 二进制 (Binary)

- 二进制是在计算机系统中使用的数制,它用 0、1 这两个数来描述。二进制数的主要特点如下:

- ① 任何二进制数都是由 0、1 这两个数组成。

- ② 二进制数的基数为 2、它遵循逢 2 进 1 的进位计数原则。

- 3. 十六进制 (Hexadecimal)

十六进制是计算机指令代码和数据以及软件工具中经常使用的数制,它用 $0,1,\dots,9$ 和 $A,B,\dots,F$ 这十六个数和字母来描述。十六进制数的主要特点如下:

- ① 任何一个十六进制数都是由0、1、···、9和A、B、···、F这十六个数和字母构成。

- ② 十六进制数的基数为 16. 它遵循逢 16 进 1 的进位计数原则。

为方便起见,现将部分十进制、二进制和十六进制数的对照表列于表 1-1。

整 数 数 二进制 十 进 制 二进制 十 进 制 十六进制 十六进制 0 0000 0 0 0 1 0.5 0001 1 0.1 0.8 2 0.25 0010 2 0.01 0.4 3 0011 3 0.125 0.001 0.2 4 0100 4 0.0625 0.0001 0.1 5 0101 5 0.03125 0.00001 0.08 0110 0.015625 0.000001 0.04 7 0111 7 1000 8 1001 9 1010 10 Α 11 1011 В 1100 13 1101 D 14 1110 Ε 15 F 1111 16 10000 10

表 1-1 部分十进制、二进制和十六进制数的对照表

#### 1.1.2 数制间的转换

在计算机中都是以二进制数进行算术运算和逻辑运算操作的,而人们习惯使用十进制数,计算机会自动对不同数制的数进行转换。下面学习不同数制的数是如何转换的。

#### 1. 二进制数和十进制数间的转换

- (1) 二进制数转换成十进制数

- 二进制数转换成十进制数只要把欲转换数按权展开后相加即可。例如:

11010. 01B =

$$1 \times 2^4 + 1 \times 2^3 + 1 \times 2^1 + 1 \times 2^{-2} = 26.25$$

(2) 十进制数转换成二进制数

本转换过程是上述转换过程的逆过程,但十进制整数和小数转换成二进制整数和小数的 方法是不相同的,现分别进行介绍。

1) 十进制整数转换成二进制整数

常用的是"除2取余法"。用2连续去除要转换的十进制数,直到商小于2为止,然后把各次余数按最后得到的为最高位、最早得到的为最低位,依次排列起来所得到的数便是所求的二进制数。

答案: 100D = 1100100B

#### 2) 十进制小数转换成二进制小数

通常采用"乘2取整法"。用2连续去乘要转换的十进制小数,直到所得积的小数部分为0或满足所需精度为止,然后把各次整数按最先得到的为最高位、最后得到的为最低位,依次排列起来所对应的数便是所求的二进制小数,现结合实例加以介绍。

答案: 0.625D = 0.101B

#### 2. 二进制数与十六进制数的转换

#### 1) 二进制数转换为十六进制数

采用四位二进制数合成为一位十六进制数的方法,以小数点为界分成左侧整数部分和右侧小数部分;整数部分从小数点开始,向左每4位二进制数一组,不足4位在数的前面补0;小数部分从小数点开始,向右每4位二进制数一组,不足4位在数的后面补0,然后每组用十六进制数码表示,并按序相连即可。

【**例 1-3**】 把 111010. 011110B 转换为十六进制数。

#### 2) 十六进制数转换为二进制数

将十六进制数的每位分别用 4 位二进制数码表示,然后它们按序连在一起即为对应的二进制数。

#### 【**例 1-4**】 把 2BD4H 和 20.5H 转换为二进制数

2BD4H = 0010 1011 1101 0100B

20.5H = 00100000.0101B

#### 3. 十六进制数与十进制数的转换

(1) 十六进制数转换成十进制数

十六进制数转换成十进制数的方法和二进制数转换成十进制数的方法类似,将十六进制 数按权展开后求和即得到十进制数。

【**例 1-5**】 将十六进制数 3DF2H 转换成十进制数。

$3DF2H = 3 \times 16^3 + 13 \times 16^2 + 15 \times 16^1 + 2 \times 16^0 = 15858$

- (2) 十进制数转换成十六进制数

- ① 十进制整数转换成十六进制整数与十进制整数转换成二进制整数类似,十进制整数转换成十六进制整数可以采用"除 16 取余法"。用 16 连续去除要转换的十进制整数,直到商数小于 16 为止,然后把各次余数按逆得到顺序排列起来所得的数,便是所求的十六进制数。

- ② 十进制小数转换成十六进制小数的方法类似十进制小数转换成二进制小数,常采用 "乘 16 取整法"。把欲转换的十进制小数连续乘以 16,直到所得乘积的小数部分为 0 或达到 所需精度为止,然后把各次整数按相同的得到顺序排列起来所得的数,便是所求的十六进制 小数。

#### 1.2 计算机中数的表示方法

在讨论计算机如何对有符号数或无符号数进行运算和处理之前,先弄清计算机中数的表示方法是十分必要的。在计算机中,小数和整数都是以二进制形式表示的,但对小数点通常有定点和浮点两种表示方法。小数点采用定点表示法的称为定点机,采用浮点表示法的叫做浮点机。

#### 1.2.1 定点机中数的表示方法

在定点计算机中,二进制数的小数点位置是固定不变的,小数点位置可以固定在数值位之前,也可以固定在数值位之后。前者称为定点小数计算机,后者叫做定点整数计算机。

在理论和习惯上,小数点固定在中间位置比较合适,但因为它所能表示的数既有整数又有小数部分,会给数在数制间替换带来麻烦,故这种方法通常并不为计算机设计师们所采用。

#### 1. 定点整数表示法

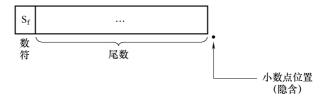

在采用定点整数表示法的计算机中,小数点位置被固定在数值位之后。因此,这种计算机在实际运算前应先把参加运算的数 (二进制形式)按适当比例替换成纯整数,并在运算后把结果操作数按同一比例还原后输出。设 N 为某一定点二进制整数,其表示形式为

其中,  $S_f$  为数符,  $S_f = 0$  表示 N 为正数,  $S_f = 1$  表示 N 为负数。

数的表示形式在大多数计算机中都是采用定点整数法,MCS-51 单片机也是一种定点整数计算机。因此,MCS-51 单片机只能对二进制整数进行直接运算和处理,它在遇到二进制小数时,必须把该小数按比例扩大成二进制整数后进行处理,并在处理完后再按同样比例缩小后进行输出。

定点整数表示法的优点是,运算规则简单,它所能表示的数的范围没有相同位数的浮点 法大。例如,一个 16 位的二进制定点整数 N,若它的  $S_r$  占 1 位、尾数占 15 位,则它所能表示的原码数的范围为

$$|N| \le 11 \cdots 11 = 100 \cdots 00 - 1 = 2^{15} - 1$$

,近似形式为  $-2^{15} \le N2^{15}$

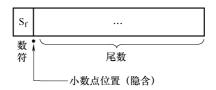

#### 2. 定点小数表示法

在采用定点小数表示法的计算机中,小数点的位置被固定在数值位之前。因此,这种计算机在实际运算前应首先把参加运算的二进制整数按适当比例替换成纯小数,并在运算结束后把结果操作数(纯小数)按同样比例逆替换后输出。设N为定点小数,其表示形式为

其中,  $S_f$  为数符,  $S_f = 0$  表示 N 为正数,  $S_f = 1$  表示 N 为负数。

定点小数表示法的优点是,运算规则简单,但它所能表示的数的范围较小。例如,一个 16 位的二进制小数 N, 若它的  $S_i$  占 1 位、尾数占 15 位,则它所能表示的原码数范围为

$$|N| \le 0.11 \cdots 11 = 1 - 0.00 \cdots 01 = 1 - 2^{-15}$$

$\mathbb{E}[1 - (1 - 2^{-15})] \leq N \leq (1 - 2^{-15})$

#### 1.2.2 浮点机中数的表示方法

在采用浮点表示的二进制数中,小数点位置是浮动的、不固定的。 通常,任意一个二进制数都可以写为

$$N = 2^P \times S$$

式中, S 为二进制数 N 的尾数, 代表了 N 的实际有效值; P 为 N 的阶码, 可以决定小数点的具体位置。例如:  $N=101.11B=2^3\times0.10111B$ 。

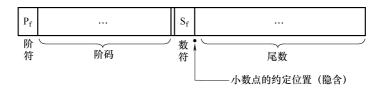

因此,任何一个浮点数N都由阶码和尾数两部分组成。阶码部分包括阶符和阶码,尾数部分由数符和尾数组成,其形式为

其中,  $P_f$  为阶符,  $P_f = 0$  表示阶码为正,  $P_f = 1$  表示阶码为负;  $S_f$  为数符,  $S_f = 0$  表示该数为正数,  $S_f = 1$  表示该数为负数; 小数点的约定位置在尾数之前,实际位置是浮动的,由阶码

决定。浮点法的优点是,数的表示范围大。浮点表示法的缺点是,运算规则复杂,通常要对 阶码和尾数分别运算。

#### 1.2.3 二进制数的运算

- 二进制数的运算分为二进制整数运算和二进制小数运算两种类型,但运算法则完全相同。由于大部分计算机中数的表示方法均采用定点整数表示法,故这里仅介绍二进制整数运算,二进制小数运算与它相同。

- 二进制数的运算比较简单,包括算术运算和逻辑运算。算术运算包括加、减、乘、除运算;逻辑运算包括逻辑乘、逻辑加、逻辑非和逻辑异或等。

#### 1. 二进制数的算数运算

(1) 加法运算

运算规则为

(2) 减法运算

运算规则

$$0-0=0$$

;  $1-0=1$ ;  $1-1=0$ ;  $0-1=1$  (向高位借1)

(3) 乘法运算

运算规则

$$0 \times 0 = 0$$

;  $0 \times 1 = 1 \times 0 = 0$ ;  $1 \times 1 = 1$

#### (4) 除法运算

除法是乘法的逆运算。与十进制类似,二进制除法也是从被除数最高位开始,查找出够减除数的位数,并在其最高位处上商1和完成它对除数的减法运算,然后把被除数的下一位移到余数位置上。若余数不够减除数,则上商0,并把被除数的再下一位移到余数位置上;若余数够减除数,则上商1并进行余数减除数。这样反复进行,直到全部被除数的各位都下移到余数位置上为止。

#### 2. 逻辑运算

计算机处理数据时常常要用到逻辑运算。逻辑运算由专门的逻辑电路完成。下面介绍几 种常用的逻辑运算。

(1) 逻辑乘运算

逻辑乘又称逻辑与,常用 / 算符表示。逻辑乘运算法则为

$$0 \land 0 = 0$$

;  $1 \land 0 = 0 \land 1 = 0$ ;  $1 \land 1 = 1$

(2) 逻辑加运算

逻辑加又称逻辑或、常用算符 \ 表示。逻辑加的运算规则为

$$0 \lor 0 = 0$$

:  $1 \lor 0 = 0 \lor 1 = 1$ :  $1 \lor 1 = 1$

(3) 逻辑非运算

逻辑非运算又称逻辑取反,常采用"-"运算符表示。逻辑非的运算规则为

$$\overline{0} = 1$$

:  $\overline{1} = 0$

(4) 逻辑异或

逻辑异或又称为半加,是不考虑进位的加法,常采用算符表示。逻辑异或的运算规则为

$0 \oplus 0 = 0$ ;  $1 \oplus 1 = 0$ ;  $1 \oplus 0 = 0 \oplus 1 = 1$

#### 1.3 计算机中数的表示形式

在现代微型机中,其内部运算器通常由一个补码加法器、n 位寄存器/计数器组和移位控制电路等组成,但它恰能进行各种算术运算和逻辑操作。这就是说,补码加法器既能做加法又能将减法运算变为加法来做,从而大大简化了运算器内部的电路设计。这应归功于人们长期以来对计算机中码制的研究。

机器数是指数的符号和值均采用二进制的表示形式。因此,机器数在定点和浮点机中的表示形式各不相同。为了方便起见,这里的机器数均指在定点整数机中的表示形式。即最高位是符号位(0表示正数,1表示负数),其余位为数值位,小数点约定在数值位之后。在计算机中,机器数有原码、反码、补码、变形原码、变形反码、变形补码和移码等多种形式。

#### 1.3.1 机器数的原码、反码和补码

原码、反码和补码是机器数的三种基本形式,它和机器数的真值不同。机器数的真值定义为采用+和-表示的二进制数符号,并非是真正的机器数。例如,+76的机器数真值为+1001100B,原码形式为01001100B(最高位的0表示正数);-76的真值为-1001100B,原码为11001100B(最高位的1表示负数)。

#### 1. 原码

原码表示法是机器数的一种简单的表示法。这种表示法数的最高位为符号位(用 0 或 1 来表示),其余位为数值位,符号位的 0 表示该数为正数,符号位为 1 表示它是负数。通常,一个数的原码可以先把该数用方括号括起来,并在方括号右下角加个"原"字来标记。设有一数为 x,则原码表示可记作 [x] 。

【例 1-6】 设 X1 = +1100B, X2 = -1100B, 请分别写出它们在 8 位微机中的原码。

解: 其原码记为

$$[X1]_{\mathbb{R}} = [00001100]_{\mathbb{R}}$$

$[X2]_{\mathbb{R}} = [10001100]_{\mathbb{R}}$

原码表示数的范围与二进制位数有关。当用8位二进制来表示小数原码时,其表示范围为

最大值为 0.1111111, 其真值约为 (0.99) D

最小值为 1.1111111, 其真值约为 (-0.99) D

当用8位二进制来表示整数原码时,其表示范围为

最大值为01111111, 其真值为(127)D

最小值为11111111, 其真值为(-127)D

在原码表示法中,对0有两种表示形式:

$[ +0]_{\text{\tiny \Bar{\tiny \it E}}} = 00000000$

$[-0]_{\text{IF}} = 10000000$

#### 2. 反码

在微型计算机中,二进制数的反码可由原码得到,有正数的反码和负数的反码之分:正数的反码和原码相同;负数反码的符号位和负数原码的符号位相同,数值位是它的数值位的按位取反。反码的标记方法和原码类似,只要在被括数方括号的右下角添加一个"反"字即可。设有一数为 x,则反码表示可记作 [x]。

【**例 1-7**】 设 X1 = +1010110,X2 = -1001010,请分别写出它们在 8 位微机的原码和反码。

解:由于正数的反码就是其原码;负数的反码是符号位不变,数值位是它的数值位的按 位取反,所以有

$[X1]_{\mathbb{R}} = 01010110$

$[X1]_{\text{g}} = [X1]_{\text{g}} = 01010110$

$[X2]_{\text{if}} = 11001010$

$[X2]_{\mathbb{R}} = 10110101$

反码通常作为求补过程的中间形式,即在一个负数的反码的末位上加1,就得到了该负数的补码。

#### 3. 补码

补码的概念是在计算机中经常会遇到的,二进制数的补码可由反码得到,如果是正数,则该机器数的补码与原码一样;如果是负数,则该机器数的补码是对它的原码(除符号位外)各位取反,并在末位加1而得到的。补码的标记方法和原码、反码类似,只要在被括数方括号的右下角添加一个"补"字即可。设有一数 X,则 X 的补码表示记作 [X]

【**例 1-8**】 设 X1 = +1010B, X2 = -01010B, 试分别写出它们在 8 位微机中的原码、反码和补码形式。

解:由原码、反码和补码的定义得

补码的优点是可以将减法运算转换为加法运算,其符号位可以连同数值位一起运算。这 样非常有利于计算机的实现。

【**例 1-9**】 45H, -55H, 用补码运算的方法求两数之和。

**M**:  $[45H]_{*}$  -  $[-55H]_{*}$  =  $[-10H]_{*}$

#### 1.3.2 计算机中二进制数的单位表示

在计算机中使用的二进制数共有3个单位,从小到大依次为位、字节和字。

**1.** 位 (bit)

这里所说的位是指二进制数的位。位是数的最小单位, bit 是位的英文名称, 读作"比特"。

在计算机中位仅有0和1两个数值,表示两种状态。

#### 2. 字节 (Byte)

8 位二进制数称为一个字节, 其英文名称是 Byte, 在使用时常用大写字母 B 表示。字节

是最基本的数据单位、计算机中的数据、代码、指令、地址多以字节为单位。

#### 3. 字 (Word)

字是一台计算机上所能并行处理的二进制数,字的位数(或长度)称之为字长。字长必须是字节的整数倍。例如,MCS-51单片机字长为8位,MCS-96单片机字长为16位,还有32位、64位字长的计算机。

#### 1.3.3 计算机使用二进制数的原因

为什么在计算机中要使用二进制数呢? 其原因主要有以下几点:

#### 1. 易于实现

在计算机中,数是用不同的物理状态来表示的。因为二进制数只有两个数字 0 和 1,用 两种物理状态就可以表示出来。而两种相反的物理状态在技术上极易实现。例如,开关的接通与断开,晶体管的导通与截止,电平的高低,脉冲的有无等。

对于这样两种截然相反的物理状态,不但易于实现,而且状态稳定可靠。而两种以上的物理状态,不但难以实现,而且稳定性也差。

#### 2. 运算简单

因为二进制数只有两个数字,所以对二进制数的运算比人们熟悉的十进制数的运算要简单得多,而运算简单将有利于简化计算机的电路结构。

#### 3. 具有逻辑属性

由于二进制数的0和1正好与逻辑值的"假(F)"和"真(T)"相对应,因此可以使用二进制数实现逻辑运算,从而使逻辑代数运算成为可能。

#### 4. 可靠性高

由于二进制数用两种截然相反的物理状态表示,十分稳定。因此二进制数的处理、存储和传送都最为可靠。

#### 1.4 计算机中使用的编码

计算机中除了使用数以外,还使用编码。可以把编码分为两类:一类是数的编码,另一类是文字符号的编码。因为是在计算机中使用,所以编码必须是二进制数。

#### 1. 二一十进制编码

在计算机中最常用的是用二进制数给十进制数编码,即通常所说的二-十进制编码。若要给一位十进制数编码,则须用4位二进制数。在二-十进制编码中最常用的是BCD码。

BCD 码共有 10 个编码,即二进制数 0000~1001,分别对应十进制数 0~9。例如,十进制数 3 的 BCD 码是 0011;9 的 BCD 码是 1001;39 的 BCD 码是把 3 和 9 的 BCD 码连在一起,即 00111001,正好为 1 个字节。BCD 码的特点是,4 位之内为二进制关系,每 4 位之间为十进制关系。

定义 BCD 码是为了便于在计算机中使用人们最熟悉的十进制数,特别是在输入与输出操作中。例如,从键盘输入的十进制数到计算机中就变为 BCD 码形式,当然这需要有相应的转换程序。有了十进制数的输入和输出,在计算机中就会存在十进制数的存储和计算。但十进制数计算存在调整问题,即所谓的十进制调整,以解决 BCD 码运算时因进位和借位产

生的偏差。

#### 2. ASCII 码

文字符号代码用于在计算机中表示西文字符、汉字以及各种符号,最常用的文字符号代码是 ASCII 码和汉字国标码。这里只介绍 ASCII 码。

ASCII 代表的是"美国信息交换标准代码"。它原是美国的字符代码标准,于 1968 年发表,由于使用广泛,早已被国际标准化组织确定为国际标准,成为计算机领域中最重要的代码。

ASCII 码表见表 1-2。

| $\begin{array}{c} b_6 b_5 b_4 \\ b_3 b_2 b_1 b_0 \end{array}$ | 000 | 001 | 010 | 011 | 100 | 101 | 110 | 111 |

|---------------------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|

| 0000                                                          | NUL | DLE | SP  | 0   | @   | P   | `   | p   |

| 0001                                                          | SOH | DC1 | !   | 1   | A   | Q   | a   | q   |

| 0010                                                          | STX | DC2 | "   | 2   | В   | R   | b   | r   |

| 0011                                                          | ETX | DC3 | #   | 3   | С   | S   | c   | s   |

| 0100                                                          | EOT | DC4 | \$  | 4   | D   | Т   | d   | t   |

| 0101                                                          | ENQ | NAK | %   | 5   | E   | U   | e   | u   |

| 0110                                                          | ACK | SYN | &   | 6   | F   | V   | f   | v   |

| 0111                                                          | BEL | ETB | •   | 7   | G   | W   | g   | w   |

| 1000                                                          | BS  | CAN | (   | 8   | Н   | X   | h   | x   |

| 1001                                                          | HT  | EM  | )   | 9   | I   | Y   | i   | у   |

| 1010                                                          | LF  | SUB | *   | :   | J   | Z   | j   | z   |

| 1011                                                          | VT  | ESC | +   | ;   | K   | [   | k   | {   |

| 1100                                                          | FF  | FS  | ,   | <   | L   | \   | 1   | I   |

| 1101                                                          | CR  | GS  | -   | =   | M   | ]   | m   | }   |

| 1110                                                          | so  | RS  |     | >   | N   | ^   | n   | ~   |

| 1111                                                          | SI  | US  | /   | ?   | 0   | _   | o   | DEL |

表 1-2 ASCII 码表

ASCII 码中字符和功能符号共计 128 个: 其中字符 94 个,包括十进制数字 10 个,英文 小写字母 26 个,英文大写字母 26 个,标点符号及专用符号 32 个,功能符 34 个 (字符区首 尾两个符号 SP 和 DEL 一般归入功能符)。由于  $2^7$  = 128,因此 128 个字符和功能符使用 7 位二进制数就可以进行编码,此编码即为 ASCII 码。

ASCII 码表是一个 16 行  $\times$  8 列的矩阵,其中行为编码中的后 4 位二进制数( $b_3b_2b_1b_0$ ),列为编码中的前 3 位二进制数( $b_6b_5b_4$ ),合在一起为 7 位二进制编码。例如,字符 A 的编码为 1000001。

为了方便,常用十进制数或十六进制数来表示 ASCII 码。例如,字符 A 的 ASCII 码用十进制数表示为 65,用十六进制数表示为 41 H。

7 位 ASCII 码结构是基本 ASCII 码,由于在计算机中常用字节(8 位)来表示数据。因此,为凑成一个字节,应在 ASCII 码的最高位补 1 个 0。

#### 本章小结

在计算机中常用的数制有十进制、二进制和十六进制。不同数制之间的转换都有一定的 规则,如二进制数转换成十六进制数采用"四位合一位"法,十六进制数转换成二进制数 采用"一位分四位"法、十进制整数转换成二进制整数采用"除2取余"法、十进制整数 转换成十六进制整数采用"除16取余"法、十进制小数转换成二进制小数采用"乘2取 整"法、十进制小数转换成十六进制小数采用"乘 16 取整"法。

有符号二进制数有三种表示法,即原码、反码和补码。在计算机中有符号数一般用补码 表示,无论是加法还是减法都可采用加法运算,而且是连同符号位一起进行的,运算的结果 仍为补码。

BCD 码的加减法运算与十进制运算规则相同,但必须对运算结果进行修正。ASCII 码是 国际通用的标准编码,采用7位二进制编码,分为图形字符和控制字符两类,共128个 字符。

#### ⋾ 题

- 1. 十进制和二进制数各有什么特点?请举例加以说明。

- 2. 为什么微机要采用二进制?

- 3. 把下列十进制数转换为二进制数和十六进制数:

- ① 135 ② 0.625 ③ 47.6875 ④ 0.94 ⑤ 111.111 ⑥ 1995.12

- 4. 把下列二进制数转换为十进制数和十六进制数。

- ① 11010110B

- ② 1100110111B

- ③ 0. 1011B

- ④ 0. 10011001B

- ⑤ 1011. 1011B

- ⑥ 111100001111. 11011B

- 5. 把下列十六进制数转换成十进制数和二进制数:

- ① AAH ② BBH ③ C. CH ④ DE. FCH ⑤ ABC. DH ⑥ 128. 08H

- 6. 先把下列十六进制数变成二进制数, 然后分别完成逻辑乘、逻辑加和逻辑异或操作, 应写出竖式:

- ① 33H 和 BBH ② ABH 和 7FH ③ CDH 和 80H ④ 78H 和 0FH

- 7. 先把下列各数变成 8 位二进制数 (含符号位), 然后按补码运算规则求 \ [X+Y\]补及其真值:

- ② X = +78 ③ X = +112 ④ X = -51

- 8. 请写出下列各十进制数在8位定点整数机中的原码、反码和补码形式(最高位为符号位):

- 3 X = -54 4 X = -115(1) X = +38 (2) X = +76

- 9. 写出下列各数的 BCD 码:

- ① 47 ② 59 ③ 1996 ④ 1997. 6

- 10. 用十六进制形式写出下列字符的 ASCII 码:

- (1) AB8 (2) STUDENT (3) COMPUTER (4) GOOD

## 第2章 80C51的结构及原理

#### 【学习目的】

- 1. 了解 80C51 的内部结构。

- 2. 掌握80C51 引脚信号功能定义。

- 3. 掌握80C51的存储器空间分配及各I/O口的特点。

- 4. 掌握80C51的复位电路、时钟电路及指令时序。

美国英特尔 (intel) 公司生产的 MCS-51 系列单片机具有典型的硬件结构和完善的指令系统,为单片机的发展奠定了良好的基础。众多单片机芯片的厂商都以它为基核,开发出具有不同功能和应用场合的单片机,为单片机的使用者提供了更多的选择余地。本书所介绍的80C51 型单片机是 MCS-51 系列单片机的典型产品。

#### 2.1 单片机的概述

#### 2.1.1 单片机的定义

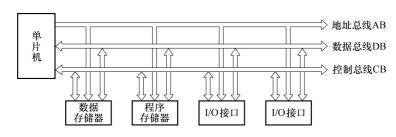

微型计算机的发展,促进了工业控制领域的进步。目前,已有各种各样的微型计算机控制系统在工业中得到应用。一个微型计算机包括微处理器(CPU)、存放程序指令存储器(ROM)和存放数据的存储器(RAM)、输入/输出端口(I/O端口)及时钟、计数器和中断等。它们经过地址总线(Address Bus)、数据总线(Data Bus)和控制总线(Control Bus)的连接以及输入/输出端口与外围设备连接,构成微机系统。由于单片微处理器集成了计算机的主要器件,所以把单片微处理器看做一个微型计算机,简称单片机(Single Chip Microcomputer)。

#### 2.1.2 单片机的特点

单片机是微型计算机的一个重要分支,它是工业控制和智能化系统中应用最多的一种微机。它的最大特点是设计者可以根据自己的实际需要开发、设计一个单片机系统,更加方便、灵活,且成本低。

单片机就是计算机,由于计算机的特殊结构,其具有如下特点:

- ① 体积小、重量轻。

- ② 电源单一、功耗低 (突出特点)。

许多单片机可在 2.2V 的电压下工作,有的能在 1.2V 或 0.9V 电压下工作,功耗降为 μA 级。

- ③ 功能强、价格低,有优异的性能价格比。

- ④ 全部集成在芯片上,布线短、合理、集成度高。

⑤ 数据大部分在单片机内传递,运行速度快,抗干扰能力强,可靠性高。

#### 2.1.3 单片机的发展

单片机自问世以来,性能不断提高和完善,不仅能满足很多应用场合的需要,而且具有集成度高、功能强、速度快、体积小、功耗低、使用方便、性能可靠、价格低廉等特点,因此,在工业控制、智能仪器仪表、数据采集和处理、通信系统、网络系统、汽车工业、国防工业、高级计算器具、家用电器等领域的应用日益广泛,并且正在逐步取代现有的多片微机应用系统,单片机的潜力越来越被人们所重视。特别是当前用 CMOS 工艺制成的各种单片机,由于功耗低,使用的温度范围大、抗干扰能力强、能满足一些特殊要求的应用场合,更加扩大了单片机的应用范围,也进一步促进了单片机技术的发展。

单片机的发展主要经历了3个阶段(美国 intel 公司)。

第1阶段(1971~1978年):初级单片机阶段,以MCS-48系列为代表。有4位、8位CPU,并行I/O口,8位定时器/计数器,无串行口,中断处理比较简单,RAM、ROM容量较小,寻址范围不超过4KB。

第 2 阶段 (1978~1983 年): 单片机普及阶段,以 MCS-51 系列为代表。是 8 位 CPU,片内 RAM、ROM 容量加大,片外寻址范围可达 64KB,增加了串行口,多级中断处理系统,16 位定时器/计数器。

第 3 阶段 (1983 年以后): 16 位单片机阶段,以 MCS-96 系列为代表。是 16 位 CPU, 片内 RAM、ROM 容量进一步增大,增加了 A-D 和 D-A 转换器,8 级中断处理功能,实时处理能力更强。它允许用户采用面向工业控制的专用语言,如 C 语言等。

总之,单片机发展可归结为以下几个方面:

- ① 增加字长、提高数据精度和处理的速度。

- ② 改进制作工艺,提高单片机的整体性能。

- ③ 由复杂指令集 CISC 转向简单指令集 RISC 技术。

- ④ 多功能模块集成技术, 使一块"嵌入式"芯片具有多种功能。

- ⑤ 微处理器与 DSP 技术相结合。

- ⑥ 融入高级语言的编译程序。

- ⑥ 低电压、宽电压、低功耗。

目前,国际市场上8位、16位单片机系列已有很多,32位的单片机也已经进入了实用阶段。随着单片机技术的不断发展,新型单片机还将不断涌现,单片机技术正以惊人的速度向前发展着。

#### 2.1.4 单片机的应用

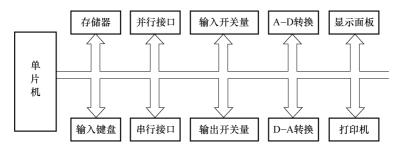

单片机是在芯片上集成了微型计算机所需的 CPU、存储器、输入/输出部件和时钟电路等。因此它具有体积小、使用灵活、成本低、易于产品化、抗干扰能力强、可在各种恶劣环境下可靠地工作等特点。特别是它应用面广,控制能力强,使它在工业控制、智能仪表、外设控制、家用电器、机器人、军事装置等方面得到了广泛的应用。单片机主要可用于以下几方面:

#### 1. 家用电器

已广泛应用于家用电器的自动控制中,如洗衣机、空调机、电冰箱、彩色电视机、录像机、VCD、音响设备和手机等。单片机的使用提高了家用电器的性能和质量,降低了家用电器的生产成本和销售价格。

#### 2. 智能卡

尽管目前使用的各种卡主要是磁卡和 IC 卡,但是,带有 CPU 和存储器的智能卡,已经 并将日益广泛用于金融、通信、信息、医疗保健、社会保险、教育、旅游、娱乐和交通等各 个领域。

#### 3. 智能仪器仪表

单片机体积小、耗电少,被广泛用于各类仪器仪表,如智能电表、智能流量计、气体分析仪、智能电压电流测试仪和智能医疗仪器等。单片机使仪器仪表走向了智能化和微型化,使仪器仪表的功能和可靠性大大提高。

#### 4. 网络与诵信

许多型号的单片机都有通信接口可方便地进行机间通信,也可方便地组成网络系统,如 单片机控制的无线遥控系统、列车无线通信系统和串行自动呼叫应答系统等。

#### 5. 工业控制

单片机可以构成各种工业测控系统、数据采集系统,如数控机床、汽车安全技术检测系统、报警系统和生产过程自动控制等。

#### 2.2 80C51 单片机的逻辑结构

#### 2.2.1 80C51 单片机的组成

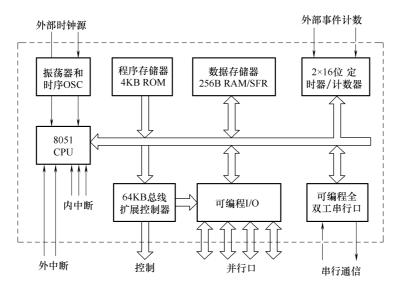

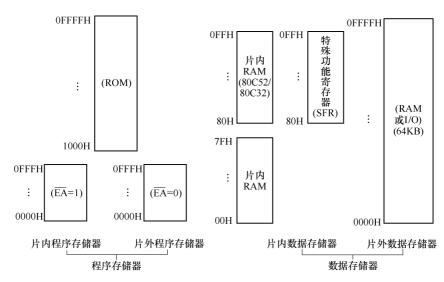

单片机芯片上集成了微型计算机的 5 个组成部分,单片机的片内结构框图如图 2-1 所示。它主要由以下几部分组成:8 位的微处理器 CPU,内含布尔处理器,一个片内振荡器和时钟电路;数据存储器 RAM,程序存储器 ROM;定时器/计数器;串行通信接口;64KB总线扩展控制器和 4 个并行 I/O 接口等。MCS-51 单片机片内总体结构框图如图 2-1 所示。

#### 2.2.2 中央处理单元

中央处理单元 (CPU) 是 MCS-51 单片机核心部分,主要由运算器和控制器两部分构成。它的工作过程是,取指令→分析指令→根据指令的功能控制单片机的各功能部件执行指定的运算或操作,如此循环往复。

#### 1. 运算器

运算器由算术/逻辑运算单元 ALU、累加器 ACC、寄存器 B、暂存寄存器、程序状态字寄存器 PSW 组成。它所完成的任务是实现算术与逻辑运算、位变量处理和数据传送等操作。

- 1) 算术/逻辑运算单元 ALU 可以实现 8 位数据的加、减、乘、除算术运算和与、或、 异或、循环、取反等逻辑运算,同时还具有一般微处理器所不具备的位处理功能。

- 2) 累加器 ACC 的作用是向 ALU 提供操作数和存放运算的结果。同一般微机一样, MCS-51 单片机在结构上也是以累加器 ACC 为中心, 大部分指令的执行都要通过累加器

图 2-1 MCS-51 单片机片内总体结构框图

ACC 进行。在运算时将累加器 ACC 中的一个操作数经暂存器 2 送至 ALU,与另一个来自暂存器 1 的操作数在 ALU 中进行运算,运算后的结果又送回累加器 ACC。

- 3)寄存器 B 作为通用的寄存器使用。另外在乘、除运算时用来存放一个操作数,也用来存放运算后的一部分结果。

- 4) 暂存寄存器用来暂时存放数据总线或其他寄存器送来的操作数。它作为 ALU 的数据输入源,向 ALU 提供操作数。

- 5)程序状态字寄存器 PSW 用来保存 ALU 运算结果的特征位,如结果是否有溢出、是 否有进位/借位等。这些特征位可以作为控制程序转移的条件,供程序判别和查询。

#### 2. 控制器

控制器是由指令寄存器 IR、指令译码器 ID、定时及控制逻辑电路和程序计数器 PC 等部件组成。

- 1)程序计数器 PC 是一个 16 位的计数器。它总是存放着下一个要取指令的 16 位存储单元地址。即 CPU 将 PC 的内容作为地址,从内存中取出指令码或含在指令中的操作数。每取完一个字节后,PC 的内容自动加 1,为取下一个字节做好准备。在执行转移、子程序调用指令和中断响应时例外,PC 的内容不再加 1,而是由指令或中断响应过程自动给 PC 置入新的地址。

- 2) 指令寄存器 (IR) 保存当前正在执行的一条指令。执行一条指令,先要把它从程序存储器取到指令寄存器中,然后进行译码,并形成相应指令的微操作信号。

- 3) 定时与控制是微处理器的核心部件,它的任务是控制取指令、执行指令、存取操作数或运算结果等操作,以及向其他部件发出各种微操作控制信号、协调各部件的工作。

#### 2.2.3 存储器

MCS-51 系列单片机片内有程序存储器 ROM 和数据存储器 RAM,不同型号的单片机片内存储器的容量稍有不同,内部结构框图如图 2-2 所示。

图 2-2 MCS-51 单片机内部结构框图

8051 及 8751 的片内程序存储器容量为 4KB,用于存放程序和表格常数;8051/8751/8031 片内数据存储器均为 128B,用于存放运算的中间结果、数据暂存以及数据缓冲等。在这 128B 的 RAM 中,有 32B 可指定为工作寄存器,和片内 RAM 排在一个队列里统一编址。

#### 2.2.4 输入/输出接口

MCS-51 系列单片机有四个 8 位并行接口 (P0 ~ P3), 它们都是双向的,每个接口的 8 条 I/O 线均可以进行数据的输入/输出。端口的详细介绍请看本章第 5 节。

#### 2.3 80C51 单片机的引脚及功能

#### 2.3.1 80C51 单片机的引脚封装

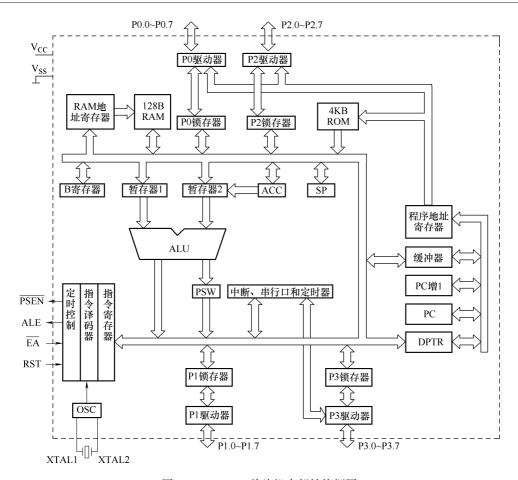

MCS-51 系列单片机通常有两种封装:一种是双列直插式封装,另一种是方形封装。图 2-3 所示为双列直插式封装 (DIP) 形式。

图 2-3 双列直插式封装形式

#### 2.3.2 80C51 单片机引脚及功能

这种封装形式的80C51单片机共有40根引脚,分为电源线、端口线和控制线三类。

#### 1. 电源线

$V_{cc}$ 、 $V_{ss}$  (⑩、②脚): 电源接入引脚,MCS-51 系列单片机采用 +5V 的电源电压。使用时  $V_{cc}$ 接电源的正极 (+5V), $V_{ss}$ 接电源负极 (0V)。

#### 2. 输入/输出端口引脚

PO, P1, P2 和 P3。

四个并行端口都可以作为普通的 I/O 端口使用,除 P1 口外其他三个端口都具有第二功能。

#### (1) P0 口 (P0.7~P0.1, 39~32脚)

P0 口具有两种功能,分别适用于不同的情况。第一种情况是 P0 口作为通用 L/O 端口使用, P0.0~P0.7 用于传送 CPU 输入/输出数据。这时,输出数据可以得到所存,不需要外接专用锁存器,输入数据可以得到缓冲,增加了数据输入的可靠性。第二种情况是单片机使用了外部存储器, P0.0~P0.7 在 CPU 访问外部存储器时,P0 口作为低 8 位地址/数据的复用总线使用。在此期间,P0 口内部上拉电阻有效。P0 口是一个漏极开路的 8 位准双向 L/O端口。每位能驱动 8 个 LS 型 TTL 负载。

#### (2) P1 口 (P1.7~P1.0, ①~⑧脚)

P1 口作为通用 L/O 端口使用,与 P0 口的第一功能类似,用于传送 CPU 的输入/输出数据。在 P1 口作为输入口使用时,应先向 P1 口锁存器 (地址 90H)写入全 1,此时 P1 口引脚由内部上拉电阻拉成高电平,然后再读入 P1 口的数据。P1 口的每一位能驱动(灌入或输出电流)4个 LS型 TTL 负载。

#### (3) P2 口 (P2.0~P2.7, ②~②脚)

P2 和 P0 类似,也有两种功能,分别适用于不同的情况。第一种情况和以上两组引脚的第一功能相同,作为通用 I/O 口使用,用于传送 CPU 输入/输出数据。第二种情况与 P0 口的第二功能配合使用,用于输出片外存储器的高 8 位地址,以构成片外存储器的 16 位地址。但不能像 P0 口那样还可以用来传送存储器的读写数据。P2 口是一个带内部上拉电阻的 8 位

准双向 I/O 端口,每一位能驱动 4 个 LS 型 TTL 负载。

(4) P3 口 (P3.0~P3.7, ⑩~①脚)

P3 口是一个带内部上拉电阻的 8 位准双向 I/O 端口,也具有两种功能,第一功能与其余三个端口一样,可以作为通用 I/O 来用。第二功能作为控制来用,功能如下:

- P3.0——串行数据输入引脚 RXD。

- P3.1——串行数据输出引脚 TXD。

- P3.2——外部中断 0 (INTO) 的中断请求信号输入引脚。

- P3.3——外部中断1(INTI)的中断请求信号输入引脚。

- P3.4——定时器 0 (T0) 外部计数脉冲输入引脚。

- P3.5——定时器1(T1)外部计数脉冲输入引脚。

- P3.6——片外数据存储器写选通控制信号输出引脚WR。

- P3.7——片外数据存储器读选通控制信号输出引脚RD。

#### 3. 控制线

(1) XTAL1、XTAL2 (18、19脚)

外部晶体振荡器的接入引脚。

(2) RST/VPD (⑨脚)

此引脚有两个功能: 一是作为复位信号输入端 RST 使用,高电平有效,正常工作时,当此输入端保持两个机器周期 (24 个振荡周期) 的高电平时,就可以完成复位操作;此引脚的第二功能是作为备用电源的输入端  $V_{PD}$ ,当主电源  $V_{CC}$ 发生故障,降低到低电平规定值时,将备用电源自动接入,为 RAM 提供备用电源,以保证存储在 RAM 中的信息不丢失,从而使复位后能继续正常运行。

#### (3) ALE/PROG (30脚)

此引脚有两个功能:一是输出地址锁存控制信号 ALE, 高电平有效; 二是作为片内 EPROM 编程写人脉冲输入端。

当单片机上电正常工作后,ALE 引脚不断向外输出地址锁存信号,其频率为振荡器频率  $f_{\rm osc}$  的 1/6。CPU 访问片外存储器时,P0 端口输出片外存储器的低 8 位地址的同时在 ALE/ $\overline{\rm PROG}$ 输出一个高电平脉冲,其下降沿用于这个 8 位地址所存到外部专用地址锁存器,此时 P0 口即可以传送片外存储器的读写数据。在对片内带有 4KB EPROM 的单片机进行固化程序时,作为编程脉冲输入端 $\overline{\rm PROG}$ 使用。

#### (4) PSEN (29脚)

程序存储器输出允许信号,低电平有效。在访问片外扩展的程序存储器时,此端定时输出负脉冲,作为片外存储器的读选通信号。PSEN同样可驱动8个LS型TTL负载。

#### (5) EA/V<sub>pp</sub> (3)脚)

此引脚有两个功能:一是作为内/外部程序存储器设置信号输入端;二是作为片内 EPROM 编程写入电压输入端使用。

当EA引脚接高电平时,CPU 访问片内程序存储器的顺序是由内到外,即CPU 首先从片内程序存储器开始执行程序,当PC 的值超过0FFFH时,将自动转去执行片外程序存储器内的程序。

当输入信号EA引脚接低电平(接地)时,CPU 只访问外部程序存储器,执行外部程序

存储器中的程序,而不管是否有片内程序存储器。对于无片内 ROM 的 8031 或 8032 型号的单片机,在使用时需要通过外部电路扩展程序存储器,此时必须将EA引脚接地。

此引脚的第二功能  $V_{PP}$ 是对 8751 片内 EPROM 固化编程时,作为施加较高编程电压(一般 12~21V)的输入端。

#### 2.4 80C51 单片机的存储器组织

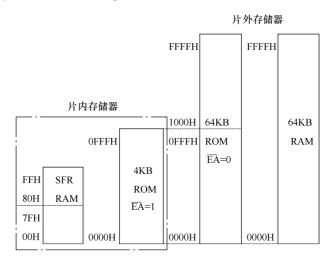

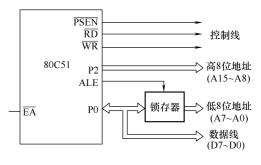

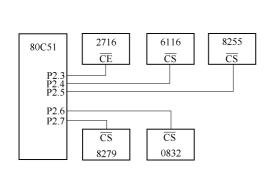

80C51 单片机的存储器在物理结构上分为程序存储器和数据存储器,共有四个存储空间:分别是片内程序存储器、片内数据存储器、片外程序存储器和片外数据存储器。存储空间分布如图 2-4 所示,从使用者的角度看,80C51 单片机存储器的地址空间为三类:程序存储器、数据存储器、特殊功能寄存器。

图 2-4 80C51 存储器物理结构

#### 2.4.1 80C51 单片机的程序存储器

80C51 单片机的程序存储器最大配置为 64KB,用于存放编好的程序和表格常数。由图 2-4 所示可知,程序存储器由两个部分组成:片内程序存储器 ROM,8051/8751 的容量为 4KB,地址为 0000H ~ 0FFFH; 片外程序存储器最多可扩至 64KB,地址为 1000H ~ FFFFH,片内外统一编址。并且通过EA引脚进行设置。

#### 1. EA引脚的作用

当引脚EA接高电平(EA = 1)时,80C51单片机程序计数器在0000H~0FFFH范围内(即前4KB地址)执行片内ROM中的程序;当指令地址超过0FFFH后,就自动转向执行片外ROM中的程序。80C51单片机从片内程序存储器和片外程序存储器取值时执行速度相同。

当引脚EA接低电平 (EA = 0) 时,80C51 单片机片内 ROM 不起作用,CPU 只能从片外扩展的程序存储器 ROM 中取指令执行,片外扩展的程序存储器 ROM 的地址从0000H 开始编址。这种接法特别适用于无片内程序存储器的8031 型号的单片机。

CPU 访问片内、片外 ROM 时, 使用 MOVC 指令。

#### 2. 程序存储器中的保留单元

程序存储器的某些单元是留给系统使用的,见表 2-1。由于 80C51 单片机上电复位后,程序计数器的内容为 0000H,所以 CPU 总是从 0000H 开始执行程序。存储单元 0000H ~ 0002H 用做 80C51 单片机上电复位后引导程序的存放单元。使用时通常在这三个单元中存放一条转移指令(LJMP MAIN),那么程序就被引导到转移指令指定的程序段去执行。

| 存 储 单元 | 功 能                                    |

|--------|----------------------------------------|

| 0000Н  | 上电或复位后,引导程序人口地址                        |

| 0003 H | 外部中断 0 (INTO) 中断服务程序的入口地址              |

| 000BH  | 定时器 0 (T0) 中断服务程序的人口地址                 |

| 0013H  | 外部中断 1 (INT1) 中断服务程序的入口地址              |

| 001BH  | 定时器 1 (T1) 中断服务程序的人口地址                 |

| 0023 H | 串行口中断服务程序的人口地址                         |

| 002BH  | 增强型单片机定时器/计数器 2 溢出或 T2EX 负跳变中断服务程序人口地址 |

表 2-1 保留的存储单元

80C51 单片机有 5 个中断源,在程序存储器中规定了 5 个中断服务程序的入口,并且在每个中断向量之间有 8 个单元提供用户使用。例如,外部中断 0 引脚INTO (P3.2) 有效时,向 CPU 发出中断申请,CPU 响应INTO的中断请求后自动将INTO中断服务程序的入口地址 0003H 装入 PC,程序就自动转向 0003H 单元开始执行。如果事先在 0003H ~ 000AH 存入转移到 INTO中断服务程序的转移指令,则程序就被自动转移到指定的中断服务程序空间去执行。

#### 2.4.2 80C51 单片机的数据存储器

数据存储器 RAM 用于存放运算的中间结果、数据暂存和缓冲、标志位等。数据存储器空间也分成片内和片外两大部分,片内存储器空间为 256B, 地址范围为 00H ~ 0FFH; 片外数据存储器空间可扩展为 64KB, 地址范围为 0000H ~ 0FFFFH。下面分别进行介绍。

#### 1. 片外 RAM

片外数据存储器通过硬件电路可以扩展为 64KB, 地址范围为 0000H~0FFFFH。使用时通过"MOVX"指令进行数据存取。

#### 2. 片内 RAM

片内数据存储器共有128B, 地址范围为00H~7FH。它们又分为三个部分:工作寄存器区、位寻址区和用户区。

- 1) 地址为00H~1FH的32B定义为工作寄存器区,并且分成四组来使用,称为0组、1组、2组和3组。每组有8个工作寄存器,每个字节定义为一个工作寄存器,分别用R0~R7表示。每组寄存器均可选作CPU的当前工作寄存器组。若程序中并不需要四组寄存器,其余可以作一般RAM单元使用。CPU复位后,选中第0组寄存器为当前的工作寄存器。通过对程序状态字PSW中RS1、RS0的设置,可以选择其他组为当前工作寄存器,见表2-2。

- 2) 地址为 20H~2FH 的单元为"位寻址区",这 16B 既可以按字节寻址,也可以按位寻址。这 16B 总共 128bit,每 1bit 都有唯一的位地址,可通过位寻址方式访问其各位,其位地址分布见表 2-3。

| 组   |           | R7   | R6  | R5  | R4  | R3  | R2   | R1   | R0  | RS1 RS0 |

|-----|-----------|------|-----|-----|-----|-----|------|------|-----|---------|

| 0 组 | .,,       | 07H  | 06H | 05H | 04H | 03H | 02H  | 01 H | 00H | 0 0     |

| 1组  | 工作<br>寄存器 | 0FH  | 0EH | 0DH | ОСН | ОВН | 0AH  | 09H  | 08H | 0 1     |

| 2 组 | 的地址       | 17H  | 16H | 15H | 14H | 13H | 12H  | 11H  | 10H | 1 0     |

| 3 组 |           | 1 FH | 1EH | 1DH | 1CH | 1BH | 1 AH | 19H  | 18H | 1 1     |

|     |           |      |     |     |     |     |      |      |     |         |

表 2-2 工作寄存器地址表

表 2-3 RAM 位寻址区地址表

| 字节地址 | MSB  |     | 位 地 址 |     |     |     |      |     |  |  |

|------|------|-----|-------|-----|-----|-----|------|-----|--|--|

| 2FH  | 7FH  | 7EH | 7DH   | 7CH | 7BH | 7AH | 79H  | 78H |  |  |

| 2EH  | 77H  | 76H | 75H   | 74H | 73H | 72H | 71H  | 70H |  |  |

| 2DH  | 6FH  | 6EH | 6DH   | 6CH | 6BH | 6AH | 69H  | 68H |  |  |

| 2CH  | 67H  | 66H | 65H   | 64H | 63H | 62H | 61H  | 60H |  |  |

| 2BH  | 5FH  | 5EH | 5DH   | 5CH | 5BH | 5AH | 59H  | 58H |  |  |

| 2AH  | 57H  | 56H | 55H   | 54H | 53H | 52H | 51H  | 50H |  |  |

| 29H  | 4FH  | 4EH | 4DH   | 4CH | 4BH | 4AH | 49H  | 48H |  |  |

| 28H  | 47H  | 46H | 45H   | 44H | 43H | 42H | 41H  | 40H |  |  |

| 27H  | 3FH  | 3ЕН | 3DH   | 3СН | 3ВН | 3AH | 39H  | 38H |  |  |

| 26H  | 37H  | 36H | 35H   | 34H | 33H | 32H | 31H  | 30H |  |  |

| 25H  | 2FH  | 2EH | 2DH   | 2CH | 2BH | 2AH | 29H  | 28H |  |  |

| 24H  | 27H  | 6Н  | 25H   | 24H | 23H | 22H | 21H  | 20H |  |  |

| 23H  | 1 FH | 1EH | 1DH   | 1CH | 1BH | 1AH | 19H  | 18H |  |  |

| 22H  | 17H  | 16H | 15H   | 14H | 13H | 12H | 11H  | 10H |  |  |

| 21H  | 0FH  | 0EH | 0DH   | ОСН | 0BH | 0AH | 09H  | 08H |  |  |

| 20H  | 07H  | 06H | 05H   | 04H | 03H | 02H | 01 H | 00H |  |  |

3) 地址为30H~7FH的单元为用户区,用户可以在这个区域存取数据,也可以定义为 堆栈区。

对于 128B 的 RAM 区, CPU 访问时可以采用字节地址或位地址方式。如果访问位地址区, 就用位寻址方式, 否则可以采用直接寻址或间接寻址方式。

位寻址能力是 80C51 单片机的一个重要特点。这些可寻址位,通过执行指令可直接对某一位操作,如置 1、清 0等,可用作软件标志位或用于位(布尔)处理。

#### 2.4.3 80C51 单片机的特殊功能寄存器

80C51 单片机片内 RAM 的地址空间 80H~FFH 为特殊功能寄存器 (SFR) 区,有 21 个特殊功能寄存器,它们离散地分布在 80H~FFH 的 RAM 空间中。访问特殊功能寄存器只允许使用直接寻址方式,这些特殊功能寄存器见表 2-4 所示。

在表 2-4 中,有 21 个特殊功能寄存器,有些特殊功能寄存器的符号地址上标有"※"号,它表示该特殊功能寄存器既可以位寻址也可以字节寻址。表中有 10 个寄存器是既可以

表 2-4 80C51 单片机特殊功能寄存器表

| 符号地址   | 名 称            | 字节地址 |

|--------|----------------|------|

| В      | B 寄存器          | F0   |

| * ACC  | 累加器            | ЕОН  |

| * PSW  | 程序状态字寄存器       | DOH  |

| * IP   | 中断优先级控制寄存器     | В8Н  |

| * P3   | P3 口锁存寄存器      | ВОН  |

| * IE   | 中断允许控制寄存器      | A8H  |

| * P2   | P2 口锁存寄存器      | АОН  |

| SBUF   | 串行口数据缓冲器       | 99H  |

| * SCON | 串行口控制寄存器       | 98H  |

| * P1   | P1 口锁存寄存器      | 90H  |

| TH1    | 定时器/计数器1的高字节   | 8DH  |

| TH0    | 定时器/计数器1的低字节   | 8CH  |

| TL1    | 定时器/计数器 0 的高字节 | 8BH  |

| TLO    | 定时器/计数器 0 的低字节 | 8AH  |

| TMOD   | 定时器/计数器工作方式寄存器 | 89H  |

| * TCON | 定时器/计数器控制寄存器   | 88H  |

| PCON   | 电源控制寄存器        | 87H  |

| DPH    | 数据指针寄存器高字节     | 83H  |

| DPL    | 数据指针寄存器低字节     | 82H  |

| SP     | 堆栈指针寄存器        | 81H  |

| * P0   | P0 口锁存寄存器      | 80H  |

位寻址也可以字节寻址,特征是它们的字节地址正好能被8整除,其地址分布见表2-5。下面介绍部分特殊功能寄存器,其余将在后续章节中讲述。

表 2-5 特殊功能寄存器地址表

| SFR    | MSB    |        |        |        | LSB    | 字节地址   |        |        |      |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|------|

| В      |        |        |        |        |        |        |        |        | FO   |

|        | E7H    | Е6Н    | E5H    | E4H    | ЕЗН    | E2H    | E1 H   | E0H    | ЕОН  |

| ACC    | ACC. 7 | ACC. 6 | ACC. 5 | ACC. 4 | ACC. 3 | ACC. 2 | ACC. 1 | ACC. 0 |      |

| - DOWN | D7H    | D6H    | D5H    | D4H    | D3H    | D2H    | D1H    | D0H    | D0H  |

| PSW    | CY     | AC     | F0     | RS1    | RS0    | ov     | F1     | P      |      |

|        | BFH    | BEH    | BDH    | ВСН    | ВВН    | BAH    | В9Н    | B8H    | Davi |

| IP     | /      | /      | /      | PS     | PT1    | PX1    | PT0    | PX0    | B8H  |

|        | В7Н    | В6Н    | В5Н    | В4Н    | ВЗН    | B2H    | B1 H   | ВОН    | Davi |

| Р3     | P3. 7  | P3. 6  | P3. 5  | P3. 4  | P3. 3  | P3. 2  | P3. 1  | P3. 0  | ВОН  |

(续)

|      |       |       |       |       |       |       |       |       | (吳)  |

|------|-------|-------|-------|-------|-------|-------|-------|-------|------|

| SFR  | MSB   |       |       | 位地址   | L/定义  |       |       | LSB   | 字节地址 |

|      | AFH   | AEH   | ADH   | ACH   | ABH   | AAH   | А9Н   | A8H   |      |

| ΙE   | EA    | /     | /     | ES    | ET1   | EX1   | ЕТО   | EX0   | A8H  |

|      | A7H   | А96Н  | A95H  | A4H   | АЗН   | A2H   | A1H   | AOH   |      |

| P2   | P2. 7 | P2. 6 | P2. 5 | P2. 4 | P2. 3 | P2. 2 | P2. 1 | P2. 0 | AOH  |

| SBUF |       |       |       |       |       |       |       |       | 99H  |

|      | 9FH   | 9EH   | 9DH   | 9CH   | 9BH   | 9AH   | 99 H  | 98H   |      |

| SCON | SM0   | SM1   | SM2   | REN   | TB8   | RB8   | TI    | RI    | 98H  |

|      | 97H   | 96H   | 95H   | 94H   | 93H   | 92H   | 91 H  | 90H   |      |

| P1   | P1. 7 | P1. 6 | P1. 5 | P1. 4 | P1. 3 | P1. 2 | P1. 1 | P1. 0 | 90H  |

| TH1  |       |       |       |       |       |       |       |       | 8DH  |

| TH0  |       |       |       |       |       |       |       |       | 8CH  |

| TL1  |       |       |       |       |       |       |       |       | 8BH  |

| TL0  |       |       |       |       |       |       |       |       | 8AH  |

| TMOD | GATE  | C/T   | M1    | МО    | GATE  | C/T   | M1    | МО    | 89H  |

|      | 8FH   | 8EH   | 8DH   | 8CH   | 8BH   | 8AH   | 89H   | 88H   |      |

| TCON | TF1   | TR1   | TF0   | TR0   | IT1   | IE1   | IT0   | IEO   | 88H  |

| PCON | SMOD  | /     | /     | /     | GF1   | GF0   | PD    | IDL   | 87H  |

| DPH  |       |       |       |       |       |       |       |       | 83H  |

| DPL  |       |       |       |       |       |       |       |       | 82H  |

| SP   |       |       |       |       |       |       |       |       | 81H  |

|      | 87H   | 86H   | 85H   | 84H   | 83H   | 82H   | 81H   | 80H   |      |

| P0   | P0. 7 | P0. 6 | P0. 5 | P0. 4 | P0. 3 | P0. 2 | P0. 1 | P0. 0 | 80H  |

- 1) 累加器 ACC 是 80C51 单片机最常用的 8 位特殊功能寄存器;在执行运算指令时,许 多指令的操作数取自于 ACC,许多运算中间结果也存放于 ACC 中。在指令系统中用 A 作为 累加器 ACC 的助记符。

- 2) 寄存器 B 在乘、除指令中使用最多。乘法指令的两个操作数分别取自 A 和 B,乘积存于 B 和 A 两个 8 位寄存器中。详见乘除法指令,在其他指令中,B 可作为一般通用寄存器或一个 RAM 单元使用。

- 3)程序状态字寄存器 PSW,它的 8 位包含了程序执行后的状态信息,供程序查询和判断之用。其各位含义如下:

- CY: 进位、借位标志位,有进位、借位时 CY=1, 否则 CY=0。

- AC: 辅助进位、借位标志位,当高半字节与低半字节间有进位或借位时 AC=1,否则 AC=0。

- FO: 用户标志位, 由用户自己定义。

- RS1、RS0: 当前工作寄存器组选择位,工作寄存器地址表见表 2-2。

- OV: 溢出标志位, 有溢出时 OV = 1, 否则 OV = 0。

- P: 奇偶标志位, 存于 ACC 中的运算结果有奇数个 1 时 P=1, 否则 P=0。

- 4) 8 位堆栈指针寄存器 SP, 它总是指向栈顶。80C51 单片机的堆栈通常设在 30H ~ 7FH 这一段 RAM 中。在系统上电或复位时, SP 的初始值为 07H, 可以在初始化程序中重新设置。

80C51 单片机堆栈操作遵循 "先进后出,后进先出"的原则:入栈操作时,首先执行 SP 加 1 操作,然后数据入栈存入 SP 指向的单元;出栈操作时,先将 SP 指向单元的数据弹出,然后执行 SP 减 1 操作,这时 SP 指向的单元是新的栈顶。由此可见,80C51 单片机的堆栈区是向地址增大的方向生成的。

- 5) 16 位数据指针寄存器 DPTR,通常作为地址寄存器使用,用于存放 16 位地址,也可以分成两个 8 位寄存器 DPH 和 DPL 使用。可以对片外 64KB 范围的 RAM/ROM 数据进行间接寻址或变址寻址操作。

- 6) 并行 I/O 端口锁存器 PO~P3, 它们都可以进行位寻址和字节寻址。每一条 I/O 线均可以作为输入和输出使用,输出时可以锁存数据,输入时可以进行数据缓冲。

#### 2.5 80C51 单片机的并行 I/O 口

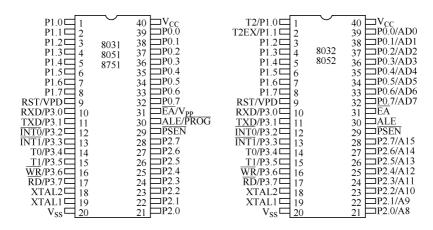

80C51 单片机有 4 个 8 位的并行 I/O 口 P0、P1、P2 和 P3。各口均由口锁存器、输出驱动器和输入缓冲器组成。4 个并行口既有字节地址又有位地址。对各个并行口锁存器的读写,就可以实现口的输入/输出操作。4 个并行口的功能有所不同,结构也存在一些差异,但每个口的位结构是相同的。所以,口结构的介绍均以其位结构进行说明。

#### 2.5.1 P0、P2 口的结构

80C51 单片机中,使用内部含有程序存储器的单片机,基本上不需要外部扩展程序存储器和数据存储器,这时 P0、P2 口可用作通用的输入/输出口。若使用内部无程序存储器型号的单片机,就需要通过外部电路扩展程序存储器和数据存储器,此时,P0、P2 口作为总线接口使用,即 P0 口为分时复用的低 8 位地址/数据总线,P2 口作为高 8 位地址总线。

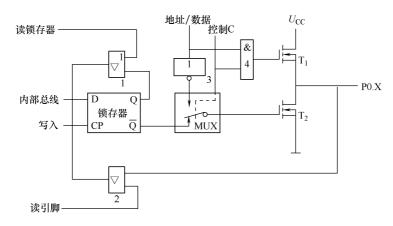

#### 1. P0 口的结构

P0 口的位结构如图 2-5 所示。P0. X 位由一个输出锁存器、一个转换开关 MUX、两个三态输入缓冲器 1、2、输出驱动电路( $T_1$ 、 $T_2$ )和一个与门 4 及一个反相器 3 组成,图中控制信号 C 的状态决定转换开关的位置。当 C=0 时,开关处于图中所示位置;当 C=1 时,开关拨向反相器输出端位置。

#### (1) PO 作为通用 I/O 口使用

当单片机系统没有外部扩展 ROM/RAM 时,PO 用作通用 L/O 口使用。在这种情况下,单片机硬件逻辑自动控制 C=0,MUX 开关处于当前位置。另外,C=0,与门 4 的输出为 "0",使输出驱动器的上拉场效应晶体管  $T_1$  处于截止状态。因此,输出驱动级工作在需要 外接上拉电阻的漏极开路方式。

作输出口时,CPU 执行口的输出指令,内部数据总线上的数据在"写锁存器"信号的作用下由 D 端进入锁存器,经锁存器的  $\overline{Q}$  端送至场效应晶体管  $T_2$ ,再经  $T_2$  反相,在 PO.X

图 2-5 P0 口的位结构

引脚出现的数据正好是内部总线的数据。

作输入口时,数据可以读自口的锁存器,也可以读自口的引脚。这要根据输入操作采用的是"读锁存器"指令,还是"读引脚"指令来决定。

CPU 在执行"读—修改—写"类输入指令时(如 ANL PO, A),内部产生的"读锁存器"操作信号,使锁存器 Q 端数据进入内部数据总线,在与累加器 A 进行逻辑运算之后,结果又送回 PO 口锁存器并出现在引脚上。读端口锁存器可以避免因外部电路原因造成的误读。

CPU 在执行"MOV"类输入指令时(如 MOV A, PO),内部产生的操作信号是"读引脚"。注意,在执行该类输入指令前要先给锁存器写入"1",目的是使场效应晶体管  $T_2$  截止,从而使引脚处于悬浮状态,可以作为高阻抗输入。否则,在作为输入方式之前曾向锁存器输出过"0", $T_2$  导通会使引脚钳位在"0"电平,使输入高电平"1"无法读入。所以,PO 口在作为通用 I/O 口时,属于准双向口。

#### (2) P0 作为地址/数据总线口使用

当系统扩展片外 ROM/RAM 时,PO 作为地址/数据总线使用。在这种情况下,单片机内硬件逻辑自动使 MUX 开关控制端 C=1,则 MUX 开关接到反相器 3 的输出端,这时与门 4 的输出由地址/数据线的状态决定。

CPU 在执行输出指令时,低 8 位地址和数据信息分时地出现在地址/数据总线上。若地址/数据总线的状态为"1",则场效应晶体管  $T_1$  导通、 $T_2$  截止,引脚状态为"1",若地址/数据总线的状态为"0",则场效应晶体管  $T_1$  截止、 $T_2$  导通,引脚状态为"0"。可见 P0. X 引脚的状态正好与地址/数据线的信息相同。

CPU 在执行输入指令时,首先低 8 位地址信息出现在地址/数据总线上,PO. X 引脚的状态与地址/数据总线的地址信息相同。然后,CPU 自动地使转换开关 MUX 拨向锁存器,并向 PO 口写入 FFH,同时"读引脚"信号有效,数据经缓冲器进入内部数据总线。

由此可见, PO 口作为地址/数据总线使用时是一个真正的双向口。

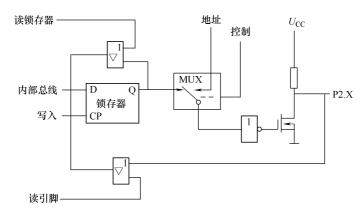

#### 2. P2 口的结构

P2 口的位结构如图 2-6 所示, P2. X 位由一个输出锁存器、一个转换开关 MUX、两个三 态输入缓冲器、输出驱动电路和一个反相器组成。图中控制信号的状态决定转换开关的位

置。当控制信号为 0 时, 开关处于图中所示位置; 当控制信号为 1 时, 开关拨向地址线位置。

由图可见, P2 口的输出驱动电路与 P0 口不同, 只使用一个场效应晶体管, 其内部设有上拉电阻。

图 2-6 P2 口的位结构

#### (1) P2 作为通用 I/O 口使用

当单片机系统没有外部扩展 ROM/RAM 时, P2 可以作为通用 I/O 口使用。

CPU 在执行输出指令时,内部数据总线的数据在"写锁存器"信号的作用下由 D 端进入锁存器,经反相器反相后送至场效应晶体管  $T_2$ ,再经  $T_2$  反相,在 P2. X 引脚出现的数据正好是内部总线的数据。

P2 口用作输入时,数据可以读自口的锁存器,也可以读自口的引脚。这要根据输入操作采用的是"读锁存器"指令还是"读引脚"指令来决定。

CPU 在执行"读一修改一写"类输入指令时(如 ANL P2, A),内部产生的"读锁存器"操作信号,使锁存器 Q 端数据进入内部数据总线,在与累加器 A 进行逻辑运算之后,结果又送回 P2 口的锁存器并出现在引脚。

CPU 在执行"MOV"类输入指令时(如 MOV A, P2),内部产生的操作信号是"读引脚"。应在执行输入指令前对锁存器写入"1",目的是使场效应晶体管  $T_2$  截止,从而使引脚处于高阻抗输入状态。所以,P2 口在作为通用 I/O 口时,属于准双向口。

#### (2) P2 口作为地址总线接口使用

当需要在单片机外部扩展程序存储器或数据存储器时,单片机内部硬件逻辑自动控制 MUX 开关接向地址线,这时 P2. X 引脚的状态正好与地址线输出的信息相同。

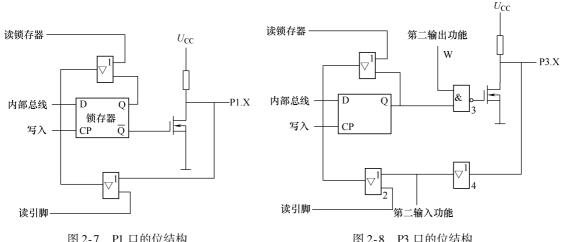

#### 2.5.2 P1、P3 口的结构

P1 口是 80C51 单片机唯一的单功能口,仅能用作通用的数据输入/输出口。P3 口是双功能口,除具有数据输入/输出功能外,还具有特殊的第二功能。

#### 1. P1 口的结构

P1 口的位结构如图 2-7 所示。由图可见, P1 口由一个输出锁存器、两个三态输入缓冲器和输出驱动电路组成。其输出驱动电路与 P2 口相同,内部设有上拉电阻。P1 口是通用的

准双向 1/0 口。输出高电平时,能向外提供拉电流负载。用作输入口使用时,在读入数据前 必须向口锁存器写入"1"。

#### 2. P3 口的结构

P3 口的位结构如图 2-8 所示。P3 口由一个输出锁存器、三个输入缓冲器 (1、2、4), 其中缓冲器 1、2 为三态门,场效应晶体管输出驱动电路和一个与非门(3)组成。输出驱 动电路内部设有上拉电阻。

图 2-7 P1 口的位结构

图 2-8 P3 口的位结构

#### (1) P3 作为通用 I/O 口使用 (第一功能)

单片机内部的硬件自动将第二功能输出线的 W 置 1。这时,对应的口线为通用 1/0 口方 式。作为输出时,锁存器的状态(Q端)与输出引脚的状态相同;作为输入时,也要先向 口锁存器写入1,使引脚处于高阻输入状态。输入的数据在"读引脚"信号的作用下,进入 内部数据总线。所以, P3 口在作为通用 I/O 口时, 也属于准双向口。

#### (2) P3 口的第二功能

当 CPU 不对 P3 口进行字节或位寻址时,单片机内部硬件自动将口锁存器的 O 端置 1。 这时,可以使用 P3 口的第二功能。P3 口第二功能的各引脚的定义如下,

- P3.0: 串行口输入信号引脚(RXD)。

- P3.1: 串行口输出信号引脚(TXD)。

- P3.2. 外部中断 0 输入信号引脚 (INTO)。

- P3. 3: 外部中断 1 输入信号引脚(INT1)。

- P3.4. 定时/计数器 0 的外部输入信号引脚(T0)。

- P3.5: 定时/计数器 1 的外部输入信号引脚(T1)。

- P3.6: 片外数据存储器"写"选通输出信号引脚(WR)。

- P3.7. 片外数据存储器"读"选通输出信号引脚(RD)。

有些应用场合若把其中的几条口线设为第二功能、另外几条口线设为第一功能使用。这 时官采用位寻址方式。

#### 2.5.3 并行口的负载能力

PO、P1、P2、P3 口的输入和输出电平与 CMOS 电平和 TTL 电平均兼容。

P0 口的每一位口线可以驱动 8 个 LSTTL 负载。在作为通用 L/O 口时,由于输出驱动电 路是开漏方式,驱动时需外接上拉电阻;当作为地址/数据总线使用时,接口线输出不是开 漏方式,无需外接上拉电阻。

P1、P2、P3 口的每一位能驱动 4个 LSTTL 负载。它们的输出驱动电路内部设有上拉电 阻, 所以可以方便地由集电极开路(OC门)电路或漏极开路电路所驱动, 而无需外接上拉 电阻。

由于单片机口线仅能提供几毫安的电流、当作为输出驱动一般晶体管的基极时、应在口 与晶体管的基极之间串接限流电阻。

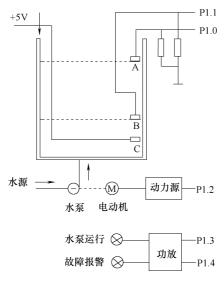

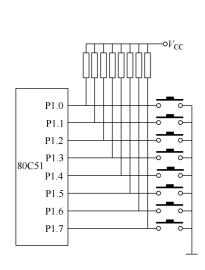

#### 2.5.4 并行口的应用举例

#### 1. 并口作为输出口的应用

利用 P1 口作为输出口控制发光二极管的应用 电路,如图 2-9 所示。将 8 个发光二极管 (LED) 的阳极接在一起,并将它们接在 +5V 电源端,这 种接法也称为共阳极接法。发光二极管的阴极通 过一个限流电阻分别接到 P1 口的 8 个引脚上。由 此可见, 若要控制 8 个发光二极管的点亮与熄灭, 只要控制 P1 口 8 个引脚的输出电平即可达到目 的。当 P1 口的每个引脚输出高电平时,发光二极 管均不导通,此时的发光二极管不亮。而当 P1 口 的每个引脚输出低电平时,发光二极管导通,发 光二极管被点亮。

#### 2. 并口作为输入、输出口的应用

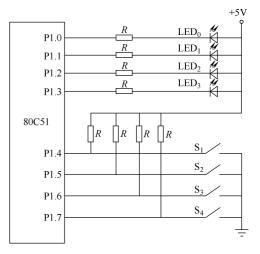

并口作为输入、输出口的应用如图 2-10 所

P1.0 P1.1 LED<sub>2</sub> P1.2  $LED_3$ P1.3 80C51  $LED_4$ P1.4  $LED_5$ P1.5  $LED_6$ P1.6 LED<sub>7</sub> P1.7

图 2-9 P1 口输出控制 LED 电路

示。由图可见, P1 口分别连接了 4 个开关和 4 个发光二极管, 组成输入/输出应用电路。 4 个开关 S<sub>1</sub> ~ S<sub>4</sub> 的一端连在一起并接低电平 (接电源地), 另一端分别接在 P1 口的 P1.4 ~

P1.7 引脚上,同时通过4个上拉电阻接到高电 平 (+5V)。当对 P1 口进行读操作时,可以读 入开关的当前状态, 开关状态与 P1 口读入的数 字量关系如下:

若开关均处于打开状态,从+5V电源→电 阻  $R \rightarrow \mathcal{H}$   $\to$  平美  $S \rightarrow$  电源地端,由于开关 S 是打开的 不能形成电流回路, 电阻 R 上无压降产生, 所 以 P1.4~P1.7 引脚的电平值为+5V(高电平). 此时从 P1.4~ P1.7 引脚读入的数字量值为 "1111B" o

当开关均处于闭合状态,从+5V 电源→电  $\mathbf{R} \rightarrow \mathbf{F} + \mathbf{S} \rightarrow \mathbf{E}$  电源地端,由于开关 S 是闭合的 能够形成电流回路, 电阻 R 上产生压降 (压降

图 2-10 P1 口输入、输出控制电路

为 +5V),开关 S 是闭合后将 P1. 4 ~ P1. 7 引脚的与电源地连接(低电平),此时从 P1. 4 ~ P1. 7 引脚读入的数字量值为 "0000B"。

P1.0~P1.3 引脚连接4个 LED,组成输出控制电路,4个 LED 的点亮与熄灭控制如前例所述。在此例中,将读入的开关状态,直接从P1.0~P1.3 引脚输出,可以控制 LED 点亮与熄灭。即改变开关的状态,就可以控制 LED 的状态,通过编程可以实现控制的目的。

在本例中,要注意在读入开关状态之前,要对 P1 口写"1"(使输出端的场效应晶体管截止),然后再读入开关状态。关于并行口的编程参考本书第3章内容。

#### 2.6 80C51 单片机的时钟与复位

单片机本身是一个复杂的同步时序系统,为保证同步工作方式的实现,单片机必须有时钟信号,以使其系统在时钟信号的控制下按时序协调工作。而所谓时序,则是指指令执行过程中各信号之间的相互时间关系。

复位是单片机的硬件初始化操作。系统复位后,单片机系统才能开始正常工作。

#### 2.6.1 80C51 单片机的时钟

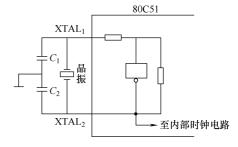

#### 1. 振荡电路

80C51 芯片中的高增益反相放大器,其输入端为引脚  $XTAL_1$ ,输出端为引脚  $XTAL_2$ 。通

过这两个引脚在芯片外并联石英晶体振荡器和两只电容器(电容  $C_1$  和  $C_2$  一般取  $30 \mathrm{pF}$ )。石英晶体为感性元件,与电容构成振荡回路,为片内放大器提供正反馈和振荡所需的相移条件,从而构成一个稳定的自激振荡器,如图 2-11 所示。

除使用石英晶体振荡器外,若对时钟频率要求 不高,还可以用电感或陶瓷振荡器,但使用陶瓷振 荡器时要把电容的容量稍微提高一些。

图 2-11 80C51 单片机自激振荡电路

#### 2. 分频电路

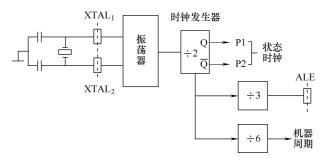

振荡电路产生的振荡信号并不直接为单片机所用,而要进行分频,经分频后才能得到单片机各种相关的时钟信号,如图 2-12 所示。

图 2-12 80C51 单片机的时钟电路框图

振荡脉冲经二分频后作为系统的时钟信号(注意时钟信号与振荡脉冲之间的二分频关系,否则会造成概念上的错误),在二分频的基础上再进行三分频产生 ALE 信号,在二分频的基础上再进行六分频得到机器周期信号。

#### 3. 晶振频率

晶振频率是指晶体振荡器的振荡频率,也就是振荡电路的脉冲频率,所以也称振荡频率。80C51的晶振频率范围一般为1.2~33MHz。随着技术的发展,单片机的晶振频率还在逐步提高,如现在一些高速芯片的晶振频率已达40MHz。晶振频率是单片机的一项重要性能指标。因为单片机的时钟信号是通过振荡信号分频得到的,所以晶振频率直接影响着时钟信号频率。晶振频率高,系统的时钟频率就高,单片机运行速度也就快。晶振频率不但影响速度,而且对单片机的工作电流也有一定的影响,所以在选择晶振频率时,要兼顾速度、功耗和线路工艺。

### 4. 从外部引入脉冲信号驱动时钟电路

高频振荡信号除了由振荡电路产生外,还可以从外部脉冲源直接引入。直接引入外部脉冲信号的情况多发生在由多片单片机组成的系统中,因为统一从一个外部脉冲源引入脉冲信号,可以保证各单片机之间时钟信号的同步。对于 80C51 芯片,外部脉冲信号经 XTAL<sub>1</sub> 引脚注入,但同时要把 XTAL<sub>2</sub> 引脚悬空,其连接电路如图 2-13 所示。

实际使用时,引入的脉冲信号应为高低电平持续时间大于20ns的矩形波,且脉冲频率应低于12MHz。注意,尽管80C51与8051兼容,但当使用外部脉冲信号驱动芯片的时钟电路时,应注意它们之间的差别。80C51的外部脉冲信号经XTAL,引脚

图 2-13 外部脉冲源接法

接入,而8051则是经XTAL,引脚接入。两种芯片之所以有如此差别,是芯片内部的原因,80C51的时钟电路是由XTAL,引脚信号驱动的,而8051则是由XTAL,引脚信号驱动的。

#### 2.6.2 80C51 单片机的定时单位

80C51 的时序就是 80C51 在执行指令时所需控制信号的时间顺序。80C51 单片机的时序 定时单位从小到大依次为,时钟周期(状态周期)、机器周期和指令周期。

#### 1. 时钟周期

把晶振脉冲的周期定义为节拍 (用 P 表示)。晶振脉冲经过二分频后,得到的振荡脉冲的周期就是单片机的时钟周期 (即一个时钟周期是晶振周期的 2 倍),时钟周期也称为状态 (用 S 表示)。这样,一个状态就包含两个节拍,具前半周期对应的拍节叫节拍 1 (P1),后半周期对应的节拍叫节拍 2 (P2)。

#### 2. 机器周期

80C51 采用定时控制方式,因此它有固定的机器周期。规定一个机器周期的宽度为 6 个状态,并依次表示为 S1~S6。由于一个状态又包括两个节拍,因此,一个机器周期总共有 12 个节拍,分别记作 S1P1、S1P2、…、S6P2。由于一个机器周期共有 12 个晶振周期,因此机器周期就是晶振脉冲的十二分频。

当晶振脉冲频率为 12MHz 时,一个机器周期为 1μs; 当晶振脉冲频率为 6MHz 时,一个机器周期为 2μs。

### 3. 指令周期

指令周期是最大的时序定时单位,执行一条指令所需要的时间称为指令周期。它一般由若干个机器周期组成。不同的指令,所需要的机器周期数也不相同。通常,包含一个机器周期的指令称为单周期指令,包含两个机器周期的指令称为双周期指令。指令的运算速度与指令所包含的机器周期有关,机器周期数越少的指令执行速度越快。80C51 单片机通常可以分为单周期指令、双周期指令和四周期指令三种。四周期指令只有乘法和除法指令两条,其余均为单周期和双周期指令。

### 2.6.3 80C51 单片机的复位方式与初始化状态

复位是单片机的硬件初始化操作。经复位操作后,单片机系统才能开始正常工作。

### 1. 复位方式

80C51 有复位信号引脚 RST,用于从外界引入复位信号。复位操作比较简单,只有两种复位方式:加电复位和手动复位。

### (1) 加电复位

加电复位是指通过专用的复位电路产生复位信号。它是系统的原始复位方式,发生在开机加电时,是系统自动完成的。加电复位是任何单片机系统都具有最基本的功能。

#### (2) 手动复位

手动复位也应通过专用的复位电路实现。在单片机系统中,手动复位是必须具有的功能。在调试或运行程序时,若遇到死机、死循环等情况,手动复位是摆脱这种尴尬局面的最常用方法。这时,手动复位所完成的是一次重新启动操作。

在实际系统中,总是把加电复位电路和手动复位电路结合在一起,形成一个既能加电复位,又能手动复位的公用复位电路。另外,目前已经出现了专用的复位芯片,如 Maxim 公司推出的 MAX813L。该芯片具有 4 项基本功能:加电复位、手动复位、看门狗和掉电监视。

### 2. 初始化状态

复位操作有:为一些专用寄存器设置初始状态、PSW 清 0、PC 被赋值为 0000H,以及为芯片的某些引脚设置电平状态等内容。复位操作后,部分专用寄存器 (SFR) 的初始化状态见表 2-6。

|         |              | , , , , , , , , , , , , , , , , , , , , |                                                                                                                                          |

|---------|--------------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| 寄存器     | 内 容          | 寄 存 器                                   | 内 容                                                                                                                                      |

| PC      | 0000H        | TCON                                    | 00Н                                                                                                                                      |

| ACC     | ООН          | TLO                                     | 00Н                                                                                                                                      |

| PSW     | 00Н          | ТНО                                     | 00Н                                                                                                                                      |

| SP      | 07H          | TL1                                     | 00Н                                                                                                                                      |

| DPTR    | 0000Н        | TH1                                     | 00Н                                                                                                                                      |

| P0 ~ P3 | 0FFH         | SCON                                    | 00Н                                                                                                                                      |

| IP      | × × × 00000B | SBUF                                    | 不定                                                                                                                                       |

| IE      | 0×000000B    | PCON                                    | $0 \times \times$ |

| TMOD    | 00Н          |                                         |                                                                                                                                          |

表 2-6 部分专用寄存器 (SFR) 的初始化状态

完成复位操作共需 24 个状态周期。复位结束后,单片机从地址 0000H 开始执行程序。对于专用寄存器的复位状态,值得关注的是,PC 为 0000H,SP 为 07H,各 L/O 口锁存器为 FFH,SBUF 状态不定,其他寄存器大多被置为 00H。此外,复位操作还对单片机的个别引脚信号有影响。例如,把 ALE 和PSEN信号变为无效状态,即 ALE = 0, PSEN = 1。

### 2.6.4 80C51 单片机的复位电路

复位电路用于产生复位信号,通过 RST 引脚送入单片机,进行复位操作。复位电路的好坏直接影响单片机系统工作的可靠性。

#### 1. 复位电路的分类

目前,在单片机系统中共使用过4种类型的复位电路:积分电路型、微分电路型、比较器型和看门狗型。其中前3种是在芯片外面用分立元器件或集成电路芯片搭建的;而最后一种位于芯片内部,是单片机芯片的一部分。对于片外复位电路,无论哪种类型,加电复位和手动复位都是必不可少的基本功能。下面把最常用的积分电路型和微分电路型复位电路做一简单说明。

#### (1) 积分型

积分型复位电路是在积分电路的基础上形成的,用于产生低电平复位信号。图 2-14 所示为最基本的积分型复位电路及其演化过程。

### (2) 微分型

微分型复位电路是在微分电路的基础上形成的,用于产生高电平复位信号。图 2-15 所示为最基本的微分型复位电路。

图 2-15 微分型复位电路

### 2. 80C51 单片机的基本复位电路

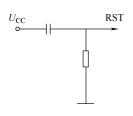

80C51 基本复位电路共有上电复位、按键电平复位和按键脉冲复位 3 种。其中上电自动复位是通过电容充电来实现的,比较简单的上电复位电路如图 2-16a 所示。只要电源  $U_{cc}$ 的上升时间不超过  $1_{ms}$ ,就可以实现自动上电复位,即接通电源即可完成系统的复位初始化。

手动复位是通过按键实现的,有电平方式和脉冲方式两种。其中按键电平复位是通过使复位端经电阻与  $U_{cc}$  电源接通而实现的,电路如图 2-16b 所示。而按键脉冲复位则是利用 RC 微分电路产生的正脉冲来实现的,电路如图 2-16c 所示。

上述电路图中的电阻、电容参数适用于 6MHz 晶振,能保证复位信号高电平持续时间大于两个机器周期。

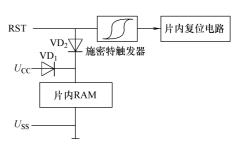

### 3. 80C51 芯片内复位电路

80C51 的 RST 引脚是复位信号的输入端。复位信号 RST 是高电平有效,其有效时间应

图 2-16 80C51 单片机的基本的复位电路

持续 24 个振荡脉冲周期 (即 2 个机器周期)以上。 若使用频率为 6MHz 的晶振,则复位信号持续时间 应超过 4μs 才能有效。产生芯片内复位信号的电路 逻辑如图 2-17 所示。

可见,整个复位电路包括芯片内、外两部分。 外部电路产生的复位信号 RST 送施密特触发器, 再由片内复位电路在每个机器周期的 S5P2 时刻对 施密特触发器的输出进行采样,最后才得到内部复 位操作所需要的信号。

图 2-17 芯片内复位信号的电路

# 本章小结

80C51 单片机的存储器在物理上设计成程序存储器和数据存储器两个独立的空间。片内程序存储器容量为0KB/4KB/8KB,中断向量设置在0003H~0023H区域内。片内数据存储器为128B,分成工作寄存器区、位寻址区和用户区,以及128B的特殊功能寄存器区。CPU使用不同指令和寻址方式对其进行相应的操作。

单片机通过复位电路实现上电和复位操作,使单片机进入初始化状态。复位后,PC内容为0000H,P0~P3口内容为FFH,SP内容为07H,SBUF内容不定,IP、IE和PCON的有效位为0,其余的特殊功能寄存器的状态均为00H。

80C51 单片机的时钟信号有内部时钟方式和外部时钟方式两种。内部的各种微操作都以晶振周期为时序基准。一个机器周期包含 12 个晶振周期(或 6 个时钟周期)。指令的执行时间称作指令周期。

80C51 单片机有 4 个 8 位的并行 I/O 口: P0 ~ P3 口。各口均由接口锁存器、输出驱动器和输入缓冲器组成。4 个并行口均可以作为普通 I/O 口使用,具有数据输入/输出功能,注意作为输入口使用时先写 1,然后再读入数据。在需要外部扩展程序存储器和数据存储器时,P0 口作为分时复用的低 8 位地址/数据总线,P2 口作为高 8 位地址总线,P3 口的P3. 6/P3. 7 提供"读写"控制信号。P1 口是唯一的单功能口,仅能用作通用的数据输入/输出口。P3 口是双功能口,除具有数据输入/输出功能外,每一个接口还具有不同的第二功能,如 P3. 0、P3. 1 是串行输入/输出口等。

## 习 题

- 1. 80C51 单片机存储器的组织采用何种结构?存储器地址空间如何划分?各地址空间的地址范围和容量如何?在使用上有何特点?

- 2. 80C51 单片机的 P0~P3 口在结构上有何不同? 在使用上有何特点?

- 3. 如果 80C51 单片机晶振频率分别为 6MHz、11.0592MHz、12MHz 时, 机器周期分别为多少?

- 4. 80C51 单片机的片内、片外存储器如何选择?

- 5. 80C51 单片机的 PSW 寄存器各位标志的意义如何?

- 6. 80C51 单片机的当前工作寄存器组如何选择?

- 7. 80C51 单片机复位后的状态如何? 复位方法有几种?

- 8. 80C51 单片机系统初始化状态, PC、ACC、PSW、P0~P3、TMOD、DPTR、SCON、TCON 等寄存器处于什么状态?

# 第3章 80C51的指令系统

### 【学习目的】

学习和应用单片机一个很重要的环节就是理解并熟练掌握它的指令系统。通过本章的学习应达到以下的学习目标:

- 1. 了解机器语言、汇编语言和高级语言的特点。

- 2. 掌握汇编语言指令的基本格式. 熟悉机器语言指令的格式。

- 3. 理解80C51的7种寻址方式及相应的寻址空间,并能实际应用。

- 4. 熟记 80C51 的 111 条汇编语言指令的形式。

- 5. 熟悉每条指令的功能、操作的对象和结果;并会根据不同的实践需要选择合适的指令。

### 3.1 指令概述

指令是 CPU 用来执行某种操作的命令。一条指令只能完成有限的功能,为了使计算机能够完成一定复杂的功能就需要一系列的指令,计算机能够执行的各种指令的集合称为它的指令系统。计算机的总体功能是由指令系统来体现的,一般来说,若一台计算机的指令越丰富、寻址方式越多,且每条指令执行速度都较快,那么它的总体功能就越强。不同型号的计算机的指令系统也不相同。

### 3.1.1 汇编语言

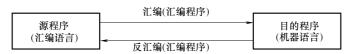

在计算机中,所有的指令、数据都是用二进制代码来表示的。这种用二进制代码表示的指令系统称为机器语言(Machine Language),用机器语言编写的程序称为机器语言程序或"目标程序"(Object Program)。为了书写方便,二进制代码常用十六进制代码表示。对于计算机,机器语言能被直接识别并快速执行。但对于使用者,这种用机器语言编写的程序很难识别和记忆,容易出错。为了克服这些缺点,出现了汇编语言和高级语言。

用英文字符来代替机器语言,这些英文字符被称为助记符。用助记符表示指令系统的语言称为汇编语言 (Assembly Language)。它由字母、数字和符号组成,又称"符号语言"。由于助记符一般都是操作功能的英文缩写,这样使程序易写、易读和易改。可见汇编语言仍是一种面向机器的语言,和 CPU 类别密切相关,不同 CPU 的机器有不同的汇编语言。本章介绍的 80C51 系列单片机程序都是汇编语言形式的。

但是计算机不能直接识别在汇编语言中出现的各种字符,需要将其转换成机器语言,通常把这一转换(翻译)工作称为汇编。汇编可以由查表的形式手工完成,也可由专门的程序来进行,这种程序称为汇编程序。汇编后得到的机器语言程序称为目的程序或目标程序,原来的汇编语言程序称为源程序。

由于汇编语言是一种面向机器的语言,因此受到机器种类的限制,不能在不同类型的计

算机上通用,这样就出现了高级语言,如 BASIC、PASCAL、C 语言等。高级语言是一种面向过程的语言,这种语言更接近英语和数字表达式,易被一般用户掌握。高级语言是独立于机器的,在编程时,用户不需要对机器的硬件结构和指令系统有深入的了解。高级语言直观、易学、通用性强、易于移植到不同类型的机器上去。

计算机对高级语言不能直接识别和执行,需要转换为机器语言,因此它的执行速度比机器语言和汇编语言慢,且占用内存空间大。

因汇编语言运行速度快,占用内存空间小,且易读易记,所以在工业控制中广泛采用的 是汇编语言。本章就用80C51单片机的汇编语言来描述其指令功能。

### 3.1.2 指令格式

### 1. 汇编语言指令的格式

汇编语言指令的一般格式如下:

「标号: ] 操作码助记符 「操作数] 「;注释]

其中每条指令必须有操作码助记符,带「 ] 的为可选项,可有可无。

标号是表示该指令位置的符号地址,代表该指令第一个字节所存放的存储器单元的地址。它是以英文字母开始的由 1~8 个字母或者数字组成的字符串,并以":"结尾。通常在子程序入口或者转移指令的目标地址才标号。

操作码助记符是表示指令功能的英文缩写。它是指令的核心部分,不能省略。例如,ADD 是加法的助记符,MOV 是传送的助记符。

操作数是表示指令操作所需要的操作数或者操作数的地址。指令的操作数可以是1个、2个或者3个,也可以没有。例如,NOP指令就没有操作数。操作数之间以","分隔,操作码与操作数之间以空格分隔。

注释字段是用户给该条指令或该程序的功能说明,是为了方便阅读程序的一种标注。注释以";"开始。注释不影响该指令的执行。

### 2. 机器语言指令的格式

机器语言指令是一种二进制代码,它包括两个基本部分:操作码和操作数。操作码规定 了指令操作的性质,操作数则表示指令操作的对象。在80C51的指令系统中,有单字节、

双字节和三字节共 3 种指令,它们分别占有 1~3 个程序存储器的单元。机器语言指令格式如图 3-1 所示。

器语言指令格式如图 3-1 所示。

本章第 3 节中每条指令都有较详

细的机器语言格式说明。

操作码

nn

操作码

nn

操作码

单字节指令

nn+1

操作数

nn+1

第一操作数

双字节指令

nn+2

第二操作数

三字节指令

图 3-1 机器语言指令的格式示意图

# 3.1.3 常用符号

在描述 80C51 指令系统的功能时,规定了一些描述寄存器、地址及数据等的符号,其意义如下:

Rn 当前选中的工作寄存器组 R0~R7 (n 为 0~7)。它在片内数据存储器中的地址由 PSW 中的 RS1、RS0 确定,可以是 00H~07H (第 0 组)、08H~0FH (第 1 组)、10H~17H (第 2 组)、18H~1FH (第 3 组)。

Ri 当前选中的工作寄存器组中可作为地址指针的 2 个工作寄存器 R0、R1 (i 为 0 或 1)。它在片内数据存储器中的地址由 RS0、RSI 确定,分别为 00H、01H; 08H、09H; 10H、11H; 18H、19H。

#data 8 位立即数,即包含在指令中的8 位常数。

#data16 16 位立即数,即包含在指令中的16 位常数。

direct 8 位片内 RAM 单元 (包括 SFR) 的直接地址。对于 SFR, 此地址可以直接用它的名称来表示, 如 ACC (此时不能用 A 代替)、PSW、PO 等。

addr11 11 位目的地址。用于 ACALL 和 AJMP 指令中,目的地址必须放在与下一条指令第 1 个字节同一个 2KB 程序存储器地址空间之内。

addr16 16 位目的地址。用于 LCALL 和 LJMP 指令中,目的地址范围在 64KB 程序存储器地址空间。

rel 补码形式的 8 位地址偏移量,用于相对转移指令中。偏移量以下一条指令第 1 个字节地址为基值,偏移范围为 - 128 ~ + 127。

bit 片内 RAM 或特殊功能寄存器的直接寻址位地址。

- @ 在间接寻址方式中,表示间址寄存器的符号。

- / 在位操作指令中,表示对该位先取反,再参与操作,但不影响该位原值。

以下符号仅出现在指令注释或功能说明中:

- X 片内 RAM 的直接地址(包含位地址)或寄存器。

- (X) 在直接寻址方式中,表示直接地址 X 中的内容;在间接寻址方式中,表示由间址寄存器 X 指出的地址单元。

- ((X)) 在间接寻址方式中,表示由间址寄存器 X 指出的地址单元中的内容。

- ← 在指令操作流程中,将箭头右边的内容送入箭头左边的单元内。

在本章指令注释中,表示寄存器 Rn 或累加器 A、寄存器 B 等中的内容时均不加括号。源操作数中的间址内容用((Ri))表示,但是目的操作数中送入某间址单元用(Ri)表示。注意,不是表示 Ri 中的内容,而是表示 Ri 间址单元里的内容。

# 3.2 寻址方式

执行任何一条指令都需要使用操作数(空操作除外)。寻址方式就是指在寻找操作数所在地址的方式。在这里,地址泛指一个立即数、某个存储单元或者某个寄存器等。80C51系列单片机有以下7种寻址方式。

### 3.2.1 立即寻址

立即寻址指在该指令中直接给出参与操作的常数 (称为立即数)。立即数前冠以"#", 以便与直接地址相区别。

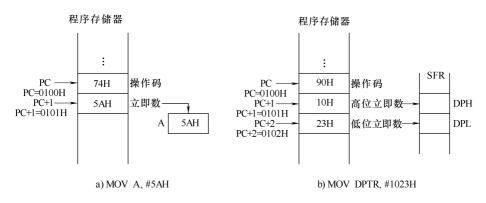

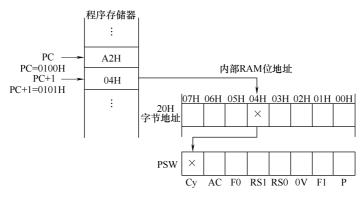

### 【例 3-1】 传送指令: MOV A. #5AH

这条指令的功能是把立即数 5AH 送入到累加器 A 中。指令机器代码为 74H、5AH, 双字节指令。在程序存储器中占的地址为 0100H 和 0101H (存放指令的起始地址是任意假设的)。该指令的执行过程如图 3-2a 所示。

在80C51 系列指令系统中还有一条16的立即数传送指令,即

MOV DPTR, #data16

该指令是把 16 位立即数 data16 送入数据指针 DPTR 中。DPTR 由两个特殊功能寄存器 DPH 和 DPL 组成。立即数的高 8 位送入 DPH 中,低 8 位送入 DPL 中。

### 【**例 3-2**】 16 位传送指令: MOV DPTR, #1023H

这条指令的功能是把 16 位的立即数送入 DPTR 中。其中高字节 10H 送入 DPH 中,低字节 23H 送入 DPL 中。指令的机器代码为 90H、10H、23H,是三字节指令,在程序存储器中占的地址为 0100H、0101H 及 0102H。该指令的执行过程如图 3-2b 所示。

图 3-2 立即寻址示意图

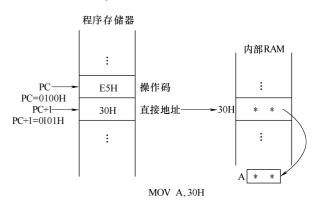

### 3.2.2 直接寻址

直接寻址就是在指令中直接给出操作数所在存储单元的地址,该地址指出了参与操作的数据所在的字节地址或者是位地址。在80C51单片机中,直接地址只能用来表示特殊功能

寄存器。内部数据存储器和位地址空间。其中,特殊功能寄存器和位地址 空间只能用直接寻址方式来访问。

【例 3-3】 传送指令: MOV A, 30H 这条指令的功能是把内部 RAM30H 单元的内容送入 A 中 (注意,内部 RAM 地址为 30H 单元中的内容可以是 00H ~ 0FFH 范围内的任意一个数)。指令代码为 E5H、30H,为双字节指令。在程序存储器中占的空间及寻址示意图如图 3-3 所示。

图 3-3 直接寻址示意图

### 3.2.3 寄存器寻址

在指令中指出某个寄存器 (Rn, A, B 和 DPTR 等) 中的内容作为操作数,这种寻址方式称为寄存器寻址。采用寄存器寻址可以获得较高的运算速度。

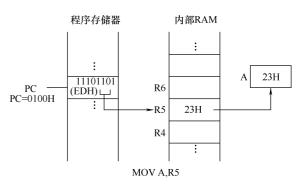

【例 3-4】 传送指令: MOV A, R5

这条指令的功能是把寄存器 R5 的内容送入到累加器 A 中。指令的代码为0EDH,单字节指令。其寻址示意图如图 3-4 所示。

### 3.2.4 寄存器间接寻址

寄存器间接寻址是指把指令中指定的寄存器的内容作为操作数的地址,把该地址对应单元中的内容作为操作数。这种寻址方式适于访问内部 RAM 和外部

图 3-4 寄存器寻址示意图

RAM。可以看出,在寄存器寻址中寄存器的内容作为操作数,但是寄存器间接寻址方式中,寄存器中存放的是操作数的地址。即指令操作数的获得是通过寄存器间接得到的。为了区别寄存器寻址和寄存器间接寻址,在寄存器间接寻址中应在寄存器名称的前面加间址符"@"。

在访问内部 RAM 的 00H~7FH 地址单元时,用当前工做寄存器 R0 或 R1 做地址指针来间接寻址。对于栈操作指令 PUSH 和 POP,则用堆栈指针 SP 进行寄存器间接寻址。

在访问外部 RAM 的页内 256 个单元( $00H \sim FFH$ )时,用 R0 或 R1 工作寄存器来间接寻址。在访问外部 RAM 整个 64K( $0000H \sim FFFFH$ )地址空间时,用数据指针 DPTR 来间接寻址。

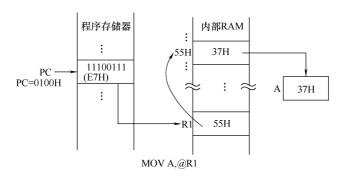

### 【例 3-5】 传送指令: MOV A, @ R1

这条指令属于寄存器间接寻址。它的功能是将寄存器 R1 的内容(设 R1 = 75H)作为地址,再将片内 RAM的 75H单元的内容(设 (75H) = 37H)送入累加器 A中。指令中在寄存器名前冠以"@",表示寄存器间接寻址,称之为间址符。指令代码为 0E7H,单字节指令。其寻址示意图如图 3-5 所示。

图 3-5 寄存器间接寻址示意图

# 3.2.5 变址寻址

变址寻址以程序计数器 PC 或数据指针 DPTR 作为基地址寄存器,以累加器 A 作为变址寄存器,把两者的内容相加形成操作数的地址 (16 位)。这种寻址方式用于读取程序存储器中的常数表。

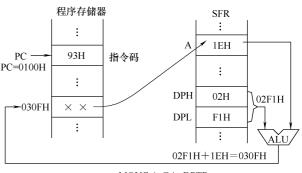

【**例 3-6**】 查表指令: MOVC A,@A+DPTR

这条指令的其功能是把 DPTR 的 内容作为基地址,把累加器 A 中的内 容作为地址偏移量,两者相加后得到 16 位地址,把该地址对应的程序存储 器 ROM 单元中的内容送到累加器 A 中。指令代码为 93H,单字节指令。 其寻址过程示意图如图 3-6 所示。

### 3.2.6 相对寻址

相对寻址以程序计数器 PC 的当前 值作为基地址,与指令中给定的相对

MOVC A,@A+DPTR

图 3-6 变址寻址示意图

偏移量 rel 进行相加,把所得之和作为程序的转移地址。这种寻址方式用于相对转移指令中。 指令中的相对偏移量是一个 8 位带符号数,用补码表示。

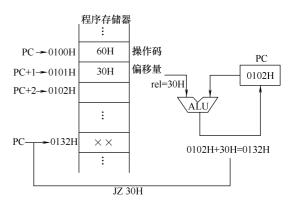

### 【例 3-7】 累加器 A 内容判零指令: JZ 30H

这条指令是以累加器 A 的内容是否为零作为条件的相对转移指令,指令代码为60H、30H,为两字节指令。其功能为:当 A=0 时,条件满足,则程序执行发生转移  $PC\leftarrow PC+2+rel;$ 当  $A\neq 0$  时,条件不能满足,则程序顺序执行  $PC\leftarrow PC+2$ 。其寻址示意图如图 3-7 所示。

80C51 指令系统中,相对寻址指令多数为 2 字节指令,执行完相对寻址指令后,当前的 PC 值应该为这条指令首字节所在单元的地址值(源地址)加2,所以偏移量应该为

图 3-7 相对寻址示意图

rel = 目的地址 - (源地址 + 2)

但也有一些是 3 字节的相对寻址指令 (如 CJNE A, direct, rel), 那么执行完这条指令后, 当前的 PC 值应该为本指令首字节所在单元的地址值加 3, 所以偏移量为

$$rel = 目的地址 - (源地址 + 3)$$

相对偏移量 rel 是一个带符号的 8 位二进制数,以补码形式出现。因此,程序的转移范围在相对 PC 当前值的 – 128 ~ +127 个字节单元之间。

### 3.2.7 位寻址

80C51 单片机中设有独立的位处理器。位操作指令能对内部 RAM 中的位寻址区和某些有位地址的特殊功能寄存器进行位操作。也就是说可对位地址空间的每个位进行位变量传送、状态控制、逻辑运算等操作。

【例 3-8】 位传送指令: MOV C, 04H

这条指令的功能是把位地址 04H 中的内容传送到 Cy 中 (即把内部 RAM 的 20H 单元的

$D_4$  位 (位地址为 04H) 的内容传送到位累加器 C 中)。指令代码为 0A2H、04H,为双字节指令。其寻址示意图如图 3-8 所示。

MOVC, 04H

图 3-8 位寻址示意图

上面介绍了80C51 指令系统的7种寻址方式。实际上许多指令本身包含着两个或三个操作数,这时往往就具有几种类型的寻址方式。这里面重点讨论的是源操作数的寻址方式。

这条指令的功能是把 4FH 这个立即数送入到累加器 A 中。其中源操作数为立即寻址,目标操作数为寄存器寻址。

比较不相等则转移指令: CJNE

A,

30H,

NEXT

寄存器寻址

直接寻址

相对寻址

这是条件转移指令中的比较不相等则转移指令,其功能为比较累加器 A 的内容与直接 地址 30H 的内容是否相等,如果不相等则加上偏移量 rel 转移到 NEXT 位置,如果相等则顺序执行。

### 3.2.8 寻址空间

80C51 单片机指令系统一共有 7 种寻址方式,每种寻址方式都有自己使用的变量和适用的寻址空间,见表 3-1。根据不同的存储器或者存储器中不同的位置分别采用不同的寻址方式,这是 80C51 单片机指令系统的特点,在以后学习的过程中应注意区分。

| 序 号 | 寻址方式  | 使用的变量                 | 寻址空间                     |

|-----|-------|-----------------------|--------------------------|

| 1   | 立即寻址  |                       | 程序存储器                    |

| 2   | 直接寻址  |                       | 片内 RAM 低 128B<br>特殊功能寄存器 |

| 3   | 寄存器寻址 | RO~R7, A, B, DPTR, CY |                          |

|     | 寄存器   | @ R0 、@ R1 、SP        | 片内 RAM                   |

| 4   | 间接寻址  | @ R0 、@ R1 、@ DPTR    | 片外 RAM                   |

表 3-1 80C51 中的寻址方式和寻址空间

序 묵 寻址方式 使用的变量 寻址空间 相对寻址 5 PC + 偏移量 程序存储器  $@A + PC \setminus @A + DPTR$ 变址寻址 程序存储器 片内 RAM 中的位寻址区可以位寻址的特殊功能 7 位寻址 寄存器位

3.3 80C51 的指令系统

80C51 的指令系统使用了7种寻址方式,共有111条指令。若按字节数分类,则单字节指令49条,双字节46条,3字节指令16条;若按运算速度分类,则单周期指令64条,双周期45条,4周期指令2条。由此可见,80C51指令系统在占用存储空间和运行时间方面,效率都比较高。按照指令的功能来分类,80C51指令系统可分为下面的5类;

- ① 数据传送类指令(28条)。

- ② 算术运算类指令 (24 条)。

- ③ 逻辑运算类指令 (25条)。

- ④ 控制转移类指令(17条)。

- ⑤ 位操作类指令 (17条)。

### 3.3.1 数据传送指令

数据传送指令把第二个"源操作数"中的数据传送到第一个"目的操作数"中去,而"源操作数"的内容保持不变。这类指令在程序中占有较大的比重,是一种最基本最常用的操作。

### 1. 对内部 RAM 和 SFR 之间的数据传送指令

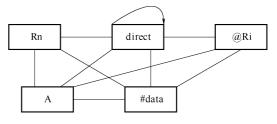

80C51 内部 RAM 和特殊功能寄存器 SFR 各存储单元之间的数据传送,通常是通过 MOV 指令来实现的,这类指令称为内部 RAM 和 SFR 的一般数据传送指令。其传送操作示意图如图 3-9 所示。

(1) 以累加器为目的操作数的指令(见表 3-2)

图 3-9 内部 RAM 和 SFR 之间的传送操作示意图

表 3-2 以累加器为目的操作数的指令

| 指令名称     | 汇编格式          | 操作          | 机 器 码          | 机器周期 |

|----------|---------------|-------------|----------------|------|

|          | MOV A, Rn     | A←(Rn)      | E8H ~ EFH      | 1    |

| 以累加器 A 为 | MOV A, direct | A←( direct) | 85 H<br>direct | 1    |

| 目的操作数    | MOV A, @ Ri   | A←((Ri))    | E6H ~ E7H      | 1    |

|          | MOV A, #data  | A←data      | 74H<br>data    | 1    |

(续)

这类指令是把源操作数送入目的操作数 A 中,源操作数的寻址方式分别为寄存器寻址、直接寻址、寄存器间接寻址和立即寻址。

【**例 3-10**】 若 R1 = 21H, (21H) = 55H, 执行指令"MOV A, @ R1"后的结果为, A = 55H, 而 R1 的内容和 21H 单元的内容均不变。

(2) 以寄存器为目的操作数的指令(见表 3-3)

| 指令名称      | 汇编格式           | 操作           | 机器码                 | 机器周期 |

|-----------|----------------|--------------|---------------------|------|

|           | MOV Rn, A      | Rn←A         | F8H ~ FFH           | 1    |

| 以寄存器 Rn 为 | MOV Rn, direct | Rn←( direct) | A8H ~ AFH<br>direct | 2    |

| 目的操作数     | MOV Rn, #data  | Rn←data      | 78H ~7FH<br>data    | 1    |

表 3-3 以寄存器为目的操作数的指令

这类指令是把源操作数送入目的操作数 Rn 中,源操作数的寻址方式分别为寄存器寻址、直接寻址和立即寻址。

【**例 3-11**】 若 (50H) = 45H, R5 = 33H, 执行指令 "MOV R5, 50H" 后的结果为, R5 = 45H, 50H 单元的内容不变。

(3) 以直接地址为目的操作数的指令(见表 3-4)

| 指令名称            | 汇编格式                 | 操 作                                                            | 机器码                       | 机器周期 |

|-----------------|----------------------|----------------------------------------------------------------|---------------------------|------|

|                 | MOV direct, A        | $(direct) \leftarrow A$                                        | F5H<br>direct             | 1    |

|                 | MOV direct, Rn       | ( direct ) ←Rn                                                 | 88H ~8FH                  | 2    |

| 以直接地址为<br>目的操作数 | MOV direct2, direct1 | $(\operatorname{direct2}) \leftarrow (\operatorname{direct1})$ | 85H<br>direct1<br>direct2 | 2    |

|                 | MOV direct, @ Ri     | ( direct ) ←( ( Ri ) )                                         | 86H ~87H<br>direct        | 2    |

|                 | MOV direct, #data    | ( direct ) ←data                                               | 75H<br>direct<br>data     | 2    |

表 3-4 以直接地址为目的操作数的指令

这类指令的功能是把源操作数送入目的操作数 direct 中,源操作数的寻址方式分别为寄存器寻址、直接寻址、寄存器间接寻址和立即寻址。

直接地址之间的直接传送指令生产机器码时源地址在前,目的地址在后。如"MOV 40H,41H"对应的机器码为85H、41H、40H。

【**例 3-12**】 若 R0 = 50H, (50H) = 6AH, (70H) = 2FH, 执行指令 "MOV 70H, @ R0" 后的结果为, (70H) = 6AH, R0 中的内容和 50H 单元的内容不变。

# (4) 以寄存器间接地址为目的操作数的指令(见表 3-5)

| 指令名称           | 汇编格式             | 操作                                                         | 机 器 码               | 机器周期 |

|----------------|------------------|------------------------------------------------------------|---------------------|------|

| 以寄存器间接地址为目的操作数 | MOV @ Ri, A      | ( Ri ) ←A                                                  | F6H ~ F7H           | 2    |

|                | MOV @ Ri, direct | $(\operatorname{Ri})\!\leftarrow\!(\operatorname{direct})$ | A6H ~ A7H<br>direct | 2    |

|                | MOV @ Ri, #data  | (Ri)←data                                                  | 76H ~ 77H<br>data   | 1    |

表 3-5 以寄存器间接地址为目的操作数的指令

这类指令的功能是把源操作数送人目的操作数@Ri中,源操作数的寻址方式分别为寄存器寻址,直接寻址和立即寻址。提醒一下读者,在这类指令中,目的操作数@Ri中的表示方法为单括号,并不表示Ri中的内容,而是表示间址寄存器Ri的地址单元。

【**例 3-13**】 若 R1 = 30H, (30H) = 22H, A = 34H, 执行指令 "MOV @ R1, A" 后的结果为, (30H) = 34H, R1 和 A 当中的内容不变。

(5) 16 位数据的传送指令(见表 3-6)

| 指令名称     | 汇编格式              | 操作                            | 机 器 码                        | 机器周期 |

|----------|-------------------|-------------------------------|------------------------------|------|

| 16 位数据传送 | MOV DPTR, #data16 | DPH←data15 ~8<br>DPL←data7 ~0 | 90H<br>data15 ~8<br>data7 ~0 | 2    |

表 3-6 16 位数据的传送指令

这条指令是唯一的一条 16 位传送指令,通常用来给 DPTR 赋初值。源操作数的寻址方式为立即寻址。读者可以参看本章寻址方式中【例 3-2】。

有关内部 RAM 和 SFR 之间的数据传送指令的说明:

- ① 指令操作数为 Rn 时,属于寄存器寻址。80C51 内部 RAM 区中有 4 组工作寄存器,每组由 8 个寄存器组成,用户可通过改变 PSW 中的 RSO 和 RS1 这两位来切换当前工作寄存器组。

- ② 指令中操作数为@ Ri 时,属于寄存器 R0 或 R1 间接寻址。它根据操作码字节中  $D_0$  位 i 的取值为 0 或 1,来决定以哪个寄存器进行间接寻址。

- ③ 直接寻址的数传指令比较丰富,使得内部数据存储器各单元之间的数传十分方便。特别令人感兴趣的是直接地址到直接地址的传送。直接地址 direct 是 8 位地址,原则上寻址范围为 00H ~ FFH。对 80C51 来说,内部 RAM 地址空间是 00H ~ 7FH。而 21 个 SFR 离散地分布在 80H ~ FFH 的地址空间中,有许多单元是无定义的。因此 direct 不能为无定义的内部数据存储单元的地址,否则将得不到正确的结果。

- ④ 数据传送指令都不影响标志位 (除目的操作数是累加器 A 时会根据传送来的数据改变奇偶标志外)。

#### 2. 累加器 A 与外部数据存储器传送指令

CPU 与外部 RAM 的数据传送指令, 其助记符为 MOVX, 其中的 X 就是单词 external (外部) 的第二个字母,表示访问外部 RAM。这类指令共有 4 条,见表 3-7。

| 指令名称      | 汇编格式           | 操作              | 机器码       | 机器周期 |

|-----------|----------------|-----------------|-----------|------|

|           | MOVX A, @ DPTR | A←((DPTR))      | ЕОН       | 2    |

| 累加器 A 与外部 | MOVX @ DPTR, A | ( ( DPTR ) ) ←A | FOH       | 2    |

| RAM 的数据传送 | MOVX A, @ Ri   | A←((Ri))+((P2)) | E2H ~ E3H | 2    |

|           | MOVX @ Ri, A   | ((Ri))+((P2))←A | F2H ~ F3H | 2    |

表 3-7 累加器 A 与外部数据存储器传送指令

这组指令的功能是,在累加器 A 与外部 RAM 或扩展 I/O 口之间进行数据传送,且仅为寄存器间接寻址。80C51 只能用这种方式与连接在扩展 I/O 口的外部设备进行数据传送。

前两条指令以 DPTR 作为外部 RAM 的 16 位地址指针,由 P0 口送出低 8 位地址,由 P2 口送出高 8 位地址,寻址能力为 64KB。后 2 条指令用 R0 或 R1 作外部 RAM 的低 8 位地址指针,由 P0 口送出地址码,P2 口的状态不受影响,寻址能力为外部 RAM 空间 256 个字节单元。

【**例 3-14**】 若 DPTR = 1020H, 外部 RAM (1020H) = 54H, 执行指令"MOVX A, @ DPTR"的结果为 A = 54H, DPTR 的内容和外部 RAM1020H 单元的内容不变。

【**例 3-15**】 若 P2 = 03H, R1 = 40H, A = 7FH, 执行指令"MOVX @ R1, A"后的结果为外部 RAM (0340H) = 7FH, P2 和 R1 及 A 中内容不变。

【例 3-16】 把外部数据存储器 2040H 单元的内容送入内部寄存器 R2 中。

MOV DPTR, #2040H

MOVX A, @ DPTR

MOV R2, A

#### 3. 累加器 A 与程序存储器的传送指令

80C51 指令系统提供了两条累加器 A 与程序存储器的数传指令,指令助记符采用 MOVC,其中 C 就是单词 code (代码)的第一字母,表示读取 ROM 中的代码。这是两条极 为有用的查表指令,见表 3-8。

| 指令名称 | 汇编格式               | 操 作                                            | 机器码 | 机器周期 |

|------|--------------------|------------------------------------------------|-----|------|

| 查表   | MOVC A, @ A + PC   | $PC \leftarrow PC + 1$ $A \leftarrow (A + PC)$ | 83H | 2    |

|      | MOVC A, @ A + DPTR | $A \leftarrow (A + DPTR)$                      | 93H | 2    |

表 3-8 累加器 A 与程序存储器的传送指令

第一条指令为单字节指令, CPU 读取本指令后, PC 已执行加 1 操作, 指向下一条指令的首字节地址。该指令以 PC 作为基址寄存器, 累加器 A 的内容为无符号整数, 两者相加得到一个 16 位地址, 把该地址指出的程序存储器单元的内容送到累加器 A 中(见表 3-8)。

【例 3-17】 设 A = 35H, 执行指令"1000H; MOVC A, @ A + PC"后的结果;

首先把累加器 A 中的内容加上本条指令执行后的 PC 值 1001H, 然后将程序存储器 1036H 单元的内容送入累加器 A 中,即 A←(1036H)<sub>ROM</sub>。

本指令的优点是不改变 PC 的状态,仅根据累加器 A 的内容就可以取出表格中的数据。 缺点是表格只能存放在该查表指令后面的 256 个单元之内,表格的长度受到限制,而且表格 只能被一段程序所使用。

第二条指令以 DPTR 作为基址寄存器, 累加器 A 的内容作为无符号数, 两者相加后得到一个 16 位地址, 把该地址指出的程序存储器单元的内容送到累加器 A 中。

【**例 3-18**】 设 DPTR = 2010H, A = 40H, 执行指令"MOVC A, @ A + DPTR"后的结果:

首先把累加器 A 与 DPTR 的内容相加得 2050H, 然后将程序存储器中 2050H 单元中的内容送入累加器 A 中,即 A $\leftarrow$ (2050H)<sub>BOM</sub>。

本查表指令的执行结果只与 DPTR 和 A 的内容有关,与该指令存放的地址及表格存放的地址无关。因此表格的长度和位置可以在 64KB 的程序存储器空间任意改变,而且一个表格可以被多个程序段共享。

【**例 3-19**】 把外部数据存储器 2042H 的内容送入内部 RAM 的 50H 中。

方法一:

MOV DPTR, #2042H

MOVX A. @ DPTR:外部 RAM 2042H 单元的内容中送入 A 中

MOV 50H. A: 由 A 送入内部 RAM 50H 中

方法二:

MOV P2, #20H; 地址的高 8 位由 P2 口送出

MOV RO, #42H

MOVX A, @ RO: 把外部 RAM 2042H 的内容送入 A 中

MOV 50H, A; 由 A 送入内部 RAM 50H 中

【**例 3-20**】 把程序存储器 0150H 单元的内容取出送到外部 RAM 的 1070H 中。

MOV DPTR, #0150H

MOV A, #00H

MOVC A, @ A + DPTR;程序存储器 0150H 的内容取到 A 中

MOV DPTR, #1070H

MOVX @ DPTR. A: A 的内容送入外部 RAM 1070H 单元中

### 4. 数据交换指令

数据传送指令还提供了 4 条数据交换指令,包括 3 条字节交换指令和 1 条半字节交换指令。

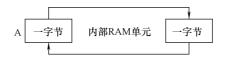

#### (1) 字节交换指令(见表 3-9)

| 指令名称 | 汇编格式          | 操作          | 机 器 码         | 机器周期 |

|------|---------------|-------------|---------------|------|

|      | XCH A, Rn     | A≒Rn        | C8H ~ CFH     | 1    |

| 字节交换 | XCH A, direct | A≒ (direct) | C5H<br>direct | 1    |

|      | XCH A, @ Ri   | A≒((Ri))    | С7Н           | 1    |

表 3-9 字节交换指令

字节交换指令的功能是将累加器 A 的内容与内部 RAM 中任何一个单元的内容相互交换。其操作也可表示为

【**例 3-21**】 若 A = 7AH, R1 = 45H, (45H) = 39H, 执行指令"XCH A, R1"后的结果为, A = 45H, R1 = 7AH。

若 A = 7AH, R1 = 45H, (45H) = 39H, 执行指令 XCH A, @ R1 后的结果为 A = 39H, (45H) = 7AH, R1 = 45H。

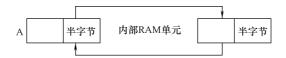

(2) 低半字节交换指令(见表 3-10)

表 3-10 低半字节交换指令

| 指令名称       | 汇编格式         | 操作                                                | 机器码       | 机器周期 |

|------------|--------------|---------------------------------------------------|-----------|------|

| 低半字<br>节交换 | XCHD A, @ Ri | $A_{0 \sim 3} \leftrightarrows ((Ri))_{0 \sim 3}$ | D6H ~ D7H | 1    |

这条指令的功能是将累加器 A 的低 4 位与 Ri 间接寻址单元的低 4 位相互交换,而各自的高 4 位维持不变。其操作表示为

【**例 3-22**】 设 A = 59H, R0 = 45H, (45H) = 7AH, 执行指令"XCHD A, @ R0"后的结果为, A = 5AH, R0 = 45H(不变), (45H) = 79H。

#### 5. 堆栈操作指令

在80C51 内部 RAM 中可以设定一个 LIFO (后进先出) 或 FILO (先进后出) 区域作为 堆栈,在 SFR 中有一堆栈指针 (8 位寄存器),它指出栈顶的位置。在80C51 指令系统中,有两条用于数据传送的栈操作指令,见表3-11。

表 3-11 堆栈操作指令

| 指令名称 | 汇编格式        | 操作                                                   | 机器码           | 机器周期 |

|------|-------------|------------------------------------------------------|---------------|------|

| 进栈   | PUSH direct | $SP \leftarrow SP + 1$<br>(SP) $\leftarrow$ (direct) | C0H<br>direct | 2    |

| 出栈   | POP direct  | ( direct ) ← ( (SP) )<br>SP←SP – 1                   | D0H<br>direct | 2    |

堆栈是在 RAM 中设定的存储区, 栈底是固定的, 栈顶是浮动的, 所有的信息存入和取出都是在浮动的栈进行的。存取数据依据"先入后出、后入先出"的规则。堆栈技术在子程序嵌套时常用于保存断点, 在多级中断时用来保存断点和现场等。用堆栈指令也可以实现内部 RAM 单元之间的数据传送和交换。

【**例 3-23**】 在中断处理时堆栈指令用于保护现场和恢复现场。设 SP = 60H,中断服务程序的一般结构如下:

PUSH ACC ;  $SP \leftarrow SP + 1 (SP = 61H)$

$(61H) \leftarrow ACC$

PUSH PSW :  $SP \leftarrow SP + 1 (SP = 62H)$

(62H)←PSW

: 中断处理

POP PSW ; PSW $\leftarrow$ (62H)

$SP \leftarrow SP-1 \quad (SP = 61H)$

POP ACC ; A←(61H)

$SP \leftarrow SP-1 \quad (SP = 60H)$

RETI ; 中断返回

【**例 3-24**】 设(30H)=51H,(40H)=6AH,将内部RAM的这两个单元的内容交换。

PUSH 30H ; 30H 单元的内容进栈 PUSH 40H ; 40H 单元的内容进栈

POP 30H ;将栈顶元素弹出,送入30H单元

POP 40H : 再将下一个元素出栈, 送入 40H 单元

执行结果为, (30H) = 6AH, (40H) = 51H。

### 3.3.2 算术运算指令

80C51 的算术运算指令也比较丰富,包括加、减、乘、除法指令,数据运算功能较强。 80C51 的算术运算指令,仅直接执行 8 位数的算术操作。指令的执行结果将使 PSW 中的进位标志 Cy、半进位标志 AC 和溢出标志 OV 置位或复位,只有加 1 和减 1 指令不影响这

些标志,乘除指令不影响 AC 标志位。注意,无论执行何种指令,PSW 中的奇偶标志 P 总是表示累加器 A 的奇偶性。

#### 1. 加法指令

(1) 不带进位的加法指令(见表 3-12)

指令名称 汇编格式 操 机器码 机器周期 1 ADD A, Rn  $A \leftarrow A + Rn$  $28H \sim 2FH$ 25H ADD A, direct  $A \leftarrow A + (direct)$ 1 不带进位加法 direct 26H~27H ADD A, @ Ri A←A + ( ( Ri ) ) 1 ADD A, #data  $A \leftarrow A + data$ 24H

表 3-12 不带进位的加法指令

这类指令的功能是把所指出的字节变量加到累加器 A 中去,运算结果存放在累加器 A 中。

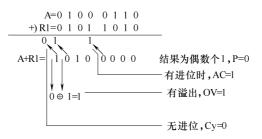

加法指令对 PSW 各标志位产生影响,在相加的结果中,如果  $D_7$  有进位,则 Cy=1,否则 Cy=0;如果  $D_3$  有进位,则 AC=1,否则 AC=0;如果  $D_6$  有进位而  $D_7$  没进位,或者  $D_7$  有进位而  $D_6$  没进位,则 OV=1,否则 OV=0;如果相加结果在 A 中 1 的个数为奇数,则 P=1,否则 P=0。

【例3-25】 设 A = 46H, R1 = 5AH, 试分析执行指令 "ADD A, R1 ; A←A + R1"

后的结果以及对标志位的影响。

结果为, A = A0H, R1 = 5AH (不变)。

(2) 带进位的加法指令 (见表 3-13)

| 指令名称  | 汇编格式           | 操作                    | 机 器 码         | 机器周期 |

|-------|----------------|-----------------------|---------------|------|

|       | ADDC A, Rn     | A←A + Rn + Cy         | 38H ~ 3FH     | 1    |

| 带进位加法 | ADDC A, direct | A←A + ( direct ) + Cy | 35H<br>direct | 1    |

|       | ADDC A, @ Ri   | A←A + ( ( Ri ) ) + Cy | 36H ~ 37H     | 1    |

|       | ADDC A, #data  | A←A + data + Cy       | 34H<br>data   | 1    |

表 3-13 带进位的加法指令

这类指令的功能是同时把所指出的字节变量、进位标志 Cy 和累加器 A 的内容相加,相加后的结果存放在累加器 A 中。

【例 3-26】 设 A = 85H, (20H) = FFH, Cy = 1, 试分析执行指令 "ADDC A, 20H;  $A \leftarrow A + (20H) + Cy$ " 后的结果以及对标志位的影响。

结果为, A=85H, (20H)=FFH (不变)。

【**例 3-27**】 编写程序计算 1234H + 0FE7H, 将和的高 8 位存入 31H 中, 低 8 位存入 30H 中。

两个 16 位数相加可以分为 2 步: 第 1 步先加低 8 位, 第 2 步对高 8 位相加。由于高 8 位相加时候需要考虑到低 8 位可能产生的进位, 第 2 步必须用带进位的加法指令。

MOV A, #34H

ADD A, #0E7H

MOV 30H, A

MOV A, #12H

ADDC A, #0FH MOV 31H, A

### (3) 加1指令(见表3-14)

|            |            | 700 II 201 I                                                     |               |      |

|------------|------------|------------------------------------------------------------------|---------------|------|

| 指令名称       | 汇编格式       | 操作                                                               | 机 器 码         | 机器周期 |

|            | INC A      | A←A + 1                                                          | 04H           | 1    |

|            | INC Rn     | Rn←Rn + 1                                                        | 08H ~0FH      | 1    |

| <b>加</b> 1 | INC direct | $(\operatorname{direct}) \leftarrow (\operatorname{direct}) + 1$ | 05H<br>direct | 1    |

|            | INC @ Ri   | (Ri)←((Ri))+1                                                    | 06H ~ 07H     | 1    |

|            | INC DPTR   | DPTR←DPTR + 1                                                    | АЗН           | 2    |

表 3-14 加 1 指令

这类指令的功能是把操作数指定单元的内容加1 (提醒读者加1指令是单操作数的指令),除奇偶标志外,操作结果不影响 PSW 中的标志位。若原来单元的内容为 FFH 时,加1后将溢出为00H。

【例 3-28】 将累加器 A 的内容加 1, 有以下两种方法:

INC A ; 单字节指令,只影响奇偶标志 P,不影响其他标志位。 或 ADD A,#01H ; 双字节指令,影响 PSW 各标志位(Cy, OV, AC, P)。 从标志位状态和指令长度来看,这两条指令是不等价的。

### 2. 减法指令

减法指令80C51指令系统中仅有带借位的减法和减1指令。

(1) 带借位减法指令(见表 3-15)

指令名称 汇编格式 操 作 机器码 机器周期 SUBB A, Rn  $A \leftarrow A - Rn - Cy$ 98H~9FH 95H SUBB A, direct  $A \leftarrow A - (direct) - Cy$ direct 带借位减法 SUBB A, @ Ri  $A \leftarrow A - ((Ri)) - Cy$ 96H~97H 1 94H  $A \leftarrow A - data - Cy$ SUBB A, #data 1 data

表 3-15 带借位减法指令

这组指令的功能是从累加器 A 中减去指定变量及借位 Cy 的值,差值存放在累加器 A 中。在 80C51 指令系统中没有提供不带借位减法指令,但在"SUBB"指令之前加一条"CLR C"指令先将 Cy 清零,可以实现不带借位减法的功能。

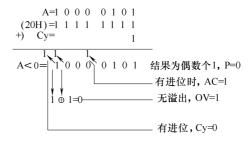

带借位的减法指令对 PSW 各标志位产生影响。在相减时,如果  $D_7$  位有借位,则  $C_9 = 1$ ,否则  $C_9 = 0$ ;若  $D_3$  位有借位,则  $C_9 = 1$ ,否则  $C_9 = 0$ ;若  $C_9 = 0$ ;若  $C_9 = 0$ ;在不需借位,则  $C_9 = 0$ ;如果  $C_9 = 0$ ,如果  $C_9 = 0$ ;如果  $C_9 = 0$ ;如果  $C_9 = 0$ ;如果  $C_9 = 0$ ,如果  $C_9 = 0$  和  $C_9 = 0$ ,

【例 3-29】 设 A = C9H, R2 = 54H, Cy = 1, 试分析执行指令 "SUBB A, R2 ; A←

A-R2-Cy"后的结果以及对标志位的影响。

结果为, A=74H, R2=54H(不变); Cy=0, AC=0, OV=1, P=0。

本例中,若看作两个无符号数相减,差为74H,是正确的;若看作两个带符号数相减,则从负数减去一个正数,结果为正数是错误的,OV=1表示运算有溢出。

### (2) 减1指令(见表3-16)

指令名称 汇编格式 作 机器码 机器周期 操 DEC A  $A \leftarrow A - 1$ 14H 1 DEC Rn  $Rn\leftarrow Rn - 1$ 18H ~ 1FH 1 减 1 15H  $(direct) \leftarrow (direct) - 1$ 1 DEC direct direct DEC @ Ri 16H ~ 17H  $(Ri)\leftarrow((Ri))-1$ 1

表 3-16 减 1 指令

减1指令的功能是,将操作数指定单元的内容减1。除奇偶标志外,操作结果不影响 PSW 的标志位。若原单元的内容为00H,减1后下溢为FFH。其他情况与加1指令类同。

### 3. 乘法指令(见表 3-17)

表 3-17 乘法指令

| 指令名称 | 汇编格式   | 操作                         | 机器码 | 机器周期 |

|------|--------|----------------------------|-----|------|

| 乘法   | MUL AB | $BA \leftarrow A \times B$ | A4H | 4    |

这条指令的功能是把累加器 A 和 B 寄存器中的两个 8 位无符号数相乘,把 16 位乘积的低 8 位存放在累加器 A 中,高 8 位存放寄存器 B 中。如果乘积大于 255 (即 FFH),则溢出标志位 OV 置 1,否则为 0;进位标志总是为 0;半进位标志 AC 保持不变;奇偶标志 P 仍按 A 中的 1 的奇偶性来确定。

【**例 3-30**】 设 A = 32H (即 50), B = 60 (即 96), 执行指令 "MUL AB; BA←A×B" 后的结果:

乘积为 12C0H (即 4800) > FFH (即 255)

A = COH, B = 12H

标志位 Cy = 0, OV = 1, P = 0

4. 除法指令(见表 3-18)

表 3-18 除法指令

| 指令名称 | 汇编格式   | 操作                                      | 机器码 | 机器周期 |

|------|--------|-----------------------------------------|-----|------|

| 除法   | DIV AB | $A (商) \leftarrow \frac{A}{B}$ $B (余数)$ | 84H | 4    |

这条指令的功能是把累加器 A 中的 8 位无符号整数除以寄存器 B 中的 8 位无符号数,所得的商(为整数)存放在 A 中,余数存放在 B 中,标志位 Cy 和 OV 均被清 O。但是,如果除数 B=00H 时,执行该指令,A、B 的内容无法确定,且溢出标志 OV 置 O 1,O 2 以行除法指令时,半进位标志 O 4 不受影响,奇偶标志 O 7 仍按 O 8 的内容而定。

【**例 3-31**】 设 A = FFH (255), B = 12H (18), 执行指令 "DIV AB; A B←A÷B" 后的结果:

商 A = 0EH (14), 余数 B = 03H (3)

标志位 Cy = 0、OV = 0、P = 1

### 5. 十进制调整指令(见表 3-19)

表 3-19 十进制调整指令

| 指令名称     | 汇编格式 | 操作                   | 机器码 | 机器周期 |

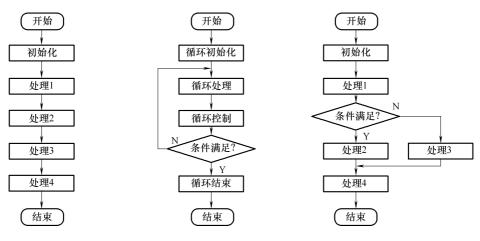

|----------|------|----------------------|-----|------|